ляющий вхЬд которого подключен к выходу элемента И, выход накапливающего сумматора соединен с информационным входом блока памяти, выход которого соединен с входом начальной установки первого делителя частоты, с первым управляющим входом блока регулируемой задержки и подключен к выходу элемента задержки, вход записи блока памяти соединен с подвижным контактом четвертого переключателя, первый неподвижный контакт которого соединен с вторым информационным входом блока регулируемой задержки и подключен к выходу второг делителя частоты, выход триггера соединен с вторым управляющим входом блока регулируемой задержки, третьим и четвертым неподвижными контактами второго переключателя, пятый неподвижный контакт которого подключен к выходу первого делителя частоты, подвижный контакт второго переключателя соединен с третьим входом элемента И, шестой неподвижный контакт второго переключателя подключен к выходу блока регулируемой задержки.

2. Устройство по п. 1, отличающееся тем, что блок регулируемой задержки содержит регистр сдвига, кольцевой счетчик и схему сравнения, первая и вторая группы входов которой соединены с соответствующими разрядными выходами регистра сдвига и кольцевого счетчика, выход схемы сравнения является выходом ,блока, счетный вход регистра сдвига .является первым информационным входом блока, первым и вторым управляющими входами которого являются соответственно вход сдвига и вход записи регистра сдвига, вход кольцевого счетчика является вторым информационным входом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения вероятностных характеристик фазы случайного процесса | 1985 |

|

SU1300510A2 |

| Устройство для измерения вероятностных характеристик фазы случайного сигнала | 1985 |

|

SU1320822A1 |

| Устройство для определения условного математического ожидания | 1980 |

|

SU959104A1 |

| Анализатор случайных процессов | 1987 |

|

SU1474678A1 |

| СПОСОБ ФОРМИРОВАНИЯ СИГНАЛА ИЗОБРАЖЕНИЯ ИНТЕРФЕРОГРАММ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2011 |

|

RU2448431C1 |

| МНОГОМЕРНЫЙ СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР УСРЕДНЕННОЙ МОЩНОСТИ НЕСТАЦИОНАРНОЙ НАГРУЗКИ | 1992 |

|

RU2060542C1 |

| Устройство для определения вероятности нахождения сигнала в заданном амплитудном диапазоне | 1990 |

|

SU1758632A1 |

| Устройство для измерения корреляционногоОТНОшЕНия дВуХ СлучАйНыХ пРОцЕССОВ | 1979 |

|

SU851420A2 |

| Цифровой измеритель частоты заполнения радиоимпульсов | 1982 |

|

SU1161892A1 |

| Анализатор плотности распределения амплитуд | 1980 |

|

SU903908A1 |

1. УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ВЕРОЯТНОСТНЫХ ХАРАКТЕРИСТИК ФАЗЫ, СЛУЧАЙНОГО СИГНАЛА, содержащее элемент задержки, счетчик, первый преобразователь фаза - временной интервал, информационный вход которого является первым информационным входом устройства, выход йервого преобразователя фаза - временной интервал соединен с первым входом первого временного селектора, второй преобразователь фаза - временной интервал, информационный вход которого является вторым информационным входом устройства, выход второго преобразователя фаза - временной интервал соединен с первым входом второго временного селектора, выход которого соединен со счетным входом первого делителя частоты и нулевым входом триггера, единичный вход которого подключен к выходу первого делителя часто-ты, последовательно соединенные формирователь импульсов и второй делитель частоты, выход которого соединен с первым входом элемента И, вход формирователя импульсов является входом синхронизации устройства, о тличающееся тем, что, с целью расширения класса решаемых задач, в него введены первый, второй, третий и четвертый переключатели, накапливающий сумматор, умножитель частоты, блок памяти и блок регулируемой задержки, причем управляющий вход первого преобразователя фаза временной интервал объединен с входом умножителя частоты, входом элемента i задержки, первым и вторым неподвижными контактами первого переключате(Л ля, с первым и вторым неподвижными контактами второго переключателя, вторым входом элемента И, информа- .. ционным входом блока регулируемой задержки, управляющим входом второго преобразователя фаза - временной интервал и подключен к выходу формирователя импульсов, управляющие входы 1чЭ первого и второго временных селекторов объединены и подключены к выходу Jd умножителя частоты, выход первого временного селектора соединен с третьим, четвертым, пятым и шестым неподвижными контактами первого переключателя, подвижный контакт которого соединен со счетным входом счетчика, разрядные выходы которого соединены с первым информационным входом накапливающего сумматора, выход старшего разряда счетчика соединен с первым неподвижным контактом третьего переключателя, подвижный контакт которого соединен с вторым информационным входом накапливающего сумматора, управ

1

Изобретение относится к специализированным средствам вычислительной техники и может быть использовано при создании приборов для измерения вероятностных характеристик фаз квазигармонических сигналов.

Известно устройство для измерения вероятностных характеристик, содержащее первый центрирующий фильтр, связанный через модульную схему с аналого-цифровым преобразователем, схемы совпадений, дискриминатор знака, реверсивный счетчик импульсов, схему сравнения, источник постоянного напряжения, второй центрирующий фильтр, соединенный с одним из двух входов схемы сравнения, узел регулируемой задержки,: временной селектор, делитель частоты, триггер и кнопочный выключатель, причем второй вход схемы сравнения связан с источником постоянного напряжения, а ее выход подключен к управляющему входу аналого-цифрового преобразователя и входу временного селектора через узел регулируемой задержки, выход которого также соединен с подвижным контактом первой линии трехлинейного двухполюсного переключателя, причем один неподвижный контакт этой

линии связан с выходом схемы сравнения , подвижный контакт второй линии переключателя соединен с входом схемы сравнения, первый неподвижный контакт подключен к входному зажиму

источника второго процесса, а второй неподвижный контакт соединен с вторым неподвижным контактом третьей линии, первый неподвижный контакт

которой подключен к входному зажиму источника первого случайного процесса, а ее подвижный контакт связан через однополюсный переключатель с входами модульной схемы и дискриминатора знака, выходы дискриминатора присоединены через двухлинейный переключатель к входам схем совпадений l ,

Однако устройство не позволяет

измерять вероятностные характеристики фазы случайного сигнала в широком диапазоне частот.

Наиболее близким по технической сущности к предлагаемому является

устройство для измерения вероятност-. ной характеристики случайной фазы, содержащее последовательно соединенные первый временной селектор и счетчик импульсов и последовательно соединенные второй временной селектор, 31 первый деЛитель частоты и триггер, а также два преобразователя фаза временной интервал (ПФВИ), формирователь импульсов, генератор импульсов, элемент задержки, регистр памяти, второй делитель частоты и элемен И, причем вход формирователя импульсов соединен с входом синхронизации устройства, а выход - с входом генератора импульсов, одним из входов обоих ПФВИ, установочным входом первого делителя частоты, входом второг делителя частоты и с одним из входов элемента И, два других входа которог подключены к выходу триггера и выходу второго делителя частоты соответственно, выход элемента И соединен с управляющим входом регистра памяти информационные входы которого подклю чены к разрядным выходам счетчика импульсов соответственно, другие вхо ды ПФВИ являются входами устройства, выходы первого и второго ПФВИ подклю чены к первым входам первого и второго временных селекторов соответственно, вторые входы которых подключены к выходу генератора импульсов, выход второго временного селектора соединен с другим входом триггера, а управляющий вход счетчика импульсов через элемент задержки подключен к выходу формирователя импульсов z Однако известное устройство позволяет измерять только одну вероятностную характеристику фазы квазигар монического сигнала, т.е. условное математическое ожидание. Целью изобретения является расширение класса решаемых задач. Указанная цель достигается тем, что в устройство для определения вероятностных характерист ик фазы случайного сигнала, содержащее элемент задержки, счетчик, первый преобразователь фаза - временной интервал, информационный вход которого является первым информационным входом устройства, выход первого преобразователя фаза - временной интервал соеди нен с первым входом первого временного селектора, второй преобразователь фаза - временной интервал, информационный вход которого является вторым информационным входом устройства, выход второго преобразователя фаза - временной интервал соединен с первым входом второго временного ;селектора, выход которого соединен 7-4 со счетным входом первого делителя частоты и нулевым входом триггера, единичный вход которого подключен к выходу первого делителя частоты, последовательно соединенные формирователь импульсов и второй делитель частоты, выход которого соединен с первым входом элемента И, вход формирователя импульсов является входом синхронизации устройства, введены первый, второй, третий и четвертый переключатели, накапливающий сумматор, умножитель частоты, блок памяти и блок регулируемой задержки, причем управляющий вход первого преобразователя .фаза - временной интервал объединен с входом умножителя частоты, входом элемента задержки,. первым и вторым неподвижными контактами первого переключателя, с первым и вторым неподвижными контактами второго переключателя, вторым входом элемента И, информационным входом блока регулируемой задержки, управляющим входом второго преобразователя фаза - временной интервал и подключен к выходу формирователя импульсов, управляющие входы первого и второго временных селекторов объединены и подключены к выходу умножителя частоты, выход первого временного селектора соединен с третьим, четвертым, пятым и шестым неподвижными контактами первого переключателя, подвижный контакт которого соединен со счетным входом счетчика, разрядные выходы которого соединены с первым информационным входом накапливающего сумматора, выход старшего разряда счетчика соединен с первым неподвижI. ным контактом третьего переключателя, подвижный контакт которого соединен с вторым информационным входом накапливающего сумматора, управляющий вход которого подключен к выходу элемента И, выход накапливающего сумматора соединен с информационным входом блока памяти, выход которого соединен с входом начальной первого делителя частоты, с первым управляющим входом блока регулируемой задержки и подключен к выходу элемента задержки, вход записи блока памяти соединен с подвижным контактом четвертого переключателя, первый неподвижный контакт которого соединен с вторым информационным входом блока регулируемой задержки и подключен к

выходу второго делителя частоты, выход триггера соединен с вторым управляющим входом блока регулируемой задержки, третьим и четвертым неподвижными контактами второго переключателя, пятый неподвижный контакт которого подключен к выходу первого делителя частоты, подвижный контакт второго переключателя соединен с третьим входом элемента И, шестой неподвижный контакт второго переключателя подключен к выходу блока регулируемой задержки.

Кроме того, блок регулирз емой задержки содержит регистр сдвига, кольцевой счетчик исхему сравнения, первая и вторая группы входов которой соединены с соответствующими разрядными выходами регистра сдвига и кольцевого счетчика, выход схемы сравнения является выходом блока, счетный вход регистра сдвига является первым информационным входом блока, первым и вторым управляющими входами которого являются соответственно вход сдвига- и вход записи регистра сдвига,, вход кольцевого счетчика является вторым информационным входом блока.

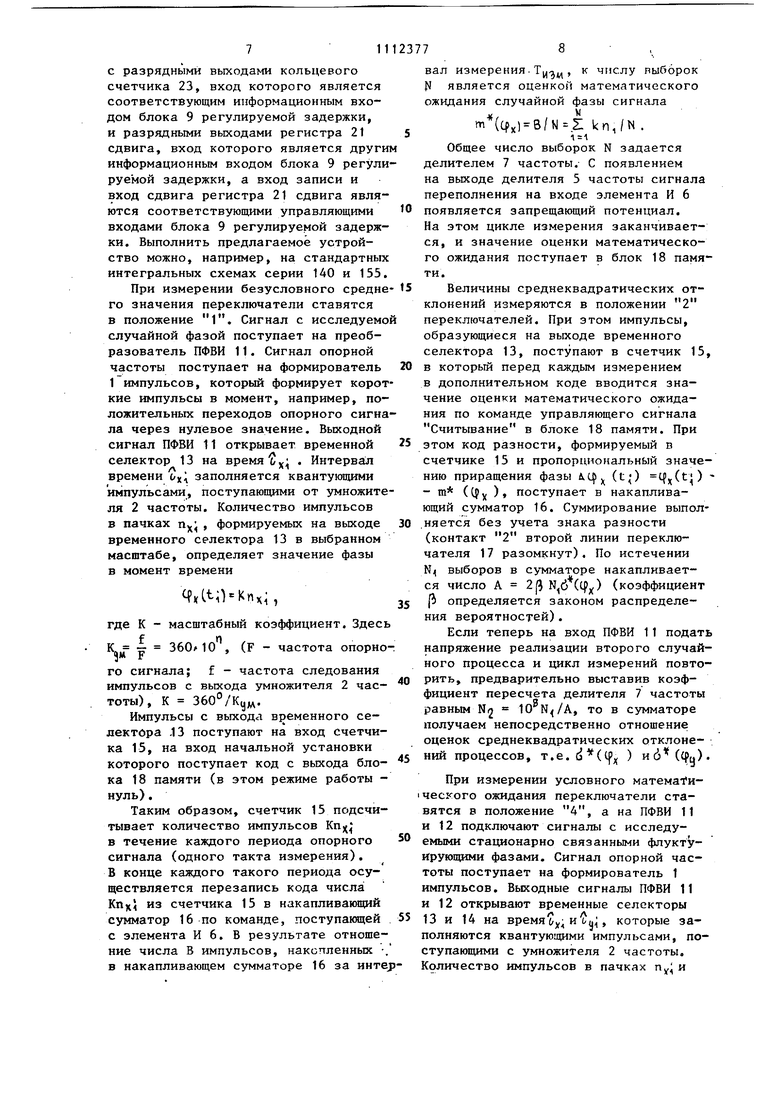

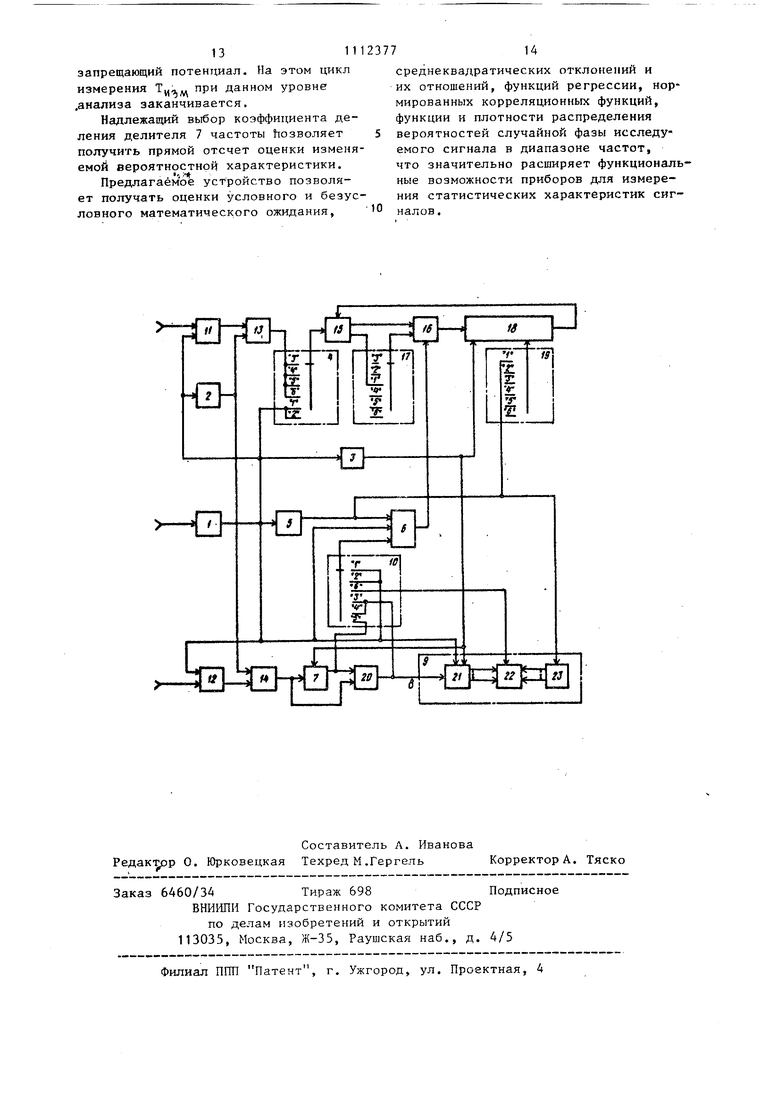

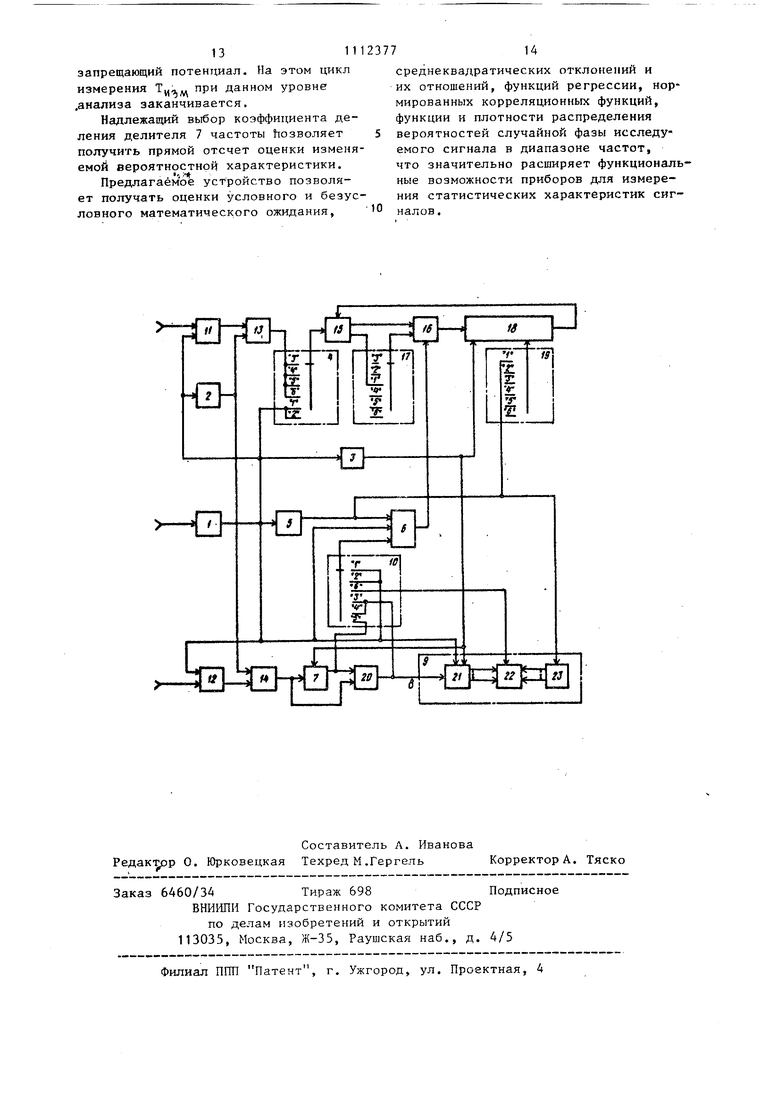

На чертеже приведена блок-схема предлагаемого устройства.

Устройство содержит формирователь 1 импульсов, умнбжитель 2 частоты, злемент 3 задержки, первый переключатель 4, первый делитель 5 частоты, элемент И 6, второй делитель 7 частоты, вход 8 регистра сдвига, блок 9 регулируемой задержки, второй переключатель 10, два преобразователя фаза - временной интервал 11 и 12, два временных селектора 13 и 14, счетчик 15, накапливающий сумматор 16, третий переключатель 17, блок 18 памяти, четвертый переключатель 19, триггер 20, регистр 21 сдвига блока 9 регулируемой задержки, схему 22 сравнения блока 9 и кольцевой счетчик 23 блока 9.

Вход формирователя 1 импульсов является входом синхронизации устройства. Выход формирователя 1 импульсов соединен с входом умножителя 2 частоты, вводом элемента 3 задержки, первым и BTopiS неподвижными контактами первого переключателя 4, с входом первого делителя 7 частоты и вторым входом элемента И 6. Установочный вход делителя 7 частоты соединен с

соответствующим управляющим входом блока 9 регулируемой задержки, первый информационный вход которого соединен с первым и вторым неподвижными контактагш второго переключателя 10, а также управляющими входами ПФВИ 11 и 12, информационные входы которых являются соответствующими информационными входами устройства. Выходы ПФВИ 11 и 12 соединены соответственно с информационными входами временных селекторов 13 и 14, управляющие входы которых соединены с выходом умножителя 2 частоты. Выход селектора 13 соединен с третьим, четвертым, пятым и шестым неподвижными контактами первого переключателя 4, подвижный контакт которого соединен с входом счетчика 15. Разрядные выходы счетчика 15 соединены с первым информационным входом накапливающего сумматора 16, причем старший разряд счетчика 15 соединен с первым неподвижным контактом третьего переключателя 17. Подвижный контакт третьего переключателя 17 соединен с вторым информационньм входом накапливающего сумматора 16. Выход накапливающего сумматора 16 соединен с входами блока 18 памяти, выход которого соединен с установочным входом счетчика 15. Вход записи блока 18 памяти соединен с подвижным контактом четвертого направления переключателя 19, первый неподвижный контакт которого соединен с выходом делителя 7 частоты и входом кольцевого счетчика 23 блока 9 регулируемой задержки. Вход считывания блока 18 памяти соединен с выходом элемента 3 задержки и информационным входом блока 9 регулируемой задержки, соответствующий управляющий вход которого соединен с выходом триггера 20, третьим и четвертым неподвижными контактами второго переключателя 10, пятый неподвижный контакт которого соединен с выходом первого, делителя 5 частоты. Блок 9 регулируемой задержки может быть вьшолнен различным образом 3J . В предлагаемом устройстве он содержит последовательно соединенные регистр 21 сдвига, схему 22 сравнения и кольцевой счетчик 23, причем выход схемы 22 сравнения является выходом блока 9 регулируемой задержки, а обе группы входов схемы 22 сравнения соединены соответственно с разрядными выходами кольцевого счетчика 23, вход которого является соответствующим информационным входом блока 9 регулируемой задержки, и разрядными выходами регистра 21 сдвига, вход которого является други информационным входом блока 9 регули руемой задержки, а вход записи и вход сдвига регистра 21 сдвига являются соответствующими управляющими входами блока 9 регулируемой задержки. Выполнить предлагаемое устройство можно, например, на стандартных интегральных схемах серии 140 и 155. При измерении безусловного средне го значения переключатели ставятся в положение 1. Сигнал с исследуемо случайной фазой поступает на преобразователь ПФВИ 11. Сигнал опорной частоты поступает на формирователь 1 импульсов, который формирует корот кие импульсы в момент, например, положительных переходов опорного сигна ла через нулевое значение. Выходной сигнал ПФВИ 11 открывает временной селектор 13 на время . Интервал времени c/xi заполняется квантующими импульсами, поступающими от умножите ля 2 частоты. Количество импульсов в пачках п, , формируемых на выходе временного селектора 13 в выбранном масштабе, определяет значение фазы в момент времени ) Кпх;, где К - масштабный коэффициент. Здесь К - , (F - частота опорно го сигнала; f - частота следования импульсов с выхода умножителя 2 частоты), К 360°/Куд. Импульсы с выхода временного селектора .13 поступают на вход счетчика 15, на вход начальной установки которого поступает код с выхода блока 18 памяти (в этом режиме работы нуль). Таким образом, счетчик 15 подсчитывает количество импульсов КП)( в течение каждого периода опорного сигнала (одного такта измерения). В конце каждого такого периода осуществляется перезапись кода числа Кпхч из счетчика 15 в накапливающий сумматор 16 по команде, поступающей с элемента И 6. Б результате отношение числа В импульсов, накопленных в накапливающем сумматоре 16 за инте вал измерения. ,, к числу пыборок N является оцанкой математического ожидания случайной фазы сигнала m(cp,) B/N 2: kn,/N. Общее число выборок N задается делителем 7 частоты.- С появлением на выходе делителя 5 частоты сигнала переполнения на входе элемента И 6 появляется запрещающий потенциал. На этом цикле измерения заканчивается, и значение оценки математического ожидания поступает в блок 18 памяти. Величины среднеквадратических отклонений измеряются в положении 2 переключателей. При этом импульсы, образующиеся на выходе временного селектора 13, поступают в счетчик 15, в который перед каждым измерением в дополнительном коде вводится значение оценки математического ожидания по команде управляющего сигнала Считывание в блоке 18 памяти. При этом код разности, формируемый в счетчике 15 и пропорциональный значению приращения фазы i-Cpjj (t;) 4i(t) - m ((py ), поступает в накапливающий сумматор 16. Суммирование выполняется без учета знака разности (контакт 2 второй линии переключателя 17 разомкнут). По истечении N выборов в сумматоре накапливается число А 2|3 (tfx (коэффициент fi определяется законом распределения вероятностей). Если теперь на вход ПФВИ 11 подать напряжение реализации второго случайного процесса и цикл измерений повторить, предварительно выставив коэффициент пересчета делителя 7 частоты равным N2 10 , то в сумматоре получаем непосредственно отношение оценок среднеквадратических отклонений процессов, T.e.d( ) и6(срц). При измерении условного математического ожидания переключатели ставятся в положение 4, а на ПФВИ 11 и 12 подключают сигналы с исследуемыми стационарно связанными флуктуирующими фазами. Сигнал опорной частоты поступает на формирователь 1 импульсов. Выходные сигналы ПФВИ 11 и 12 открывают временные селекторы 13 и 14 на время у , которые заполняются квантующими импульсами, поступающими с умножителя 2 частоты, Количество импульсов в пачках п и Пц в выбранном масштабе определяет значение фазь в моменты времени t,(tp Кп,, Hq),,(t.) Knyj . Импульсы с выхода временного селектора 13 поступают на вход счетчика 15, на вход начальной установки которого поступает с блока 18 памяти перед каждым тактом измерения код нуля (т.е. после записи кода, равного , в накапливающий сумматор 16 счетчика 15 сбрасывается в нуль). Импульсы с выхода временного селектора 14 поступают на нулевой вход триггера 20 непосредственно, а на единичный вход триггера 20 - через делитель 5 частоты. Коэффициент деления К делителя 5 частоты выбирае ся в соответствии с выбранным уровнем анализа, относительно которого определяется условное математическое ожидание. Если количество импульсов в пачке на выходе временного селектора 14 равно коэффициенту деления делителя 5 частоты (п„; . Kg-) , то на выходе (ritj г g/ 5 час готы появляется импуль делителя поступающий на вход триггера 20, на выходе которого формируется разрешающий потенциал. С приходом импульса с выхода формирователя 1 импульсов на выходе элемента И 6 появляется импульс, разрешающий поступление кода счетчика 15 в накапливающий сумматор. 16. Импульс с выхода элемента 3 задержки устанавливает в исходное (нулевое) положение делитель 5 часто ты и счетчик 15 сигналом с выхода бл ка 18 памяти. В исходное состояние триггер 20 возвращается первым импульсом умножителя частоты, проходящим через селектор 14 в следующем такте работы. Если Пи с: Kf, то на выходе делителя 5 частоты импульс не появляется и перезапись кода со счетчика 15 в накапливающий сумматор 16 не происхо дит. Счетчик 15 и делитель 5 частоты в конце цикла измерения устанавливаются в исходное (нулевое) положение. Если п„; 1, то на выходе делит ля 5 частотй появляется импульс, который приводит к тому, что на выходе триггера 20 появляется разрешающий потенциал для элемента И 6, однако импульс, порядковьй номер которого равен Пм,- К + 1, с выхода временного сел:екторЯ 14 возвращает триггер 20 в исходное состояние еще до появления очередного импульса с выхода элемента 3 задержки и, таким образом, в данном случае тоже перезапись кода со счетчика 15 в накапливающий сумматор 16 не происходит. Отношение числа импульсов, накопленных в накапливающем сумматоре 16 за интервал измерения, к числу выборок Кл пропорционально оценке определяемого условного математического ожиданияу, f t xH l4y-C l-CfNc .- Изменяя коэффициент деления делителя 5 частоты, можно измерить функцию регрессии случайной фазы сигнала. При измерении функции корреляции переключатели находятся в положении 3, в результате чего включается блок 9 регулируемой задержки. Исследуемый сигнал x(t) подключается к входам обоих ПФВИ 11 и 12, а в делителе 5 частоты устанавливается коэффициент деления К в соответствии с выбранным уровнем анализа, оптималь ное в смысле минимума продолжительности измерения значение для нормального закона распределения случайной фазы равно т(ср) -1,4l6(tp). В блоке 9 регулируемой задержки устанавливается начальное значение аргумента функции корреляции р ( ) . Устройство .работает принципиально так же, как и при измерении условного математического ожидания. Но .поскольку перезапись кода со счетчика 15 в накапливающий сумматор 16 производится только при наличии сигнала с выхода схемы 22 сравнения на третьем входе элемента И 6, то устройство определяет условное среднее значение фазы исследуемого сигнала C..(t +u) относительно моментов выполнения условийц) (t) Кп., К. К,-Центрирование значений фазы ис ::ледуемого сигнала x(t) выполняется следующим образом. Перед.каждым измерением в счетчике 15 устанавливается код среднего значения, как при измерении среднеквадратического отклонения, но суммирование в накапливающем сумматоре 16 выполняется с учетом знака кода Д(0 ( + ) в соответствии с подготовительным управляющим сигналом на входе накаплива1111ющегосумматора 16 с подвижного кон- такта третьего переключателя 17. Блок 9 регулируемой задержки работает следующим образом. В зависимости от значения сигнала с триггера 20 (1 или О) на втором управляющем входе регистра 21 сдвига записывается 1 или О с приходом на второй его информационный вход импульса с формирователя 1 импульсов. Если код в регистре 21 сдвига равен коду, записанному в кольцевом счетчике 23, то на выходе схемы 22 сравнения появляется импульс, который разрешает перезапись кода счетчи ка 15 в накапливающий сумматор 16. Через время импульс с элемента 3 задержки производит перемещение запи санной информации в регистре 21 сдви га на один разряд. Сигнал с выхода делителя 7 частоты (через интервал времени Tj ) продвигает единицу в кольцевом счетчике 23 на один разряд, тем самым изменяя значение аргу мента при определении функции корреляции. Отношение числа L импульсов, накопленных в накапливающем сумматоре 16 за интервал измерения Ту, , к числу выборок N пропорционально оценке нормированной функции корреля ции исследуемой случайной фазы Cfi(t) при данном значении с . Если на входы устройства в этом режиме измерения подключить два сигнала x(t) и y(t) со стационарно связанными флуктуирующими фазами, то за интервал измерения Тиу11,получаем оцен ку произведения нормированной функции взаимной корреляции на отношение среднеквадратических отклонений первого, и второго случайных процессов (t) и Cptj (t) ч ... . ч. . (tl LВ первом положении первого пере-клк)чателя 4 получаем оценку плотности вероятности распределения случайной фазы сигнала. При этом сигнал с исследуемой случайной фазой подклю чается на вход ПФВИ 12. Формируемые на выходе временного селектора 14 пачки импульсов в выбранном масштабе определяют значение фазы в момент времени t qlfKi i x,. Импульсы с выхода временного селектора 14 поступают на нулевой вход триггера 20 непосредственно, а на единичный вход триггера 20 - через депитель 5 частоты. Коэффициент деления делителя 5 частоты выбирается в соответствии с выбранным уровнем анализа плотности вероятности. Интервал анализа ДЦ) равняется интервалу дискретизации случайной фазы,т.е. iC 360°F/1 .. Дальше измерение выполняется так же, как и при определении условного математического ожидания (или функции регрессии) за исключением того, что импульсы на вход счетчика 15 поступают с формирователя 1 импульсов (первое положение первого переключателя 4). Таким образом, накапливанлций сум- матор 16 фиксирует число h наступления события Cfx-- (t)cpv-i-itf , где KKgrqy(t) Kn.. Через интервал времени Т,„ в накапливающем сумматоре 16 формируется код, пропорциональный опенке плотности вероятности случайной фазы сигнала при заданном уровне анализа /.. х 1 h h N, Для получения оценки функции подвижный контакт третьего распределения переключателя ставится в положение 6. Устройство работает в этом режиме аналогично, только перезапись кода со счетчика 15 в накагшивающий сумматор 16 вьтолняется по команде с элемента И 6 при появлении сигнала переполнения на выходе делителя 5 частоты. За время Т, в накопителе формируется код, пропорциональный оценке функции, Р,(И-1Г-, ё где d - число импульсов, гоответствующих случаям (t) Cf d. Общее число выборок N во нгех режимах измерения задается делителем 7 частоты. С появлением из вихоле елителя 7 частоты сигнал;) переполнеия на входе элемента И 6 поянплотся 1311 запрещающий потенциал. На этом цикл измерения T, при данном уровне .анализа заканчивается. Надлежащий вьйор коэффициента деления делителя 7 частоты Ьозволяет получить прямой отсчет оценки изменя емой вероятностной характеристики. Предлагаемое устройство позволяет получать оценки условного и безус ловного математического ожидания. среднеквадратических отклонений и их отношений, функций регрессии, нормированных корреляционных функций, функции и плотности распределения вероятностей случайной фазы исследуемого сигнала в диапазоне частот, что значительно расширяет функциональные возможности приборов для измерения статистических характеристик сигналов ,

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| УСТРОЙСТВО для ИЗМЕРЕНИЯ ВЕРОЯТНОСТНЫХ ХАРАКТЕРИСТИК СЛУЧАЙНЫХ ПРОЦЕССОВ | 0 |

|

SU285368A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппаратурное определение характеристик случайных процессов | |||

| М., Энергия, 1972. | |||

Авторы

Даты

1984-09-07—Публикация

1982-12-27—Подача