Изобретение относится к электротехнике, а именно к устройствам аварийного или резервного электроснабжения.

Известно устройство, содержащее источник питания, подключенный к входу двух стабилизаторов напряжения, выход первого из которых подключен к входу первой схемы сравнения напряжения, выход второго стабилизатора подключен к входу второй схемы сравнения напряжения. Выход первой схемы сравнения напряжения управляет первым ключом, отключающим цепь нагрузки от выхода первого стабилизатора напряжения при отказах его компонентов и подключающим ее к выходу второго стабилизатора напряжения. Выход второй схемы сравнения напряжения управляет вторым ключом, отключающим цепь нагрузки от выхода второго стабилизатора напряжения при отказах его компонентов.

Однако в известном устройстве оба резервированных источника питания постоянно подключены к первичному источнику питания и вырабатывают свой ресурс, что является недостатком данного устройства.

Наиболее близким по технической сущности к предлагаемому устройству является выбранное в качестве прототипа устройство для резервированного питания, содержащее источник питания и две параллельные цепи, каждая из которых состоит из первого электронного ключа, включенного между источником питания и входом стабилизатора напряжения, выход которого подключен через схему сравнения напряжения к управляющему входу второго электронного ключа, включенного между выходом

Х|

00

ел

стабилизатора и нагрузкой, Второй выход схемы сравнения напряжения соединен с первым управляющим входом первого элек- тронного ключа. Второй управляющий вход первого электронного ключа соединен с первым выходом схемы сравнения напряжения параллельной цепи. Напряжение питания от источника питания через первые электронные ключи поступает на оба стабилизатора напряжения. Как только напряжение на выходе стабилизатора одной из двух параллельных цепей достигает требуемого уровня, схема сравнения напряжения этой цепи выдает сигнал на управляющий вход второго электронного ключа, который подключает цепь нагрузки к выходу стабилизатора, одновременно сигнал с выхода схемы сравнения напряжения поступает на второй управляющий вход первого электронного ключа другой параллельной цепи и размыкает его, отключая стабилизатор этой цепи от первичного источника. Таким образом, питание нагрузки осуществляется от одного стабилизатора, другой при этом обесточен.

Однако это устройство характеризуется невысокой надежностью, вызванной следующими недостатками.

Вследствие неиндентичности параметров элементов стабилизаторов и схем срав- нениянапряжениявозможно

преимущественное включение одного из двух стабилизаторов. Таким образом, ресурс стабилизаторов вырабатывается неравномерно. Другой недостаток заключается в том, что в случае уменьшения напряжения на выходе стабилизатора ниже установленной нормы не происходит немедленного отключения аварийного стабилизатора, а при возрастании напряжения на выходе стабилизатора выше максимально допустимого значения не происходит немедленного отключения цепи нагрузки от выхода отказавшего стабилизатора. Таким образом, данное устройство невозможно использовать для питания нагрузки, чувствительной к повышению питающего напряжения, что сужает область его применения. К недостаткам устройства следует отнести и отсутствие блокировки от повторного включения аварийного стабилизатора.

Целью изобретения является повышение надежности в работе устройства для резервированного питания.

Указанная цель достигается тем, что в устройство для резервированного питания, содержащее основной источник питания, подключенный через первый и второй электронные ключи соответственно к входу первого и второго стабилизатора напряжения, выход первого стабилизатора напряжения

подключен к входу первого элемента сравнения напряжения и к входу третьего электронного ключа, выход которого подключен к цепи нагрузки, а выход второго стабилизатора напряжения соединен с входом второго элемента сравнения напряжения и с входом четвертого электронного ключа, выход которого подключен к клеммам для подключения нагрузки, введен блок управления

0 включением, состоящий из первого и второго логических элементов И, входы которых соединены соответственно с выходами первого и второго элементов сравнения напряжения, а выходы - соответственно с

5 управляющими входами третьего и четвертого электронных ключей и первыми входами первого и второго логических элементов ИЛИ, другие входы которых объединены и соединены с выходами реле времени. Вход

0 реле времени соединен с выходом третьего логического элемента И, с четырьмя входами, первый и второй входы которого соединены соответственно с инверсными выходами первого и второго одновибрато5 ров, третий вход третьего элемента И соеди- нен с выходами двухпорогового компаратора, а четвертый вход- с выходом элемента установки исходного состояния. Входы одновибраторов соединены с инвер0 сными выходами первого и второго RS-триг- геров соответственно, S-входы которых соединены соответственно с выходами первого и второго логических элементов ИЛИ, а R-входы, также как и R-вход третьего RS5 триггера, соединены с выходом элемента установки исходного состояния.

Первый вход компаратора соединен с выходом вспомогательного третьего стабилизатора напряжения и с анодом первого

0 диода. Вход вспомогательного стабилизатора напряжения соединен с выходом источника питания, второй вход компаратора соединен с источником опорного напряжения, катод первого диода соединен с выхо5 дом элемента установки исходного состояния, с первой шиной питания всех логических элементов блока и с катодом второго диода, анод которого соединен через выключатель с положительным полюсом

0 вспомогательного источника питания.

Отрицательный полюс вспомогательного источника соединен с второй шиной питания элементов блока, первые входы четвертого и пятого логических элементов И

5 соединены с выходом компаратора, а вторые входы этих элементов И соединены с инверсными выходами первого и второго RS-триггеров соответственно, а также с первым и вторым входами шестого логического элемента И, выход которого соединен с Sвходом третьего RS-триггера, прямой выход которого соединен с первыми входами третьего и четвертого логических элементов ИЛИ, вторые входы которых соединены соответственно с прямым и инверсным выходами D-триггера, D-вход которого соединен с его же инверсным выходом, а С-вход через логический элемент НЕ связан с выходом компаратора. Выход третьего логического элемента ИЛИ соединен с первым входом седьмого логического элемента И, второй вход которого соединен с выходом четвертого логического элемента И, а выход - с управляющим входоя первого электронного ключа. Выход четвертого логического элемента ИЛИ соединен с первым входом восьмого логического элемента И, второй вход которого соединен с выходом пятого логического элемента И, а выход - с управляющим входом третьего электронного ключа, при этом электронные ключи выполнены замыкающими.

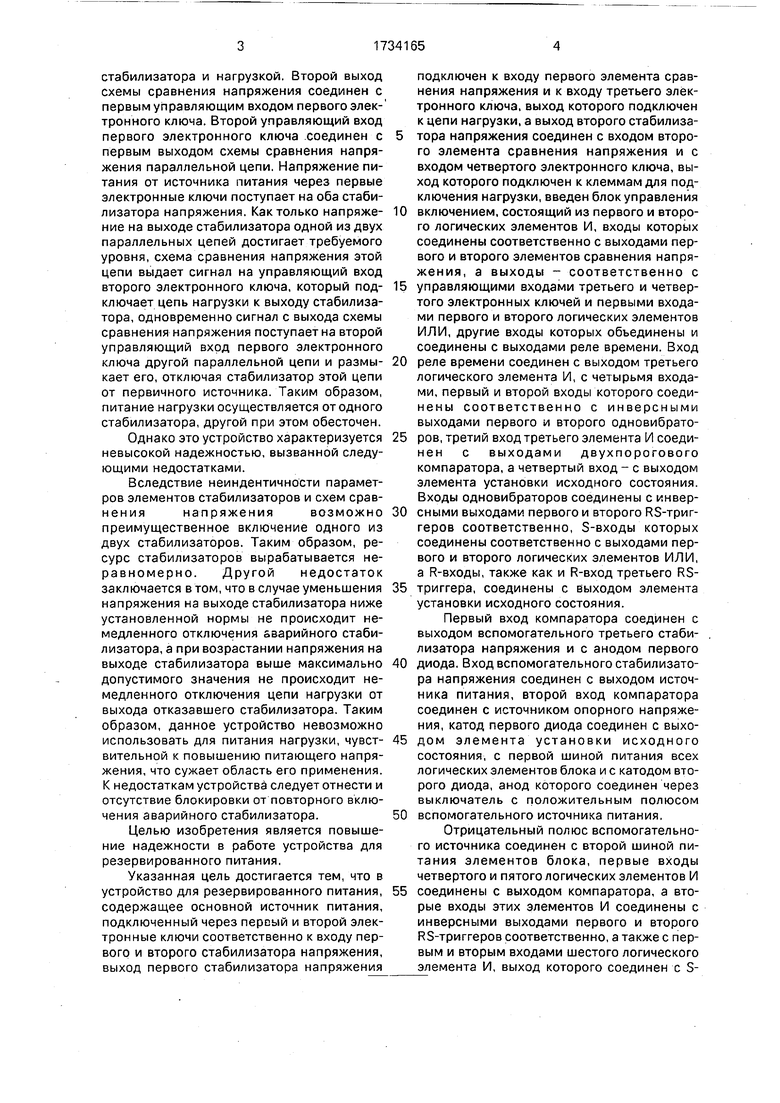

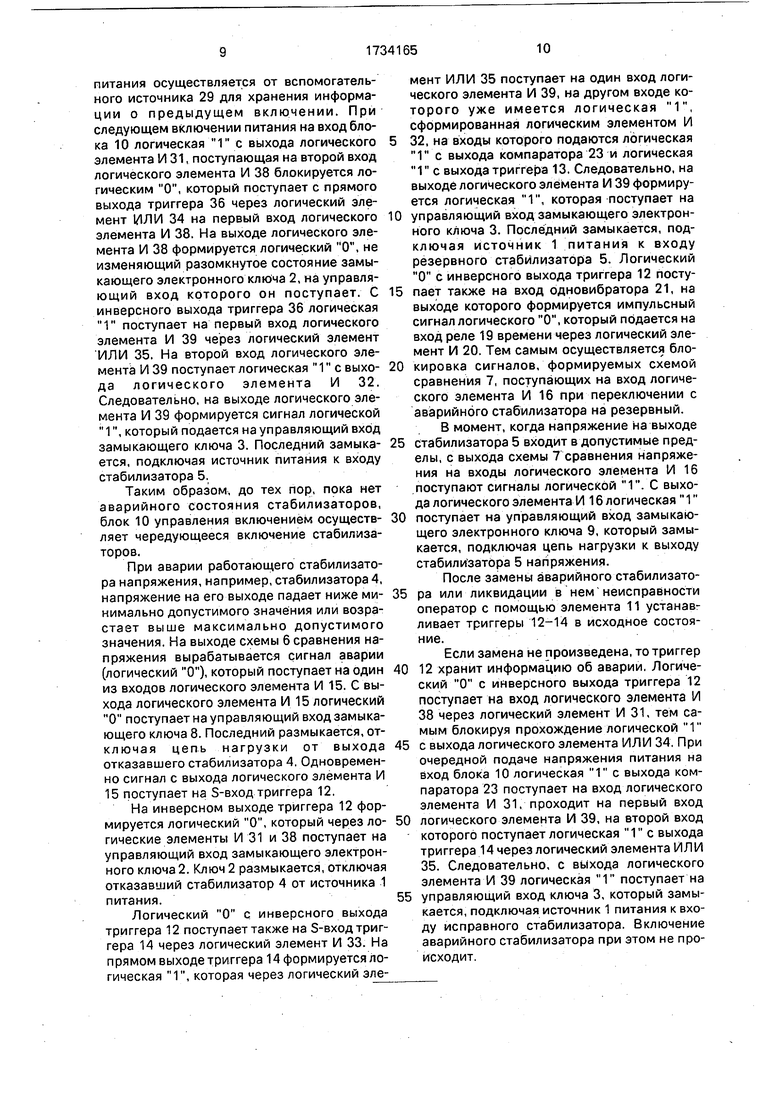

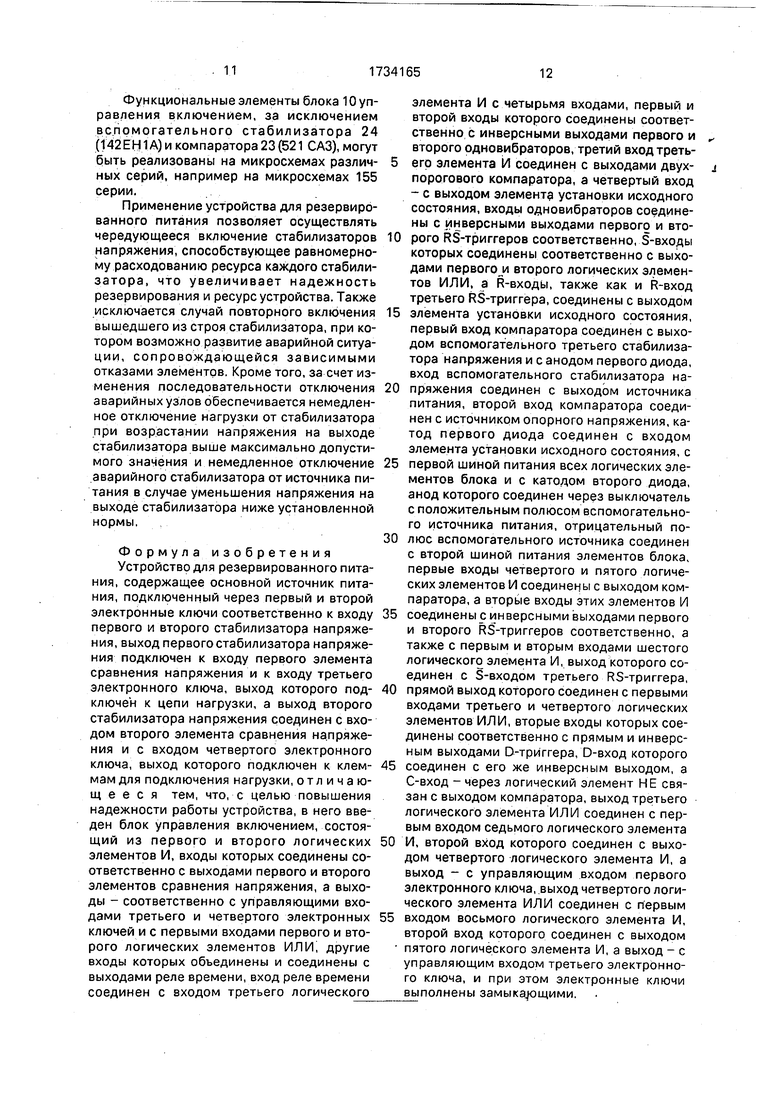

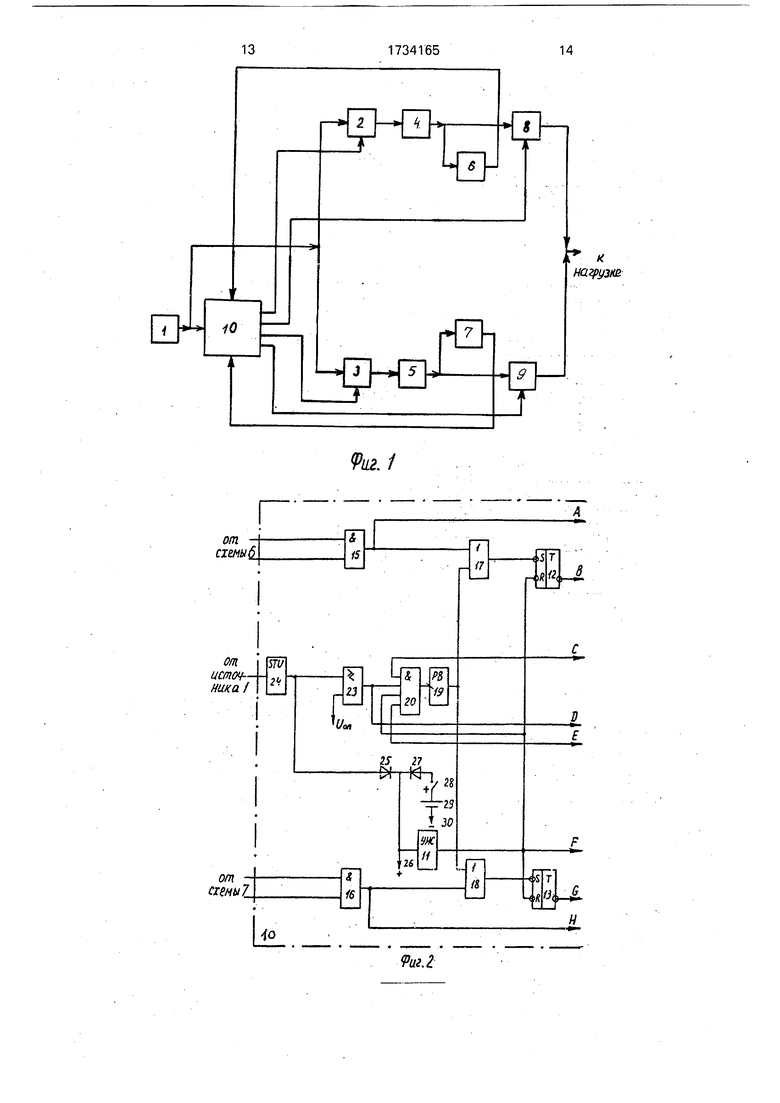

На фиг.1 представлена блок-схема устройства для резервированшго питания; на фиг.2 и 3 - пример выполнеттая блока управления включением,

Устройство для резервированного питания (фиг.1) содержит источник 1 питания, первый и третий замыкающие электронные ключи 2 и 3, стабилизаторы 4 и 5 напряжения, схемы 6 и 7 сравнения напряжения, второй и четвертый замыкающие электронные ключи 8 и 9, блок 10 управления включением.

Замыкающий электронный ключ 2 включен между источником 1 питания и входом стабилизатора 4, а замыкающий электронный ключ 3 между источником 1 питания и входом стабилизатора 5 напряжения. Выход стабилизатора 4 подключен к входу схемы 6 сравнения напряжения и к входу замыкающего электронного ключа 8, выход которого подключен к цепи нагрузки, а выход стабилизатора 5 подключен к входу схемы 7 сравнения напряжения и к входу замыкающего электронного ключа 9, выход которого подключен к цепи нагрузки.

Блок 10 управления включением может быть выполнен, например, как это показано на фиг.2 и 3.

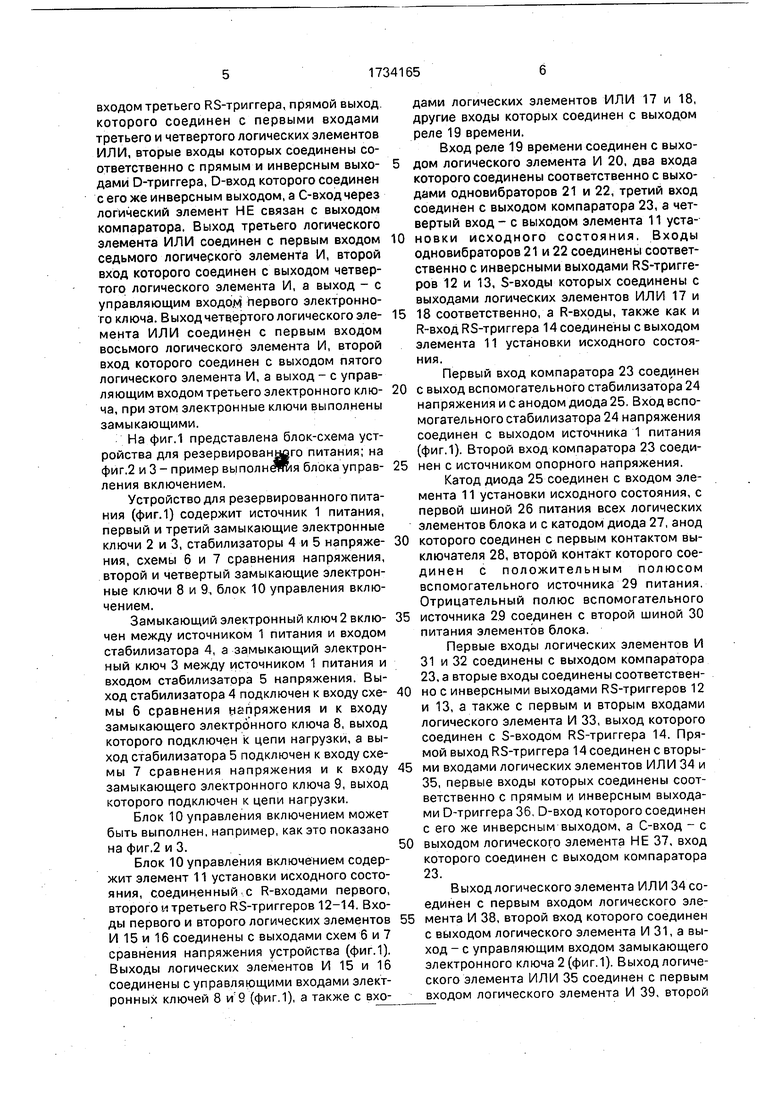

Блок 10 управления включением содержит элемент 11 установки исходного состояния, соединенный с R-входами первого, второго и третьего RS-триггеров 12-14. Входы первого и второго логических элементов И 15 и 16 соединены с выходами схем 6 и 7 сравнения напряжения устройства (фиг.1). Выходы логических элементов И 15 и 16 соединены с управляющими входами электронных ключей 8 и 9 (фиг.1), а также с входами логических элементов ИЛИ 17 и 18, другие входы которых соединен с выходом реле 19 времени.

Вход реле 19 времени соединен с выходом логического элемента И 20, два входа которого соединены соответственно с выходами одновибраторов 21 и 22, третий вход соединен с выходом компаратора 23, а четвертый вход - с выходом элемента 11 уста0 новки исходного состояния, Входы одновибраторов 21 и 22 соединены соответственно с инверсными выходами RS-триггеров 12 и 13, S-входы которых соединены с выходами логических элементов ИЛИ 17 и

5 18 соответственно, а R-входы, также как и R-вход RS-триггера 14 соединены с выходом элемента 11 установки исходного состояния.

Первый вход компаратора 23 соединен

0 с выход вспомогательного стабилизатора 24 напряжения и с анодом диода 25. Вход вспомогательного стабилизатора 24 напряжения соединен с выходом источника 1 питания (фиг.1). Второй вход компаратора 23 соеди5 нен с источником опорного напряжения.

Катод диода 25 соединен с входом элемента 11 установки исходного состояния, с первой шиной 26 питания всех логических элементов блока и с катодом диода 27, анод

0 которого соединен с первым контактом выключателя 28, второй контакт которого соединен с положительным полюсом вспомогательного источника 29 питания. Отрицательный полюс вспомогательного

5 источника 29 соединен с второй шиной 30 питания элементов блока.

Первые входы логических элементов И 31 и 32 соединены с выходом компаратора 23, а вторые входы соединены соответствен0 но с инверсными выходами RS-триггеров 12 и 13, а также с первым и вторым входами логического элемента И 33, выход которого соединен с S-входом RS-триггера 14. Прямой выход RS-триггера 14 соединен с вторы5 ми входами логических элементов ИЛИ 34 и 35, первые входы которых соединены соответственно с прямым и инверсным выходами D-триггера 36 D-вход которого соединен с его же инверсным выходом, а С-вход - с

0 выходом логического элемента НЕ 37, вход которого соединен с выходом компаратора 23.

Выход логического элемента ИЛИ 34 соединен с первым входом логического эле5 мента И 38, второй вход которого соединен с выходом логического элемента И 31, а выход - с управляющим входом замыкающего электронного ключа 2 (фиг.1). Выход логического элемента ИЛИ 35 соединен с первым входом логического элемента И 39, второй

вход которого соединен с выходом логического элемента И 32, а выход - с управляющим входом замыкающего электронного ключа 3 (фиг.1).

Устройство работает следующим обра- зом.

При включении питания блока 10 выключателем 28 через развязывающий диод 27 осуществляется питание элементов блока 10 управления включением, а также на- пряжение питания подается на вход элемента 11 установки исходного состояния, на выходе которого формируется импульс, поступающий на R-входы триггеров 12-14. Последние устанавливаются в нуле- вое состояние.

При подаче напряжения от источника 1 питания на вход блока 10 на выходе вспомогательного стабилизатора 24 появляется напряжение, которое через развязывающий диод 25 поступает для питания элементов блока 10, при этом диод 27 закрывается, и потребление тока от вспомогательного источника 29 прекращается. При достижении этим напряжением величины, равной вели- чине опорного напряжения, на выходе компаратора 23 формируется логическая 1, поступающая на входы логических элементов И 20, 31, 32, элемента НЕ 37. На вторые входы элементов 31 и 32 поступают логиче- ские 1 с инверсных выходов триггеров 12 и 13. Логический О, поступающий на С- вход триггера 36 с выхода элемента НЕ 37 не изменяет предыдущего состояния этого триггера. На прямом выходе триггера 36 может быть логический О или 1, например логическая 1, которая поступает на первый вход логического элемента ИЛИ 34, на второй вход которого поступает логический О с триггера 14.

С выхода логического элемента ИЛИ 34 логическая 1 поступает на первый вход логического элемента И 38. На второй вход логического элемента И 38 поступает логическая 1 с выхода логического элемента И 31. Следовательно, на выходе логического элемента И 38 формируется сигнал логической 1, который подается на управляющий вход замыкающего ключа 2. Ключ 2 замыкается, подключая источник питания к входу стабилизатора 4 (фиг.1), С инверсного выхода триггера 36 логический О подается на первый вход логического элемента ИЛИ 35. На второй вход логического элемента ИЛИ 35 подается логическая 1 с выхода тригге- ра 14, на S-вход которого поступает логическая 1 с выхода логического элемента И 33, не изменяющая предыдущего состояния триггера. С выхода логического элемента ИЛИ 35 логический О поступает на первый

вход логического элемента И 39, на второй вход которого поступает логическая 1 с выхода логического элемента И 32.

На выходе логического элемента И 39 формируется логический О, не изменяющий разомкнутое состояние замыкающего электронного ключа 3, на управляющий вход которого он поступает. Сигнал логического О от элемента 11 поступает также через логический элемент И 20 на вход реле 19 времени. На его выходе в течение заданного времени формируется логическая 1, которая поступает на входы логических элементов ИЛИ 17 и 18.

Таким образом, сигналы с выходов логических элементов И 15 и 16 не смогут поступить на S-входы триггеров 12 и 13. Через заданный временный интервал реле 19 времени выдает логический О на входы логических элементов ИЛИ 17 и 18. Этот интервал необходим для вхождения выходного напряжения стабилизатора в поле допуска при включении. Логический О на входе логического элемента ИЛИ 17 разрешает прохождение сигнала с выхода логического элемента И 15, на вход которого поступают сигналы логической 1 с выхода схемы 6 сравнения, вырабатываемые схемой после установления на выходе стабилизатора 4 напряжения требуемого уровня. Логическая 1 на выходе логического элемента И 15 подается на управляющий вход замыкающего электронного ключа 8, который замыкается, подключая цепь нагрузки к выходу стабилизатора 4. При включении напряжения питания на входе блока 10 диод 27 открывается, а диод 25 закрывается и напряжение питания от вспомогательного источника 29 не поступает на первый вход компаратора 23. На выходе компаратора 23 формируется логический О, который через логические элементы И 31 и 38 подается на управляющий вход замыкающего электронного ключа 2. Последний размыкается, отключая стабилизатор 4 от источника 1 питания.

Логический О с выхода компаратора 23 подается также на вход логического элемента НЕ 37, на выходе которого формируется логическая 1, под передний фронт которой триггер 36 меняет состояние на противоположное. Логический О, подаваемый на вход реле 19 времени через логический элемент И 20, формирует в течение заданного времени на выходе реле 19 логическую 1, которая блокирует прохождение логического О с выхода логического элемента И 15 при включении напряжения питания. Питание логических элементов блока 10 управления включением при выключении

питания осуществляется от вспомогательного источника 29 для хранения информации о предыдущем включении. При следующем включении питания на вход блока 10 логическая 1 с выхода логического элемента 1/131, поступающая на второй вход логического элемента И 38 блокируется логическим О, который поступает с прямого выхода триггера 36 через логический элемент ИЛИ 34 на первый вход логического элемента И 38. На выходе логического элемента И 38 формируется логический О, не изменяющий разомкнутое состояние замыкающего электронного ключа 2, на управляющий вход которого он поступает. С инверсного выхода триггера 36 логическая 1 поступает на первый вход логического элемента И 39 через логический элемент ИЛИ 35. На второй вход логического элемента И 39 поступает логическая 1 с выхода логического элемента И 32. Следовательно, на выходе логического элемента И 39 формируется сигнал логической 1, который подается на управляющий вход замыкающего ключа 3. Последний замыкается, подключая источник питания к входу стабилизатора 5.

Таким образом, до тех пор, пока нет аварийного состояния стабилизаторов, блок 10 управления включением осуществляет чередующееся включение стабилизаторов.

При аварии работающего стабилизатора напряжения, например, стабилизатора 4, напряжение на его выходе падает ниже минимально допустимого значения или возрастает выше максимально допустимого значения. На выходе схемы 6 сравнения напряжения вырабатывается сигнал аварии (логический О), который поступает на один из входов логического элемента И 15. С выхода логического элемента И 15 логический О поступает на управляющий вход замыкающего ключа 8. Последний размыкается, от- ключая цепь нагрузки от выхода отказавшего стабилизатора 4. Одновременно сигнал с выхода логического элемента И 15 поступает на S-вход триггера 12.

На инверсном выходе триггера 12 формируется логический О, который через логические элементы И 31 и 38 поступает на управляющий вход замыкающего электронного ключа 2. Ключ 2 размыкается, отключая отказавший стабилизатор 4 от источника 1 питания.

Логический О с инверсного выхода триггера 12 поступает также на S-вход триггера 14 через логический элемент И 33. На прямом выходе триггера 14 формируется логическая 1, которая через логический элемент ИЛИ 35 поступает на один вход логического элемента И 39, на другом входе которого уже имеется логическая 1, сформированная логическим элементом И

32, на входы которого подаются логическая 1 с выхода компаратора 23 и логическая 1 с выхода триггера 13. Следовательно, на выходе логического элемента И 39 формируется логическая 1, которая поступает на

управляющий вход замыкающего электронного ключа 3. Последний замыкается, подключая источник 1 питания к входу резервного стабилизатора 5. Логический О с инверсного выхода триггера 12 поступает также на вход одновибратора 21, на выходе которого формируется импульсный сигнал логического О, который подается на вход реле 19 времени через логический элемент И 20. Тем самым осуществляется блокировка сигналов, формируемых схемой сравнения 7, поступающих на вход логического элемента И 16 при переключении с аварийного стабилизатора на резервный. В момент, когда напряжение на выходе

стабилизатора 5 входит в допустимые пределы, с выхода схемы 7 сравнения напряжения на входы логического элемента И 16 поступают сигналы логической 1. С выхода логического элемента И 16 логическая 1

поступает на управляющий вход замыкающего электронного ключа 9, который замыкается, подключая цепь нагрузки к выходу стабилизатора 5 напряжения.

После замены аварийного стабилизатора или ликвидации в нем неисправности оператор с помощью элемента 11 устанавливает триггеры 12-14 в исходное состояние.

Если замена не произведена, то триггер

12 хранит информацию об аварии, Логический О с инверсного выхода триггера 12 поступает на вход логического элемента И 38 через логический элемент И 31, тем самым блокируя прохождение логической 1

с выхода логического элемента ИЛИ 34. При очередной подаче напряжения питания на вход блока 10 логическая 1 с выхода компаратора 23 поступает на вход логического элемента И 31, проходит на первый вход

логического элемента И 39, на второй вход которого поступает логическая 1 с выхода триггера 14 через логический элемента ИЛ И 35. Следовательно, с выхода логического элемента И 39 логическая 1 поступает на

управляющий вход ключа 3, который замыкается, подключая источник 1 питания к входу исправного стабилизатора. Включение аварийного стабилизатора при этом не происходит

Функциональные элементы блока 10 управления включением, за исключением вспомогательного стабилизатора 24 (142ЕН1 А) и компаратора 23 (521 САЗ), могут быть реализованы на микросхемах различных серий, например на микросхемах 155 серии.

Применение устройства для резервированного питания позволяет осуществлять чередующееся включение стабилизаторов напряжения, способствующее равномерному расходованию ресурса каждого стабилизатора, что увеличивает надежность резервирования и ресурс устройства. Также исключается случай повторного включения вышедшего из строя стабилизатора, при котором возможно развитие аварийной ситуации, сопровождающейся зависимыми отказами элементов. Кроме того, за счет изменения последовательности отключения аварийных узлов обеспечивается немедленное отключение нагрузки от стабилизатора при возрастании напряжения на выходе стабилизатора выше максимально допустимого значения и немедленное отключение аварийного стабилизатора от источника питания в случае уменьшения напряжения на выходе стабилизатора ниже установленной нормы,

Формула изобретения Устройство для резервированного питания, содержащее основной источник питания, подключенный через первый и второй электронные ключи соответственно к входу первого и второго стабилизатора напряжения, выход первого стабилизатора напряжения подключен к входу первого элемента сравнения напряжения и к входу третьего электронного ключа, выход которого подключен к цепи нагрузки, а выход второго стабилизатора напряжения соединен с входом второго элемента сравнения напряжения и с входом четвертого электронного ключа, выход которого подключен к клеммам для подключения нагрузки, отличающееся тем, что, с целью повышения надежности работы устройства, в него введен блок управления включением, состоящий из первого и второго логических элементов И, входы которых соединены соответственно с выходами первого и второго элементов сравнения напряжения, а выходы - соответственно с управляющими входами третьего и четвертого электронных ключей и с первыми входами первого и второго логических элементов ИЛИ, другие входы которых объединены и соединены с выходами реле времени, вход реле времени соединен с входом третьего логического

элемента И с четырьмя входами, первый и второй входы которого соединены соответственно с инверсными выходами первого и ,, второго одновибраторов, третий вход третьего элемента И соединен с выходами двух- j порогового компаратора, а четвертый вход - с выходом элемента установки исходного состояния, входы одновибраторов соединены с инверсными выходами первого и вто0 рого RS-триггеров соответственно, S-входы которых соединены соответственно с выходами первого и второго логических элементов ИЛИ, а R-входы, также как и R-вход третьего RS-триггера, соединены с выходом

5 элемента установки исходного состояния, первый вход компаратора соединен с выходом вспомогательного третьего стабилизатора напряжения и с анодом первого диода, вход вспомогательного стабилизатора на0 пряжения соединен с выходом источника питания, второй вход компаратора соединен с источником опорного напряжения, катод первого диода соединен с входом элемента установки исходного состояния, с

5 первой шиной питания всех логических элементов блока и с катодом второго диода, анод которого соединен через выключатель с положительным полюсом вспомогательного источника питания, отрицательный по0 люс вспомогательного источника соединен с второй шиной питания элементов блока, первые входы четвертого и пятого логических элементов И соединены с выходом компаратора, а вторые входы этих элементов И

5 соединены с инверсными выходами первого и второго RS-триггеров соответственно, а также с первым и вторым входами шестого логического элемента И, выход которого соединен с S-входом третьего RS-триггера,

0 прямой выход которого соединен с первыми входами третьего и четвертого логических элементов ИЛИ, вторые входы которых соединены соответственно с прямым и инверсным выходами D-триггера, D-вход которого

5 соединен с его же инверсным выходом, а С-вход - через логический элемент НЕ связан с выходом компаратора, выход третьего логического элемента ИЛИ соединен с первым входом седьмого логического элемента

0 И, второй вход которого соединен с выходом четвертого логического элемента И, а выход - с управляющим входом первого электронного ключа, выход четвертого логического элемента ИЛИ соединен с первым

5 входом восьмого логического элемента И, второй вход которого соединен с выходом пятого логического элемента И, а выход - с управляющим входом третьего электронного ключа, и при этом электронные ключи выполнены замыкающими.

к нагрузке

| название | год | авторы | номер документа |

|---|---|---|---|

| СТАБИЛИЗАТОР ПЕРЕМЕННОГО НАПРЯЖЕНИЯ (ВАРИАНТЫ) | 1999 |

|

RU2158954C1 |

| Импульсный стабилизатор постоянного напряжения | 1987 |

|

SU1471181A1 |

| Импульсный понижающий стабилизатор постоянного напряжения | 1990 |

|

SU1786477A1 |

| Источник вторичного электропитания для сети постоянного напряжения | 1990 |

|

SU1786476A1 |

| Импульсный стабилизатор постоянного напряжения с программным управлением | 1987 |

|

SU1458865A1 |

| ИМПУЛЬСНЫЙ СТАБИЛИЗАТОР ПОСТОЯННОГО НАПРЯЖЕНИЯ | 1992 |

|

RU2051404C1 |

| УСТРОЙСТВО ЗАЩИТЫ СВЕТОДИОДОВ ОТ ПЕРЕГРУЗОК | 2013 |

|

RU2572378C2 |

| СТАБИЛИЗАТОР ПЕРЕМЕННОГО НАПРЯЖЕНИЯ | 2017 |

|

RU2665731C1 |

| УСТРОЙСТВО ДЛЯ НАКАЛА КАЛИЛЬНОЙ СВЕЧИ | 2017 |

|

RU2660979C1 |

| Устройство управления инвертором с однополярной частотно-импульсной модуляцией | 2024 |

|

RU2829334C1 |

Сущность изобретения: устройство содержит источник питания, подключенный через электронные ключи к входам первого и второго стабилизаторов напряжения. Выход первого стабилизатора напряжения подключен к входу первой схемы сравнения напряжения и к входу электронного ключа, включенного между выходом первого стабилизатора и цепью нагрузки, а выход второго стабилизатора напряжения соединен с входом второй схемы сравнения напряжения и с входом четвертого электронного ключа, выход которого подключен к цепи нагрузки. Новым в устройстве является блок управления включением, первый и второй входы которого соединены соответственно с выходами первой и второй схем сравнения напряжения, а третий вход соединен с выходом источника питания. Выходы блока управляют работой электронных ключей. Повышение надежности достигается путем упорядочивания расхода ресурса стабилизаторов и изменения последовательности аварийного отключения функциональных узлов устройства с блокировкой повторного включения аварийного стабилизатора. 3 ил Ё

te. /

| Патент США № 3440492,кл | |||

| Приспособление для обрезывания караваев теста | 1921 |

|

SU317A1 |

| Устройство для резервированного питания | 1977 |

|

SU734850A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1992-05-15—Публикация

1989-07-06—Подача