Фиг Л

Изобретение относится к управлению и регулированию и может быть использовано в программируемых контроллерах технологического оборудования.

Известно устройство, содержащее триг- гер, транзисторный ключ с токоизмеритель- ным резистором и датчик тока нагрузки.

Недостаток этого устройства состоит в том, что при реализации на его базе многоканального блока транзисторных ключей с защитой по току при повышенных уровнях помех требуется применение дополнительных элементов и в целом такой блок будет иметь большие аппаратурные затраты. Кроме того, на токоизмерительном резисторе должно падать достаточно большое напряжение для срабатывания датчика тока, что приводит к паразитному выделению тепловой мощности.

Наиболее близким по технической сущ- ности к предлагаемому устройству является модуль МВД-1, содержащий интерфейсный блок, регистр данных, оптронные и транзисторные ключи с индивидуальной триггер- ной защитой от перегрузки по току, регистр перегрузки по току.

Существенные признаки этого устройства: интерфейсный блок, регистр данных, оптронные и транзисторные ключи, регистр перегрузки потоку,совпадаютс признаками предлагаемого устройства.

Недостатком известного устройства является наличие устройства защиты от перегрузки по току в каждом из транзисторных ключей. В модуле МВД-1 имеется 16 кана- лов, таким образом, средства защиты ключей от перегрузки по току занимают основную часть схемы. Большое количество элементов приводит к снижению надежности устройства в целом.

Цель изобретения - уменьшение аппаратурных затрат, повышение надежности устройства.

Цель достигается тем, что в устройство, состоящее из блока связи с ЭВМ, регистра данных, регистра защиты блока силовых ключей, отличающееся тем. что. с целью уменьшения аппаратурных затрат и увеличения надежности, в него введены аналоговый коммутатор, интегратор, схема сравнения, источник опорного напряжения, формирователь управляющих сигналов, элемент И и блок элементов И, причем входы аналогового коммутатора соединены с выходом блока силовых ключей, информа- ционный вход интегратора подключен к выходу аналогового коммутатора, первый вход схемы сравнения подключен к выходу интегратора, выход источника опорного напряжения подключен к второму входу

схемы сравнения, вход формирователя управляющих сигналов подключен к выходу Сброс блока связи с ЭВМ, адресный выход формирователя управляющих сигналов подключен к входу адреса аналогового коммутатора, выход Сброс - к входу Сброс интегратора, первый вход элемента И подключен к выходу Строб формирователя управляющих сигналов, второй вход подключен к выходу схемы сравнения, а выход к входу Запись регистра защиты и к входу Запись блока связи с ЭВМ, первый вход блока элементов И подключен к выходу регистра данных, второй вход подключен к выходу регистра защиты, а выход блока элементов И подключен к входу блока силовых ключей, вход Адрес регистра защиты подключен к адресному выходу формирователя управляющих сигналов, первый вход Сброс регистра защиты подключен к выходу Сброс защиты блока связи с ЭВМ, второй вход Сброс регистра защиты подключен к выходу Сброс блока связи с ЭВМ и ко входу Сброс регистра данных, информационный выход которого подключен к выходу данных блока связи с ЭВМ, выходы блока силовых ключей являются выходом модуля вывода дискретных сигналов.

В предлагаемом изобретении аналоговый коммутатор, интегратор, источник опорного напряжения, схема сравнения, формирователь управляющих сигналов, элемент И, блок элементов И и регистр защиты в совокупности с указанными связями предназначены для организации поочередного опроса каналов блока силовых ключей, выявления канала, находящегося под перегрузкой по току и перевод этого канала в отключенное состояние, т.е. осуществляется защита силовых ключей от короткого замыкания в нагрузке. Так как для этой цели используются общие для всех каналов элементы, то уменьшаются аппаратурные затраты на реализацию модуля выхода дискретных сигналов для программируемых контроллеров.

Применение интегратора позволяет реагировать на интегральную перегрузку ключа, исключая ложное срабатывание защиты при помехах по питающему нагрузку напряжению.

В предложенном устройстве имеется специальная схема сравнения, позволяющая применять меньший по сравнению с аналогом номинал токоизмерительного резистора, что приводит к снижению выделения тепловой мощности на этих резисторах.

Отличительные признаки предлагаемого устройства; аналоговый коммутатор, интегратор, схема сравнения, источник

опорного напряжения, формирователь управляющих сигналов, элемент И и блок элементов И, причем входы аналогового коммутатора соединены с выходом блока силовых ключей, информационный вход интегратора подключен к выходу аналогового коммутатора, первый вход схемы сравнения подключен к выходу интегратора, выход источника опорного напряжения подключен к второму входу схемы сравнения, вход формирователя управляющих сигналов подключен к выходу Сброс блока связи с ЭВМ, адресный выход формирователя управляющих сигналов подключен к входу адреса аналогового коммутатора, а выход Сброс - к входу Сброс интегратора, первый вход элемента И подключен к выходу Строб формирователя управляющих сигналов, второй вход подключен к выходу схемы сравнения, а выход - к входу Запись регистра защиты и к входу Запись блока связи с ЭВМ, первый вход блока элементов И подключен к выходу регистра данных, второй вход подключен к выходу регистра защиты, а выход блока элементов И подключен к входу блока силовых ключей, вход Адрес регистра защиты подключен к адресному выходу формирователя управляющих сигналов, первый вход Сброс регистра защиты подключен к выходу Сброс защиты блока связи с ЭВМ, второй вход Сброс регистра защиты подключен к выходу Сброс блока связи с ЭВМ и к входу Сброс регистра данных, информационный вход которого подключен к выходу данных блока связи с ЭВМ, выходы блока силовых ключей являются выходом модуля вывода дискретных сигналов.

В результате анализа известных-аналогичных решений установлено, что отличительные признаки в аналогах отсутствуют, а их наличие в предлагаемом устройстве в совокупности обеспечивает достижение нового технического свойства, выражающегося в повышении надежности устройства и уменьшении аппаратурных затрат на его реализацию.

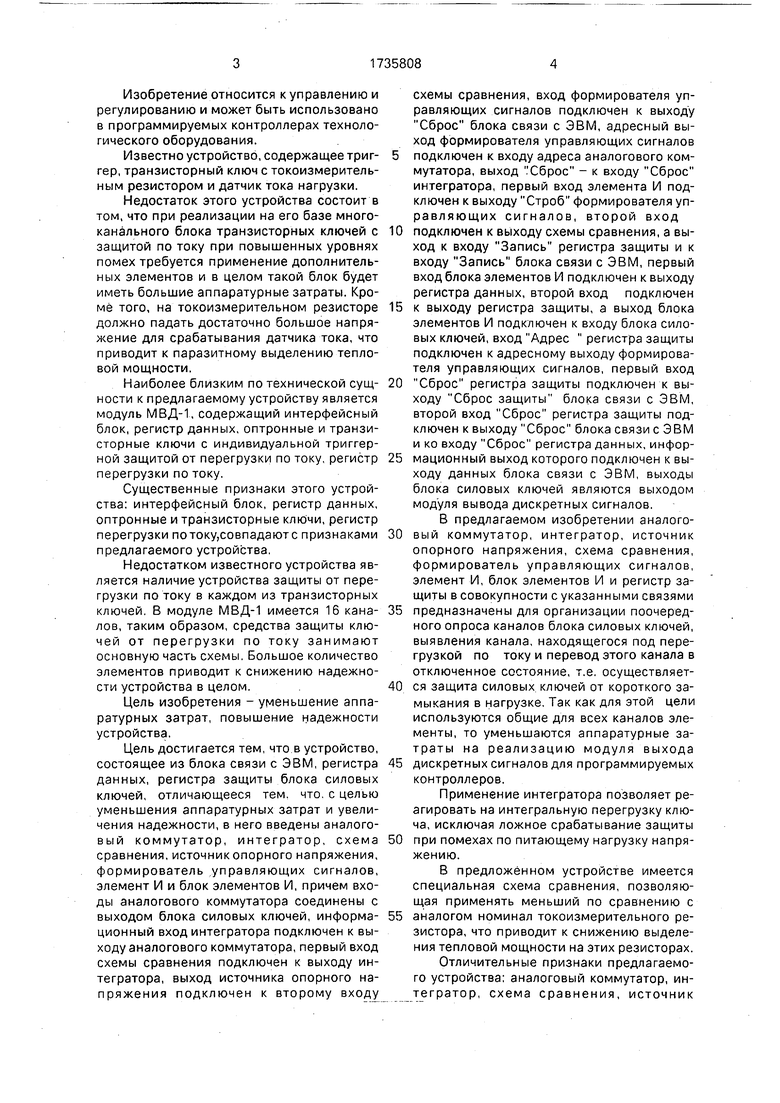

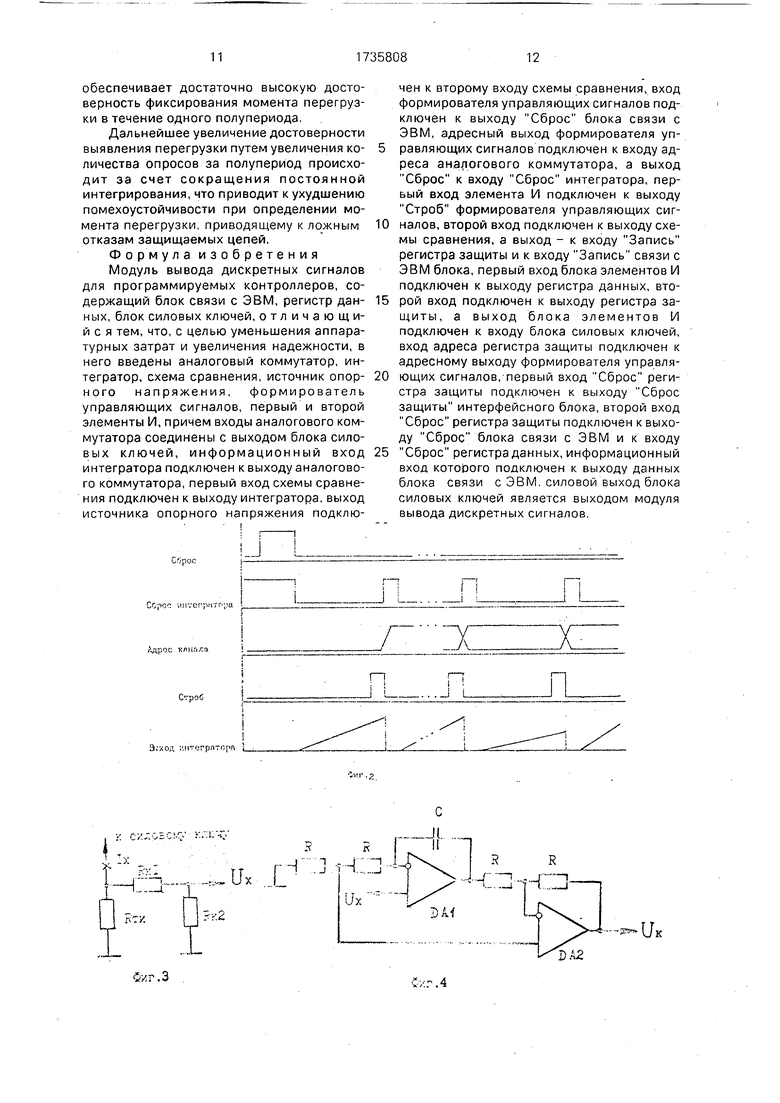

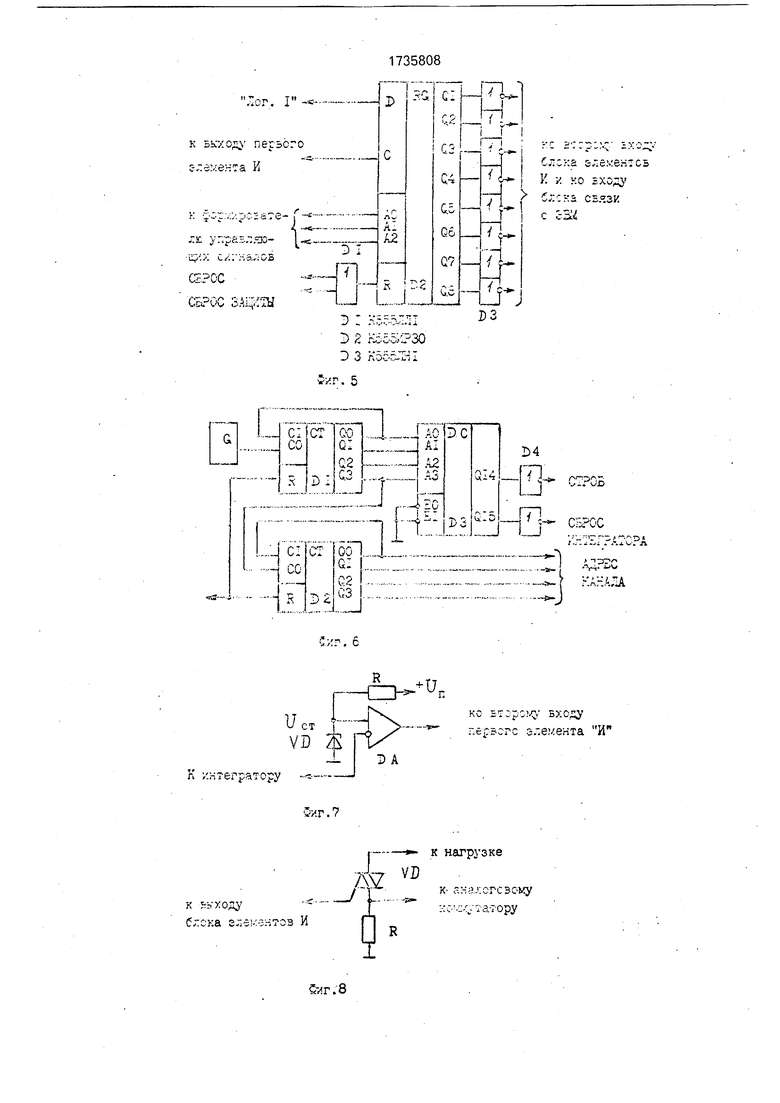

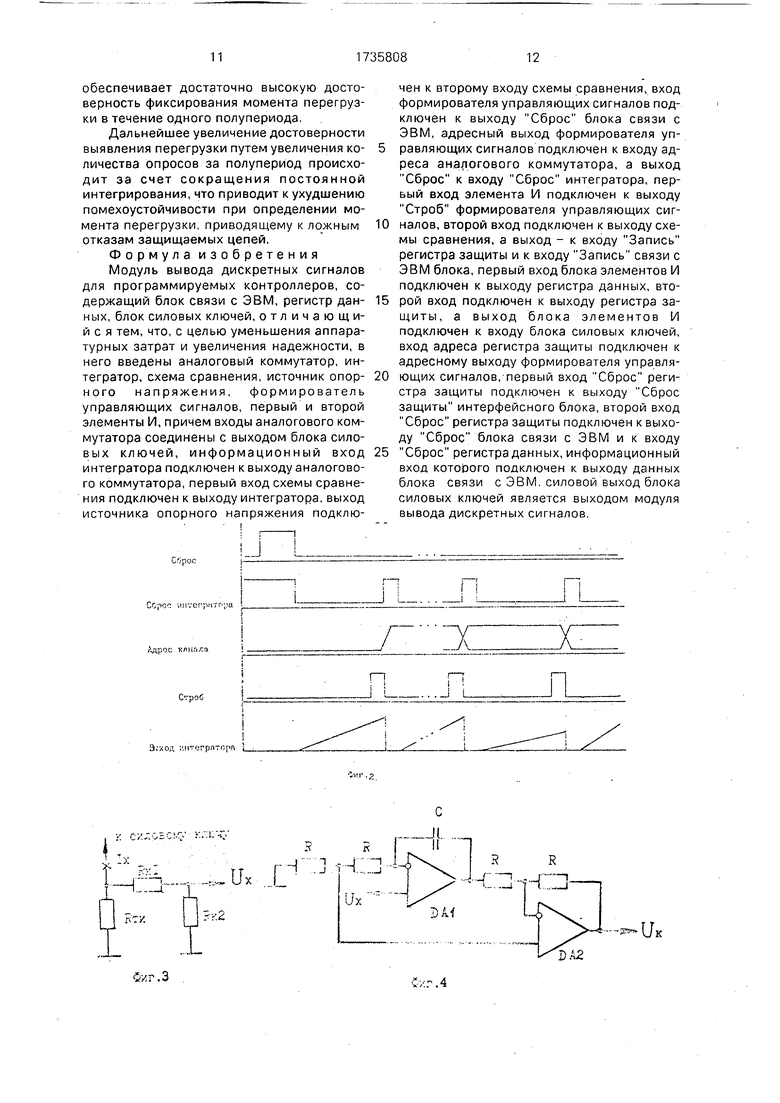

На фиг. 1 представлена функциональная схема модуля вывода дискретных сигналов для программируемых контроллеров; на фиг. 2 - эпюры сигналов; на фиг. 3-9 - пример конкретной реализации.

Устройство содержит блок 1 связи с ЭВМ, регистр 2 данных, блокЗ элементов И, формирователь 4 управляющих сигналов, блок 5 силовых ключей, аналоговый коммутатор 6, элемент И 7, источник 8 опорного напряжения, интегратор 9, регистр 10 защиты, схему 11 сравнения.

Устройство работает следующим образом.

Первоначально из управляющих сигналов ЭВМ в блоке связи с ЭВМ вырабатывается сигнал Сброс, который приводит в исходное состояние элементы устройства. При этом регистр данных устанавливается в нуль, регистр защиты устанавливается в единичное состояние, формирователь уп0 равляющих сигналов начинает разворачивать временную диаграмму с адреса первого канала, устанавливает активный сигнал Сброс интегратора и пассивный сигнал Строб. Активным считается сигнал

5 высокого уровня (логическая 1). Пассивным принят сигнал низкого уровня (логический О).

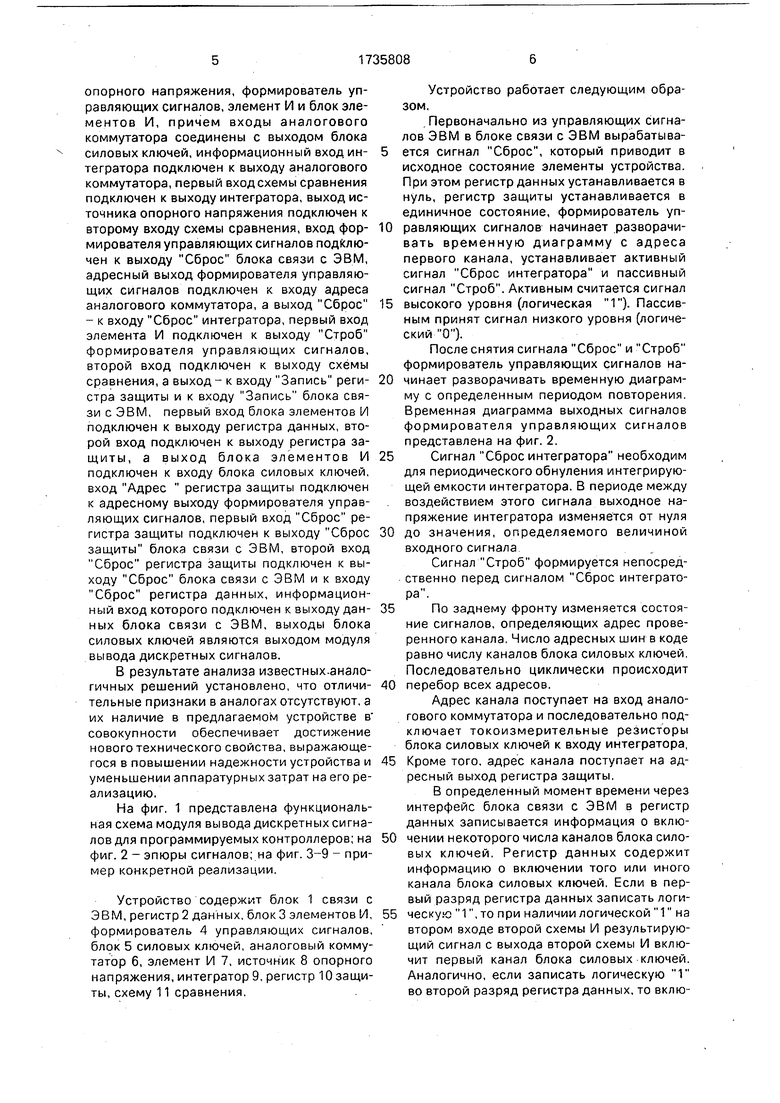

После снятия сигнала Сброс и Строб формирователь управляющих сигналов на0 чинает разворачивать временную диаграмму с определенным периодом повторения. Временная диаграмма выходных сигналов формирователя управляющих сигналов представлена на фиг. 2.

5 Сигнал Сброс интегратора необходим для периодического обнуления интегрирующей емкости интегратора. В периоде между воздействием этого сигнала выходное напряжение интегратора изменяется от нуля

0 до значения, определяемого величиной входного сигнала

Сигнал Строб формируется непосредственно перед сигналом Сброс интегратора.

5По заднему фронту изменяется состояние сигналов, определяющих адрес проверенного канала. Число адресных шин в коде равно числу каналов блока силовых ключей Последовательно циклически происходит

0 перебор всех адресов.

Адрес канала поступает на вход аналогового коммутатора и последовательно подключает токоизмерительные резисторы блока силовых ключей к входу интегратора,

5 Кроме того, адрес канала поступает на адресный выход регистра защиты.

В определенный момент времени через интерфейс блока связи с ЭВМ в регистр данных записывается информация о вклю0 чении некоторого числа каналов блока силовых ключей. Регистр данных содержит информацию о включении того или иного канала блока силовых ключей. Если в первый разряд регистра данных записать логи5 ческукз 1,то при наличии логической 1 на втором входе второй схемы И результирующий сигнал с выхода второй схемы И включит первый канал блока силовых ключей. Аналогично, если записать логическую 1 во второй разряд регистра данных, то включится второй канал блока силовых ключей. При записи логического О в первый разряд регистра данных, выключится первый канал блока силовых ключей. Аналогично выключается второй канал. Таким образом, можно включать/выключать любой канал блока силовых ключей. Информация о включении некоторого числа каналов блока силовых ключей представляет собой многоразрядное двоичное слово, которое поступает из канала ЭВМ через блок связи с ЭВМ на вход регистра данных. Первый разряд этого слова проходит и записывается в первый разряд регистра данных, и в зависимости от содержания этого разряда (логическая 1 или логический О) включает или выключает первый канал блока силовых ключей. Второй разряд информационного слова включает или выключает второй канал блока силовых ключей. Аналогично N-й разряд включает или выключает N-й канал блока силовых ключей. Для выключения всех каналов все разряды информационного слова должны содержать единицы. Для выключения все разряды должны быть установлены в нуль. В общем случае можно включать каналы блока силовых ключей в любом сочетании друг с другом.

Информация с выхода регистра данных проходит через блок элементов И на вход блока силовых ключей, Так как на второй вход этого же блока элементов И поступает единичный сигнал с выхода регистра защиты, на токоизмерительных резисторах включенных каналов начинает падать напряжение, пропорциональное току нагрузки соответствующего канала.

Аналоговый коммутатор в зависимости от поступающего на него адреса последовательно подключает токоизмерительные резисторы каждого из каналов на вход интегратора. После снятия сигнала Сброс интегратора, поступающего из формирователя управляющих сигналов, выходное напряжение интегратора начинает изменяться от нуля пропорционально входному сигналу. Период повторения сигнала Сброс интегратора, величина токоизмерительно- го резистора и постоянная времени интегратора рассчитаны таким образом, что в допустимом диапазоне токовой нагрузки ключа в конце периода интегрирования на выходе интегратора формируется напряжение меньше, чем выходное напряжение источника опорного напряжения. В случае перегрузки ключа это напряжение превысит опорное.

Если на одном из каналов произошла перегрузка по току, то в определенный момент времени токоизмерительный резистор

этого канала подключен через аналоговый коммутатор на вход интегратора. За период интегрирования на выходе интегратора сформируется напряжение, превышающее

напряжение источника опорного сигнала. Этот факт выявится схемой сравнения - на ее выходе появится логическая 1. С выхода схемы сравнения логическая 1 поступает на второй вход элемента И. На первом

0 входе элемента И периодически появляется импульсный сигнал Строб. При совпадении во времени входных сигналов элемента И на ее входе формируется единый сигнал Запись. Этот сигнал перебрасывает раз5 ряд регистра защиты, номер которого соответствует установленному в данный момент адресу канала в нулевое состояние. Нуль с выхода регистра защиты поступает на второй вход соответствующего канала блока

0 элементов И. Таким образом, на входе соответствующего канала блока элементов И появится логический нуль, что вызывает выключение силового ключа соответствующего канала. Аналогично работает защита

5 по любому другому каналу модуля вывода дискретных сигналов.

При выявлении фактов перегрузки по тому или иному каналу сигнал Запись поступает на вход блока связи с ЭВМ. Это

0 вызывает появление на канале ЭВМ требования прерывания работы ЭВМ. Данный сигнал указывает ЭВМ на то, что произошла перегрузка по току в одном из каналов модуля вывода дискретных сигналов, Для вы5 явления отказавшего канала ЭВМ должна прочитать через блок связи с ЭВМ состояния выходов регистра защиты. Наличие логического нуля на том или ином выходе регистра защиты указывает на соответству0 ющий номер канала модуля вывода дискретных сигналов, который имел перегрузку по току.

После принятия решения о возобновлении работы выключившегося канала ЭВМ

5 программным образом через блок связи с ЭВМ формирует сигнал Сброс защиты. Этот сигнал устанавливает регистр защиты в исходное единичное состояние.

Период повторения (Т) сигналов Сброс

0 интегратора, Строб, t соответствует времени измерения протекающего тока нагрузки одного канала.

Период измерения протекающего тока нагрузки каждого канала Т зависит от числа

5 каналов N

Т №.

Выбор периода Т выбирается в соответствии со следующими требованиями: силовой ключ должен находиться минимальное время под перегрузкой (большой протекающий ток короткого замыкания в нагрузке); время интегрирования должно быть достаточно большим, чтобы уменьшить влияния помех.

Исходя из реально используемого тран- зистора в силовом ключе и уровня помех, практически выбраны: N 16, Т 4,8 мс, t 210 мкс.

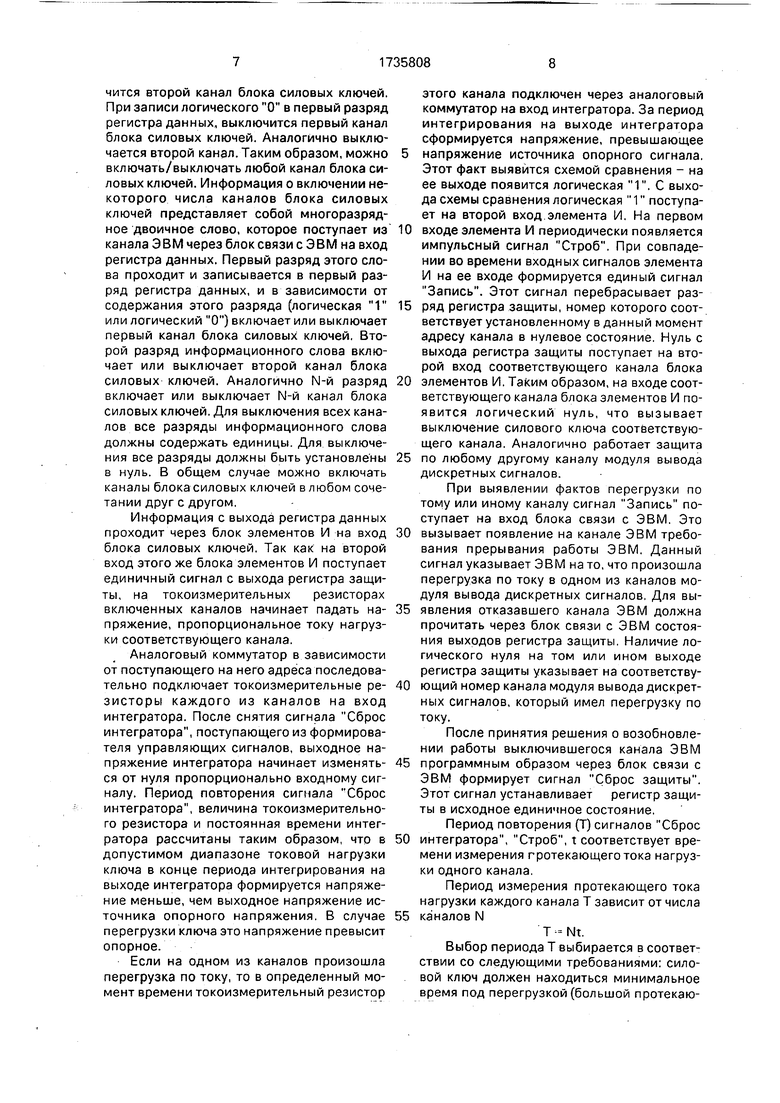

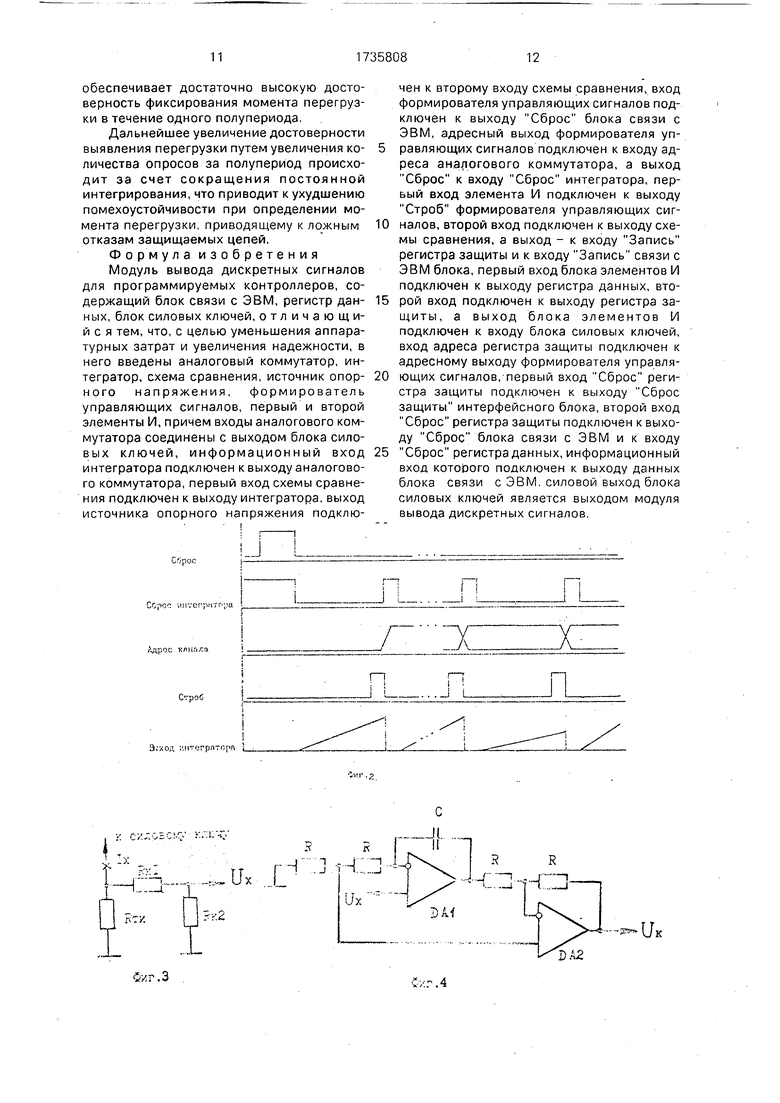

Ниже проводится анализ работы интегратора со сбросом в конкретной схеме включения, приведенной на фиг. 3.

Обозначим: R™ - токоизмерительный резистор;

Нк1 и Rx2 последовательная и параллельная составляющие входного сопротив- ления коммутатора относительно одного отдельно взятого канала;

1Х - контролируемый ток.

Полученное напряжение Ux на практике поступает на вход интегратора, построенно- го по схеме, приведенной на фиг. 4.

При номинальном токе короткого замыкания 1х напряжение на выходе интегратора UK изменяется от нуля до напряжения, равного напряжению источника опорного на- пряжения UCT. Напряжения UCT и UK поступают на вход схемы сравнения.

Для данной схемы

Ux

UxtM

2 RC

О)

Х- ХГХ

Подставив (2) в (1), получаем

I I - Ix Rx

UK (RK1+RK2) tM

С целью минимизации аппаратных затрат один период Т делится на 16 частей

1 /16 Т Тси tcrp,

где гси-длительность сигнала Сброс интегратора,

tcrp длительность сигнала Строб.

14/16T tn 7/8T;

7 Ix Rx Rx1 Хи

UK - g n

16RC(RK1 )

Задавшись конкретными типами опера- ционногоусилителя, коммутатора, компаратора, максимальным током нагрузки и номиналом токоизмерительного резистора можно рассчитать R и С,

5

0

5

0

5

0

5

0

5

50

55

Токоизмерительный резистор выбирается эмпирически минимально возможным, исходя из ограничений: уровень помех, параметры коммутатора, величина коммутируемого тока.

Модуль вывода дискретных сигналов реализован на базе стандартных элементов. Блок связан с ЭВМ построен по рекомендациям, приводимым в описании на используемую ЭВМ (например, ЭВМ Электро- ника-60). Для регистра данных и блока элементов И использован универсальный коммутатор К588ВАЗ. Этот элемент позволяет сократить аппаратурные затраты по сравнению с вариантом применения отдельных элементов И.

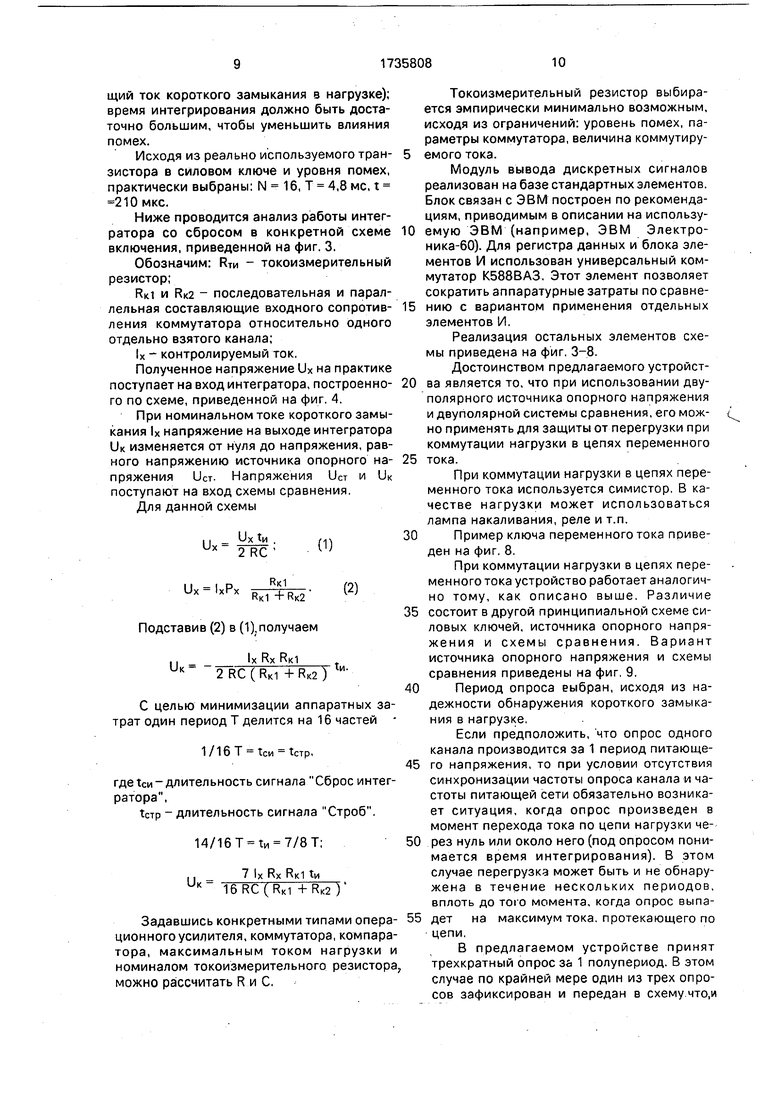

Реализация остальных элементов схемы приведена на фиг. 3-8.

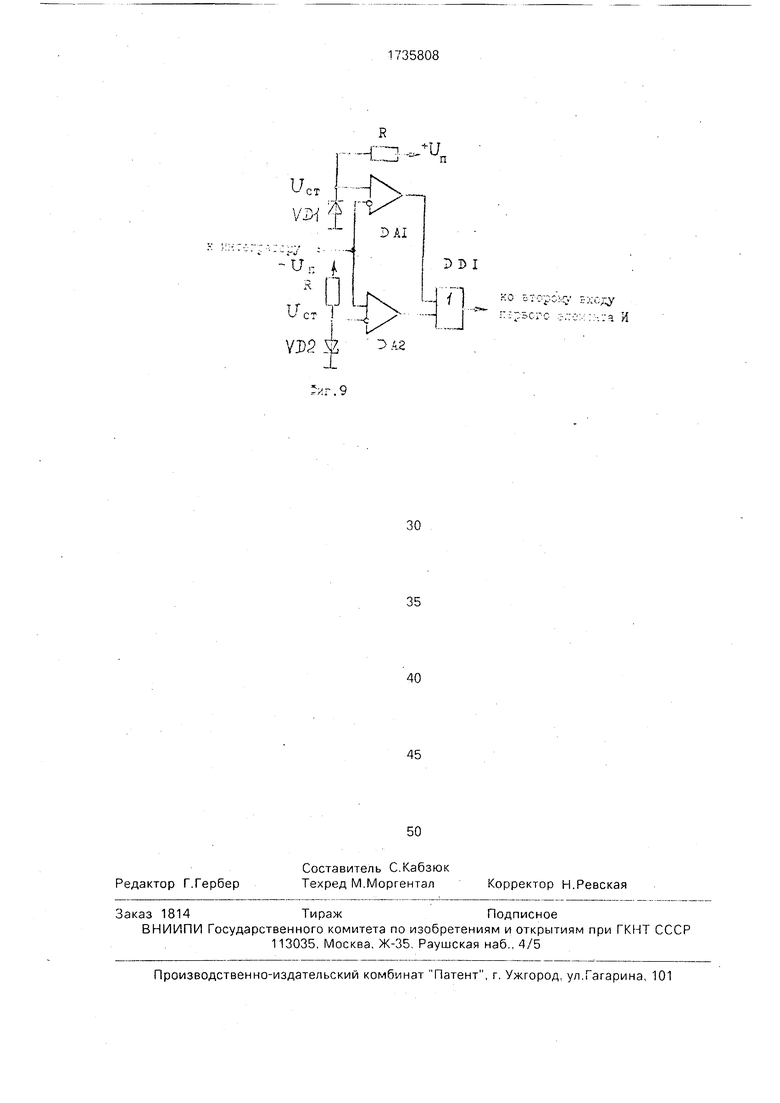

Достоинством предлагаемого устройства является то, что при использовании дву- полярного источника опорного напряжения и двуполярной системы сравнения, его мож- / но применять для защиты от перегрузки при коммутации нагрузки в цепях переменного тока.

При коммутации нагрузки в цепях переменного тока используется симистор. В качестве нагрузки может использоваться лампа накаливания, реле и т.п.

Пример ключа переменного тока приведен на фиг. 8.

При коммутации нагрузки в цепях переменного тока устройство работает аналогично тому, как описано выше. Различие состоит в другой принципиальной схеме силовых ключей, источника опорного напряжения и схемы сравнения. Вариант источника опорного напряжения и схемы сравнения приведены на фиг. 9.

Период опроса выбран, исходя из надежности обнаружения короткого замыкания в нагрузке.

Если предположить, что опрос одного канала производится за 1 период питающего напряжения, то при условии отсутствия синхронизации частоты опроса канала и частоты питающей сети обязательно возникает ситуация, когда опрос произведен в момент перехода тока по цепи нагрузки через нуль или около него (под опросом понимается время интегрирования). В этом случае перегрузка может быть и не обнаружена в течение нескольких периодов, вплоть до тою момента, когда опрос выпадет на максимум тока, протекающего по цепи.

В предлагаемом устройстве принят трехкратный опрос за 1 полупериод. В этом случае по крайней мере один из трех опросов зафиксирован и передан в схему что.и

обеспечивает достаточно высокую достоверность фиксирования момента перегрузки в течение одного полупериода.

Дальнейшее увеличение достоверности выявления перегрузки путем увеличения ко- личества опросов за полупериод происходит за счет сокращения постоянной интегрирования, что приводит к ухудшению помехоустойчивости при определении момента перегрузки, приводящему к ложным отказам защищаемых цепей.

Формула изобретения Модуль вывода дискретных сигналов для программируемых контроллеров, содержащий блок связи с ЭВМ, регистр дан- ных, блок силовых ключей, отличающийся тем, что, с целью уменьшения аппаратурных затрат и увеличения надежности, в него введены аналоговый коммутатор, интегратор, схема сравнения, источник опор- ного напряжения, формирователь управляющих сигналов, первый и второй элементы И, причем входы аналогового коммутатора соединены с выходом блока силовых ключей, информационный вход интегратора подключен к выходу аналогового коммутатора, первый вход схемы сравнения подключен к выходу интегратора, выход источника опорного напряжения подключен к второму входу схемы сравнения, вход формирователя управляющих сигналов подключен к выходу Сброс блока связи с ЭВМ, адресный выход формирователя управляющих сигналов подключен к входу адреса аналогового коммутатора, а выход Сброс к входу Сброс интегратора, первый вход элемента И подключен к выходу Строб формирователя управляющих сигналов, второй вход подключен к выходу схемы сравнения, а выход - к входу Запись регистра защиты и к входу Запись связи с ЭВМ блока, первый вход блока элементов И подключен к выходу регистра данных, второй вход подключен к выходу регистра защиты, а выход блока элементов И подключен к входу блока силовых ключей, вход адреса регистра защиты подключен к адресному выходу формирователя управляющих сигналов, первый вход Сброс регистра защиты подключен к выходу Сброс защиты интерфейсного блока, второй вход Сброс регистра защиты подключен к выходу Сброс блока связи с ЭВМ и к входу Сброс регистра данных, информационный вход которого подключен к выходу данных блока связи с ЭВМ. силовой выход блока силовых ключей является выходом модуля вывода дискретных сигналов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Распределенная система управления лучом | 2016 |

|

RU2632983C2 |

| Устройство для преобразования напряжения переменного тока в код | 1990 |

|

SU1795543A1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ НАПРЯЖЕНИЯ ПЕРЕМЕННОГО ТОКА В КОД | 2001 |

|

RU2195767C1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ПРОЦЕССОМ ДУГОВОЙ СВАРКИ НЕПЛАВЯЩИМСЯ ЭЛЕКТРОДОМ В СРЕДЕ ЗАЩИТНЫХ ГАЗОВ | 1988 |

|

SU1683244A1 |

| МИКРОПРОЦЕССОРНАЯ СИСТЕМА ЗАЩИТЫ | 2005 |

|

RU2344532C2 |

| Устройство для определения динамической податливости крупномасштабных фундаментов | 1988 |

|

SU1564502A1 |

| Ультразвуковой дефектоскоп | 1986 |

|

SU1385064A1 |

| Многоканальное устройство для стабилизации постоянного напряжения | 1984 |

|

SU1264156A2 |

| Устройство для програмного управления производственными процессами от ЭВМ | 1987 |

|

SU1524023A1 |

| Частотноуправляемый электропривод переменного тока | 1982 |

|

SU1086536A1 |

Адрос клн,-.ла .

Строб

й;ход ..iii-огрптора L

-н. ч и

ixr.3

-V А-.. .|

DA2

Гхг.4

11 т. Т -«.

А. БЬ:ХОД первого г-еуечта И

- - - -

с-.-v

А- А2

э: .

- L: j::,

з: Хт-гтсл:

D 2 лосо/РЗО Э 3 Ko6i-T-iI

с: со

ст

D:

хП Л--ГАС ЭС

- -JA:

..J Л2

00

с:

С2

:jс:

СС

н

I

т 551.J.

зг

1:

- ID3

G:

сг сз

п интегратору

к j-кходу

блока зле1. i.-iTOB И

..-/

1735808

Тр/ГТГи-Т1,

Си

А- А2

D3

Ь4

П J

v.rVD

W.iTvV

-1

Vf. v

КАНАЛА

кс 5r;pcvy входу г.есвогс И

VD

к нагрузке

к ..огсзоку ::;-..; 3.7 ору

- Л ix 1

YDP И ЭА2

.и

I.,,-iп

г.. : :а И

| Способ получения на волокне оливково-зеленой окраски путем образования никелевого лака азокрасителя | 1920 |

|

SU57A1 |

| (Япония), кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Кузнецов М.Н | |||

| и др.Распределенная система управления технологическим оборудованием и гибкими автоматизированными линиями | |||

| - Микропроцессорные средства и системы, 1987, № 2, с.24-30 | |||

Авторы

Даты

1992-05-23—Публикация

1989-08-14—Подача