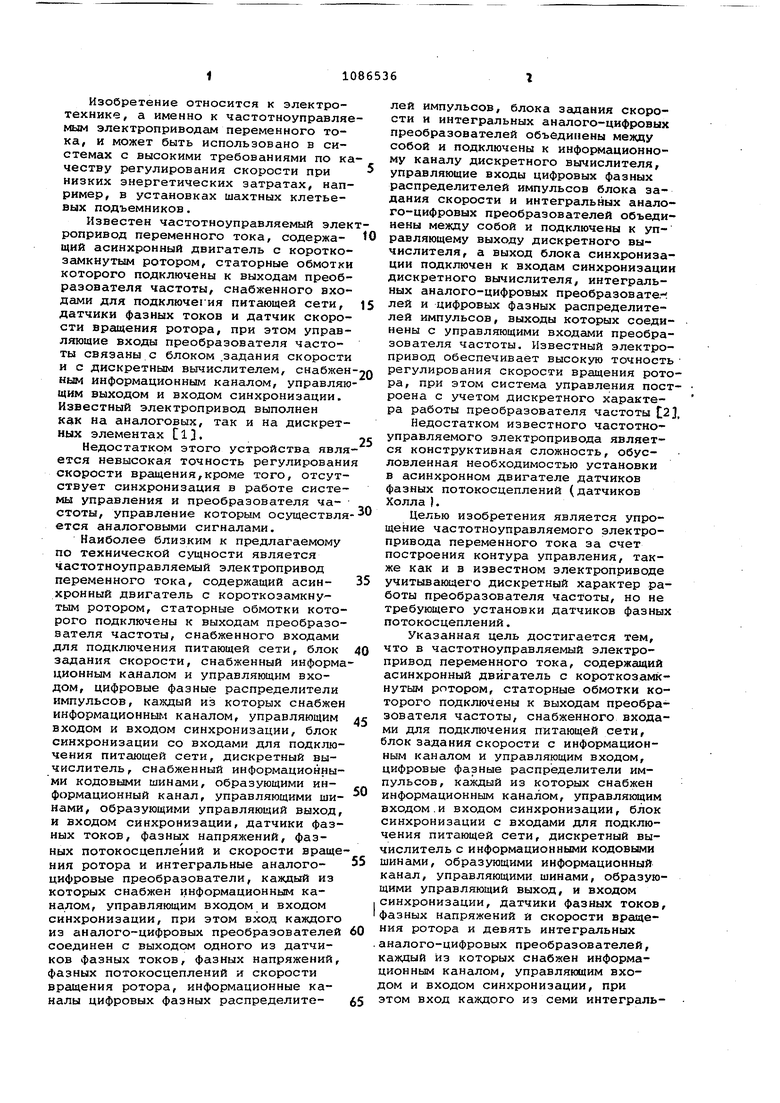

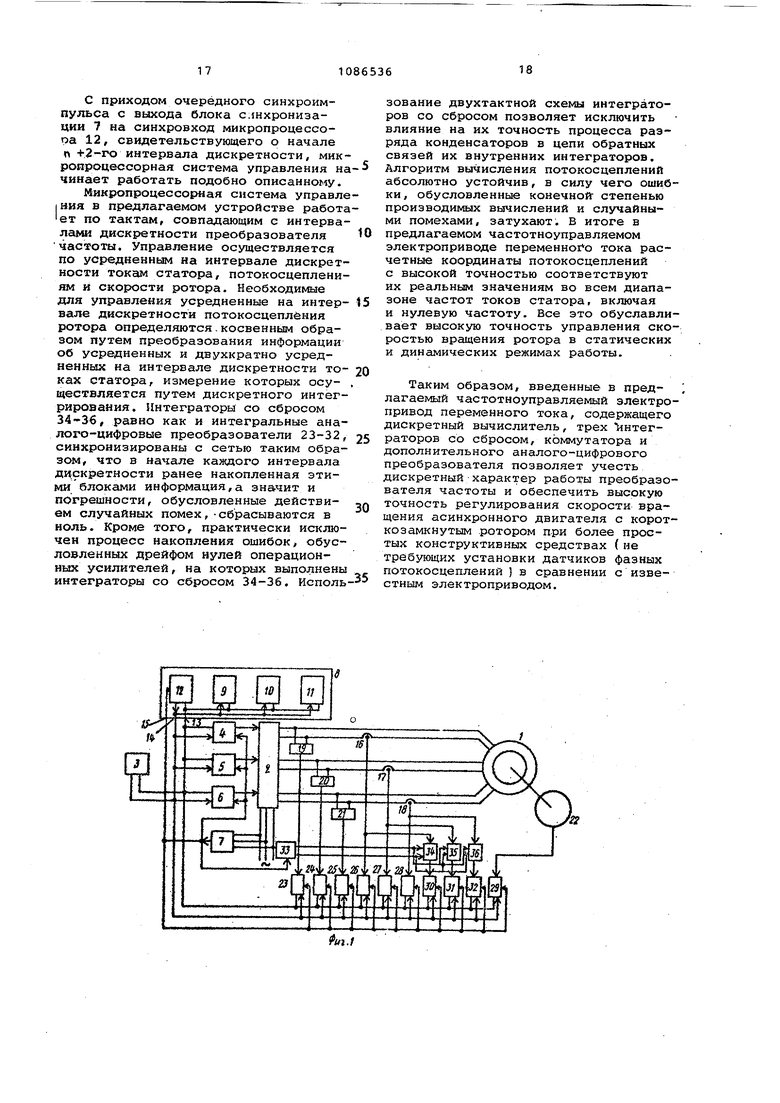

Изобретение относится к электротехнике, а именно к частотноуправля мым электроприводам переменного тока, и может быть использовано в системах с высокими требованиями по к честву регулирования скорости при низких энергетических затратах, нап ример, в установках шахтных клетьевых подъемников. Известен частотноуправляемый эле ропривод переменного тока, содержащий асинхронный двигатель с коротко замкнутым ротором, статорные обмотк которого подключены к выходам преоб разователя частоты, снабженного вхо дами для подключегия питающей сети, датчики фазных токов и датчик скоро сти вращения ротора, при этом управ ляющие входы преобразователя частоты связаны с блоком .задания скорост и с дискретным вычислителем, снабже ным информационным каналом, управляю щим выходом и входом синхронизации. Известный электропривод выполнен Кёцк На аналоговых, так и на дискретных элементах Cl3. Недостатком этого устройства явля ется невысокая точность регулировани скорости вращения,кроме того, отсутствует синхронизация в работе системы управления и преобразователя частоты, управление которым осуществля ется аналоговыми сигналами, Наиболее близким к предлагаемому по технической сущности является частотноуправляемый электропривод переменного тока, содержащий асинхронный двигатель с короткозамкнутым ротором, статорные обмотки которого подключены к выходам преобразователя частоты, снабженного входами для подключения питающей сети, блок задания скорости, снабженный информа ционным каналом и управляющим входом, цифровые фазные распределители импульсов, каждый из которых снабжен информационныг. каналом, управляющим входом и входом синхронизации, блок синхронизации со входами для подключения питающей сети, дискретный вычислитель, снабженный информационными кодовыми шинами, образующими информационный канал, управляющими шинами, образующими управляющий выход, и входом синхронизации, датчики фазных токов, фазных напряжений, фазных потокосцеплений и скорости враще ния ротора и интегральные аналогоцифровые преобразователи, каждый из которых снабжен информационным каналом, управляющим входом и входом синхронизации, при этом вход каждого из аналого-цифровых преобразователей соединен с выходом одного из датчиков фазных токов, фазных напряжений, фазных потокосцеплений и скорости вращения ротора, информационные каналы цифровых фазных распределителей импульсов, блока задания скорости и интегральных аналого-цифровых преобразователей объединены между собой и подключены к информационному каналу дискретного вычислителя, управляющие входы цифровых фазных распределителей импульсов блока задания скорости и интегральных аналого-цифровых преобразователей объединены между собой и подключены к управляющему выходу дискретного вычислителя, а выход блока синхронизации подключен к входам синхронизации дискретного вычислителя, интегральных аналого-цифровых преобразователей и цифровых фазных распределителей импульсов, выходы которых соединены с управляющими входами преобразователя частоты. Известный электропривод обеспечивает высокую точность регулирования скорости вращения ротора, при этом система управления построена с учетом дискретного характера работы преобразователя частоты L21 Недостатком известного частотноуправляемого электропривода является конструктивная сложность, обусловленная необходимостью установки в асинхронном двигателе датчиков фазных потокосцеплений (датчиков Холла I. Целью изобретения является упрощение частотноуправляемого электропривода переменного тока за счет построения контура управления, также как и в известном электроприводе учитывающего дискретный характер работы преобразователя частоты, но не требующего установки датчиков фазных потокосцеплений. Указанная цель достигается тем, что в частотноуправляемый электропривод переменного тока, содержащий асинхронный двигатель с короткозамкнутым ротором, статорные обмотки которого подключены к выходам преобразователя частоты, снабженного входами для подключения питающей сети, блок задания скорости с информационным каналом и управляющим входом, цифровые фазные распределители импульсов, каждый из которых снабжен информационным каналом, управляющим входом.и входом синхронизации, блок синхронизации с входами для подключения питающей сети, дискретный вычислитель с информационными кодовыми шинами, образующими информационный канал, управляющими шинами, образующими управляющий выход, и входом синхронизации, датчики фазных токов, фазных напряжений и скорости вращения ротора и девять интегральных аналого-цифровых преобразователей, каждый из которых снабжен информационным каналом, управляющим входом и входом синхронизации, при этом вход каждого из семи интегральных аналого-цифровых преобразователей соединен с выходом одного из датчиков фазных токов, фазных напряжений и скорости вращения ротора, информационные каналы цифровых фазных распределителей импульсов, блока задания скорости и интегральных аналого-цифровых преобразователей объединены между собой и подключены к информационному каналу дискретного вычислителя, управляющие входы цифро вых фазных распределителей импульсов блока задания скорости и интегральных аналого-цифровых преобразователей объединены мезкду собой и подключены к управляющему выходу дискретно го вычислителя, а выход блока синхро низации подключен к входам синхронизации дискретного вЕлчислителя, интег ральных аналого-цифровых преобразова телей и цифровых фазных распределите лей импульсов, выходы которых соедииены с управляющими входами преобразователя частоты, введены дополнител ный десятый интегральный аналого-циф ровой преобразователь, снабженный HH |)Ормационным каналом, управляющим входом и входом синхронизации,объеди ненными соответственно с информацион ными каналами, управляющими входами и входами синхронизации остальных девяти аналого-цифровых преобраэоваталей, коммутатор, выполненный в виде двухпозиционного триггера, и три интегратора со сбросом, каждый из которых снабжен двумя входами синхро низации, подключенными к выходам коммутатора, при этом вход коммутато ра соединен с выходом блока синхрони зации, вход каждого из интеграторов со сбросом подключен к выходу одного из датчиков фазных токов, а вы- , ход каждого из интеграторов со сбросом подключен соответственно к входам восьмого,, девятого и десято1О аналого-цифровых преобразователей. На фиг. 1 представлена функциональная схема частотноуправляемого электропривода переменного тока; на фиг. 2 - функциональная схема интегратора со сбросом. Частотноуправляемый электропривод переменного тока tфиг. 1) содержит асинхронный двигатель 1 с короткозамкнутым ротором, статорные обмотки которого подключены к выходам преобразователя частоты 2, снабженного входами для подключения питающей сети, блок задания скорости 3, снабженный информационным каналом и управляющим входом, цифровые фазные распределители импульсов 4-6, каждый из которых снабжен.информационным каналом, управляющим входом и входом синхронизации, блок синхронизации 7 с входами для подключения питающей сети, дискретный вычислитель 8, составленный из программного блока 9, блока нелинейных преобразователей 10, блока памяти 11 и микропроцессора 12 и снабженный информационными кодовыми шинами, образующими информационный анал 13, управляющими шинами, обазующими управляющий выход 14, и входом синхронизации 15, при этом программный блок 9, блок нелинейных преобразователей 10 и блок памяти 11 снабжены информационными каналами и управляющими входами, которые подключены соответственно к информационному каналу и управляющему выходу микропроцессора 12 и образуют соответственно информационный канал 13 и управляющий выход 14 дискретного вычислителя 8, а вход синхронизации микропроцессора 12 образует вход синхронизации 15 дискретного вычислителя 8, Частотноуправляемый электропривод переменного тока содержит также датчики фазных токов 16-18, датчики фазных напряжений 19,20 и 21, датчик скорости вращения 22 ротора и девять интегральных аналого-цифровых преобразователей 23-31, каждый из которых снабжен информационным каналом, управляющим входом и входом синхронизации, при этом входы аналого-цифровых преобразователей 23,24 и 25 соединены соответственно с выходами датчиков фазных напряжений -19-21, входы аналого-цифровых преобразователей 2628 соединены соответственно с выходами датчиков фазных токов 16-18,вход аналого-цифрового преобразователя 29 соединен с выходом датчика скорости вращения 22 ротора. Информационные Каналы цифровых фазных распределителей импульсов 4-6, блока задания скорости 3 и интегральных аналогоцифровых преобразователей 23-31 объединены между собой и подключены к информационному каналу 13 дискретного вычислителя 8. Управляющие входы цифровых фазных распределителей импульсов 4-6, блока задания скорости 3 и интегральных аналого-цифровых преобразователей 23-31 объединены между собой и подключены к управляющему выходу 14 дискретного вычислителя 8. Выход блока синхронизации 7 подключен к входам синхронизации дискретного вычислителя 8, интегральных аналого-цифровых преобразователей 23-31 и цифровых фазных распределителей импульсов 4-6, выходы которых соединены с управляющими входами преобразователя частоты 2. В Частотноуправляемый электропривод переменного тока введен десятый аналого-цифровой преобразователь 32, снабженный информационным каналом, управляющим входом и входом синхронизации, объединенными соответственно с информационными каналами, управляющими входами и входами синхронизации остальных девяти интегральных аналого-цифровых преобразователей 23-31.

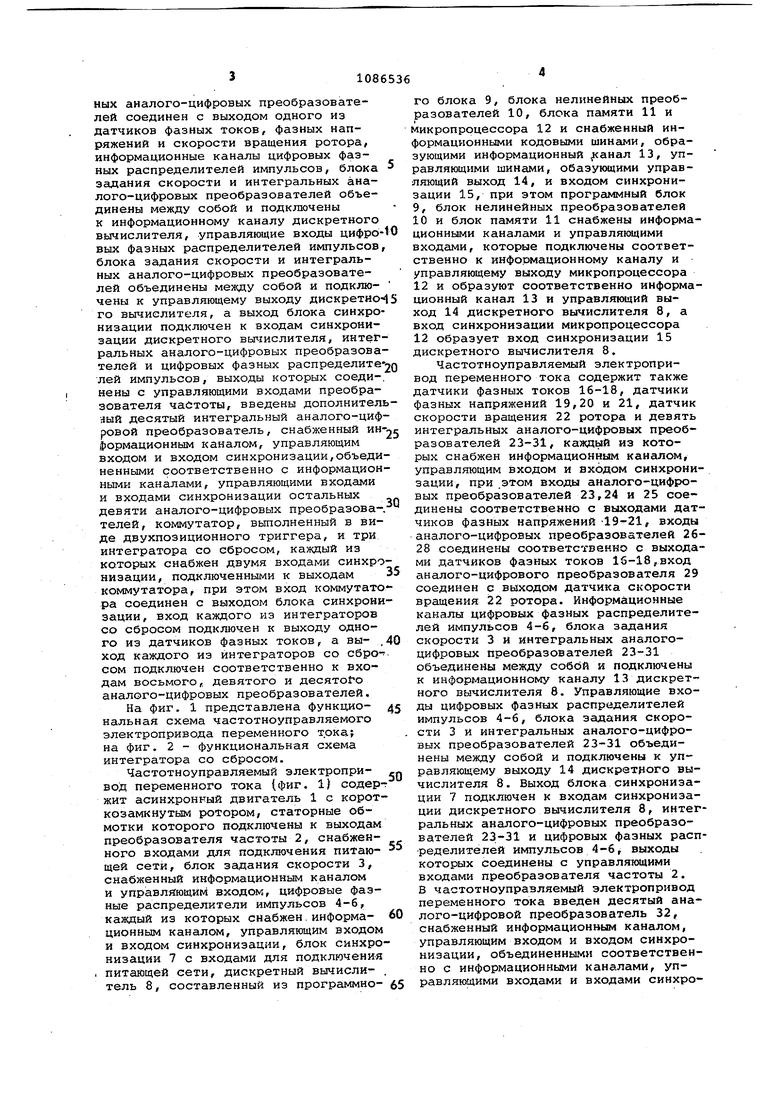

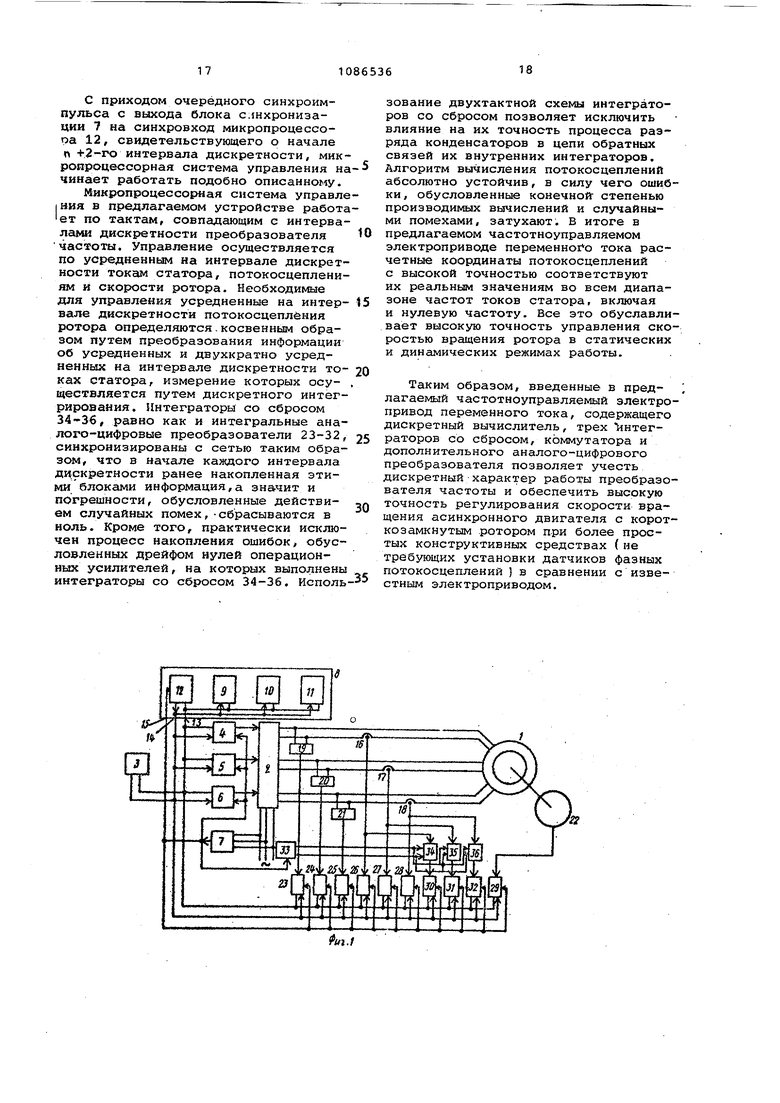

В частотноуправляемый электропривод переменного тока введены также коивиутатор 33, выполненный в виде двухпозиционного триггера, и три интегратора со.сбросом 34-36, каждый из которых снабжен двумя входами синхронизации/ подключенными к выходам коммутатора 33, при этом вход коммутатора 33 соединен с выходом блока синхронизации 7, вход каждого из интеграторов со сбросом 34-36 подключен к выходу одного из датчиков фазных токов 16-18 соответственно, а выход каждого из интеграторов со сбросом подключен соответственно к входам аналого-цифровых преобразователей 30-32. Интегратор со сбросом 34 (фиг. 2f содержит интеграторы 37 и 38, входы которых соединены между собой и образуют вход интегратора со сбросом 34. Параллельно конденсаторам, включенным в цепь обратной связи интеграторов 37 и 38, подключены электронные ключи соответственно 39 и 40. Одновременно выходы интеграторов 37 и 38 через электронные ключи соответственно 41 и 42 соединены мелоду собой и образуют выход интегратора со сбросом 34. Входы управления электронных ключей 39,42 и 40, 41 попарно соединены между собой и образуют два входа синхронизации интегратора со сбросом 34. Интеграторы со сбросом 35 и 36 выполнены аналогичным образом.

Частотноуправляемый электропривод переменного тока работает следующим образом.

Связь между информационным каналом микропроцессора 12 и информационными каналами программного блока 9, блока нелинейных преобразователей 10 блока памяти 11, цифровых фазных распределителей импульсов 4-6, блока задания скорости 3 и интегральных аналого-цифровых преобразователей 2332 осуществляется по единой системе информационных шин, количество которых определяется разрядностью микропроцессора 12 и равно в данном электроприводе шестнадцати. В свою очередь , управляющий выход микропроцессора 12 соединен с управляющими входами упомянутых блоков посредством трех служебных шин, по которым передается код служебных сигналов. Система управления предлагаемого электропривода выполнена на базе микропроцессорных БИС серий К 589, КР1802 и серии К155. Каждый из блоков, с которым микропроцессор 12 обменивается информацией, имеет свой адрес.

Прежде,чем осуществить обмен полезной информацией с одним из блоков микропроцессор 12 вырабатывает управ

ляющий сигнал записи адреса ЗПА, } который поступает с его управляющего выхода на управляющие входы всех блоков. Управляющий сигнал ЗПА ориентирует информационный канал микропроцессора 12 на передачу, а каналы остальных блоков на прием информации, после чего микропроцессор выдает, в информационный канал адресную информацию, содержащую как адрес необходимого блока, так и адрес конкретного носителя информации, расположенного в этом блоке. Казадый из фазных распределителей импульсов 4-6, блок задания скорости 3, программный блок блок нелинейных преобразователей 10, блок памяти 11, каждый из аналогоцифровых преобразователей содержит внутренний адресный дешифратор. Прог раммный блок 9, блок нелинейных преобразователей 10 и блок памяти 11 содержит дополнительно внутренний адресный регистр. Внутренние ад:;ресные дешифраторы управляются сигналом ЗПА таким образом, что при наличии последнего и совпадении выданного микропроцессором 12 адреса с адресом блока дешифратор вырабатывает сигнал, который переводит блок в активное состояние. Если мик/ропроцессор 12 обращается к одному из блоков 9-11, то после перевода блока в активное состояние в его внутренний адресный регистр записывается адрес конкретного носителя информации, размещенного в данном блоке, с которым микропроцесс9р 12 должен осуществить обмен полезной информацией.

После этого микропроцессор 12 вырабатывает управляющие сигналы чтения ЧтИ или .записи информации , которые ориентируют его информационный канал соответственно на приём или передачу. Одновременно эти сигналы поступают на управляющие входы всех блоков, однако реагирует на них только тот блок, который предварительно был переведен в активное состояние. .Сигналы ЧтИ или ЗПИ переводят информационный канал активного блока соответственно на передачу или прием, и между микропроцессором 12 и этим блоком, или конкретным информационным носителем, расположенным на этом блоке (в соответствии с адресом, записанным во внутреннем адресном регистре |, происходит обмен информацией. По окончанию обмена по заднему фронту сигналов ЧтИ или ЗПИ блок переходит в пассивное состояние. Если информационный канал любого блока не ориентирован на прием или передачу информации, то он находится в Z -состоянии, при котором его входное сопротивление очень велико, в силу чего такой блок не оказывает влияния на поток информации, пе редаваемый по информационным шинам. Программный блок 9 выполнен на базе постоянного запоминающегоустройства,- в котором зашита управляющая программа. В процессе работы микропроцессор 12 выдает адрес необходимой команды, по которому с программного блока 9 считывает ее код и выполняет ее. По выполнению команды микропроцессор 12 формирует адрес следующей команды, по которому считывает ее код и т.д. Вычисление функций cos(x); arc cos (х|; Vit, необходимых для управления, осуществлено в электроприводе табличным способом при помощи блока нелинейных преобразователей 10, который содержит нелинейные преобразователи, количество которых определяется числом необходимых функций и которые реализованы на базе постоянных запоминающих устройств. В каждый нелинейный преоб разователь зашиты заранее рассчитанные значения определенной функции для требуемого диапазона изменения ее аргумента. Обрабатывая код команды вычисления функции и аргумент, от которого вычисляется функция, микропроцессор 12 вырабатывает адрес необходимой ячейки памяти, расположенной в определенном нелинейном преобразователе, в которой хранится значение функции, соответствующее требуемому аргументу Значение функции считывается с этой ячейки и.поступает в микропроцессор 12, который использует это значе ние в дальнейшем вычислительном процессе. В процессе работы блок синхро низации вырабатывает синхроимпульсы, моменты появления которых совпадают с точками естественной коммутации ти ристОров преобразователя частоты 2 и период равен интервалу дискретности преобразователя частоты, причем длительность последнего равна для т-фаз ного тиристорного преобразователя Ти 115ГТ Г где ujg- круговая частота напряжения питающей сети. Синхроимпульсы с выхода блока син хронизации 7 поступают на входы синхронизации интегральных -аналого-. цифровых преобразователей 23-32, которые выполнены по принципу напряжение-частота. Аналоговые входные сигналы преобразуются в них в последовательность И1 1пульсов, частота которых пропорциональна величине входного сигнала. Счетчики, которыми снабжены интегральные аналого-цифровые преобразователи 23-32, осуществляют- суммирование угтомянутых импульсов , Сумма импульсов за определенный интервал времени пропорциональна интегралу от входного сигнала за этот -интервал. Интегральные аналогоцифровые преобразователи 23-32 снабжены также регистрами, входы которых подключены к выходам упомянутых счетчиков. По приходу синхроимпульса информация, которая была накоплена их внутренними счетчиками до этого момента, переписываемся во внутренние регистры, после чего содержимое счетчиков сбрасывается в ноль и они начинают накапливать новую информацию. В результате этого в конце каждого п-го интервала дискретности во внутренних регистрах интегральных аналого-цифровых преобразователей 23-32 фиксируется информация, которая численна равна . )Ти и, (tidt , т.е. пропорциональна усредненной за интервал v. дискретности преобразователя частоты 2 измеряемой величине (а - коэффициент пропорциональности). Синхроимпульсы с выхода блока синхронизации 7 поступают также на вход коммутатора 33, который выполнен на базе двухпозиционного триггера, работающего в счетном режиме, благодаря чему сигналы на выходах коммутатора 33 в любой момент времени имеют различный логический уровень (логический О или 1), и приходочередного импульса на его вход приводит к изменению логического уровня выходных сигналов с О на 1 и наоборот. Выходные сигналы коммутатора 31 поступают на входы синхронизации каждого из интеграторов со сбросом 34-36, синхронизируя их по интервалам дискретности преобразователя частоты 2. Пример работы интегратора со сбросом 34. Как упоминалось, выходные сигналы коммутатора 33 поступают на синхровходы интегратора со сбросом 34, а именно на входы управления электронных ключей 39,42 и 40, 41 (фиг. 2 f. Электронные ключи 39-42 устроены таким образом, что при подаче на их управляющие входы сигнала с логическим уровнем 1 они замыкаются, а при подаче сигнала с логическим уровнем О - размыкаются. За счет попарного соединения входов управления электронных ключей 39,42 и 40,41 и подачи на входы управления каждой из пар сигналов с различным логическим уровнем обеспечивается различное состояние электронных ключей из пар. Предполагается, что на входы управления электронных ключей 39 и 42 подается сигнал с логическим уровнем 1, а на входы электронных ключей 40 и 41 - сигнал с логическим уровнем О. При этом ключи 39 и 42 замкнуты, а ключи 40 и 41 разомкнуты. В силу этого конденсатор в цепи обратной связи интегратора 37 разряжен и напряжение на его выходе равно нулю. В то же время интегратор 38 осуществляет интегрирование входного сигнала, и его выходной сигнал через замкнутый ключ 42 поступает на выход интегратора со сбросом 34. По окончанию интервала дискретности на вход коммутатора 33 поступает очередной синхроимпульс, в результате чего логические уровни 10 выходных сигналов коммутатора 33 изменяются. При этом на входы ynpaBj;eния электронных ключей 39 и 42 подается сигнал с логическим уровнем О, а на входы электронных ключей 40 и 5 41 - сигнал с логическим уровнем 1. Электронные ключи 39 и 42 размыкаются, а 40 и 41 - замыкаются, в результате чего конденсатрр в цепи обратной связи интегратора 38 начинает разря- Q жаться/ и напряжение на выходе интегратора 38 резко уменьшается. Одновременно интегратор 37 начинает интегрировать выходное напряжение, и его выходной сигнал ерез замкнутый ключ г 41 поступает на выход интегратора со сбросом 34. в силу того, что в замкнутом состоянии сопротивление электронного ключа мало, на всетаки имеет конечное значение, разряд конденсатора- в цепи, обратной связи 30 .интегратора 38, а значит и уменьшение его выходного напряжения до нуля, происходит не мгновенно, а за конечное время. Однако за счет того, что одновременно с замыканием элект-35 ронкого ключа 40 размыкается электронный ключ 42, выходной сигнал интегратора 38 прекращает поступать I на выход интегратора со сбросом 34. В результате этого точность интегра-40 тора со сбросом 34 абсолютно не зависит от времени разряда конденсаторов, включенных в цепи обратных связей интеграторов 37 и 38.

Сопротивления входных резисторов 45 интеграторов 37 и 38 и емкости конденсаторов, включенных в цепи их обратных связей, подбираются таким образом, чтобы постоянные интегрирования упомянутьгх интеграторов были CQ одинаковыми и равными постоянным интегрирования аналогичных интеграторов в интеграторах со сбросом 35 и 36. В силу того, что по окончанию каждого ин -ервала дискретности информация, накопленная работавшим интегратором 37 или 38, сбрасывается в ноль, не происходит накопления ошибки, обусловленной дрейфом нуля операционных усилителей, на которых выполнены интеграторы 37 и 38, по- 60 этому точность интегратора со сбросом 34 практически не зависит от частоты входного сигнала.

Интеграторы со сбросом 35 и 36 работают аналогично интегратору со 5

сбросом 34, в силу чего все приве- денные выводы, касающиеся работы интегратора со сбросом 34, в равной степени относятся и к интеграторам со сбросом 35 и 36. В любой момент времени на каждом п-м интервале дискретности выходные сигналы интеграторов со сбросом 34-36 численно равны

.-i(t),J(t),

и

и-вы

пТ..

где (/u.A,B,C; а - коэффициент пропорциональности ),

т.е. пропорциональны средним текущим значениям фазных токов.статора. Соответственно в конце каждого интервала дискретности во внутренних регистрах интегральных аналогоцифровых преобразователей 30-32 фиксируется информация, численно равная

а Г

V6.

и v J

Ти пТ

где jU. А,в,С;с(2 сх-а -коэффициент яропорциональности,

т.е. пропорциональная двукратно усредненнЕлм на интервале дискретности фазным токам статора.

Синхроимпульсы, вырабатываемые блоком синхронизации 7 в начале каждого интервала дискретности, поступают также на вход синхронизации микропроцессора 12, последний запускается и начинает выполнять управляющую программу, зашитую в програгдмном блоке 9. Последняя состоит из следующих основных подпрограмм: подпрограмма опроса датчиков, расчета отклонений, регулятора усредненных токов статора и потокосцеплений ротора, расчета управляющих воздействий, расчета коэффициентов, определения координат потока, формирователя траектории движения.

Быполне,ние управляющей программы начинается с подпрограммы опроса датчиков, выполняя которую, микропроцессор 12 осуществляет последовательное считывание информации с блока задания скорости 3 и интегральных аналого-цифровых преобразователей 23-25, 26-28, 30-32, 29, пропорциональной соответственно заданию на усредненную скорость ротора на два интервала вперед ш п-(-23 , усредненным напряжениям статора токам статора , двукратно усредненным токам статора ijiiCnJ (/ь.А, В,С ) и усредненной скорости ротора u)CnJ на истекшем п-м интервале дискретности. После считывания упомянутая информация записывается в соответствующие ячейки блока памяти 11. После вьтолнения подпрограммы опроса датчиков микропроцессор 12 начинает выполнять подпрограмму расчета отклонений. По этой подпрограмме микропроцессор 12 рассчитывает отклонения между заданными управляющими кoopдинaтa - усредненными напряжениями статора на истекшем интервале (определение которых дано ниже) и их реальными значениями W uj W-yW . (Я Рассчитанные значения отклонений микропроцессор 12 записывает в соответствующие ячейки блока памяти 11. После этого выполнение подпрограммы расчета отклонений прерывается, микропроцессор 12 начинает выполнять подпрограмму регулятора усредненных токов статора и потокосцеплений ротора. По эти, подпрограмме микропроцессор 12 осуществляет расчет кор ректирующих добавок к заданию на фаз ные напряжения статора на п +1-м интервале дискретности, которые обеспе чивают выход управляемых электромагнитных координат электродвигателя 1усредненнык фазных токов статора и потокосцеплений ротора на заданную траекторию .движения, которая задается при выполнении подпрограммы формирователя траекторий движения (см. ниже). Вычислительный алгоритм определения корректирующих добавок синтезирован в неподвижной системе координат и определяется следующим выражением Ae liD- i -чЗ усредненные на п-1-м интервале дискретности потокосцепления фаз А и В ротора; D- матрица коэффициентов ра мерностью 3x5; С - матрица коэффициентов ра 2 .-i. мерностью 3x3} индексом 4 обозначены разности между заданными и реальными значени ми управляющих и управляемых коорди нат электродвигателя 1 на одноимен ных интервалах дискретности.

(4)

45 Для уменьшения запаздывания при реализации управляющих воздействий большая часть вьпислительного алгоритма , определяемого выражением (21, выполняется на истекшем п-м интервале дискретности, в частности, при выполнении подпрограммы расчета коэффициентов вычисляются компоненты матриц) , С ч Су , зависящие как от параметров электродвигателя 1, так и от усредненной скорости вращения ротора ujfn-lj; при выполнении подпрограммы определения координат потока рассчитываются усредненные на n-1-M интервале дискретности лотокосцепления ротора , (см.ниже I, при выполнении подпрограммы расчета отклонений рассчитываются разности между заданными и реальными значениями управляемых электромагнитных и управляющих координат электродвигателя 1 на ri-1-м интервале дискретности; при выполнении второй части подпрограммы регулятора усредненных токов статора и потокосцеплений ротора рассчитывается сумма 2-х первых матричных слагаемых, входящих в выражение (21: Поэтому на текущем n+1-M интервале дискретности при выполнении первой части подпрограммы регулятора усредненных токов статора и потокосцеплений ротора микропроцессор 12 только завершает расчет корректирующих добавок, реализуя при этом выражение и затрачивая на это минимум необходимого времени. После расчета корректирующих добавок микропроцессор 12 осущестЕляет расчет средних значений фазных напряжений статора, которые необходимо реализовать на ti +1-М интервале дискретности0, U3 nHj-4U fn+ J , {51 где А,В,С. Если хотя бы одно из расчетных значений напряжений CTaTopaU {n+l превосходит допустимое, то производится их ограничение. Полученные значения фазных напряжений статора О,{я+1 микропроцессор 12 записывает в соответствующие ячейки блока памяти 11, после чего выполнение подпрограммы регулятора усредненных токов статора и потокосцеплений ротора пр рывается и микропроцессор 12 начинает выполнять подпрограмму расчета управляющих воздействий. По этой подпрограмме микропроцессор 12 осуще ствляет расчет углов управления преобразователем на n+1-M интервале дискретности, реализуя следующие выраженияot nHj / arccos(R,,0 i:nHj|, (6) где R и % постоянные коэффициенты. Рассчитанные углы управления оС(Ъ+1 микропроцессор 12 переписывает во внутренние регистры цифровых фазных распределителей импульсов 4-6, последние представляют собой преобразователи цифровой код - временный интервал, которые измеряют временные интервалы, отсчитываемые от точек естественной коммутации тиристоров в преобразователе частоты 2 и сравнивают их с содержимым внутрен них регистров, в которые записаны значения углов управления на соответ ствующем интервале дискретности. В момент их сравнения цифровые фазные распределители импульсов 4-6 вырабатывают импульсы управления и подают их на соответствующие тиристоры преобразователя частоты 2, реализуя таКИМ образом требуемые углы управления. Максимальное запаздывание при pea лизации углов управления преобразова телем частоты 2 равно временному интервалу между моментом начала интервала дискретности и моментом записи значений углов управления во внутрен ние регистры цифровых фазных распределителей импульсов 4-6. В предлагае мом электроприводе это запаздывание равно 1 эл.град и практически не ухудшает динамические качества систе мы. После записи значений углов управления преобразователем частоты 2 oC-i во внутренние регистры цифровых распределителей импульсов 4-6 микропроцессорная система управления приступает к подготовке информации, необходимой для расчета углов управлен я преобразователем частоты 2, на п Н-2-М интервале дискретности. При этом микропроцессор 12 начинает выполнять подпрограмму расчета коэффициентов. По этой подпрограмме микропроцессор 12 рассчитывает коэффициенты матриц В , С;,, С2/ В, Б2, Bj, Вл, Bg, зависящие как от параметров электродвигателя 1, так и от усредненной скорости вращения , и используемые в дальнейшем при выполнении подпрограммы регулятора усредненных токов статора и потокосцеплений ротора и определения координат потока (см.ниже). Значения вновь рассчитанных коэффициентов микропроцессор 12 записывает в соответствующие ячейки блока памяти 11. После этого микропроцессор 12 заканчивает выполнение подпрограммы расчета коэффициентов и начинает выполнять подпрограмму определения координат потока. Под этой подпрограмме микропроцессор 12 рассчитывает усредненные на п-м интервале дискретности потокосцепления фаз А и В ротора, реализуя при этом следующий вычислительный алгоритм. B - матрица коэффициентов размерностью 2x2; Bj-Bj - матрицы коэффициентов размерностью 2x3. Следует подчеркнуть, что собственные числа матрицы В во всем диапазоне изменения скорости ротора по модулю меньше единицы, поэтому вычислительный алгоритм, определяемый выражением (7|, является абсолютно устойчивым. Следовательно, возникающие ошибки, обусловленные конечной точностью измерений и вычислений, не накапливаются в процессе работы, а затухают. Кроме того, точность вычислительного алгоритма (71 абсолютно не зависит от частоты изменения усредненных и двукратно усредненных на интервале дискретности токов статора соответственно Т CnJ, Т СпТ ,В,С|. Рассчитанные значения усредненных на п-м интервале дискретности потокосцеплений ротора Фд Сп и VgC микропроцессор 12 записывает в соответст,вующие ячейки блока памяти 11. После этого микропроцессор 12 заканчивает выполнение подпрограммы определения координат потока и начинает выполнять подпрограмму формирователя траектории движения. Выполняя эту одпрограмму, микропроцессор 12 осуествляет расчет требуемого усредненого скольжения, которое должно подерживаться на п +1-М и п +2-М интералах дискретности для обеспечения ребуемого момента электродвигателя 1 (, . (8) Если расчетное значение усредненого скольжения превышает допустимое, о производится его ограничение и оответственно корректировка задания усредненной скорости ротора (г+23 . После этого осуществляется расчет требуемого углового положения усред ненного вектора потокосцепления рот ра на n+2-M интервале дискретности относительно оси фазы А статора. Д(.Г K,a,rn.u,) . Определяется требуемая усредненная скорость вращения усредненного вектора потокосцепления ротора, на п +2-М интервале дискретности. (:n42j + aJ В дальнейшем микропроцессор 12 осуществляет расчет требуемых состав ляющих усредненных векторов тока и напряжения статора нап+2-м интервале дискретности в системе координат одна из осей которых совпадает с усредненным вектором потокосцепления ротора. Расчет упомянутых составляющих осуществляется из условия поддер жания модуля усредненного вектора потокосцепления в процессе регулиро.вания постоянным, T.e. (f -CJOi St . и,Сп.2 Кз4Д5гзГп.23.)К5Шз,2) ; и,,),.к,); i, KgV ; T2Cnt2 K9Vf-UJcK где К0-Кд - постоянные коэффициенты. В выражениях 11 индексом 1 обозначены проекции векторов на ось, сов падающую с вектором усредненного век тора потокосцепления ротора, а индек сом 2 - проекции усредненных векто ров на ортогональную ей ось. По знач ниям составляющих микропроцессор 12 рассчитывает требуемые модули усредненных векторов тока и напряжения ст тора и их положение относительно усредненкого вектора потокосцепления ротор на (1+2-м интервале дискретности {0|Ь.2 /05Сп 2 и|Сп 2 i i (12) РД-2: «гс.. / titn-e23 I ,гс1.( Суммируя требуемое угловое положе ние усредненного вектора потокосцеп ления ротора на п +2-м интервале .. дискретности п +2 с величинами и ;, п , микропроцессор 12 определяет требуемое угловое положение усредненных векторов тока и напряжения статора на h 4-2-м интервале дискретности относительно фаз статора V. Сп-2 -Ч Сп42 - /1 Гп+22; V, ,. Раскладывая полученные требуемые усредненные вектора тока, напряжения статора и потокосцепления ротора по осям фаз статора, микропроцессор 12 определяет задания соответственно на усредненные фазные токи, напряжения статора и потокосцепления ротора на п +2-м интервале дискретности. 3)и 1 Г 23cos(V.fnt2J- f I 1 fn ajcos(V (14) 3 tf 2 r 4Y4r 2)где ,B,C} , 2Л/Э , -2Л/3 . Полученные величины задания микропроцессор записывает в соответствующие ячейки блока памяти 11. На этом подпрограмма формирователя траектории движения заканчивается, после чего микропроцессор 12 начинает выполнять вт.орую часть подпрограммы расчета отклонений, прерванной ранее (см.выше }, Реализуя вторую часть упомянутой подпрограммы, микропроцессор 12 рассчитывает отклонения между заданными электромагнитными управляемыми координатами электродвигателя 1- усредненными фазными токами статора и потокосцепления ротора и их реальными значениями на истекшем (л-м интервале дискретности 4u.uW ; . Рассчитанные значения отклонений микропроцессор записывает в соответствующие ячейки блока памяти 11. На этом подпрограмма расчета отклонений заканчивается, и микропроцессор начинает выполнять вторую часть подпрограммы регулятора усредненных токов статора и потокосцеплений ротора, прерванную ранее (см.выше). Выполняя вторую часть упомянутой программы, микропроцессор 12 реализует выражение (31, подготавливая информацию для расчета корректирующих добавок к заданию на фааные напряжения статора на -п +2-м интервале дискретности (см.выше I. Рассчитанные значения микропроцессор 12 записывает в соответствующие ячейки блока памяти 11. После этого работа микропроцессорной системы управления на .п+1-м интервале дискретности заканчивается. С приходом очерёдного синхроимпульса с выхода блока слнхронизации 7 на синхровход микропроцессора 12, свидетельствующего о начале п +г-го интервала дискретности, микропроцессорная система управления на чинает работать подобно описанному. Микропроцессорная система управле Iния в предлагаемом устройстве работа ет по тактам, совпадающим с интервалами дискретности преобразователя частоты. Управление осуществляется по усредненным на интервале дискретности токам статора, потокосцеплениям и скорости ротора. Необходимые для управления усредненные на интервале дискретности потокосцеплёния ротора определяются.косвенным образом путем преобразования информации об усредненных и двухкратно усредненных на интервале дискретности токах статора, измерение которых осуществляется путем дискретного интегрирования. Интеграторы со сбросом 34-36, равно как и интегральные аналого-цифровые преобразователи 23-32, синхронизированы с сетью таким образом, что в начале каждого интервала дИ:СКретности ранее накопленная этимиблоками информация,а значит и погрешности, обусловленные действием случайных помех,-сбрасываются в ноль. Кроме того, практически исключен процесс накопления ошибок обусловленных дрейфом нулей операционных усилителей, на которых выполнены интеграторы со сбросом 34-36. Исполь зование двухтактной схемы интеграторов со сбросом позволяет исключить влияние на их точность процесса разряда конденсаторов в цепи обратных связей их внутренних интеграторов. Алгоритм вычисления потокосцеплений абсолютно устойчив, в силу чего ошибки, обусловленные конечной степенью производимых вычислений и случайными помехами, затухают. В итоге в предлагаемом частотноуправляемом электроприводе переменного тока расчетные координаты потокосцеплений с высокой точностью соответствуют их реальным значениям во всем диапазоне частот токов статора, включая и нулевую частоту. Все это обуславливает высокую точность управления скоростью вращения ротора в статических и динс1мических режимах работы. Таким образом, введенные в предлагаемый частотноуправляемый электропривод переменного тока, содержащего дискретный вычислитель, трех интеграторов со сбросом, коммутатора и дополнительного аналого-цифрового преобразователя позволяет учесть дискретный характер работы преобразователя частоты и обеспечить высокую точность регулирования скорости вращения асинхронного двигателя с короткозамкнутым ротором при более простых конструктивных средствах ( не требующих установки датчиков фазных потокосцеплений ) в сравнении с известным электроприводом.

| название | год | авторы | номер документа |

|---|---|---|---|

| Частотноуправляемый электропривод переменного тока | 1982 |

|

SU1086535A1 |

| Электропривод переменного тока | 1981 |

|

SU1026272A1 |

| СПОСОБ ВЕКТОРНОГО УПРАВЛЕНИЯ СИНХРОННЫМ ЭЛЕКТРОДВИГАТЕЛЕМ С ПОСТОЯННЫМИ МАГНИТАМИ НА РОТОРЕ И ЭЛЕКТРОПРИВОД ДЛЯ ОСУЩЕСТВЛЕНИЯ ЭТОГО СПОСОБА | 1998 |

|

RU2141719C1 |

| Электропривод переменного тока | 1987 |

|

SU1534735A1 |

| СПОСОБ УПРАВЛЕНИЯ ЭЛЕКТРОПРИВОДОМ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2020724C1 |

| СПОСОБ ВЕКТОРНОЙ ОРИЕНТАЦИИ ТОКА ЭЛЕКТРОМЕХАНИЧЕСКОГО ПРЕОБРАЗОВАТЕЛЯ ЭНЕРГИИ И УСТРОЙСТВО ВЕКТОРНОЙ ОРИЕНТАЦИИ ("ВЕКТОРИНГ") ДЛЯ ОСУЩЕСТВЛЕНИЯ СПОСОБА | 1998 |

|

RU2141720C1 |

| Частотно-регулируемый электропривод | 1986 |

|

SU1347142A1 |

| ЧАСТОТНО-РЕГУЛИРУЕМЫЙ АСИНХРОННЫЙ ЭЛЕКТРОПРИВОД | 2006 |

|

RU2313894C1 |

| СИСТЕМА ВЕКТОРНОГО УПРАВЛЕНИЯ СКОРОСТЬЮ АСИНХРОННОГО ЭЛЕКТРОДВИГАТЕЛЯ | 2006 |

|

RU2317632C1 |

| Электропривод переменного тока | 1984 |

|

SU1464276A1 |

ЧАСТОТНОУПРАВЛЯЕМЫЙ ЭЛЕКТРОПРИВОД ПЕРЕМЕННОГО ТОКА, содержащий асинхронный двигатель с короткозамкнутьом ротором, статорные обмотки которого подключены к выходам преобразователя частоты, снабженного входами для подключения питающей сети, блок задания скорости с информационным каналом и управлякэцщм входом, цифровые фазные распределители импульсов, каждый из которых снабжен информационным каналом, управляющим входом и выходом синхронизации, блок синхронизации с входами для подключения питающей сети, дискретный вычислитель, с информационными кодовыми шинамиг образующими информационный канал, управляющими шинами, образующими управляющий выход, и входом синхронизации, датчики фазных токов, фазных-напряжений и скорости вращения ротора и интегральных аналого-цифровых преобразователей, каждый из которых снабжен информационным каналом, управляющим входом и входом синхронизации, при этом вход каждого из семи интегральных аналого-цифровых преобразователей соединен с выходом одного из датчиков фазных токов, фазных напряжений и скорости вращения ротора. . г /3 13 34 информационные каналы цифровых фазных распределителей импульсов, .блока задания скорости и интегральных аналого-цифровых преобразователей объединены между собой и подключены к информационному каналу дискретного вычислителя, управляющие входы цифровых фазных распределителей импульсов , блока задания скорости и интегральных аналого-цифровых преобразователей объединены между собой и подключены к управляющему выходу дискретного вычислителя, а выход блока синхронизации подключен к входам синхронизации дискретного вычислителя, интегральных аналого-цифровых преобразователей и цифровых фазных распределителей импульсов, йн- i ходы которых соединены с управляющими входами преобразозателя часто- i ты, отличающиеся тем, | что, с целью упрощения, в него внедевы дополнительный десятый интег- С ральныт аналого-цифроаой преобразо ватель, снабженный инфopмaциoнны Jo каналом, управляккдим входом и входом синхронизации,объединенными соответственно с информациоиньями канада лами, управляющими входами и входами i синхронизации остальных девяти интег™ сд оо ральных аналого-цифровых преобразователей,коммутатор,вьпюлкенный в виде двухпозиционного триггерами три интегО) ратора со сбросом,каждый из которых ; снабжен двумя входг ми синхронизаиии подключенными к выходам коммутатора, при этом вход коммутатора соединен с выходом блока синхронизации, вход каждого из интеграторов со сбросом подключен к выходу одного из датчиков фазных токов, а выход каждого из интеграторов со сбросом подключен соответственно к входам восьмого, девятого и десятого аналого-цифровых преобразователей.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент СССР по заявке 3348146/07, кл | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР по заявке 3430071/07, кл | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1984-04-15—Публикация

1982-06-24—Подача