Изобретение относится к импульсной технике, а также к радиоизмерительной технике и может быть использовано в автоматизированных измерительных системах (АИС) динамического и функционального контроля параметров интегральных схем (ИС) различных классов в качестве источника стимулирующих воздействий для испытуемого устройства.

Целью изобретения является снижение мощности при одновременном сохранении высокого быстродействия.

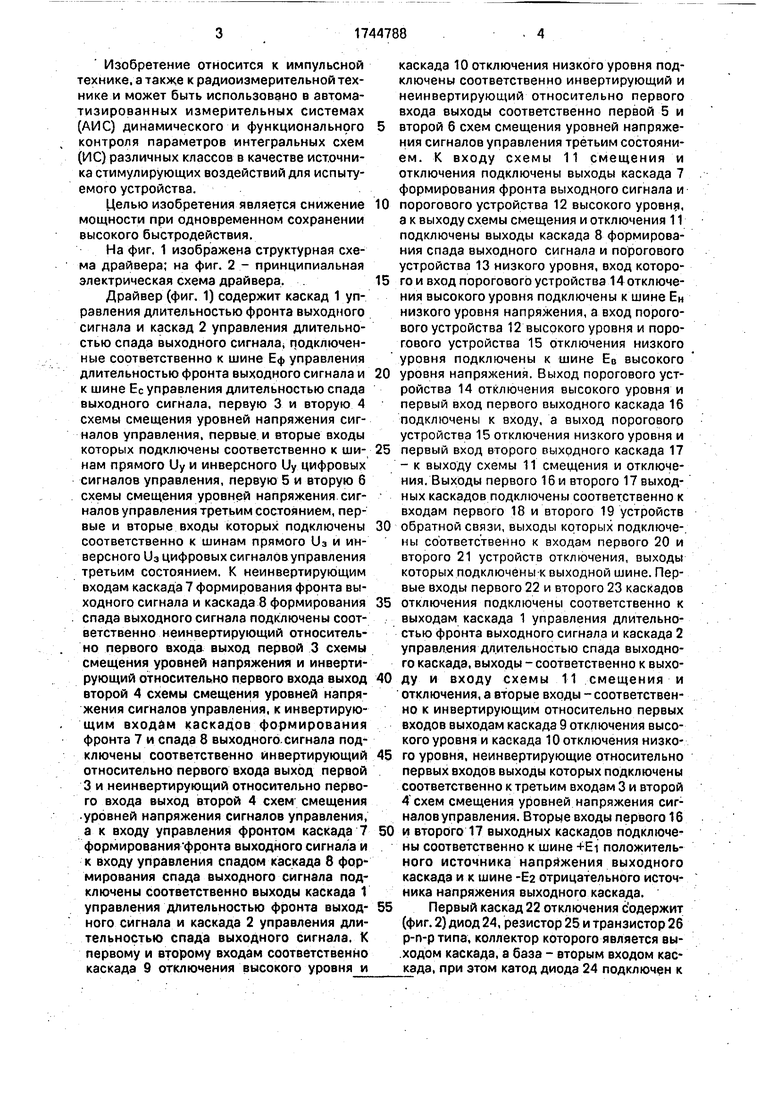

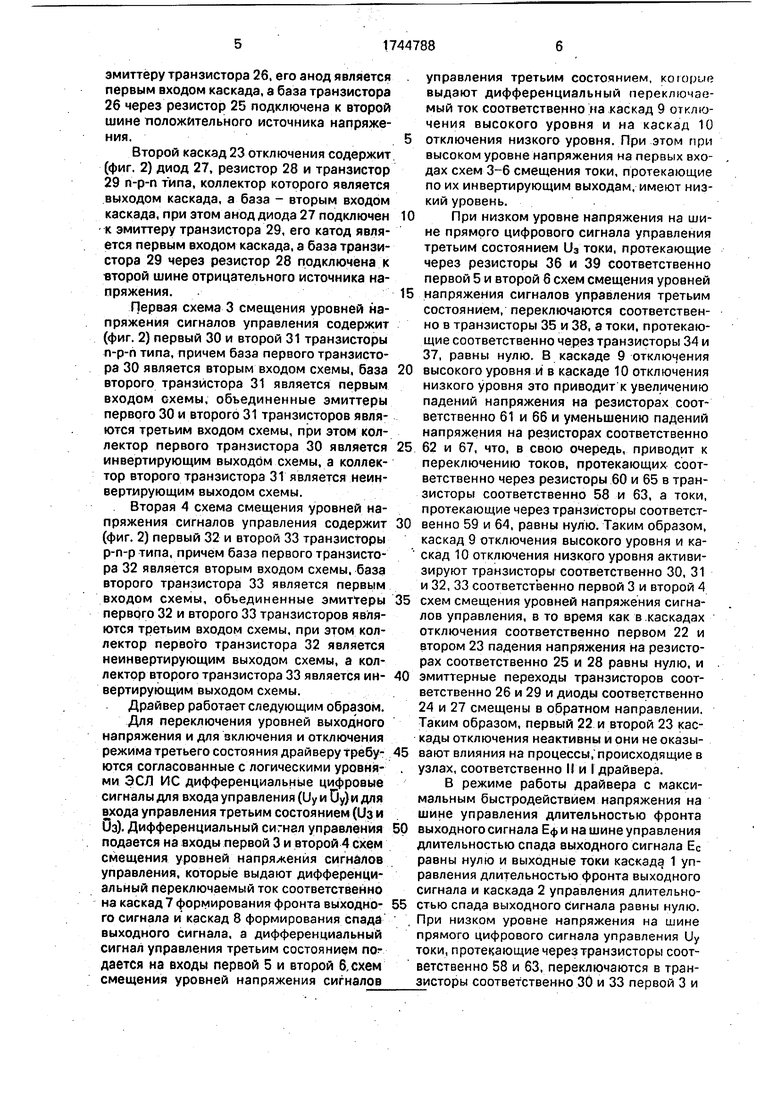

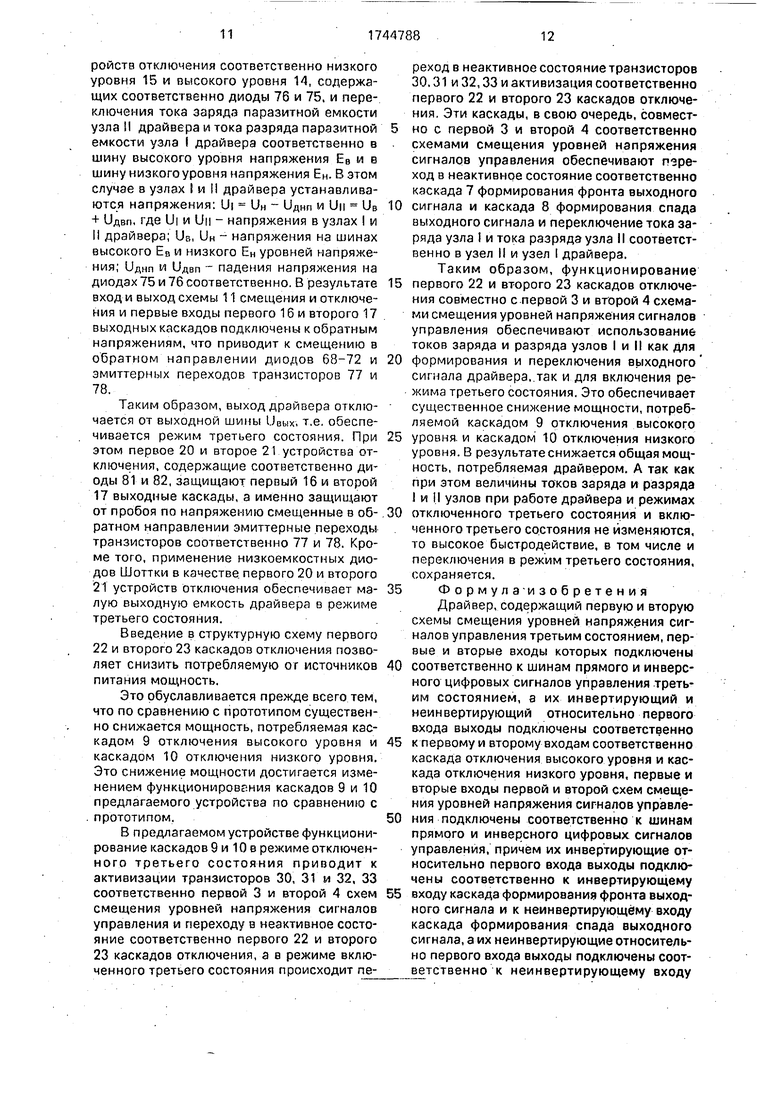

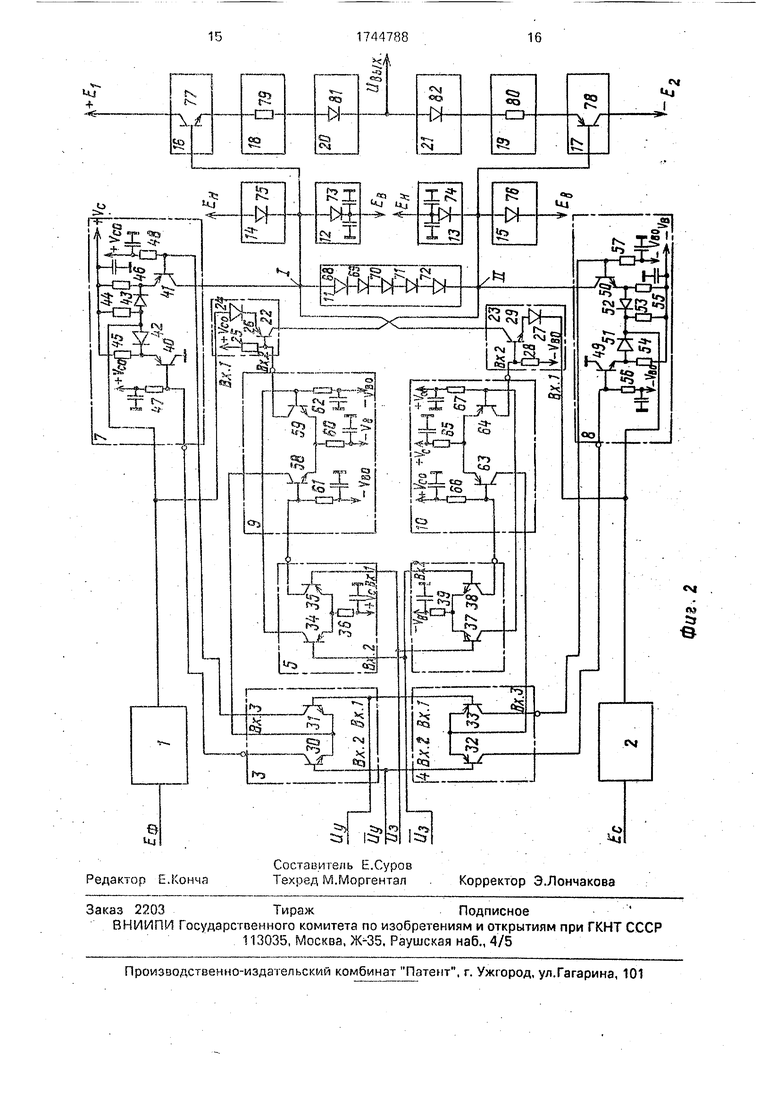

На фиг. 1 изображена структурная схема драйвера; на фиг. 2 - принципиальная электрическая схема драйвера.

Драйвер (фиг. 1) содержит каскад 1 управления длительностью фронта выходного сигнала и каскад 2 управления длительностью спада выходного сигнала, подключенные соответственно к шине Еф управления длительностью фронта выходного сигнала и к шине Ее управления длительностью спада выходного сигнала, первую 3 и вторую 4 схемы смещения уровней напряжения сигналов управления, первые и вторые входы которых подключены соответственно к шинам прямого Uy и инверсного Uy цифровых сигналов управления, первую 5 и вторую б схемы смещения уровней напряжения сигналов управления третьим состоянием, первые и вторые входы которых подключены соответственно к шинам прямого Ua и инверсного Us цифровых сигналов управления третьим состоянием. К неинвертирующим входам каскада 7 формирования фронта выходного сигнала и каскада 8 формирования спада выходного сигнала подключены соответственно неинвертирующий относительно первого входа выход первой 3 схемы смещения уровней напряжения и инвертирующий относительно первого входа выход второй 4 схемы смещения уровней напряжения сигналов управления, к инвертирующим входам каскадов формирования фронта 7 и спада 8 выходного, сигнала подключены соответственно инвертирующий относительно первого входа выход первой 3 и неинвертирующий относительно первого входа выход второй 4 схем смещения уровней напряжения сигналов управления, а к входу управления фронтом каскада 7 формирования фронта выходного сигнала и к входу управления спадом каскада 8 формирования спада выходного сигнала подключены соответственно выходы каскада 1 управления длительностью фронта выходного сигнала и каскада 2 управления длительностью спада выходного сигнала. К первому и второму входам соответственно каскада 9 отключения высокого уровня и

каскада 10 отключения низкого уровня подключены соответственно инвертирующий и неинвертирующий относительно первого входа выходы соответственно первой 5 и

второй 6 схем смещения уровней напряжения сигналов управления третьим состоянием. К входу схемы 11 смещения и отключения подключены выходы каскада 7 формирования фронта выходного сигнала и

0 порогового устройства 12 высокого уровня, а к выходу схемы смещения и отключения 11 подключены выходы каскада 8 формирования спада выходного сигнала и порогового устройства 13 низкого уровня, вход которо5 го и вход порогового устройства 14 отключения высокого уровня подключены к шине Ен низкого уровня напряжения, а вход порогового устройства 12 высокого уровня и порогового устройства 15 отключения низкого уровня подключены к шине Ев высокого

0 уровня напряжения. Выход порогового устройства 14 отключения высокого уровня и первый вход первого выходного каскада 16 подключены к входу, а выход порогового устройства 15 отключения низкого уровня и

5 первый вход второго выходного каскада 17 - к выходу схемы 11 смещения и отключения. Выходы первого 16 и второго 17 выходных каскадов подключены соответственно к входам первого 18 и второго 19 устройств

0 обратной связи, выходы которых подключены соответственно к входам первого 20 и второго 21 устройств отключения, выходы которых подключены выходной шине. Первые входы первого 22 и второго 23 каскадов

5 отключения подключены соответственно к выходам каскада 1 управления длительностью фронта выходного сигнала и каскада 2 управления длительностью спада выходного каскада, выходы - соответственно к выхо0 ду и входу схемы 11 смещения и отключения, а вторые входы -соответственно к инвертирующим относительно первых входов выходам каскада 9 отключения высокого уровня и каскада 10 отключения низко5 го уровня, неинвертирующие относительно первых входов выходы которых подключены соответственно к третьим входам 3 и второй 4 схем смещения уровней напряжения сигналов управления. Вторые входы первого 16

0 и второго 17 выходных каскадов подключены соответственно к шине +Ei положительного источника напряжения выходного каскада и к шине -Еа отрицательного источника напряжения выходного каскада.

5 Первый каскад 22 отключения с одержит (фиг. 2) диод 24, резистор 25 и транзистор 26 p-n-ртипа, коллектор которого является выходом каскада, а база - вторым входом каскада, при этом катод диода 24 подключен к

эмиттеру транзистора 26. его анод является первым входом каскада, а база транзистора 26 через резистор 25 подключена к второй шине положительного источника напряжения.

Второй каскад 23 отключения содержит (фиг. 2) диод 27, резистор 28 и транзистор 29 n-p-п типа, коллектор которого является выходом каскада, а база - вторым входом каскада, при этом анод диода 27 подключен к эмиттеру транзистора 29, его катод является первым входом каскада, а база транзистора 29 через резистор 28 подключена к второй шине отрицательного источника напряжения.

Первая схема 3 смещения уровней напряжения сигналов управления содержит (фиг. 2) первый 30 и второй 31 транзисторы n-p-п типа, причем база первого транзистора 30 является вторым входом схемы, база второго транзистора 31 является первым входом схемы, объединенные эмиттеры первого 30 и второго 31 транзисторов являются третьим входом схемы, при этом коллектор первого транзистора 30 является инвертирующим выходом схемы, а коллектор второго транзистора 31 является неинвертирующим выходом схемы.

Вторая 4 схема смещения уровней напряжения сигналов управления содержит (фиг. 2) первый 32 и второй 33 транзисторы p-n-р типа, причем база первого транзистора 32 является вторым входом схемы, база второго транзистора 33 является первым входом схемы, объединенные эмиттеры nepeqro 32 и второго 33 транзисторов являются третьим входом схемы, при этом коллектор первого транзистора 32 является неинвертирующим выходом схемы, а коллектор второго транзистора 33 является инвертирующим выходом схемы.

Драйвер работает следующим образом.

Для переключения уровней выходного напряжения и для включения и отключения режима третьего состояния драйверу требуются согласованные с логическими уровнями ЭСЛ ИС дифференциальные цифровые сигналы для входа управления (Uy и Оу)и для входа управления третьим состоянием (Оз и Da). Дифференциальный сигнал управления подается на входы первой 3 и второй 4 схем смещения уровней напряжения сигналов управления, которые выдают дифференциальный переключаемый ток соответственно на каскад 7 формирования фронта выходного сигнала и каскад 8 формирования спада выходного сигнала, а дифференциальный сигнал управления третьим состоянием подается на входы первой 5 и второй 6, схем смещения уровней напряжения сигналов

управления третьим состоянием, когорие выдают дифференциальный переключаемый ток соответственно на каскад 9 отключения высокого уровня и на каскад 10 5 отключения низкого уровня. При этом при высоком уровне напряжения на первых входах схем 3-6 смещения токи, протекающие по их инвертирующим выходам, имеют низкий уровень.

0 При низком уровне напряжения на шине прямого цифрового сигнала управления третьим состоянием U3 токи, протекающие через резисторы 36 и 39 соответственно первой 5 и второй б схем смещения уровней

5 напряжения сигналов управления третьим состоянием, переключаются соответственно в транзисторы 35 и 38, а токи, протекающие соответственно через транзисторы 34 и 37, равны нулю. В каскаде 9 отключения

0 высокого уровня и в каскаде 10 отключения низкого уровня это приводит к увеличению падений напряжения на резисторах соответственно 61 и 66 и уменьшению падений напряжения на резисторах соответственно

5 62 и 67, что, в свою очередь, приводит к переключению токов, протекающих соответственно через резисторы 60 и 65 в транзисторы соответственно 58 и 63, а токи, протекающие через транзисторы соответст0 венно 59 и 64, равны нулю. Таким образом, каскад 9 отключения высокого уровня и каскад 10 отключения низкого уровня активизируют транзисторы соответственно 30, 31 и 32, 33 соответственно первой 3 и второй 4

5 схем смещения уровней напряжения сигналов управления, в то время как в каскадах отключения соответственно первом 22 и втором 23 падения напряжения на резисторах соответственно 25 и 28 равны нулю, и

0 эмиттерные переходы транзисторов соответственно 26 и 29 и диоды соответственно 24 и 27 смещены в обратном направлении. Таким образом, первый 22 и второй 23 каскады отключения неактивны и они не оказы5 вают влияния на процессы, происходящие в . узлах, соответственно II и I драйвера.

В режиме работы драйвера с максимальным быстродействием напряжения на шине управления длительностью фронта

0 выходного сигнала Еф и на шине управления длительностью спада выходного сигнала Ее равны нулю и выходные токи каскада 1 управления длительностью фронта выходного сигнала и каскада 2 управления длительно5 стью спада выходного сигнала равны нулю. При низком уровне напряжения на шине прямого цифрового сигнала управления Uy токи, протекающие через транзисторы соответственно 58 и 63, переключаются в транзисторы соответственно 30 и 33 первой 3 и

второй 4 схем смещения уровней напряжения сигналов управления, а токи, протекающие через транзисторы соответственно 31 и 32, равны нулю, В каскаде 7 формирования фронта выходного сигнала и в каскаде 8 формирования спада выходного сигнала это приводит к увеличению падений напряжений на резисторах соответственно 47, 45 и 57, 55 и уменьшению падений напряжения на резисторах соответственно 48, 46 и 56, 54. В результате токи, протекающие через резисторы, соответственно 44 и 53 переключаются через диоды соответственно 42 и 52 в транзисторы соответственно 40 и 50. При этом диоды соответственно 43 и 51 смещены в обратном направлении и через транзисторы соответственно 41 и 49 протекают токи резисторов соответственно 46 и 54. Величины токов, протекающих через резисторы соответственно 44,45, 46 и 53, 54, 55, определяются величинами их сопротивлений, напряжениями источников питания каскадов драйвера соответственно +VC, +VCo и -Vet - VBO, причем |+Vc I 1+ Vco I и l-Ve l I -V/Bol, а также падениями напряжений на диодах соответственно 42,43 и 51, 52. эмиттерных переходах транзисторов соответственно 40, 41 и 49, 50. При этом ток, протекающий через транзистор 46, обеспечивает рабочий режим схемы 11 смещения и отключения, содержащей диоды 68-72, а именно обеспечивает падение напряжения между узлами I и II драйвера и поддерживает его постоянным, а также обеспечивает входной ток смещений первого выходного каскада 16, содержащего транзистор 77. Ток, протекающий через резистор 53, обеспечивает разряд паразитной емкости узла II, а также обеспечивает через низкое сопротивление смещенных в прямом направлении диодов 68-72 схемы 11 смещения и отключения разряд паразитной емкости узла I. В результате разряда паразитных емкостей узлов t и II драйвера напряжение в этих узлах уменьшается. Уменьшение напряжения в узле II происходит до открывания порогового устройства низкого уровня 13, содержащего диод 74. В результате большая часть тока, протекающего через . транзистор 50. переключается через диод 74 в шину низкого уровня напряжения Ен, а узле U устанавливается напряжение UH - Удн, где UH - напряжение на шину низкого уровня напряжения Ен; 1)Дн - падение напряжения на диоде 74, а меньшая часть тока обеспечивает рабочий режим схемы 11 смещения и отключения и входной ток смещения второго выходного каскада 17, содержащего транзистор 78. Так как падение напряжения между узлами I и II драйвера определяется током, протекающим через резистор 46, и не зависит от тока, протекающего через транзистор 50, то между узлами I и II драйвера поддерживается

постоянное напряжение, которое обеспечивает режим работы первого 16 и второго 17 выходных каскадов, содержащих соответственно транзисторы 77 и 78 по напряжению. Первое 18 и второе 19 устройства обратной

0 связи, содержащее соответственно резисторы 79 и 80, а также первое 20 и второе 21 устройства отключения, содержащие соответственно диоды 81 и 82, обеспечивают ток покоя транзисторов первого 16 и второго 17

5 выходных каскадов. Причем изменения напряжений в узлах I и I драйвера передаются на выходную шину Увых. Таким образом, на выходной шине драйвера формируется напряжение низкого уровня,

0 При высоком уровне напряжения на ши- не прямого цифрового сигнала управления токи, протекающие через транзисторы 58 и 63, переключаются в транзисторы соответственно 31 и 32 первой 3 и второй 4 схем

5 смещения уровней напряжения сигналов управления, а токи, протекающие через транзисторы соответственно 30 и 33, равны нулю. В каскаде 7 формирования фронта выходного сигнала и в каскаде 8 формиро0 вания спада выходного сигнала это приводит к увеличению падений напряжения на резисторах соответственно 48, 46 и 56, 54 и к уменьшению падений напряжения на резисторах соответственно 47. 45 и 57. 55. В

5 результате токи, протекэкщие через резисторы соответственно 44 и 53. переключаются через диоды соответственно 43 и 51 в транзисторы соответственно 41 и 49. При этом диоды соответственно 42 и 52 смеще0 ны в обратном направлении и через транзисторы соответственно 40 и 50 протекают токи резисторов соответственно 45 и 55. Причем ток, протекающий через резистор 55, обеспечивает рабочий режим схемы 11

5 смещения и отключения, содержащей диоды 68-72, а именно обеспечивает падение напряжения между узлами I и II драйвера и поддерживает его постоянным, а также обеспечивает входной ток смещения второ0 го выходного каскада 17, содержащего транзистор 78. Ток. протекающий через резистор 44, обеспечивает заряд паразитной емкости узла I, а также обеспечивает через низкое сопротивление смещенных в пря5 мом направлении диодов 68-72 схемы 11 смещения и отключения заряд паразитной емкости узла II. В результате заряда паразитных емкостей узлов I и II драйвера напря- жения в этих узлах увеличиваются. Увеличение напряжения в узле I происходит

до открывания порогового устройства 12. высокого уровня, содержащего диод 73. В результате большая часть тока, протекающего через транзистор 41, переключается через диод 73 в шину высокого уровня на- пряжения Ев, и в узле I драйвера устанавливается напряжение UB + идв, где UB - напряжение на шине высокого уровня напряжения Ев; 11дв - падение напряжения на диоде 73, а меньшая часть тока обеспечива- ет рабочий режим схемы 11 смещения и отключения и входной ток смещения первого выходного каскада 16, содержащего транзистор 77. Так как падение напряжения между узлами I и II драйвера определяется током, протекающим через резистор 55i и не зависит от тока, протекающего через транзистор 41, то между узлами I и II драйвера поддерживается постоянное напряжение, которое обеспечивает режим работы первого 16 и второго 17 выходных каскадов, содержащих соответственно транзисторы 77 и 78 по напряжению. Первое 18 и второе 19 устройства обратной связи, содержащие соответственно резисторы 79 и 80, также первое 20 и второе 21 устройства отключения, содержащие соответственно диоды 81 и 82, обеспечивают ток покоя транзисторов первого 16 и второго 17 выходных каскадов. Причем изменения напряжений в узлах I и II драйвера передается на выходную шину Квых и на выходной шине драйвера формируется напряжение высокого уровня.

Управление длительностями фронта и спада выходного сигнала драйвера осуществляется следующим образом.

При ненулевых напряжениях на шине управления длительностью фронта выходного сигнала Еф и на шине управления дли- тельностью спада выходного сигнала Ее выходные токи каскада 1 управления длительностью фронта выходного сигнала и каскада 2 управления длительностью спада выходного сигнала не равны нулю. При этом выходные токи этих каскадов являются соответственно втекающим и вытекающим токами. В результате уменьшается ток, переключаемый через диоды 42 и 43 в кас- каде 7 формирования фронта выходного сигнала, и уменьшается ток, переключав- мый через диоды 51 и 52 в каскаде 8 формирования спада выходного сигнала, что, в свою очередь, приводит к уменьшению величин токов заряда и разряда паразитных емкостей узлов I и II драйвера. Поэтому ско- рости измерения напряжений в узлах I и II драйвера уменьшаются, а значит, увеличиваются длительности фронта и спада выходного сигнала драйвера.

При высоком уровне напряжения на шине прямого цифрового сигнала управления третьим состоянием 1)з токи, протекающие через резисторы 36 и 39 соответственно первой 5 и второй 6 схем смещения уровней напряжения сигналов управления третьим состоянием, переключается соответственно в транзисторы 34 и 37, а токи, протекающие соответственно через транзисторы 35 и 38, равны нулю. В каскаде 9 отключения высокого уровня и в каскаде 10 отключения низкого уровня это приводит- к увеличению падений напряжения на резисторах соответственно 52 и 67 и уменьшению падений напряжений на резисторах соответственно 61 и 66, что в свою очередь, приводит к переключению токов, протекающих соответственно через резисторы 60 и 65 в транзисторы соответственно 59 и 64, а токи, протекающие через транзисторы соответственно 58 и 63, равны нулю. Таким образом, каскад 9 отключения высокого уровня и каскад 10 отключения низкого уровня переводят транзисторы первой 3 и второй 4 схем смещения уровней напряжения сигналов управления соответственно 30, 31 и 32, 33 в неактивное состояние, что, в свою очередь, приводит в каскаде 7 формирования фронта выходного сигнала и в каскаде 8 формирования спада выходного сигнала к уменьшению падений напряжения на резисторах соответственно47,45,48, 46 и56,54,57,55, а в первом 22 и втором 23 каскадах отключения увеличиваются падения напряжения на резисторах соответственно 25 и 28, что, в свою очередь, приводит к смещению в прямом направлении эмиттерных переходов транзисторов соответственно 26 и 29, и диодов соответствен но 24 и 27. В результате в каскаде 7 формирования фронта выходного сигнала и в каскаде 8 формирования спада выходного сигнала диоды соответственно 42, 43 и 51, 52 смещены в обратном направлении и через транзисторы соответственно 40, 41 и 49, 50 протекают токи резисторов соответственно 45,46 и 54, 55, а токи, протекающие через резисторы соответственно 44 и 53 переключаются соответственно через первый 22 и второй 23 каскады отключения соответственно во И и в I узлы драйвера. Токи, протекающие через резисторы соответственно 44 и 53, брльше токов, протекающих через резисторы соответственно 46 и 55. Разностью токов, протекающих через резисторы соответственно 44, 55 и 53, 46, происходит соответственно заряд паразитной емкости узла II драйвера и разряд паразитной емкости узла I драйвера. Изменение напряжения в этих узлах происходит до открывания пороговых устройств отключения соответственно низкого уровня 15 и высокого уровня 14, содержащих соответственно диоды 76 и 75, и переключения тока заряда паразитной емкости узла II драйвера и тока разряда паразитной емкости узла драйвера соответственно в шину высокого уровня напряжения Ев и в шину низкого уровня напряжения Еи. В этом случае в узлах I и I драйвера устанавливаются напряжения: Ui Un - 11днп и Un UB + 11двп, где Ui и Un - напряжения в узлах I и II драйвера; Us, UH напряжения на шинах высокого Ев и низкого Ен уровней напряжения; Удил и идвп - падения напряжения на диодах 75 и 76 соответственно. В результате вход и выход схемы 11 смещения и отключения и первые входы первого 1 б и второго 17 выходных каскадов подключены к обратным напряжениям, что приводит к смещению в обратном направлении диодов 68-72 и эмиттерных переходов транзисторов 77 и 78.

Таким образом, выход драйвера отключается от выходной шины ивых. т.е. обеспечивается режим третьего состояния. При этом первое 20 и второе 21 устройства отключения, содержащие соответственно диоды 81 и 82, защищают первый 16 и второй 17 выходные каскады, а именно защищают от пробоя по напряжению смещенные в обратном направлении эмиттерные переходы транзисторов соответственно 77 и 78. Кроме того, применение низкоемкостных диодов Шоттки в качестве первого 20 и второго

21устройств отключения обеспечивает малую выходную емкость драйвера в режиме третьего состояния.

Введение в структурную схему первого

22и второго 23 каскадов отключения позволяет снизить потребляемую or источников питания мощность.

Это обуславливается прежде всего тем, что по сравнению с прототипом существенно снижается мощность, потребляемая каскадом 9 отключения высокого уровня и каскадом 10 отключения низкого уровня. Это снижение мощности достигается изменением функционирования каскадов 9 и 10 предлагаемого устройства по сравнению с прототипом.

В предлагаемом устройстве функционирование каскадов 9 и 10 в режиме отключенного третьего состояния приводит к активизации транзисторов 30, 31 и 32, 33 соответственно первой 3 и второй 4 схем смещения уровней напряжения сигналов управления и переходу в неактивное состояние соответственно первого 22 и второго

23каскадов отключения, а в режиме включенного третьего состояния происходит переход в неактивное состояние транзисторов 30,31 и 32,33 и активизация соответственно первого 22 и второго 23 каскадов отключения. Эти каскады, в свою очередь, совместно с первой 3 и второй 4 соответственно схемами смещения уровней напряжения сигналов управления обеспечивают пэре- ход в неактивное состояние соответственно каскада 7 формирования фронта выходного

0 сигнала и каскада 8 формирования спада выходного сигнала и переключение тока заряда узла I и тока разряда узла II соответственно в узел II и узел I драйвера.

Таким образом, функционирование

5 первого 22 и второго 23 каскадов отключения совместно с первой 3 и второй 4 схемами смещения уровней напряжения сигналов управления обеспечивают использование токов заряда и разряда узлов I и II как для

0 формирования и переключения выходного сигнала драйвера, так и для включения режима третьего состояния. Это обеспечивает существенное снижение мощности, потребляемой каскадом 9 отключения высокого

5 уровня и каскадом 10 отключения низкого уровня. В результате снижается общая мощность, потребляемая драйвером. А так как при этом величины токов заряда и разряда I и II узлов при работе драйвера и режимах

0 отключенного третьего состояния и включенного третьего состояния не изменяются, то высокое быстродействие, в том числе и переключения в режим третьего состояния, сохраняется.

5 Формула изобретения

Драйвер, содержащий первую и вторую схемы смещения уровней напряжения сигналов управления третьим состоянием, первые и вторые входы которых подключены

0 соответственно к шинам прямого и инверсного цифровых сигналов управления третьим состоянием, а их инвертирующий и неинвертирующий относительно первого входа выходы подключены соответственно

5 к первому и второму входам соответственно каскада отключения высокого уровня и каскада отключения низкого уровня, первые и вторые входы первой и второй схем смещения уровней напряжения сигналов управле0 ния подключены соответственно к шинам прямого и инверсного цифровых сигналов управления, причем их инвертирующие относит ельно первого входа выходы подключены соответственно к инвертирующему

5 входу каскада формирования фронта выходного сигнала и к неинвертирующему входу каскада формирования спада выходного сигнала, а их неинвертирующие относительно первого входа выходы подключены соответственно к неинвертирующему входу

каскада формирования фронта выходного сигнала и к инвертирующему входу каскада формирования спада выходного сигнала, входы каскада управления длительностью фронта выходного сигнала и каскада управления длительностью спада выходного сигнала подключены соответственно к шине управления длительностью фронта выходного сигнала и к шине управления длительностью спада выходного сигнала, а их выходы подключены соответственно к третьему входу каскада формирования фронта выходного сигнала и к третьему входу каскада формирования спада выходного сигнала, выходы каскада формирования фронта выходного сигнала, порогового устройства высокого уровня и порогового устройства отключения высокого уровня объединены с первым входом первого выходного каскада и подключены к входу- схемы смещения и отключения, а выходы каскада формирования спада выходного сигнала, пороговогр устройства низкого уровня и порогового устройства отключения низкого уровня объединены с первым входом второго выходного каскада и подключены к выходу схемы смещения и отключения, при этом входы порогового устройства высокого уровня и порогового устройства отключения низкого уровня подключены к шине высокого уровня напряжения, а входы порогового устройства низкого уровня и порогового устройства отключения высокого уровня подключены к шине низкого уровня напряжения, выходы первого и второго устройств отключения подключены к выходной шине, а между их входами и выходами соответственно первого и второго выходных каскадов включены соответственно первое- и второе устройства обратной связи, причем вторые входы первого и второго выходных каскадов подключены соответственно к шине положительного источника напряжения выходного каскада и к шине отрицательного источника напряжения выходного каскада, отличающийся тем, что, с целью снижения потребляемой мощности при сохранении быстродействия, в него введены первый и второй каскады отключения, первые входы которых подключены соответственно к выходу каскада управления длительностью фронта выходного сигнала и

выходу каскада управления длительностью спада выходного сигнала, вторые входы - к инвертирующим относительно первого входа выходам соответственно каскада отклю5 чения высокого уровня и каскада отключения низкого уровня, а выходы - к первым входам соответственно второго и первого выходных каскадов, при этом неинвертирующие относительно первого входа

0 выходы каскада отключения высокого уровня и каскада отключения низкого уровня подключены соответственно к третьим входам соответственно первой и второй схем смещения уровней напряжения сигналов

5 управления, при этом первый каскад отключения содержит диод, резистор и транзистор p-n-р типа, причем коллектор транзистора является выходом каскада, база транзистора - вторым входом каскада, а

0 анод диода - первым входом каскада, при этом катод диода подключен к эмиттеру транзистора, база которого Через резистор подключена к шине положительного источника напряжения, а второй каскад отключе5 ния содержит диод, резистор и транзистор n-p-n-типа, причем коллектор транзистора является выходом.каскада, база транзистора - вторым входом каскада, а катод диода

-первым входом каскада, при этом анод 0 диода подключен к эмиттеру транзистора,

база которого через резистор подключена к шине отрицательного источника напряжения, первая схема смещения уровней напряжения сигналов управления содержит

5 первый и второй транзисторы п-р-п-типа, причем база первого и второго транзисторов являются соответственно вторым и первым входами схемы, объединенные эмиттеры транзисторов - третьим входом

0 схемы, а коллекторы первого и второго тран- - Зисторов- соответственно инвертирующим и неинвертирующим выходами схемы, а вторая схема смещения уровней напряжения сигналов управления содержит первый и

5 второй транзисторы p-n-p-типэ, причем базы первого и второго транзисторов являются соответственно вторым и первым входами схемы, объединенные эмиттеры транзисторов - третьим входом схемы, а

0 коллекторы первого и второго транзисторов

-соответственно неинвертирующим и инвертирующим выходами схемы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Ключевое устройство | 2019 |

|

RU2749278C1 |

| Ключевой регулятор напряжения | 2018 |

|

RU2692699C1 |

| МОДУЛЬ ВЫСОКОВОЛЬТНОГО КЛЮЧЕВОГО УСИЛИТЕЛЯ МОЩНОСТИ | 2018 |

|

RU2716041C1 |

| Ключевой стабилизатор напряжения с трансформаторной развязкой | 2023 |

|

RU2814894C1 |

| СПОСОБ УСИЛЕНИЯ МОЩНОСТИ НА GaN СВЧ-ТРАНЗИСТОРАХ И ИМПУЛЬСНЫЙ СВЧ-УСИЛИТЕЛЬ МОЩНОСТИ | 2012 |

|

RU2501155C1 |

| МАЛОГАБАРИТНЫЙ ШИРОТНО-ИМПУЛЬСНЫЙ МОДУЛЯТОР, УСТОЙЧИВЫЙ К ВОЗДЕЙСТВИЮ ИОНИЗИРУЮЩИМ ИЗЛУЧЕНИЕМ | 2013 |

|

RU2557479C2 |

| ИСТОЧНИК ПИТАНИЯ ДЛЯ ЭЛЕКТРОЛЮМИНЕСЦЕНТНОЙ ПАНЕЛИ | 2001 |

|

RU2210120C1 |

| Управляемый ключевой преобразователь напряжения | 2019 |

|

RU2736058C1 |

| Импульсный генератор инфранизкой частоты | 1979 |

|

SU793303A1 |

| Фазоимпульсный преобразователь | 2023 |

|

RU2821269C1 |

Изобретение относится к импульсной технике, а также к радиоизмерительной технике и может быть использовано в автоматизированных измерительных системах в качестве источника стимулирующих воздействий и регулируемых импульсных сигналов. Целью изобретения является снижение потребляемой мощности при одновременном сохранении быстродействия. Драйвер содержит каскады 1 и 2 управления длительностью фронта и спада выходного сигнала, первую и вторую схемы 3 и 4 смещения уровней напряжения сигналов управления, первую и вторую схемы 5 и 6 смещения уровней напряжения сигналов управления третьим состоянием, каскады 7 и 8 формирования фронта и среза выходного сигнала, каскады 9 и 10 отключения высокого уровня и низкого уровня, схему 11 смещения и отключения, пороговые устройства 12 и 13 высокого и низкого уровней, пороговые устройства 14 и 15 отключения высокого и низкого уровней, первый и второй выходные каскады 16 и 17. первое и второе устройства 18 и 19 обратной связи, первое и второе устройства 20 и 21 отключения. Введение первого и второго каскадов 22, 23 отключения позволяет снизить общую мощность, а т.к. величины токов заряда и разряда I и I узлов в режимах отключения третьего состояния и включения третьего состояния не из- меняются, то высокое быстродействие сохраняется. 2 ил. -N XI со оо Фп1 ///

| Устройство формирования импульсов | 1986 |

|

SU1347170A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Патент США № 4507576, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для установки двигателя в топках с получающими возвратно-поступательное перемещение колосниками | 1917 |

|

SU1985A1 |

Авторы

Даты

1992-06-30—Публикация

1990-01-05—Подача