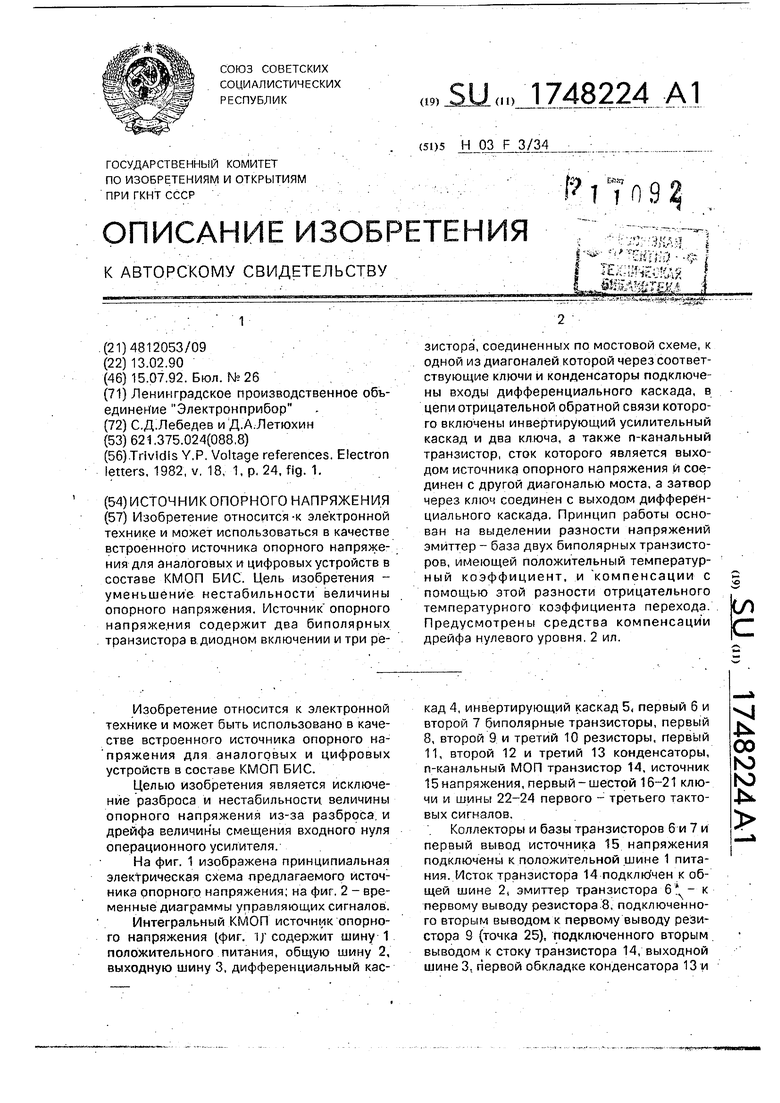

первому выводу резистора 10. Первый вы- ход ключа 16 соединен с точкой 25 соединения резисторов 8 и 9, а второй выход - с первой обкладкой конденсатора 11 и первым выходом ключа 17, вторым выходом подключенного к точке 26 соединения второго вывода резистора 10, эмиттера транзистора 7 и первой обкладки конденсатора 12, вторая обкладка которого подключена к инвертирующему входу дифференциального усилителя 4 и первому выходу ключа 18, второй вывод которого подключен к второму выводу источника 15 напряжения Первый выход ключа 19 соединен с выходом инвертирующего каскада 5, а второй выход

-с второй обкладкой конденсатора 11 и неинвертирующим входом дифференциального каскада 4. Первый выход ключа 20 соединен с входом инвертирующего каскада 5, а второй выход - с выходом дифференциального каскада 4 и первым выходом ключа 21, второй выход которого подключен к затвору транзистора 14 и второй обкладке конденсатора 13. Шина 22 тактового сигнала подключена к управляющим входам ключей 17-20, шина 23 - к управляющему входу ключа 16, а шина 24-к управляющему входу ключа 21

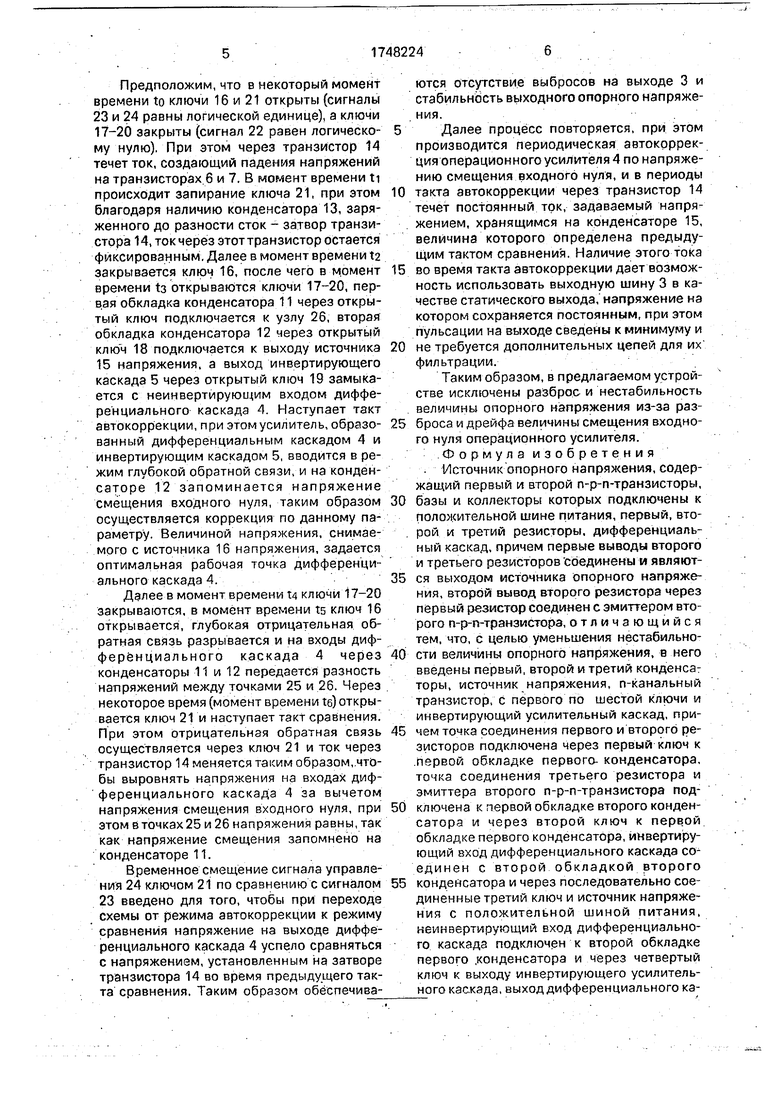

Источник опорного напряжения работает следующим образом.

Принцип работы устройства основан на выделении разности напряжений эмиттер - база у двух биполярных транзисторов, имеющей положительный температурный коэффициент, и компенсации с помощью этой разности, умноженной на величину отношения второго и первого резисторов, отрицательного температурного коэффициента р-п-перехода

Два вертикальных биполярных п-р-п- транзисторз 6 и 7 (фиг 1) получены тем же технологическим путем, что и стандартные КМОП элементы (коллектором является п- подложка, базами - р-карманы, а эмиттерами

-области n-диффузии в соответствующих карманах), при этом транзисторы выполнены таким образом, что площадь эмиттера транзистора б намного больше площади эмиттера транзистора 7.

Температурный коэффициент напряжения эмиттер,- база транзистора 7 tkU -2,1 mB/град при типичном значении этого напряжения UBEO 650 мВ (для транзистора с площадью эмиттерэ S 400 мк , тока через него 1 25 мкА и То - 300 К).

Чтобы скомпенсировать данный отрицательный tkU, на резисторе 10 выделяется напряжение, имеющее равный ему по модулю положительный tkU. Для этого резисторы 9 и 10 выбираются одинаковыми по

номиналу, а потенциалы точек 25 и 26 поддерживаются равными друг другу. Через транзисторы 6 и 7 протекают одинаковые по значению токи, а на резисторе 8 формируется разность напряжений, которая определяется как

UBEI - UB2 (kT/q)ln(|i/j2) (kT/q)ln((I/Si)/(l /S2)) (kT/q)ln(S2/Si),(1)

где

0I(UBE1-UBE2)/R2,(2)

UBE, J1. Si и UBE2, J2,82 - соответственно напряжение эмиттер - база, плотность тока и площадь эмиттера транзисторов 6 и 7; - ток через эти транзисторы.

5 Таким образом, на выходной шине 3 получено напряжение относительно положительной шины питания

Uon UBE2 + (R2/Ri)(kT/Q)ln(S2/Si) (3) где Ri - сопротивление резистора 10;

0R2 - сопротивление резистора 8.

Зная величину tkU для UBE2, подбором отношения Rz/Ri можно полностью скомпенсировать отрицательный tkU получив таким образом постоянное и термонезави5 симое напряжение на выходе 3 опорного источника (относительно шины положительного питания) При этом

(R2/R2Xk/q)ln(S2/Si) -dUBE2/dT, (4) Подставив (4) в (3), получаем

0 Uon UBEI + (Ug - UBE i) + 3(kTo)/q) Ug + (3kTo/q) 1205 + 78 1283 (мВ)(5)

где Ug - напряжение запрещенной зоны кремния;

kTo/q - температурный потенциал (26

5 мВ 300 К).

Напряжение Uon близко к напряжению запрещенной зоны кремния (Ug 1205 мВ). При этом для соотношения площадей транзистора (S2/SO 10 получаем

0 (R2/Rl) 633/(,3) 10,6.(6)

Однако КМОП операционные усилители имеют напряжения смещения входного нуля порядка +/-10 мВ. С учетом напряжения смещения нуля операционного усилителя

5 получаем, что опорное напряжение имеет разбросы 1283 +/-106 (мВ), при этом температурный дрейф величины опорного напряжения определяется температурным дрейфом напряжения смещения входного

0 нуля операционного усилителя, умноженным на отношение R2/Ri.

Для. компенсации напряжения смещения входного нуля операционного усилителя в предлагаемом устройстве введен

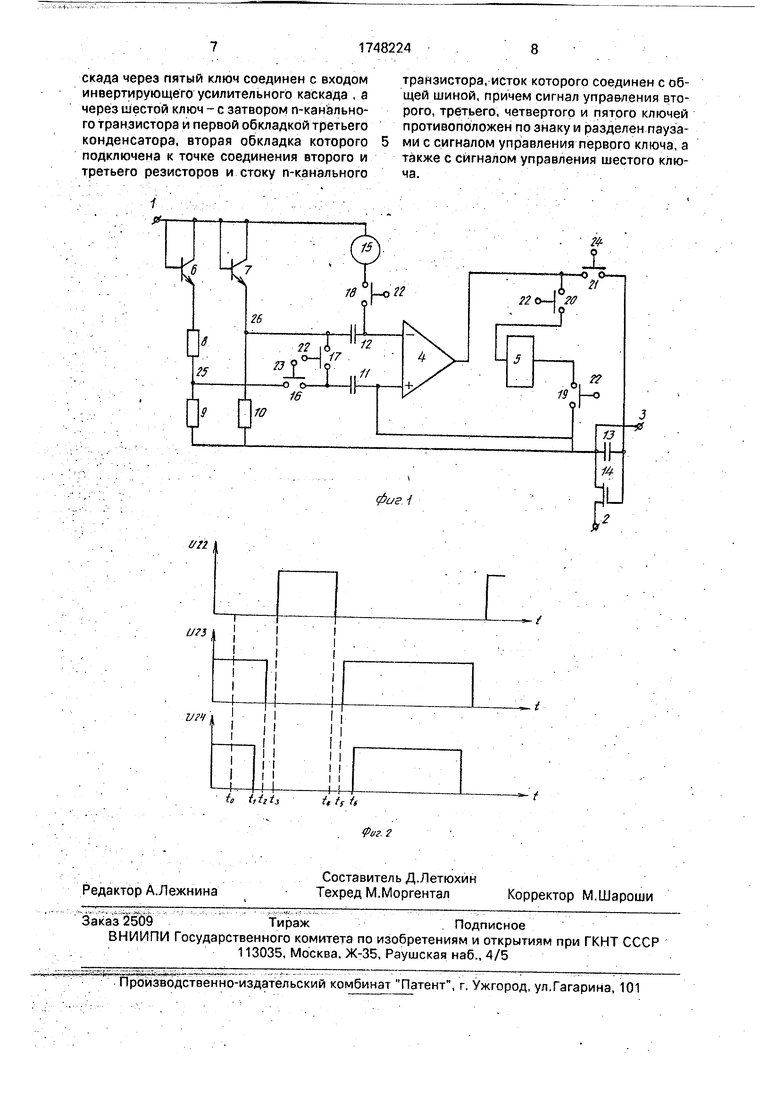

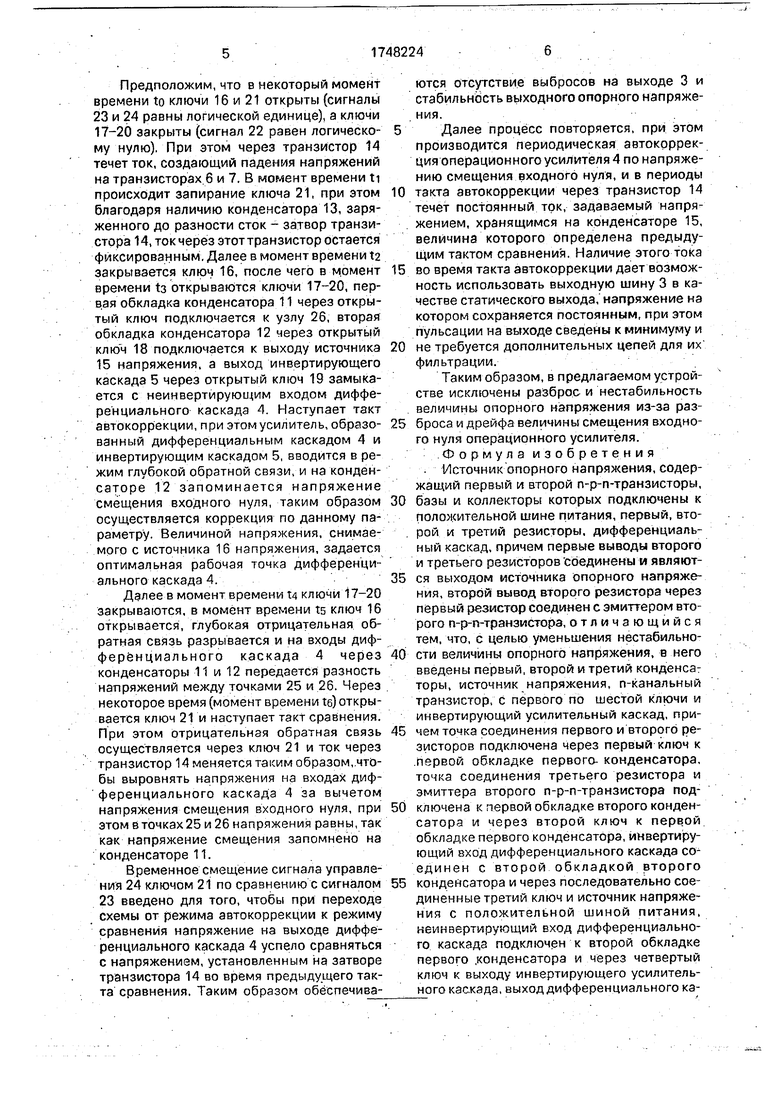

5 режим автокоррекции, при этом работа устройства делится на два такта, такт автокоррекции и такт сравнения (фиг. 2). Нумерация тактирующих сигналов на фиг. 3 совпадает с нумерацией соответствующих тактовых шин.

Предположим, что в некоторый момент времени to ключи 16 и 21 открыты (сигналы 23 и 24 равны логической единице), а ключи 17-20 закрыты (сигнал 22 равен логическо- му нулю). При этом через транзистор 14 течет ток, создающий падения напряжений на транзисторах 6 и 7. В момент времени ti происходит запирание ключа 21, при этом благодаря наличию конденсатора 13, заряженного до разности сток - затвор транзистора 14, токчерез этот транзистор остается фиксированным. Далее в момент времени t2 закрывается ключ 16, после чего в момент времени т.з открываются ключи 17-20, первая обкладка конденсатора 11 через открытый ключ подключается к узлу 26, вторая обкладка конденсатора 12 через открытый ключ 18 подключается к выходу источника 15 напряжения, а выход инвертирующего каскада 5 через открытый ключ 19 замыкается с неинвертирующим входом дифференциального каскада А Наступает такт автокоррекции, при этом усилитель, образо- ванный дифференциальным каскадом 4 и инвертирующим каскадом 5, вводится в режим глубокой обратной связи, и на конденсаторе 12 запоминается напряжение смещения входного нуля, таким образом осуществляется коррекция по данному параметру. Величиной напряжения, снимаемого с источника 16 напряжения, задается оптимальная рабочая точка дифференциального каскада 4.

Далее в момент времени t4 ключи 17-20 закрываются, в момент времени ts ключ 16 открывается, глубокая отрицательная обратная связь разрывается и на входы дифференциального каскада 4 через конденсаторы 11 и 12 передается разность напряжений между точками 25 и 26. Через некоторое время (момент времени te) открывается ключ 21 и наступает такт сравнения. При этом отрицательная обратная связь осуществляется через ключ 21 и ток через транзистор 14 меняется таким образом, чтобы выровнять напряжения на входах дифференциального каскада 4 за вычетом напряжения смещения входного нуля, при этом вточках25 и 26 напряжения равны, так как напряжение смещения запомнено на конденсаторе 11.

Временное смещение сигнала управления 24 ключом 21 по сравнению с сигналом 23 введено для того, чтобы при переходе схемы от режима автокоррекции к режиму сравнения напряжение на выходе дифференциального каскада 4 успело сравняться с напряжением, установленным на затворе транзистора 14 во время предыдущего такта сравнения. Таким образом обеспечиваются отсутствие выбросов на выходе 3 и стабильность выходного опорного напряжения.

Далее процесс повторяется, при этом производится периодическая автокоррекция операционного усилителя 4 по напряжению смещения входного нуля, и в периоды такта автокоррекции через транзистор 14 течет постоянный ток, задаваемый напряжением, хранящимся на конденсаторе 15, величина которого определена предыдущим тактом сравнения. Наличие этого тока во время такта автокоррекции дает возможность использовать выходную шину 3 в качестве статического выхода, напряжение на котором сохраняется постоянным, при этом пульсации на выходе сведены к минимуму и не требуется дополнительных цепей для их фильтрации.

Таким образом, в предлагаемом устройстве исключены разброс и нестабильность величины опорного напряжения из-за разброса и дрейфа величины смещения входного нуля операционного усилителя.

Формула изобретения

Источник опорного напряжения, содержащий первый и второй п-р-п-транзисторы, базы и коллекторы которых подключены к положительной шине питания, первый, второй и третий резисторы, дифференциальный каскад, причем первые выводы второго и третьего резисторов соединены и являются выходом источника опорного напряжения, второй вывод второго резистора через первый резистор соединен с эмиттером второго n-p-n-транзисторз, отличающийся тем, что, с целью уменьшения нестабильности величины опорного напряжения, в него введены первый, второй и третий конденсаторы, источник напряжения, п-канальный транзистор, с первого по шестой ключи и инвертирующий усилительный каскад, причем точка соединения первого и второго резисторов подключена через первый ключ к первой обкладке первого- конденсатора, точка соединения третьего резистора и эмиттера второго n-p-n-транзистора подключена к первой обкладке второго конденсатора и через второй ключ к первой обкладке первого конденсатора, инвертирующий вход дифференциального каскада соединен с второй обкладкой второго конденсатора и через последовательно соединенные третий ключ и источник напряжения с положительной шиной питания, неинвертирующий вход дифференциального каскада подключен к второй обкладке первого конденсатора и через четвертый ключ к выходу инвертирующего усилительного каскада, выход дифференциального каскада через пятый ключ соединен с входом инвертирующего усилительного каскада , а через шестой ключ - с затвором п-канально- го транзистора и первой обкладкой третьего конденсатора, вторая обкладка которого подключена к точке соединения второго и третьего резисторов и стоку п-канального

транзистора, исток которого соединен с общей шиной, причем сигнал управления второго, третьего, четвертого и пятого ключей противоположен по знаку и разделен паузами с сигналом управления первого ключа, а также с сигналом управления шестого ключа.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО АВТОКОРРЕКЦИИ НУЛЯ ОПЕРАЦИОННОГО УСИЛИТЕЛЯ В КОНТУРЕ УПРАВЛЕНИЯ ОБОРУДОВАНИЕМ С ЧПУ | 2009 |

|

RU2397058C1 |

| Аналоговое запоминающее устройство | 1981 |

|

SU978200A1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ КОМПАРАТОР С ВЫБОРКОЙ ВХОДНОГО СИГНАЛА | 2008 |

|

RU2352061C1 |

| ИСТОЧНИК ЭЛЕКТРИЧЕСКОГО СИГНАЛА, ПРОПОРЦИОНАЛЬНОГО АБСОЛЮТНОЙ ТЕМПЕРАТУРЕ | 1993 |

|

RU2115099C1 |

| ИНДИКАТОР ЭЛЕКТРОМАГНИТНОГО ИЗЛУЧЕНИЯ | 1992 |

|

RU2060508C1 |

| Импульсный генератор инфранизкой частоты | 1979 |

|

SU793303A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU855737A1 |

| Усилитель заряда | 1983 |

|

SU1148003A1 |

| Коммутатор аналоговых сигналов | 1981 |

|

SU978345A1 |

| ПИКОВЫЙ ДЕТЕКТОР | 2009 |

|

RU2409818C1 |

Авторы

Даты

1992-07-15—Публикация

1990-02-13—Подача