ки, приводит к значительному росту внепо- лосных излучений.

Цель изобретения - уменьшение вне- полосных излучений передаваемого сигнала.

Для достижения поставленной цели в устройство введены на передающей стороне первый;, и второй коммутаторы, N дополнительных формирователей широкополосных сигналов, первый и второй дополнительные сумматоры, второй фазовый модулятор и второй преобразователь абсолютного кода в относительный, причем N выходов блока преобразования сигналов подключены через первый коммутатор к входам N формирователей широкополосных сигналов и к входам N дополнительных формирователей широкополосных сигналов, при этом выход первого фазового модулятора подключен к входу передатчика через второй дополнительный сумматор, а выходы N дополнительных формирователей широкополосных сигналов подключены к входам первого дополнительного сумматора, выхЪд которого через второй фазо- вый модулятор подключен к второму входу второго дополнительного сумматора, причем выход делителя тактовой частоты подключен к управляющему входу первого коммутатора и через последовательно со- единенные второй коммутатор и второй преобразователь абсолютного кода в относительный, к второму входу второго фазового модулятора, a N+1 выход блока преобразования сигналов подключен к вхо- ду первого преобразователя абсолютного кода в относительный через второй коммутатор, на приемной стороне введены N дополнительных согласованных фильтров, дополнительный блок квазиоптимальной обработки сигналов с относительной фазовой модуляцией и элемент ИЛИ, при этом к входам N дополнительных согласованных фильтров подключен выход приемника, а выходы N дополнительных согласованных фильтров подключены к входам соответствующих дополнительных перемножителей дополнительного блока квазиоптимальной обработки сигналов с бтносительной фазовой модуляцией, выход которого подключен к первому входу элемента ИЛИ, к второму входу которого подключен выход знакового перемножителя, а выход элемента ИЛИ является выходом устройства.

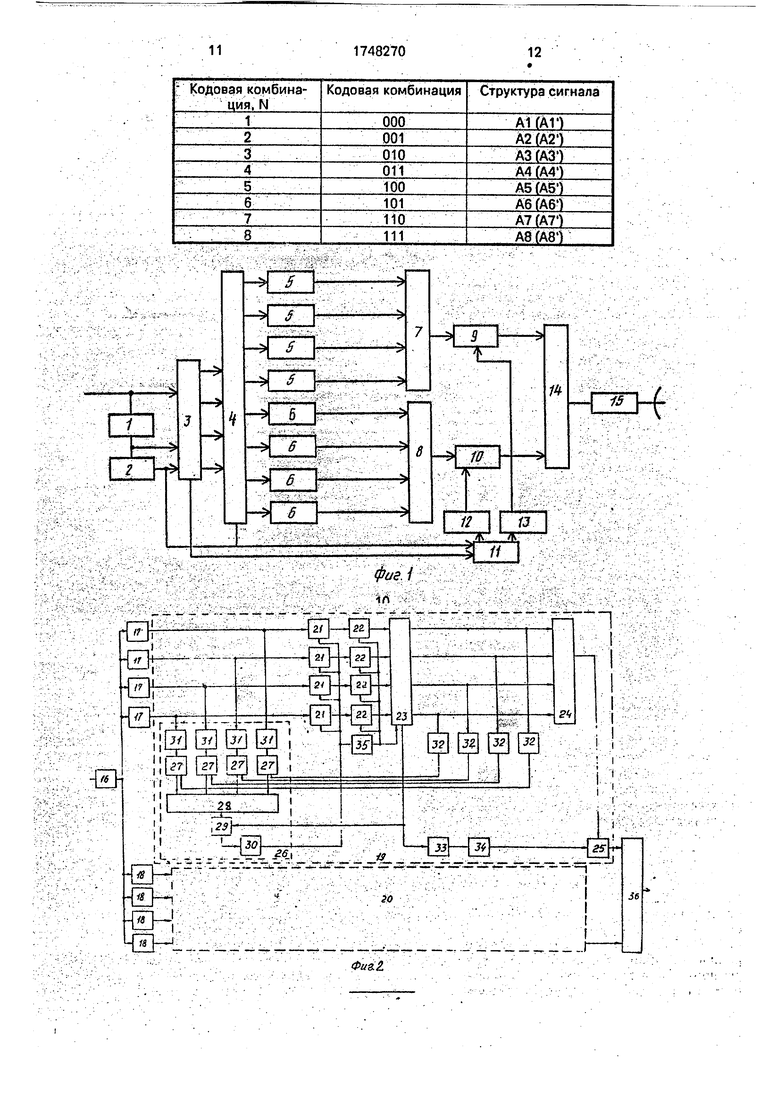

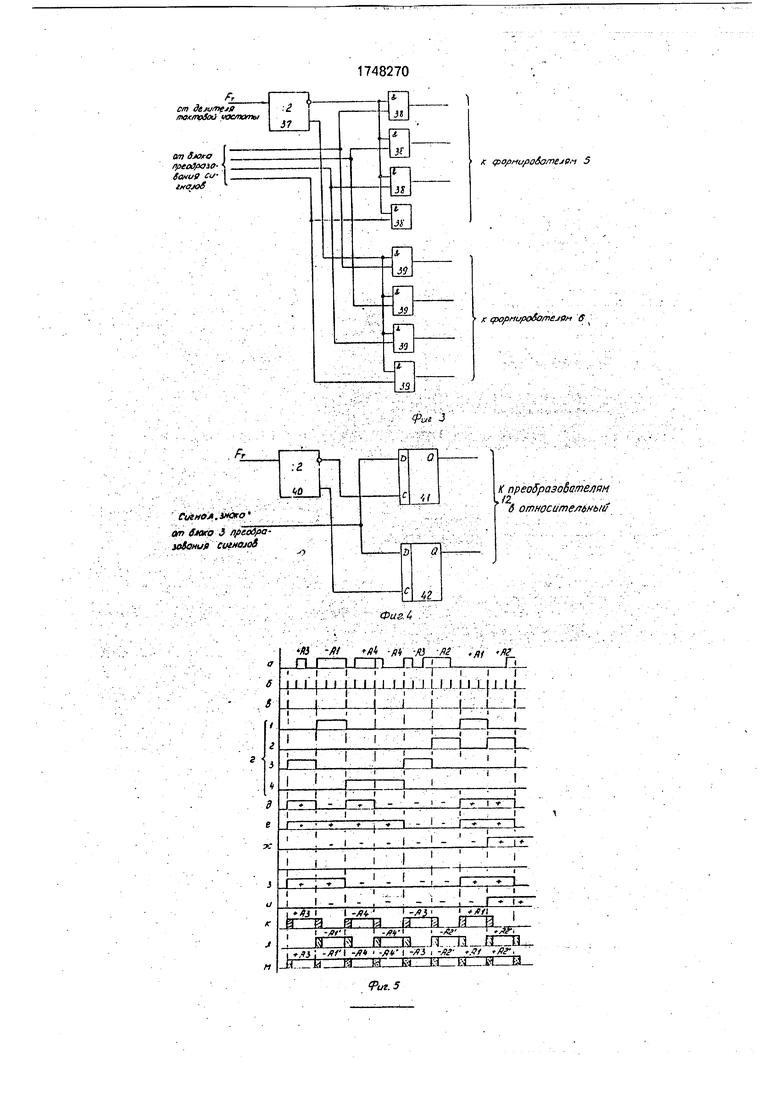

На фиг. 1 приведена структурная схема передающей части устройства для передачи и приема многопозиционных широкополосных сигналов; на фиг. 2 - структурная схема приемной части устройства; на фиг. 3 - структурная схема коммутатора логических

сигналов; на фиг. 4 - структурная схема другого коммутатора; на фиг. 5 и 6 - графики работы устройства.

Устройство содержит на передающей стороне выделитель 1 тактовых импульсов, делитель 2 тактовой частоты, блок 3 преобразования сигналов, коммутатор 4, N формирователей 5 многопозиционных широкополосных сигналов, N дополнительных формирователей 6 многопозиционных широкополосных сигналов, сумматор 7, дополнительный сумматор 8, фазовый модулятор 9, дополнительный фазовый модулятор 10, коммутатор 11, основной 12 и дополнительный 13 преобразователи абсолютного кода в относительный, второй дополнительный сумматор 14, радиопередатчик 15.

На приемной стороне устройство содержит приемник 16, N согласованных фильтров 17, N дополнительных согласованных фильтров 18, основной 19 и дополнительный 20 блоки квазиоптимальной обработки сигналов с относительной фазовой манипуляцией, в состав каждого из которых входит N перемножителей 21, N интеграторов 22, решающий блок 23, преобразователь 24 сигналов, знаковый перемножитель 25, блок 26 формирования опорного сигнала, который содержит N блоков стробирования 27, сумматор 28, перемножитель 29, гребенчатый фильтр 30, N линий 31 задержки, N формирователей 32 стробирующего напряжения, преобразователь 33 относительного кода в абсолютный, элемент НЕ 34, блок 35 синхронизации. Кроме того, на приемной стороне устройство содержит схему ИЛИ 36.

Устройство работает следующим образом.

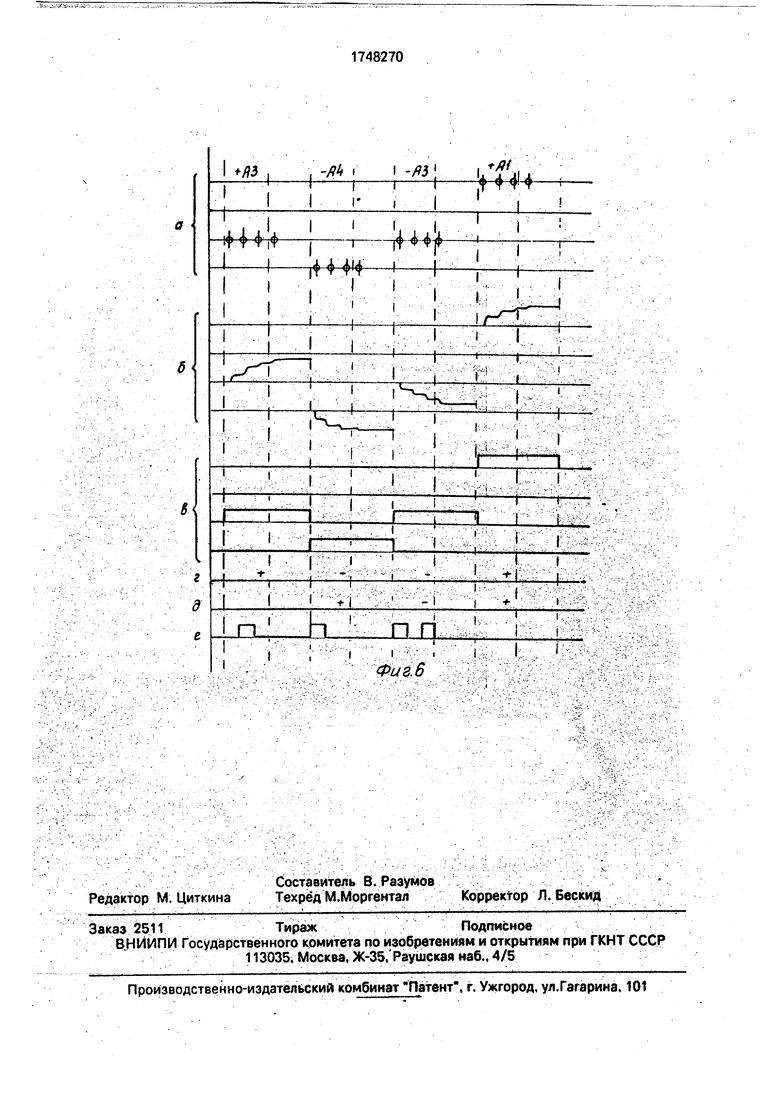

Двоичная последовательность (фиг. 5а) поступает на третий вход блока 3 преобразования сигналов и вход выделителя 1 тактовых импульсов, который осуществляет формирование коротких импульсов с частотой следования fri 1/Ти i где Ти -длительность двоичного информационного Символа (фиг. 56). Таковые импульсы от выделителя 1 тактовых импульсов поступают на второй вход блока 3 преобразования сигналов и на вход делителя 2 тактовой частоты, с выхода которого тактовые импульсы с частотой гт2 fri /К, где K log2N (фиг. 5в), поступают на первый вход блока 3 преобразования сигналов.

Осциллограммы выходных напряжений блока 3 преобразования сигналов показаны на фиг. 5г.

Выходы блока 3 преобразования сигналов подключены к входам коммутатора 4 логических сигналов на два положения и

четыре направления, который управляется импульсами с выхода делителя 2 тактовой частоты. Сигналы с выхода делителя 2 тактовой частоты поступают на вход делителя 37 частоты на два, имеющего два выхода - прямой и инверсный и вырабатывающего меандр поделенной на два токтовой частоты. Сигналы с прямого делителя 37 частоты поступают на входы N элементов И 38,39, на вторые входы которых также под- с отся сигналы блока 3 преобразования сигналов. В соответствии с импульсами делителя 2 тактовой частоты выходные сигналы блока 3 преобразования сигналов под- аются попеременно то на входы формирователей 5 широкополосных сигналов, то на входы дополнительных формирователей 6 широкополосных сигналов. При этом возбуждение многопозиционных широкополосных сигналов происходит попеременно в основных 5 или дополнительных 6 формирователях широкополосных сигналов. Сигналы, формируемые дополнительными формирователями б широкополосных сигналов, отличаются от соответствующих сигналов формирователей 5 широкополосных сигналов только сдвигом частоты заполнения на величину Л f :Ј A F, где A F - полоса широкополосного сигнала, и поворотом фазы сигнала на 90°. Для обеспечения стыковки соседних широкополосных многопозиционных сигналов без разрыва фазы начала и концы всех многопозиционных широкополосных сигналов имеют одинаковую частоту заполнения, а фронт нарастания (спада) сигналов формируется

по закону sinx (cosx); Ъ х -. Формирование широкополосных многопозиционных сигналов может проводиться с помощью фильтров на поверхностных акустических волнах. Длительность формируемых сигналов составляет гс Кги + Дг , где Аг- время, необходимое для формирования стыков сигналов. Длительность формируемых сигналов определяется длительностью импульсного отклика ПАВ-фильтров, а формирование сигнала начинается по фронту импульса, поступающего с коммутатора 4. Сигналы, сформированные формирователями 5 широкополосных сигналов, обьеди- няются сумматором 7, а сигналы, сформированные дополнительными формирователями 6 широкополосных сигналов, объединяются первым дополнительным сумматором 8, С выхода сумматора 7 сигнал поступает на вход фазового модулятора 9, а с выхода дополнительного сумматора 8 сигнал поступает на вход дополнительного фазового модулятора 10. В фазовых

модуляторах 9, 10 осуществляется манипуляция начальной фазы широкополосных многопозиционных сигналов в соответствии с двоичными последовательностями,

поступающими с выхода основного 12 и дополнительного преобразователей абсолютного кода в относительный (фиг. 5 з, и).

Знаковый сигнал, поступающий с выхода блока 3 преобразования сигналов (фиг.

0 5д), поступает на коммутатор 11, на второй вход которого поступает управляющий сигнал с выхода делителя 2 тактовой частоты. Коммутатор 11 поочередно распределяет импульсы знакового сигнала на два парал5 лельных потока (фиг. 5е, ж). В состав коммутатора 11 (фиг. 4} входят делитель 40 на два, имеющий два выхода - прямой и инверсный. Делитель 40 формирует меандр поделенной на два тактовой частоты, которую

0 вырабатывает делитель 2 тактовой частоты. Инверсный выход делителя 40 подключен к триггеру 41, который по фройту инверсного сигнала тактовой частоты переписывает сигнал знака, поступающий с выхода блока

5 3 преобразования сигналов.

Прямой выход делителя 40 подключен к триггеру 42, который срабатывает по фронту сигнала тактовой частоты, вырабатываемого делителем 39. Выходные сигналы тригге0 ров 41,42 поступают на входы основного 12 и дополнительного 13 преобразователей абсолютного кода в относительный. Осциллограммы выходных сигналов преобразователей приведены на фиг. 5з, и

5 Выходные сигналы основного 9 и дополнительного 10 фазовых модуляторов поступают на Второй дополнительный сумматор 14 и далее на выход радиопередатчика 15. Поскольку соседние широкополосные сигналы

0 перекрываются на величину А г, имеют фазовый сдвиг ±90° и одинаковую частоту за- полнения стыков сигналов, а фронты нарастания (спада) сформированных сигналов имеют закон sinx (cosx), 0 х - . то

DЈ.

стыковка соседних сигналов осуществляется без разрыва фазы, что дает возможность уменьшить внеполосные излучения радиопередатчика 15.

0 На приемной стороне после широкополосного приемника 16 сигнал поступает на основные 17 и дополнительные 18 согласованные фильтры, согласованные со структурой соответствующих широкопо5 лосних сигналов. На выходах основных 17 и дополнительных 18 согласованных фильтров появляются отклики (короткие радиоимпульсы), начальная фаза которых может принимать значения 0 и 180° в зависимости от передаваемых сигналов. Изменение

начальной фазы в последовательностях принимаемых сигналов осуществляется по относительному закону. Сигналы с выходов основных 17 и дополнительных 18 согласованных фильтров поступают на два идентич- ных блока 19, 20 квазиоптимальной обработки сигналов с относительной фазовой модуляцией, в каждом ш которых осуществляется когерентный прием сигналов, для чего выделяется опорное когерентное колебание путем суммирования откликов согласованных фильтров, 17 в сумматоре 28 и очищение этой суммы от шумов с помощью гребенчатого фильтра 30. Для повышения эффективности работы гребенчатого фильтра 30 применяется обратная связь по решению со съемом манипуляции с помощью линий 31 задержки на длительность сигнала и блоков 27 стробированмя, перемножителя 29,связанного со знаковым выходом решающего блока 23.

На выходе сумматора 28 появляются колебания с переменной фазой, что не дает возможности гребенчатому фильтру 30 осуществлять когерентное накопление сигналов за много тактов передачи. Для устранения фазовой манипуляции на второй вход перемножителя 29 поступают управляющие импульсы положительной или отрицательной полярности со знакового выхода решающего блока 23. На выходе сумматора 28 появляются колебания с переменной фазой, что не дает возможности гребенчатому фильтру 30 осуществлять когерентное накопление сигналов за много тактов передачи. Для устранения фазовой манипуляции на второй вход перемножителя 29 поступают управляющие импульсы положительной или отрицательной полярности со знакового выхода решающего блока 23, Таким образом осуществляется Съем манипуляции и обеспечение работы гребенчатого фильтра.

Очищенное от шумов опорное когерентное напряжение с выхода гребенчатого фильтра 30 поступает на вторые входы перемножителей 21, первые входы которых соединены с выходами согласованных фильтров 17. Этим осуществляется синхронное когерентное детектирование принятых сигналов. Для борьбы с замираниями, которые проявляются в рассыпании откликов на выходах согласованных фильтров 17 (многолучевая картина), сигналы с выходов перемножителей 21 поступают ни интеграторы 22, в которых осуществляется когерентное накопление лучей.

Пределы интегрирования устанавливаются блоком 35 синхронизации, соединенным по входу с гребенчатым фильтром 21, а

по выходу- суправляющими входами интеграторов 22 и последующими устройствами обработки сигналов. Блок синхронизации 35 осуществляет формирование синхросигнала, представляющего собой последовательность коротких импульсов с частотой 1/(гс-Дт).

Моменты появления коротких импульсов соответствуют временным границам

прянятого широкополосного сигнала. Конкретная реализация блока 35 синхронизации определяется структурой используемого многопозиционного широкополосного сигнала.

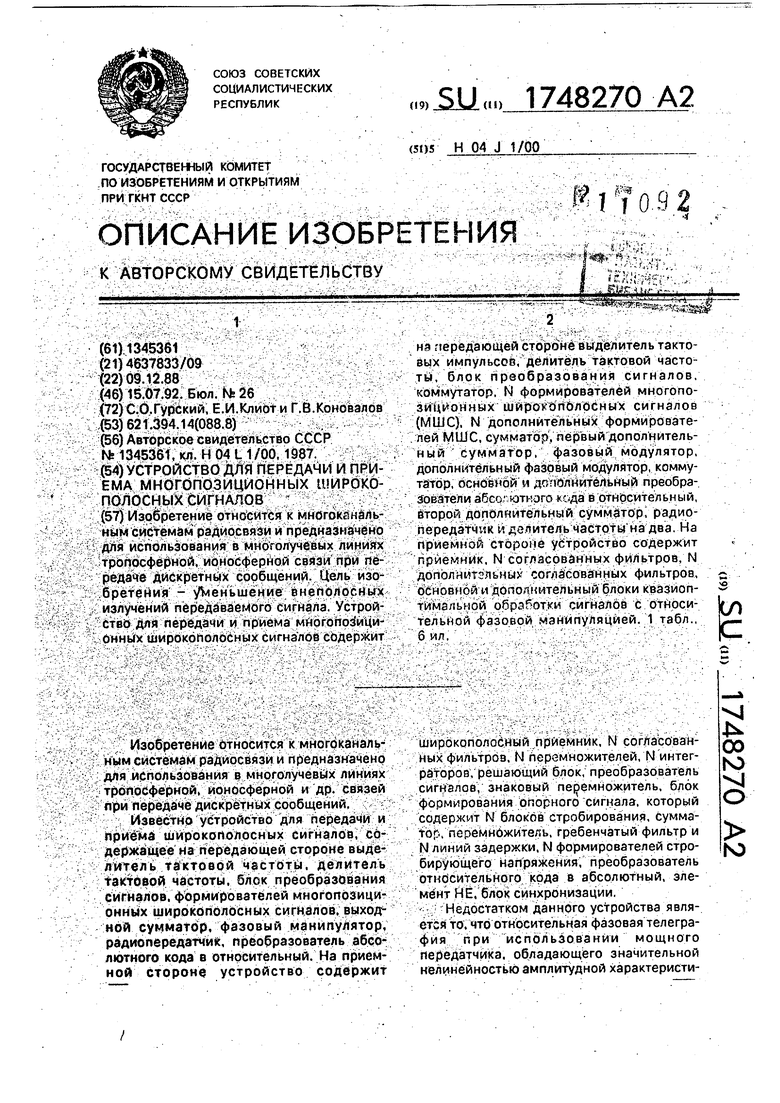

Поскольку принимаемые широкополосные сигналы манипулированы по фазе ( или ), на выходах интеграторов 22 появляются разнополярные импульсы. Временные диаграммы напряжений на выходах

интеграторов приведены на фиг. 66. С выходов интеграторов 22 сигнал поступает на N входов решающего блока 23. На выходах решающего блока появляется сигнал в той ветви, которая соответствует максимальной

амплитуде принятого сигнала. Кроме того, решающий блок 23 выносит решение о знаке отсчета сигнала с максимальной амплитудой.

С N выходов решающего блока 23 сигналы, несущие в себе информацию о том, в какой из N ветвей обработки максимальный сигнал, поступают на выходы преобразователя 24 сигналов. На выходе преобразователя 24 сигналов в соответствии с номером его

входа, на который поступает сигнал с решающего блока 22, формируется соответствующая кодовая комбинация. При этом на выходе преобразователя 24 сигналов формируется одна из первых четырех кодовых

комбинаций, приведенных в таблице.

Вид кодовой комбинации определяется структурой принятого многопозиционного широкополосного сигнала. Преобразователь 24 сигналов не учитывает знак или начал ьную фазу ( или 180°), с которым был передан многопозиционный сигнал, и не обеспечивает формирование остальных четырех кодовых комбинаций, которые являются инверсией первых четырех кодовых

комбинаций.

Временные диаграммы сигналов на выходе преобразователя 24 сигналов при вед е: ны на фиг. бе. Кодовые комбинации с выхода преобразователя 24 сигналов поступают на первый вход знакового перемножителя 25. Второй вход знакового перемножителя 25 соединен через последовательно соединенные преобразователь 33 относительного кода в абсолютный и первый элемент НЕ 34 со знаковым входом решающего блока 23.

В связи с тем, что в устройстве используется относительная фазовая манипуляция, информация о знаке передаваемого сигнала представлена в относительном коде. Поэтому для окончательного получения на выходе приемного устройства последовательности двоичных символов с относительной фазовой манипуляцией необходимо двоичную последовательность, поступающую со знакового выхода решающего блока 23, представить в абсолютном коде, а затем с противоположным знаком перемножить с последовательностью импульсов, получаемой на выходе преобразователя 24 сигналов.

Преобразователь 33 относительного кода в абсолютный производит сравнение по- лярностей двух соседних двоичных символов. Если при этом полярности сравниваемых импульсов одинаковы, то на выходе формируется импульс с положительной полярностью. Если сравниваемые импульсы имеют различные полярности, то на выходе преобразователя 33 относительного кода в абсолютный будут импульсы, которые приведены на фиг. 6г д. На выходе первого элемента НЕ 34 эта последовательность инвертируется.

Знаковый перемножитель 25 производит сравнение полярностей, поступающих на два его входа импульсов. Если эти полярности совпадают, то на выходе блока 25 формируется положительный импульс; если не совпадают, то на выходе блока 25 формируется импульс отрицательной полярности. В результате сравнения полярностей импульсных последовательностей, поступающих с выхода преобразователя 24 сигналов и с выхода первого элемента НЕ ЗА, на выходе знакового перемножителя формируется выходная импульсная последовательность.

Сигналы блоков 19, 20 квазиоптималь- ной обработки сигналов объединяются схемой ИЛИ 36, на выходе которой восстанавливается исходный информационный поток.

Формула изобретения

Устройство для передачи и приема многопозиционных широкополосных сигналов

поавт, св. № 1345361, отличающееся тем, что, с целью уменьшения внеполосных излучений передаваемого сигнала, на передающей стороне введены первый и второй

коммутаторы, N дополнительных формирователей широкополосных сигналов, первый и второй дополнительные сумматоры, второй фазовый модулятор и второй преобразователь абсолютного кода в

относительный, причем N выходов блока преобразования сигналов подключены через первый коммутатор к входам N формирователей широкополосных сигналов и к входам N дополнительных формирователей

широкополосных сигналов, при этом выход первого фазового модулятора подключен к входу передатчика через второй дополнительный сумматор, а выходы N дополнительных формирователей широкополосных

сигналов подключены к входам первого дополнительного сумматора, выход которого через второй фазовый мудулятор подключен к второму входу второго дополнительного сумматора, причем выход делителя

тактовой частоты через делитель частоты на два подключен к управляющим входам первого коммутатбра и через последовательно соединенные второй коммутатор и второй преобразователь абсолютного кода в относительный - к второму входУ второго фазового модулятора, а (N+1)-u выход блока преобразования сигналов подключен к входу гэрвого преобразователя абсолютного кода в относительный через второй коммутатор, на приемной стороне введены N дополнительных согласованных фильтров, дополнительный блок квазиоптималыной обработки сигналов с относительной фазовой модуляцией и элемент ИЛИ, при этом к

входам N дополнительных согласованных фильтров пбдТШбЧёЧТ Выход приемника, а выходы N дополнительных согласованных фильтров подключены к входам соответствующих дополнительных перемножителей

дополнительного блока квазиоптимальной обработки сигналов с относительной фазовой модуляцией, выход которого подключен к первому входу элемента ИЛИ, к второму входу которого подключен выход знакового перемножителя, а выход элемента ИЛ ИГ является выходом устройства.

Фив.6

Авторы

Даты

1992-07-15—Публикация

1988-12-09—Подача