Изобретение относится к области вычислительной техники, в частности к специализированным вычислительным устройствам для решения задач теории графов и организационного управления, и может быть использовано в различных отраслях народного хозяйства.

Известно устройство для моделирования сетей в реальном времени, содержащее генератор импульсов, блок формирования топологии блок моделей ветвей, блок управления, последний из которых выполнен из узла памяти длительностей ветвей, узла памяти номеров моделируемых ветвей, узла памяти меток свершения ветвей, узла памяти меток фактического окончания операций, узла памяти величины задержек свершения операций, узла измерения длиннейшего пути.

Наиболее близким по технической сущности к данному является устройство для решения задач на графах содержащее многоканальный таймер, блок задания списка заходящих ветвей, блок задания списка исходящих ветвей, блок проверки параметров списка, блок памяти меток свершения вершин, блок синхронизации. Устройство позволяет определить длиннейший и кратчайший путь к графе, который вычисляется путем параллельного моделирования исследуемого графа. Решение задачи в устройстве разделяется на формирование топологии графа и временное моделирование ветвей графа. Причем моделирование топологии графа выполняется на основе информации о топологии исследуемого графа, представленной в виде списков. В устройстве использован принцип динамического за3

44 00 О

крепления каналов таймера за ветвями графа, принадлежащими фронту. Под фронтом в графе в данном случае понимается разрез, который состоит из ветвей, обрабатываемых в текущий момент времени, На основании данного подхода в устройстве для каждого момента времени моделирования графа определяются ветви, которые необходимо обрабатывать и для них информация о длительностях заносится в каналы таймера. При моделировании графа в устройстве определяется величина длиннейшего или кратчайшего пути.

Однако в устройстве отсутствует возможность оперативного контроля и прогнозирования выполнения работ по сетевому проекту в реальном масштабе времени.

Цель изобретения - расширение функциональных возможностей устройства за счет оперативного контроля и прогнозирования выполнения работ по сетевому проекту в реальном масштабе времени.

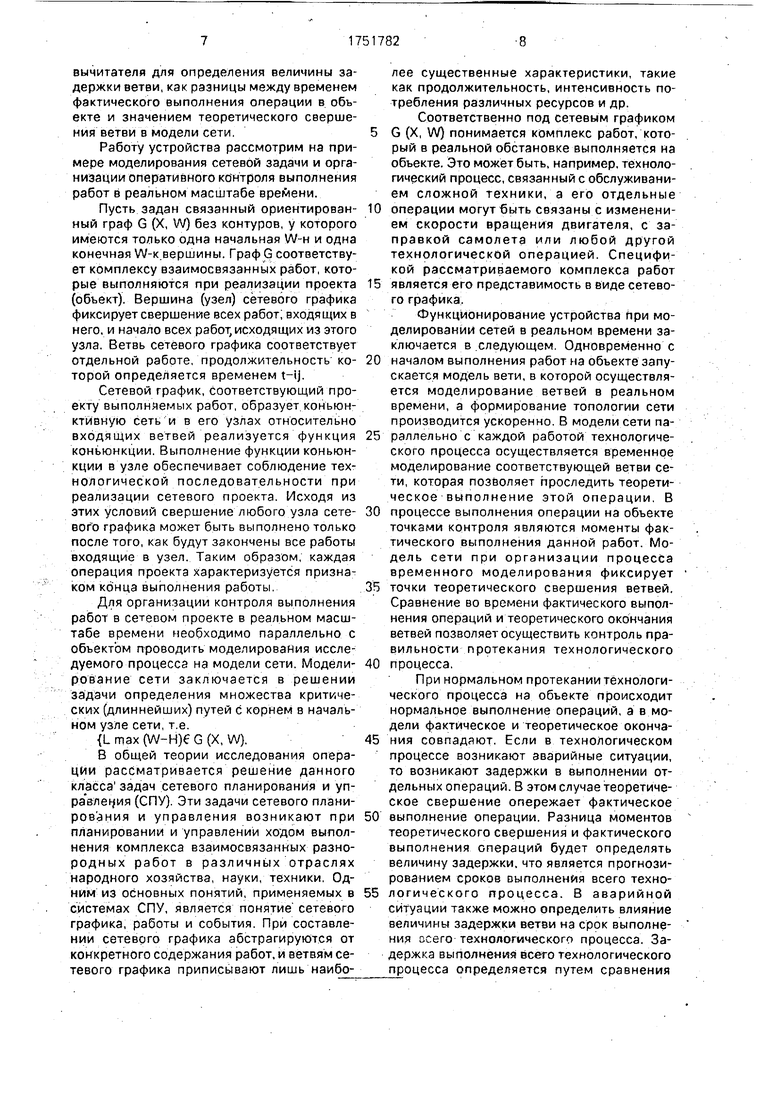

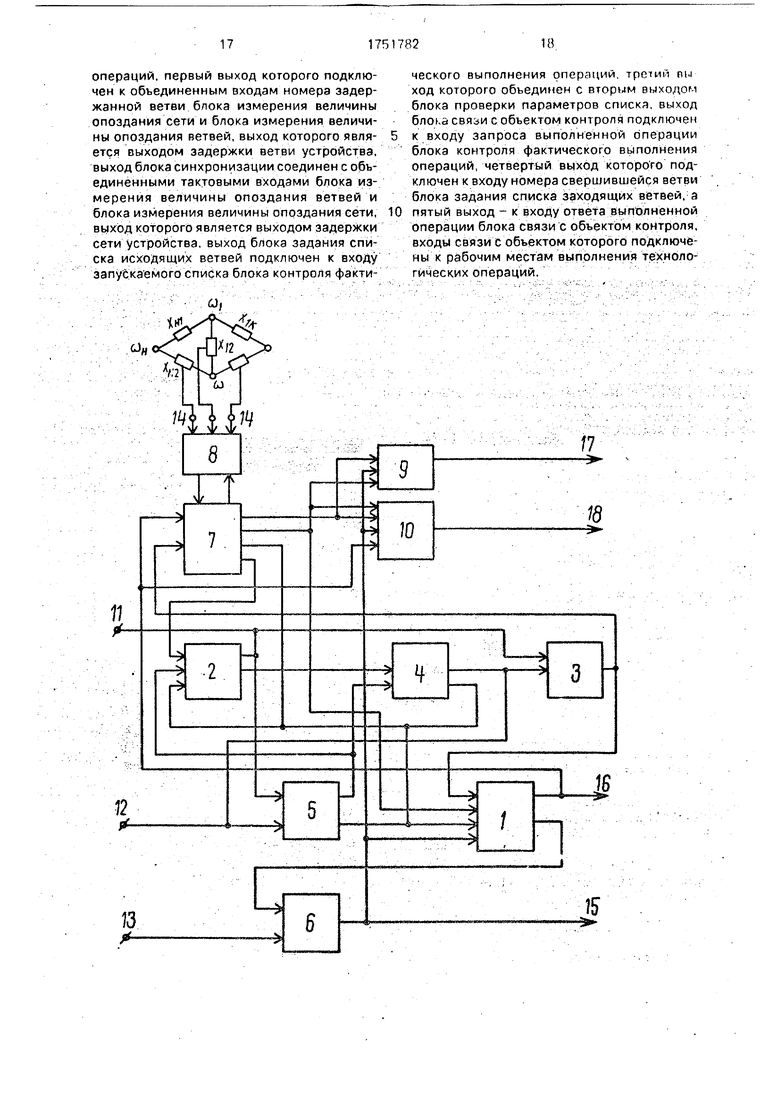

Сущность изобретения заключается в том, что устройство содержит многоканальный таймер, блок задания списка заходящих ветвей, блок задания списка исходящих ветвей, блок проверки параметров списка, блок памяти меток свершения вершин, блок синхронизации, причем входом пуска устройства является вход пуска блока синхронизации, выход которого соединен с тактовым входом многоканального таймера и является тактовым выходом устройства, первый выход многоканального таймера подключен к входу отсутствия прерывания блока синхронизации, второй выход многоканального таймера является выходом номера исполненной ветви устройства, вход установки в единицу блока памяти меток свершения вершин и вход разрешения выдачи списка блока задания списка исходящих ветвей объединены, соединены с первым выходом блока проверки параметров списка и являются входом начальной установки устройства, выход блока задания списка исходящих ветвей подключен к входу задания номера запускаемого канала многоканального таймера, вход опроса прерывания которого и вход блокировки списка блока задания списка заходящих ветвей объединены и соединены с объединенными вторым выходом блока проверки параметров списка и первым выходом блока памяти меток свершения вершин, вход адреса которого и вход номера списка блока задания списка исходящих ветвей объединены, подключены к первому выходу блока задания списка заходящих ветвей и являются входом номера исполненной вершины, второй выход блока задания заходящих ветвей подключен к входу приема записей списка блока проверки параметров списка, вход опроса которого и вход выдачи списка блока задания списка заходящих ветвей объединены и соединены с вторым выходом блока памяти меток свершения вершин, оно дополнительно содержит блок связи с объектом контроля, блок измерения величины опознания сети и блок измерения величины

0 опоздания ветвей, входы исполненной ветви которого и блока контроля фактического - выполнения операций объединены и подключены к второму выходу многоканального таймера, вход фактического прерывания ко5 торого, входы фактического прерывания блока измерений величины опоздания сети и блока измерения величины опоздания ветвей объединены и подключены к второму выходу блока контроля фактического выпол0 нения операций, первый выход которого подключен к объединенным входам номера задержанной ветви блока измерения величины опоздания сети и блока измерения величины опоздания ветвей, выход которого

5 является выходом задержки ветви устройства выход блока синхронизации соединен с объединенными тактовыми входами блока измерения величины опоздания ветвей и блок измерения величины опоздания сети,

0 выход которого является выходом задержки сети устройства, выход блока задания списка исходящих ветвей подключен к входу запускаемого списка блока контроля фактического выполнения операций, третий вы5 ход которого объединен с вторым выходом блока проверки параметров списка, выход блока связи с объектом контроля подключен к входу запроса выполненной операции блока контроля фактического выполнения

0 операций, четвертый выход которого подключен к входу номера свершившейся ветви блока задания списка заходящих ветвей, пятый выход блока контроля фактического выполнения операций подключен к входу

5 ответа выполненной операции блока связи с объектом контроля, входы связи с объектом которого подключены к рабочим местам выполнения технологических операций. На чертеже представлена функциональ0 ная схема предлагаемого устройства.

Устройство содержит многоканальный таймер 1, блок задания списка заходящих ветвей 2, блок задания списка исходящих ветвей 3, блок проверки параметров списка

5 4, блок памяти меток свершения вершин 5, блок синхронизации 6, блок контроля фактического выполнения операций 7, блок связи с объектом контроля 8, блок измерения величины опоздания сети 9, блок измерения величины опоздания ветвей 10

Кроме того, обозначены вход-выход 11 номера исполненной вершины, вход 12 начальной установки, вход 13 пуска, вход 14 связи с объектом, тактовый выход 15, выход 16 номера исполненной ветви, выход 17 задержки сети, выход 18 задержки ветви.

Многоканальный таймер 1 предназначен для хранения заданных длительностей ветвей, а также для формирования временных интервалов моделируемых ветвей сети. Многоканальный таймер может быть выполнен в виде набор отдельных таймеров, число которых определяется количеством од- новременно моделируемых ветвей сети (число ветвей, принадлежащих максимальному фронту сети). Блок задания списка заходящих ветвей 2 предназначен для определения по номеру обрабатываемой ветви номера вершины (номера списка), в которую эта ветвь входит, а также списка всех ветвей записей в списке), входящих в найденную вершину. Кроме того, блок 2 предназначен для хранения метки о свершении ветви, которое определяется фактическим выполнением операции в объекте и теоретическим свершением моделируемого временного интервала этой ветви в многоканальном таймере. Блок задания списка заходящих ветвей 2 может быть выполнен из узлов памяти для хранения информации о топологии и о метках свершения заходящих ветвей в вершины сети, представленной в виде списков. Блок задания списка исходящих ветвей 3 предназначен для определения по номеру свершенной вершины списка ветвей (записей в списке), выходящих из этой вершины Блок задания списка исходящих ветвей 3 может быть выполнен из узлов памяти для хранения информации о топологии исходящих ветвей из вершин сети, представленной в виде списков. Блок проверки параметров списка 4 предназначен для определения свершения обрабатываемой вершины сети, что соответствует выполнению функции коньюнкции относительно ветвей, входящих в рассматриваемую ве ршину. Блок проверки параметров списка 4 может быть выполнен из Логических схем для формирования функции коньюнкции (элементы И) относительно записей входящих в список. Блок памяти меток свершения вершин 5 предназначен для накопления информации о свершении вершин моделируемой сети. Блок памяти меток свершения вершин 5 может быть выполнен на основе узла памяти, где хранятся метки о свершении каждой вершины сети. БЛОК синхронизации 6 предназначен для выработки измерительной серии, которая определяет масштаб времени моделирования

сети. В нашем случае измерительная серия соответствует реальному масштабу времени, дискретность которого обеспечивает необходимый контроль протекания реального процесса с требуемой точностью (например, час, минута, или секунда). Вспомогательные процессы в устройстве выполняются с частотой большей частоты импульсов измерительной серии на столько, чтобы

0 между импульсами измерительной серии были выполнены все вычисления, связанные с формированием топологии сети. Блок синхронизации 6 может быть выполнен в виде управляемого ген ератора импульсов.

5 Блок контроля фактического выполнения операций 7 предназначен для накопления информации о фактическом выполнении операций в объекте и теоретическом свершении соответствующих ветвей в моделиру0 емой сети, а также для определения возникающих отклонений в заданном технологическом процессе. Блок контроля фактического выполнения операций 7 может быть выполнен из узлов памяти для хране5 ния меток о фактическом выполнении операций и о теоретическом свершения ветвей и из логических схем для выделения задержек фактического выполнения операций относительно теоретического свершения

0 ветвей. Блок связи с объектом контроля 8 предназначен для связи контролируемого объекта с моделью сети, которая осуществляется путем периодического опроса контролируемых операций. Блок связи 8 может

5 быть выполнен в виде управляемого регистра опроса входных разрядов Блок измерения величины опоздания сети 9 предназначен для хранения известных величин позднего окончания для каждой ветви

0 сети, а также для определения в блоке величины задержки всей сети из-за возникающих сбоев при выполнении любой операции в объекте. Блок 9 может быть выполнен из узла памяти для хранения известных вели5 чин поздних окончаний для каждой ветви сети, из таймера для измерения текущего времени моделирования сети и вычитателя для определения величины задержки сети, как разницы между фактическим окончани0 ем операции в объекте и теоретическим значением позднего свершения вет ви в модели. Блок измерения величины опоздания ветвей 10 предназначен для вычисления величины опоздания ветви сети при возник5 новении отклонений при выполнении операций в объекте. Блок 10 может быть выполнен из узла памяти для хранения величин теоретического свершения ветвей сети, из таймера для измерения текущего времени моделирования сети, а также из

вычитателя для определения величины задержки ветви, как разницы между временем фактического выполнения операции в объекте и значением теоретического свершения ветви в модели сети.

Работу устройства рассмотрим на примере моделирования сетевой задачи и организации оперативного контроля выполнения работ в реальном масштабе времени.

Пусть задан связанный ориентирован- ный граф G (X, W) без контуров, у которого имеются только одна начальная W-н и одна конечная W-к вершины. Граф G соответствует комплексу взаимосвязанных работ, которые выполняются при реализации проекта (объект). Вершина (узел) сетевого графика фиксирует свершение всех работ, входящих в него, и начало всех работ, исходящих из этого узла. Ветвь сетевого графика соответствует отдельной работе, продолжительность ко- торой определяется временем t-ij.

Сетевой график, соответствующий проекту выполняемых работ, образует коньюн- ктивную сеть и в его узлах относительно входящих ветвей реализуется функция коньюнкции. Выполнение функции коньюн- кции в узле обеспечивает соблюдение технологической последовательности при реализации сетевого проекта. Исходя из этих условий свершение любого узла сете- вого графика может быть выполнено только после того, как будут закончены все работы входящие в узел. Таким образом, каждая операция проекта характеризуется признаком конца выполнения работы.

Для организации контроля выполнения работ в сетевом проекте в реальном масштабе времени необходимо параллельно с объектом проводить моделирования исследуемого процесса на модели сети. Модели- рование сети заключается в решении задачи определения множества критических (длиннейших) путей с корнем в начальном узле сети, т.е.

{L max (W-H)6 G (X, W).

В общей теории исследования операции рассматривается решение данного класса задач сетевого планирования и уп- ра аления (СПУ). Эти задачи сетевого планирования и управления возникают при планировании и управлении ходом выполнения комплекса взаимосвязанных разнородных работ в различных отраслях народного хозяйства, науки, техники. Одним из основных понятий, применяемых в системах СПУ, является понятие сетевого графика, работы и события. При составлении сетевого графика абстрагируются от конкретного содержания работ, и ветвям сетевого графика приписывают лишь наибо-

лее существенные характеристики, такие как продолжительность, интенсивность потребления различных ресурсов и др.

Соответственно под сетевым графиком G (X, W) понимается комплекс работ, который в реальной обстановке выполняется на объекте. Это может быть, например, технологический процесс, связанный с обслуживанием сложной техники, а его отдельные операции могут Јыть связаны с изменением скорости вращения двигателя, с заправкой самолета или любой другой технологической операцией. Спецификой рассматриваемого комплекса работ является его представимость в виде сетевого графика.

Функционирование устройства гфи моделировании сетей в реальном времени заключается в следующем. Одновременно с началом выполнения работ на объекте запускается модель вети, в которой осуществляется моделирование ветвей в реальном времени, а формирование топологии сети производится ускоренно. В модели сети параллельно с каждой работой технологического процесса осуществляется временное моделирование соответствующей ветви сети, которая позволяет проследить теоретическое выполнение этой операции, В процессе выполнения операции на объекте точками контроля являются моменты фактического выполнения данной работ. Модель сети при организации процесса временного моделирования фиксирует точки теоретического свершения ветвей. Сравнение во времени фактического выполнения операций и теоретического окончания ветвей позволяет осуществить контроль правильности протекания технологического процесса.

При нормальном протекании технологического процесса на объекте происходит нормальное выполнение операций, а в модели фактическое и теоретическое окончания совпадают. Если в технологическом процессе возникают аварийные ситуации, то возникают задержки в выполнении отдельных операций. В этом случае теоретическое свершение опережает фактическое выполнение операции. Разница моментов теоретического свершения и фактического выполнения операций будет определять величину задержки, что является прогнозированием сроков выполнения всего технологического процесса. В аварийной ситуации также можно определить влияние величины задержки ветви на срок выполнения всего технологического процесса. Задержка выполнения всего технологического процесса определяется путем сравнения

величин времени фактического выполнения операций с известной величиной позднего окончания соответствующей ветви. Получаемые величины задержек выполнений отдельных операций и всего технологического процесса могут быть использованы для выработки управляющих воздействий.

Вычислительное устройство работает следующим образом.

Перед началом работы в блоки задания списка заходящих ветвей 2 и задания списка ветвей 3 заносится в виде списков информация о топологии моделируемой сети, кроме этого, в блоке 2 обнуляется узел памяти признаков свершения ветвей, в много- канальный таймер 1 для каждой ветви сети заносится информация о ее заданной длительности, в блоке памяти меток свершения вершин 5 обнуляют узел памяти признаков свершения вершин, в блоке контроля факти- ческого выполнения операций 7 обнуляют узлы памяти признаков фактического выполнения операций и теоретического свершения ветвей, в блок измерения величины опоздания сети 9 для каждой ветви сети заносится информация о известной теоретической величине позднего ее окончания, в блоке измерения величины опоздания ветвей 10 обнуляют узел памяти меток теоретического свершения ветвей сети.

После начального установа на вход 11 устройства подают номер начальной вершины сетевого графика сопровождая его импульсом на входе 12 начальной установки устройства. В блоке 3 на основании инфор- мации о топологии сети определяют номера ветвей, выходящих из заданной вершины сети, с выхода блока задания списка исходящих ветвей 3 информации поступает на вход многоканального таймера 1. В много- канальном таймере 1 производится назначение каждой ветви выходящей из накального узла сети, для моделирования ее свободным каналом таймера 1. В каждом выбранном канале таймера производится загрузка кода длительности ветви и последние переводятся в рабочие состояния.

В некоторый момент времени, совпадающий с временем начала выполнения операций на контролируемом объекте, на вход пуска 13 устройства подают импульс уровня 1. При этом блок синхронизации б начинает вырабатывать на своем выходе измерительную серию, которая поступает в многоканальный таймер 1. В таймере 1 на- чинается отсчет временных интервалов в загруженных каналах для ветвей, выходящих из начальной вершины сети.

Проследим, как на устройстве осуществляется контроль выполнения отдельных

операций и всего технолошческого процос са. При пуске комплекса раблт на одновременно в модели сети осуществляется запуск моделирования ветвей, выходящих по топологии из начальной вершины сети. Если выполнение технологического процесса происходит нормально, то в некоторый момент времени на объекте будет выполнена соответствующая операция x-lj, которая выработает через блок связи с объектом контроля 8 сигнал фактического свершения операции.

Сигнал фактического свершения операции вместе с кодом соответствующей операции с блока связи с объектом контроля 8 поступают в блок контроля фактического выполнения операций 7. По сигналу фактического свер шения в блоке 7 разрешается запись метки фактического свершения операции в узел памяти меток фактического окончания операций. Далее в блоке 7 проверяется метка теоретического свершения рассматриваемой операции в узле памяти меток теоретического свершения ветвей. Так как ход выполнения технологического процесса идет нормально, то метка теоретического свершения отсутствует. Обработка фактического свершения операции заканчивается и в блок связи с объектом контроля 8 подается сигнал ответа. В модели сети продолжается временное моделирование фронта обрабатываемых операций, при котором фиксируются моменты теоретического свершения ветвей.

В таймере 1 продолжается отсчет временных интервалов в загруженных каналах для ветвей, выходящих на начального узла сети. Через время, равное кратчайших из моделируемых ветвей, один или несколько каналов сформируют свой временной интервал. В этом случае в таймер 1 по номеру переполненного канал} определяется номер свершившейся ветви, код номера которой с выхода этого блока поступает в блоки контроля фактического выполнения операций 7 и измерения величины опоздания ветвей 10. Кроме того, таймер 1 снимает на своем выходе отсутствия прерывания потенциал уровня 1, по которому в блоке синхронизации б отмечается начало процессов, связанных с формированием топологии сети либо дпугих вспомогательных вычислений.

В блоке контроля фактического выполнения операций 7 по коду номера исполненной ветви, поступившего из таймера 1, в узле памяти меток свершения ветвей запи- сывается метка свершения ветви. Далее из узла памяти меток фактического окончания операций в блоке 7 считывается метка фактического свершения операции. В данном случае на объекте работа уже выполнена и считанная метка равна единице, поэтому в блоке фиксируется совпадение фактического и теоретического выполнения операции, и код номера исполненной ветви с выхода блока 7 передается в блок задания списка заходящих ветвей 2. В блоке 2 для полученной ветви запоминается метка ее свершения. Кроме этого, в блоке 2 по номеру полученной ветви определяется номер вершины (номер списка), в который она входит, и номера остальных ветвей (записей в списке), входящих в найденную вершину. Код номера обрабатываемой вершины с выхода блока 2 поступает на информационный вход блока задания списка исходящих ветгвей 3 и на адресный вход блока памяти меток свершения вершин 5.

В блоке памяти 5 по поступившему коду номера вершины определяется признак ее свершения-в предыдущем моделировании. Если вершина свершена, то единичный сигнал с выхода блока 5 поступает на вход опроса прерывания многоканального таймера 1. Для несвершенной вершины (метка нулевая) единичный сигнал появляется на инверсном выходе блока 5. В данном случае вершина не свершена и единичный сигнал с выхода блока 5 поступает на входы разрешения выдачи списка блока задания списков заходящих ветвей 2 и опроса блока проверки параметров списка 4. По сигналу разрешения выдачи списка блок задания списков заходящих ветвей 2 выдает на свой выход метки свершения ветвей, входящих в заданный список. Метки свершения ветвей для рассматриваемой вершины передаются на вход приема записей списка блока проверки параметров списка 4. В блоке 4 проверяется выполнение функций конъюнкции для ветвей, входящих в рассматриваемую вершину. Все метки, поступившие в блок 4, должны иметь единичное значение и тогда функция вершины будет сформирована. В случае невыполнения функции вершины, т.е. если хотя бы одна ветвь, входящая в рассматриваемую вершину, не сформировала свой временной интервал (метка равна нулю), на выходе блока 4 вырабатывается сигнал отсутствия соответствия в списке, который поступает на вход опроса прерывания многоканального таймера 1. В последнем случае таймер 1 сбрасывает текущее прерывание без приема нового списка ветвей. При выполнении функции коньюнкции вершины на выходе блока 4 вырабатывается сиг-нал свершения вершины, который поступает на вход разрешения выдачи списка блока задания списка исходящих ветвей 3 и установки единичной метки блока памяти меток свершившихся вершин 5. В блоке 5 устанавливается в единицу признак свершения вершины. По коду номера свершившейся вершины и сигналу свершения вершины в блоке 3 определяется список ветвей, выходящих из сформированной вершины. Полученный список исходящих ветвей из сформирован0 ной вершины с выхода блока 3 поступает на вход запуска списка блока контроля фактического выполнения операций 7 и на вход задания номеров запускаемых каналов многоканального таймера 1. В таймере 1

5 аналогичным образом осуществляется назначение каналов для моделирования ветвей и производится загрузка и перевод выбранных каналов в рабочее состояние. После загрузки полученного списка исхо0 дящих ветвей в многоканальном таймере 1 проверяется наличие каналов, окончивших формирование интервалов, и, если они есть, продолжается дальнейшая обработка прерывания В таймере 1 в этом случае оп5 ределяется номер следующей сформированной ветви в рассматриваемый момент времени решения, если такие еще имеются, и осуществляется обработка свершения найденной ветви. Для этой ветви проверя0 ется фактическое выполнение соответствующей операции, которое имеется при нормальном протекании технологического процесса. Далее по номеру обрабатываемой ветви определяется номер вершины, в

5 которую она входит, и список остальных ветвей, входящих в рассматриваемую вершину, проверяется выполнение логической функции вершины и для свершения вершины осуществляется загрузка канатов таймера 1

0 для моделирования ветвей, исходящих из свершенной вершины А на объекте в это время для загруженных каналов начинается выполнение соответствующих операций по технологии Так последовательно обраба5 тывзются все ветви, свершившие свои временные интервалы. Затем многоканальный таймер 1 после окончания обработки прерываний выставляет на своем выходе отсутствия прерывания потенциал уровня 1,

0 по которому отмечается окончание вспомогательных вычислений и в устройстве продолжается процесс временного моделирования сети.

временное моделирование сети и вы5 полнение операций на объекте продолжается до тех пор, пока не сформируется следующий какой-нибудь из моделируемых временных интервалов или не будет закончена одна из работ на комплекс операций. При выполнении операции в устройстве запоминается метка фактического ее выполнения. После свершения временного интервала в устройстве осуществляется обработка топологии сети. Выполнение работ на объекте и моделирование сети, состо- ящее из временного моделирования ветвей и формирования топологии, будет продолжаться до тех пор, пока не будет достигнута конечная вершина исследуемой сети. В этом случае на объекте будет выполнен весь комплекс работ, а в устройстве на входе/выходе номера исполненной вершины 11 появится код конечной вершины сети, свершение которой сопровождается сигналом на выходе признака соответствия блока проверки параметров списка 4.

Описанный случай возникает при нормальном выполнении операций технологического процесса. В этой ситуации на объекте в сетевую модель поступает сигнал фактического окончания операции, который либо совпадает, либо опережает временную точку теоретического свершения ветви, которая определяется свершением интервала в соответствующем канале таймера. Однако в объекте при выполнении комплекса работ могут быть отклонения от теоретически заданного.

Если в технологическом процессе возникают аварийные ситуации, то появляются задержки в выполнении отдельных операций. При возникновении сбоев на объекте в таймере 1 устройства как и следует определяется теоретическое свершение ветви (код номера исполненной ветви на входах бло- ков контроля фактического выполнения операций 7 и измерения величины опоздания ветвей 10), а сигнал фактического выполнения операции в это время будет отсутствовать В этом случае по коду номера исполненной ветви в блоке контроля фактического выполнения операций 7 осуществляется запись метки теоретического свершения ветви в узел памяти меток свершения ветви и считывание метки фактиче- ского выполнения операции. Так как на объекте операция еще не выполнена, то считанная метка равна нулю. По этой метке в блоке 7 устанавливается факт опоздания рассматриваемой операции на объекте и на выход блока выдается код номера задержанной ветви Последний номер ветви поступает в блок измерения величины опоздания ветвей 10, где для номера задержанной ветви в узле памяти теоретического свершения ветвей запоминается из таймера блока 10 текущее время моделирования сети. Кроме этого, в случае отсутствия метки фактического свершения операции запрещается включение в этап временного моделирования следующих по топологии потней сети На выходе блока контроля Фактического выполнения операций 7 вырабатывается сигнал отсутствия свершения, который поступает на вход опроса прерываний многоканального таймера для сброса текущего прерывания. Формирование топологии для задержанной ветви в модели сети запрещается до тех пор, пока не будет получен из объекта сигнал фактического окончания операции. В течение всего этого времени моделируемач ветвь относится к задержанным и в устройстве накапливается время невыполнения операции,

С приходом сигнала фактического окончания операции через блок связи с объектом контроля 8 в блоке контроля фактического выполнения операций 7 осуществляется запись метки фактического свершения операции в узел памяти меток фактического окончания операций и считывание метки теоретического свершения ветви из узла памяти свершения ветвей. Так как операция была задержана, то метка теоретического свершения ветви равна единице. По этой метке в блоке 7 устанавливается факт свершения задержанной ветви и на выход выдается код номера свершившейся ветви в блок задания списка заходящих ветвей 2 и код номера задержанной ветви в блоки измерения величины опоздания сети 9 и измерения величины опоздания ветвей 10, а также вырабатывается сигнал прерывания, который поступает в блоки 9, 10 и в многоканальный таймер 1. По сигналу прерывания таймер 1 снимает на своем выходе отсутствия прерывания потенциал уровня 1, по которому в блоке синхронизации 6 отмечается начало процессов, связанных с вспомогательными вычислениями.

В блоках 9, 10 по сигналу прерывания осуществляется определение величины опоздания ветви и задержки сети связанной с задержкой этой ветви. В блоке 10 по коду номера задержанной ветви и сигналу прерывания из узла памяти блока считывается код теоретического свершения задержанной ветви, который вместе с кодомтекуще- го времени с таймера блока поступает на вход вычитателя. В блоке производится вычисление величины опоздания ветви, как разницы теоретического и фактического свершения рассматриваемой ветви. Полученная величина задержки ветви с вычитателя заносится в узел памяти блока, а также выдается на выход задержки ветви 18 устройства, В блоке 9 в это время из узла памяти блока считывается величина известного позднего окончания рассматриваемой ветви, которая вместе с кодом текущего времени с таймера блока поступает на вход вычитателя. В блоке производится вычисление величины задержки сети как разницы позднего теоретического и фактического окончания ветви. Полученная величина задержки сети заносится в узел памяти блока, а также выдается на выход задержки сети 17 устройства. Так осуществляется регистрация величины задержки выполнения отдельных операций и их влияние на окончание всей сети.

После этого производится анализ топологии сети для ветвей входящих в рассматриваемую вершину. В блоке задания списка заходящих ветвей 2 по номеру свершенной ветви считывается номер вершины, в который она входит и для определения свершения функции вершины находятся остальные ветви входящие в рассматриваемую вершину. Далее в устройстве осуществляется формирование топологии, связанное с проверкой выполнения логической функции вершины и для свершенной вершины осуществляется загрузка каналов таймера 1 для моделирования ветвей, исходящих из свершенной вершины. Если в текущий момент времени в устройстве имеются еще прерывания от фактически или теоретически оконченных ветвей, то продолжается дальнейшая обработка топологии сети. Обработка топологии сменяется временным моделированием сети.

Моделирование технологического процесса, представленного в виде сети, продолжается до тех пор, пока не будет сформирован конечный узел сети (на входе/выходе 11). Как только это произойдет, одновременно на объекте будет закончено выполнение всего объема работ с учетом всех возникших задержек на отдельных его участках.

Так осуществляется контроль выполнения отдельных операций по всему технологическому процессу. В случае возникновения непредвиденных обстоятельств в выполнении операций могут быть предприняты экстренные меры. Как результат информация о вызванных задержках накапливается в блоках измерения величин опоздания ветвей и сети и может быть использована при анализе мероприятий, связанных с выполнением всего технологического процесса.

В устройстве обеспечивается поступление необходимых сигналов предварительного установа, которые не показаны.

Ф о р м у л а и з о б р ет е н и я

Устройство для моделирования сетей в реальном времени, содержащее многоканальный таймер, блок задания списка заходящих ветвей, блок задания списка

исходящих ветвей, блок проверки параметров списка, блок памяти меток свершения вершин, блок синхронизации, причем входом пуска устройства является вход пуска

блока синхронизации, выход которого соединен с тактовым входом многоканального таймера и является тактовым выходом устройства, первый выход многоканального таймера подключен к входу отсутствия пре0 рывания блока синхронизации, второй выход является выходом номера исполненной ветви устройства, вход установки в 1 блока памяти меток свершения вершин и вход разрешения выдачи списка блока задания спи5 ска исходящих ветвей объединены, соединены с первым выходом блока проверки параметров списка и являются входом начальной установки устройства, выход блока задания списка исходящих

0 ветвей подключен к входу задания номера запускаемого канала многоканального таймера, вход опроса прерывания которого и вход блокировки выдачи списка блока задания списка заходящих ветвей объединены и

5 соединены с объединенными вторым выходом блока проверки параметров списка и первым выходом блока памяти меток свершения вершин, вход адреса которого и вход номера списка блока задания списка

0 исходящих ветвей объединены, подключены к первому выходу блока задания списка заходящих ветвей и являются входом-выходом номера исполненной вершины, второй выход блока задания списка

5 заходящих ветвей подключен к входу приема записей списка блока проверки параметров списка, вход опроса которого и вхбд выдачи списка блока задания списка заходящих ветвей объединены и соедине0 ны с вторым выходом блока памяти меток свершения вершин, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет обеспечения оперативного контроля и

5 прогнозирования выполнения работ по сетевому проекту в реальном масштабе времени, введены блок контроля фактического выполнения операций, блок связи с объектом контроля, блок измерения величины опоздания

0 сети и блок измерения величины опоздания ветвей, входы исполненной ветви которого и блока контроля фактического выполнения операций объединены и подключены к второму выходу многоканального таймера.

5 вход фактического прерывания которого, входы фактического прерывания блока измерения величины опоздания сети и блока измерения величины опоздания ветвей объединены и подключены к второму выходу блока контроля фактического выполнения

операций, первый выход которого подключен к объединенным входам номера задержанной ветви блока измерения величины опоздания сети и блока измерения величины опоздания ветвей, выход которого является выходом задержки ветви устройства, выход блока синхронизации соединен с объединенными тактовыми входами блока измерения величины опоздания ветвей и блока измерения величины опоздания сети, выход которого является выходом задержки сети устройства, выход блока задания списка исходящих ветвей подключен к входу запускаемого списка блока контроля факти0

ческого выполнения операций третий пи ход которого объединен с вторым выходом блока проверки параметров списка, выход блоке связи с объектом контроля подключен к входу запроса выполненной операции блока контроля фактического выполнения операций, четвертый выход которого подключен к входу номера свершившейся ветви блока задания списка заходящих ветвей, а пятый выход - к входу ответа выполненной операции блока связи с объектом контроля, входы связи с объектом которого подключены к рабочим местам выполнения технологических операций.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для решения задач на графах | 1990 |

|

SU1837314A1 |

| Устройство для моделирования сетей в реальном времени | 1987 |

|

SU1509926A1 |

| Устройство для решения задач на графах | 1989 |

|

SU1626256A1 |

| Устройство для анализа параметров сети | 1986 |

|

SU1548793A1 |

| Устройство для анализа параметров графа | 1986 |

|

SU1532942A1 |

| Устройство для моделирования задач о длиннейшем пути в сетях | 1983 |

|

SU1161951A1 |

| Устройство для моделирования задач о длиннейшем пути в сетях | 1987 |

|

SU1509925A2 |

| Устройство для моделирования направленных графов | 1986 |

|

SU1322304A1 |

| Устройство для определения длиннейшего пути в сетях | 1986 |

|

SU1339581A1 |

| Устройство для моделирования задач о длиннейшем пути в сетях | 1986 |

|

SU1374239A2 |

Изобретение относится к вычислительной технике, в частности к специализированным вычислительным устройствам для решения задач организационного управления и теории графов, может быть использовано в различных отраслях народного хозяйства. Целью изобретения является расширение функциональных возможностей устройства за счет оперативного контроля и прогнозирования выполнения работ по сетевому проекту в реальном масштабе времени. Поставленная цель достигается тем, что устройство для моделирования сетей в реальном времени содержит многоканальный таймер, блок задания списка заходящих ветвей, блок задания списка исходящих ветвей, блок проверки параметров списка, блок памяти меток свершения вершин, блок синхронизации, блок связи с объектом контроля, блок измерения величины опоздания сети и блок измерения величины опоздания ветвей. 1 ил. W fe

Г,

&г

wTHw

| Устройство для моделирования сетей в реальном времени | 1987 |

|

SU1509926A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для решения задач на графах | 1989 |

|

SU1626256A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Механизм для сообщения поршню рабочего цилиндра возвратно-поступательного движения | 1918 |

|

SU1989A1 |

Авторы

Даты

1992-07-30—Публикация

1990-06-27—Подача