Изобретение относится к радио- измерительной технике и может быть использовано в генераторах тест- сигналоВо Создание генераторов кодового слова (ГКС) является одной из задач проектирования генераторов , тест-сигналов,.

Цель изобретения - расширение класса решаемых задач за счет увеличения набора выходных кодовых последовательностей

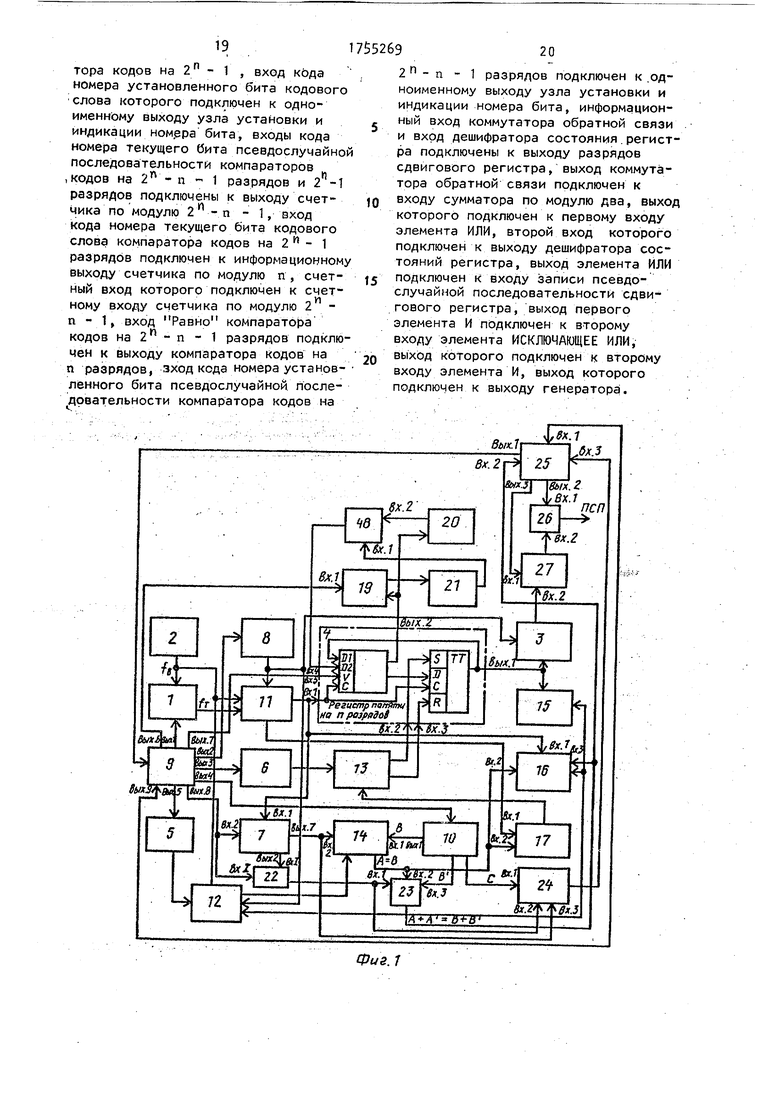

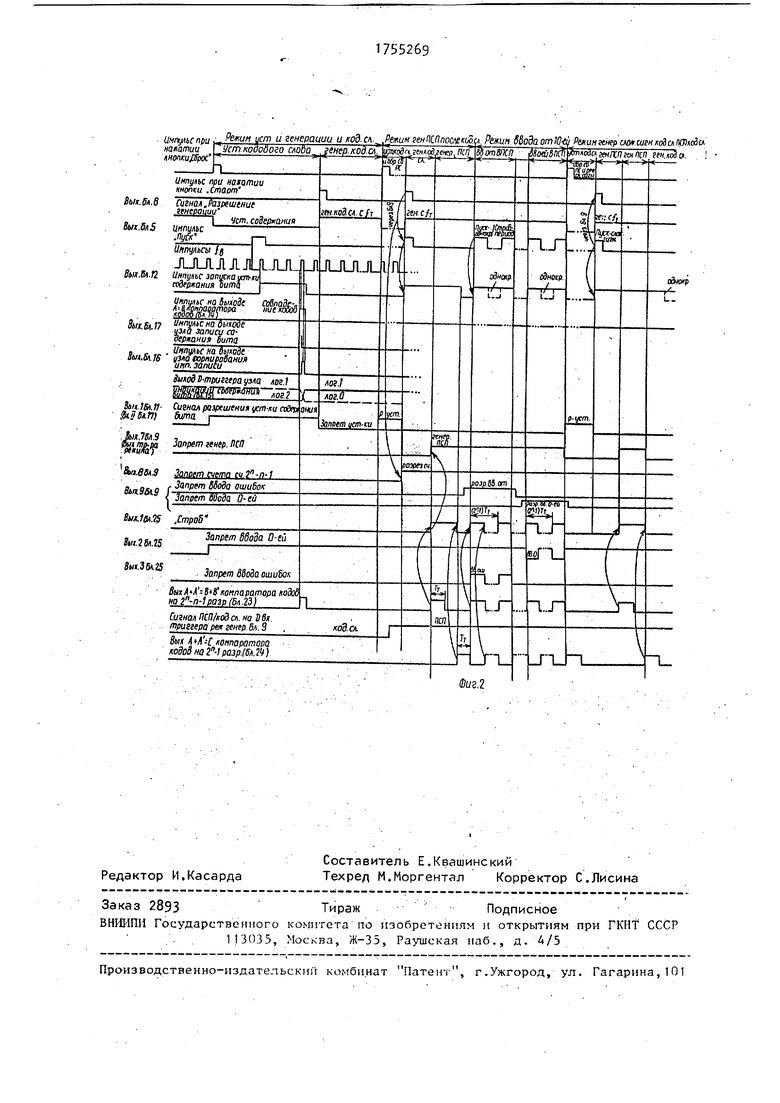

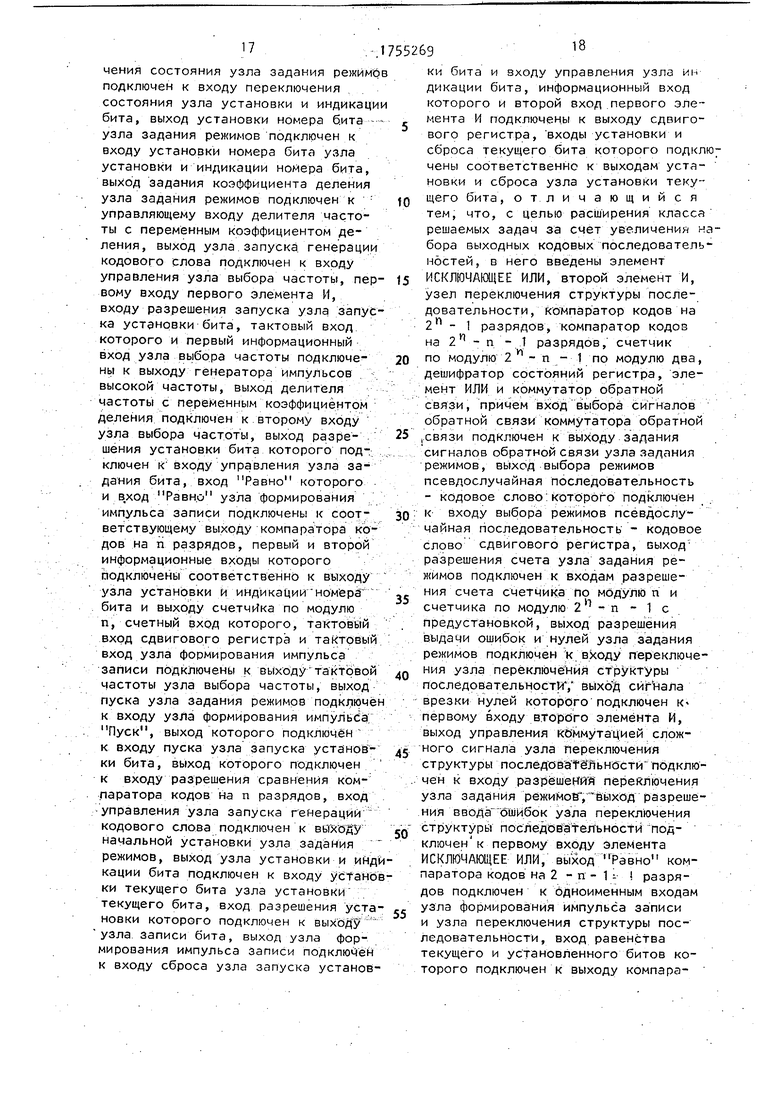

На фиг о 1 представлена структурная схема предлагаемого генератора; на фиг«2 - временная диаграмма работы устройства„

Генератор содержит делитель 1 с переменным коэффициентом деления, генератор 2 импульсов высокой частоты, первый элемент И 3, сдвиговой

регистр 4 на п разрядов (регистр памяти), узел 5 формирования импульса Пуск, узел 6 установки и индикации бита, счетчик по модулю п с предустановкой, узел 8 запуска генерации кодового слова, узел 9 задания режимов (управления генерацией), узел 10 установки и индикации номера бита, узел 11 выбора частоты, узел 12 запуска установки бита, узел 13 установки текущего бита, компаратор 14 кодов на п разрядов, узел 15 индикации бита,узел 16 формирования импульса записи, узел 17 записи бита, элемент ИЛИ 18, коммутатор 19 обратной связи, дешифратор -20 состояния регистра, сумматор 21 по модулю два, счетчик 22 по модулю 2h - п - 1 с предустановкой, комХ|

СП

го о ю

паратор 23 кодов на - п - 1 разрядов .компаратор 2 ( кодов на 2П - 1 разрядов, узел 2S переключения структуры последовательности, второй элемент И 26, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 27.

Функционирование ГКС возможно в четырех независимых режимахс

1t Установка содержания и генерация кодового слова, состоящего из п бит информации с

2. Генерация псевдослучайной последовательности (ГСП) после выдачи любого из битов кодового слова с возможностью индикации содержания последовательности„

Зс Генерация ПСП с введением в структуру последовательности одиночных или периодически бинарных ошибок или блоков (сегментов) из О, начиная с определенного номера бита.

к Генерация сложного сигнала со структурой - сначала кодовое слово, затем ПСП, затем кодовое слово, выбранное по номеру бита из ПСП.

Работа в первом режиме регенерации происходит следующим образом

Узел задания режимов (блок 9, фиг.1) в этом случае вырабатывает на своем седьмом выходе сигнал О, подключающий выход разряда п регистра памяти (блок Ц) на первый информационный вход первого разряда этого регистра и запрещающий прием выходного сигнала элемента ИЛИ (,блок 18) на второй информационный вход первого разряда сдвигового регистра 4.

Для обеспечения работы ГКС в первом режиме генерации кодового ело- , ва, содержащего п бит информации, необходимо записать произвольную комбинацию из 1 и О в сдвиговый регистр k на п разрядов Для этого на вход узла 8 запуска генерации кодового слова выдается импульс сброса с выхода узла 9 задания режимов, который вырабатывается, например, при нажатии кнопки Сброс, входящей в состав узла 9« После прихода импульса сброса с выхода узла 8 выдается низкий уровень сигнала Разрешение генерации (фиг.2), запрещающий генерацию кодового слова с тактовой частотой fT, разрешающий установку содержания кодового слова с высокой частотой f g, и закрывающий

клапанирующую схему И 3, запрещая выдачу кодового слова с генератора в процессе установки содержания,, Выбор импульсов с частотой следования fт и f6 осуществляется в зависимости от поступающего сигнала Разрешение генерации,

После этого с помощью узла 9 за0 дания режимов и узла 10 установки и индикации номера бита устанавливается номер выбранного для записи бита

Параллельный код номера устанав5 ливаемого бита с выхода узла 10

поступает на компаратор кодов И, по которому контролируют установку номера бита. После этого устанавливают содержание бита, которое необ0 ходимо записать в выбранный разряд сдвигового регистра о

Для этого с выхода узла 9 на вход узла 6 установки и индикации содержания 1 и О поступает

5 импульс 1 - 0 положительной полярности, который вырабатывается, например , кнопочным переключателем 1 - 0м узла 9. Импульс 1 - 0 поступает на вход узла 6 и устанавлива0 ет его вход в другое, отличное от первоначального, состояние (1 или О). Напряжение 1 или О с выхода узла 6 поступает на узел 13 установки текущего битас При этом

5 светодиодный индикатор 1 - 0 узла 6 служит для визуального контроля устанавливаемого содержания бита кодового слова о

Далее осуществляется формирова0 ние на выходе узла 9 импульса разрешение установи бита (например, при помощи кнопки Пуск), который поступает на вход узла 5 формирования импульса Пуск. Узел формирова5 ния импульса Пуск вырабатывает

импульс Пуск необходимой длительности , который поступает на вход узла 12 запуска установки бита. На выходе узла 12 при поступлении

0 на его вход импульса Пуск по переднему фронту импульса высокой частоты f& формируется сигнал запуска установки содержания бита, поступающий на вход А В компаратора И

Ј кодов для разрешения процесса сравнения кодов номеров текущего бита (А) и номеров устанавливаемого бита (В). Сигнал с выхода узла запуска установки содержания вырабатывается по переднему фронту сигнала высокой частоты для привязки начала процесса сравнения параллельного кода номера устанавливаемого бита (В) с параллельным кодом текущего бита (А) в компараторе кодов к высокой частоте.,

Параллельный код номера текущего бита поступает на группу входов А компаратора кодов с выхода непрег рывно работающего счетчика по модул п с предустановкой. Когда код на группе выходов счетчика по модулю п с предустановкой станет равен коду номера устанавливаемого бита (К-й бит на фиг.2) на выходе компартора кодов появится потенциал 1, который поступает на вход узла 17 записи бита. При появлении переднего фронта сигнала А В на выходе узла 17 появляется фронт импульса записи содержания бита при условии, если на втором входе узла 17 имеетс сигнал разрешения установки бита, поступающий с выхода узла 11 выбора частоты. Задний фронт импульса установки содержания бита, который поступает на вход узла 13, формируется узлом 17 спустя небольшой промежуток времени, меньший или равный длительности импульса сигнала высок частоты fg, (фиг,2). На второй вход узла 13 поступает сигнал содержания 1 или О устанавливаемого бита с выхода узла 6.

Если на выходе узла b имеется потенциал О, то импульс записи бита пройдет через узел 13 на вход R D-триггера разряда сдвигового регистра и установит содержание текущего бита К кодового слова в состояние О. Если на выходе узла 6 имеется потенциал 1, то импульс записи бита пройдет через узел 13 на вход S D-триггера разряда п сдвигового регистра 4 и установит содержание текущего бита К кодового слова в состояние 1.

Правильность установки содержани выбранного бита К, номер которого поступает на группу входов В компараторов кодов, достигается за счет синхронной работы счетчика 7 по модулю п с предустановкой и сдвиговог регистра k на п разрядов.

Потенциал 1 на выход А В компаратора 14 кодов поступает также на вход узла 16 формирователя

О

5

0

5

0

5

0

5

0

5

импульсов записи, на другой вход которого поступает сигнал высокой частоты f& с выхода узла 11. На выходе узла 16 по фронту инвертированного сигнала высокой частоты f& формируется фронт импульса записи бита, поступающий на вход узла 12 запуска установки бита и на вход узла 15 индикации бита в момент, хо- да на выходе А В узла 14 имеется потенциал 1.

Потенциал 1 с выхода узла 16 поступает на вход сброса узла 12 запуска установки бита, после чего на выходе узла 12 формируется задний фронт импульса установки бита. Потенциал О, поступающий на вхсд компаратора кодов 1, вызовет появление заднего фронта импульса срав- не ния кодов А В на выходе узла 14, который поступает на вход сброса узла 160 По заднему фронту импульса А В узел 16 вырабатывает задний фронт импульса записи (фиг02) и заканчивает процесс установки содержания бита К„

На информационный вход узла 15 индикации блока поступает сигнал содержания с выхода разряда п регистра А на п разрядов. На синхровход узла 15 приходит сигнал записи бита с выхода узла 16, который переписывает содержание бита К в D-триггер узла 15 индикации бита.

Длительность импульса записи бита на выходе узла 16 будет определяться суммой времен задержки переключения узла запуска установки бита, компаратора кодов, узла 16„ После установки содержания бита К устройство находится в режиме ожидания либо до следующей записи содержания какого-либо 1-го бита кодового слова, либо до начала генерации кодового слова

Для начала генерации кодового слова необходимо подать с выхода узла 9 на вход узла 8 запуска генерации кодового слова импульс Старт, выработанный, например, при нажатии соответствующей кнопки. По фронту импульса Старт узел запуска генерации кодового слова вырабатывает фронт импульса Разрешение генерации (фиго2)8 разрешающий появление импульсов с частотой следования fr на выходе узла 11 и запрещающий

выработку сигнала записи бита в узле 17.

После этого, выполняя описанные операции и нажимая кнопку Пуск можно, проконтролировать содержание выбранного бита в момент появления его на выходе элемента И 3, так как при нажатии этой кнопки не будет осуществляться выработка импульса; записи бита в момент равенства кодов на группах входов А и В компаратора кодов, а сигнал записи содержания в D-триггере узла индикации бита вырабатываться будет На вход клапанирующего элемента И подан сигнал разрешения генерации с выхода узла 8. Поэтому сигнал с выхода D-триггера разряда п сдвигового регистра на п разрядов через элемент И 3 пройдет на вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 27.

Сигналами На восьмой группе выходов узла задания режимов 9 запрещается работа счетчика по модулю 2п - п - 1, а сигналами О на девятой группе выходов узла k (сигналы разрешения ввода ошибок и разрешени ввода нулей) запрещается ввод ошибок в структуру ПСП и ввод в структуру ПСП сегментов нулей. При этом на .втором, выходе узла 25 имеется сигнал уровня 1, запрещающий ввод нулей при помощи схемы И (блок 26), а на третьем выходе узла 25 при-, сутствует сигнал О запрещающий ввод бинарных ошибок в структуру ПСП при помощи элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 27. Сигнал кодового слова выдается на выход устройства ГКС через элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 27 и второй элемент И 26, представляющие собой повторители информации, приходящей с выхода первого элемента И 3 В этом режиме узел задания режимов 9 при помощи узла 10 установки и индикации номера бита устанавливает на третьей группе входов компаратора кодов на

п - 1 разрядов 23 сигналы уров2П ня

Счетчик 22 по модулю 2П - п - 1 с предустановкой выдает на первую группу входов компаратора 23 кодов на п - 1 разрядов сигналы уровня О, что заставляет этот компаратор 23 пропускать сигнал А В с выхо

0

5

0

5

0

5

0

5

да компаратора k кодов на п разрядов 1 на третий вход узла 16 формирования импульса, записи, которая вырабатывает короткий импульс записи бита кодового слова в триггере узла 15 индикации бита при совпадении сигналов на втором и третьем входах, где присутствует сигнал А В, поступающий с выхода компаратора И, что позволяет индицировать содержание любого бита кодового слова в момент появления его на выходе устройства ГКС,

Работа в режиме генерации ПСП после выдачи любого из битов кодового слова с возможностью индикации содержания последовательности производится следующим образом. Сигналами на шестой группе выходов узла 9 задания режимов, включающего п сигнальных линий, выбирается требуемая для генерации ПСИ конфигурация сигналов обратной связи в коммутаторе 19 обратной связи

Коммутатор 19 обратной связи представляет собой набор из п элементов И, на первый вход каждого из которых подключен один из выходов разрядов сдвигового регистра Ц памяти на п разрядов, а на второй вход этих элементов И коммутатора 19 обратной связи подключен соответствующий сигнал выбора конфигурации обратной связи с шестой группы выходов узла 9. При этом на вход сумматора 21 по модулю два проходят только те сигналы с выходов разрядов регистра памяти, на разрешающем входе элементов И которых в коммутаторе 19 обратной связи имеется сигнал 1, поступающий по соответствующей линии конфигурации обратной связи из узла 9 На входы сумматора 21 по модулю два приходят через коммутатор 19 обратной связи сигналы с выходов тех разрядов регистра 4 памяти, которые разрушены сигналами уровня 1, поступающими с шестой группы выходов узла 9 на первую группу входов конфигурации обратной связи коммутатора 19f а на другие входы сумматора 21 по модулю два поступают сигналы уровня О и не участвуют в операции сложения.

Сигнал суммы по модулю два выбранных разрядов регистра k с выхода сумматора 21 поступает на первый

9

вход элемента ИЛИ 18, на второй вхо которого поступает сигнал с выхода дешифратора 20 состояния регистра, который вырабатывает сигнал уровня 1 в случае, если на всех п выхода регистра памяти имеются сигналы уровня О.

Таким образом, на выходе элемента ИЛИ 13 ПОЯВИТСЯ СИГНаЛ СУММЫ ПО

модулю два содержания разрядов регистра k, выбранных коммутатором обратной связи, если состояние хот бы одного разряда регистра 4 памяти представляет собой 1, или сигнал уровня 1, если состояние всех разрядов регистра k представ.- ляет собой О. Дешифратор 20 состния регистра памяти и элемент ИЛИ 18 позволяют ликвидировать запрошен ную комбинацию состояния регистра А памяти, когда содержание всех ег

разрядов соответствует

На пятый вход регистра k памяти подается сигнал О после нажатия кнопки Сброс узла У, для подключения сигнала обратной связи с выхода разряда п на вход Д1 первого разряда регистра памяти, а на второй вход счетчика 22 по модулю 2П - п - 1

с предустановкой поступает с восьмого узла 9 сигнал сброса.

При этом разрешается установка содержания регистра А памяти под управлением схемы выборочной побитной 35 поступающего с выхода компаратора

1 кодов на п разрядов; импульс заПосле этого в момент совпадения кода на выходе счетчика 7 по модулю п с предустановкой с кодом номера бита на первом выходе узла 10 осуществится процесс записи содержания 1 - 0 выбранного бита при помощи узла 17 записи бита, который вырабатывает короткий импульс записи бита по фронту сигнала А В,

установки содержания кодового слова, которая включает узел 5 формирования импульса Пуск, узел 12 запуска установки бита, узел 8 запуска генерации кодового слова, узел 40 6 установки и индикации бита, узел 10 установки и индикации номера бита , узел 11 выбора частоты, узел 13 установки текущего бита, узел 17 записи бита, узел 16 формирования 5 импульса записи, узел 15 индикации бита. По импульсу Сброс узла 9 узел 8 запуска генераций кодового слова запрещает выдачу сигналов кодового слова через элемент И и разрешает установку содержания при помощи ее выходного сигнала Разрешение генерации, поступающего на узел 11, элемент И 3 и узел 12 запуска установки бита и имеющего уровень О. Далее при помощи импульсов 1 - 0 на третьем выходе узла 3 устанавливается требуемое содержание О или 1 при помощи узла 6

50

55

писи бита, меньший или равный по длительности половине периода сигна ла fe, поступает через узел 13 на Н -вход D-триггера разряда п регистра J памяти, если на выходе узла 6 установки и индикации содержа ния 1 - 0 имеется сигнал 1 - О уровня О, или на 8 -вход D-триггера разряда п регистра k памяти, ес ли на выходе узла 6 имеется сигнал 1 - 0 уровня 1, и устанавливает содержание 1 - 0 выбранного 1-го бита кодового слова в момент появления его на выходе разряда п регистра t памяти. После этого по срезу сигна ла f& узлом 16 формируется импульс индикации бита, меньший или равный половине периода сигнала f6, поступающий на синхровход узла 15 индикации бита для переписи содержания 1-го бита в регистр узла 15 и на вход сброса узла 12 запуска установки бита для формирования среза сигна

10

,

Q

Q

установки 1 и О

Аи

и индикации содержания а при помощи импульсов

- устанавливается код номе5

0

5 поступающего с выхода компаратора

ра устанавливаемого бита на первом выходе узла 10 установки и индикации номера бита и нажимается кнопка Пуск узла 9; с выхода узла 11 на входы синхронизации регистра памяти на п разрядов счетчика 7 по модулю п с предустановкой и узла 16 подключается сигнал высокой частоты fg, с выхода генератора 2 импульсов высокой частоты, что гарантирует синхронную работу этих узлов устройства ГКС„ ИМПУЛЬС Пуск, нормированный по длительности и амплитуде в узле 5 формирования импульса Пуск, поступает на узел 12 запуска установки бита, вызывает ее срабатывание и появление на входе разрешения сравнения кодов компаратора кодов на п разрядов сигнала уровня 1.

После этого в момент совпадения кода на выходе счетчика 7 по модулю п с предустановкой с кодом номера бита на первом выходе узла 10 осуществится процесс записи содержания 1 - 0 выбранного бита при помощи узла 17 записи бита, который вырабатывает короткий импульс записи бита по фронту сигнала А В,

0 5

0

5

писи бита, меньший или равный по длительности половине периода сигнала fe, поступает через узел 13 на Н -вход D-триггера разряда п регистра J памяти, если на выходе узла 6 установки и индикации содержания 1 - 0 имеется сигнал 1 - О уровня О, или на 8 -вход D-триггера разряда п регистра k памяти, если на выходе узла 6 имеется сигнал 1 - 0 уровня 1, и устанавливает содержание 1 - 0 выбранного 1-го бита кодового слова в момент появления его на выходе разряда п регистра t памяти. После этого по срезу сигнала f& узлом 16 формируется импульс индикации бита, меньший или равный половине периода сигнала f6, поступающий на синхровход узла 15 индикации бита для переписи содержания 1-го бита в регистр узла 15 и на вход сброса узла 12 запуска установки бита для формирования среза сигнала разрешения сравнения кодов, поступающего на вход компаратора 14,

Таким же образом осуществляется установка содержания вс.ех остальных битов кодового слова, содержание которых контролируется по состоянию узла 15 индикации бита.

Набранное кодовое слово является начальным состоянием регистра 4 памяти для генерации сигналов ПСП.

Переход к генерации ПСП осуществляется следующим образомо

Переключатель ПСП/кодовое слово узла -управления генерацией устанавливается в положение ПСП, что соответствует появлению сигнала уровня 1 на D -входе D-триггера установки режима генерации узла 9,

на С -вход которого подключен сигнал Строб с выхода узла 25, а на К -вход подается импульс Сброс

Сигнал с выхода D-триггера узла 9 поступает на вход переключения информационных входов первого разряда регистра k сдвига на п разрядов. После этого нажимается кнопка Старт, которая генерирует импульс запуска генерации, поступающий на вход узла 8 и на 3 -вход первого триггера узла 25, который переключается в состояние разрешения старта ПСП, когда на его выходе присутствует сигнал уровня 1 Узел 8 запуска генерации кодового слова вырабатывает сигнал Разрешение генерации уровня 1, по которому осуществляется подключение к синхро- входам блоков k, 7, 16 вместо сигнала частоты fй, сигнала тактовой частоты Јт и открывается первый элемент И Зс По сигналу Старт снимается сигнал сброса со счетчика 22 по модулю 2 и - п - 1 с предустановкой, который включен каскадно со счетчиком 7 по модулю п с предустановкой. Вместе эти два счетчика представляют собой счетчик по модулю 2П- 1 с предустановкой.

Код текущего бита А с выхода счетчика 7 по модулю п с предустановкой поступает на вход компаратора 1 кодов на п разрядов, а код А1 с выхода счетчика по модулю 2П - п с предустановкой поступает на первый вход компаратора 23 кодов на 2 - п - i разрядов. Эти компараторы включены каскадно и их можно рассматривать ка

.-,

0

5

0

один компаратор кодов на 2 п - 1 разрядов, на вход которого подключен код А + А1 с выхода каскадного счетчика (блоки 7 и 22),

Код текущего бита с выхода каскадного счетчика (блоки 7 и 22) А + А поступает также на второй и третий входы компаратора 2k кодов на 2П - 1 разрядов. На вторые группы входов каскадного компаратора (блоки 14 и 23) поступает код В + В1 1 номера устанавливаемого бита с выхода узла 10 установки и индикации номера бита, который в этом режиме представляет собой код номера бита кодового слова, лежащий в пределах от 0 до п, по которому осуществляется запуск генерации ПСП в регистре 4 памятно Когда код А + станет равен коду В + в на втором входе каскадного компаратора (блоки 14 и 23), на выходе компаратора 23 кодов

на 2 - п - 1 разрядов появится фронт импульса совпадения кодов А + А В + в , равного по длительности периоду тактовой частоты fT, который поступит на синхровход D-триггера узла 25 и установит его выход в состояние 1. На выходе D-триггера узла 25 появится фронт сигнала Строб, поступающий на синхровход D-триггера установки режима генерации узла 9, на выходе

35

которого появится сигнал уровня 111 поступающий на вход первого

Т

40

45

50

55

разряда регистра 4 памяти для коммутации информационных входов этого разряда.

Таким образом, в регистре 4 памяти начнется процесс генерации ПСП при появлении на выходе разряда п этого регистра бита кодового слова, номер которого был установлен ранее при помощи узла 10 установки и индикации номера бита на втором входе В компараторе 14 кодов на п разрядов.

Сигнал ПСП проходит без изменения через элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 27 ;и второй элемент И 26 на выход элемента 26, который является выходом устройства ГКСо

В этом режиме возможна индикация содержания любого К-го бита кодового слова в-момент его появления на выходе устройства ГКС. Для этого номер К набирается при помощи кнопок f и Ч узла 9 , в узле 10 установки и индикации номера бита, откуда код

этого номера через группы выходов С1 и В подается на вход В - В1 каскадного крмпаратора кодов (блоки Ik и 23). После этого нажимается кнопка Пуск Ч Когда код текущего номера бита Л + А на выходе каскадного счетчика по модулю 2П - 1 с предустановкой (блоки 7 и 22) совпадает с установленными В + В1 на вы ходе компаратора кодов на 2п - п - 1 разрядов появится импульс длительностью 1/Sr, поступающий на третий вход узла 16, на втором входе которого обязательно присутствует такой же импульс с выхода компаратора кодов на п разрядов

По совпадению сигналов на этих входах узла 16 со срезом сигнала тактовой-частоты fT, узел 16 выдает короткий импульс записи бита на входы узла 12 запуска установки бита и узла 15 индикации бита. Фронтом импульса записи содержания бита содержание К-го бита К 1,2,. ,2 - 1) будет переписано в регистр индикации в узле 15 индикации бита и проинди- цировано при помощи точечного свето- диода .

Режим генерации кодового слова с введением в структуру ПСП одиночных и периодических бинарных ошибок или сегментов из О производится после перевода устройства ГКС в режим генерации ПСП, Дле генерации ПСП с бинарными ошибками узел 9 вырабатывает сигнал уровня Введение ошибок, поступающий на вход элемента И узла 25. Элемент И узла 25 пропускает сигнал Строб на второй вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 27 для инвертирования ПСП, что соответствуе введению бинарных ошибок.

Для введения в структуру ПСП сег ментов О на вход элемента И-НЕ узла 25 с выхода узла 9 подается сигнал Ввод нулей уровня 1, что позволяет пропустить сигнал Строб на выход элемента И-НЕ, откуда инвертированный импульс Строб поступит на вход второго элемента И 26, запрещая выдачу ПСП на выход устройства ГКС во время его действия

ровходы соответствующих счетных триггеров, выходные сигналы которых подаются на входы узла 25 При первом нажатии кнопки на выходе соответствующего счетного триггера появится сигнал 1, а при повторном нажатии J О,

Сигнал Строб формируется при помощи каскадного счетчика по модул 211 - 1 с предустановкой (блоки 7 и 22), каскадного компаратора кодов на 2П - 1 разрядов (блоки И и 23), компаратора 2k кодов на 2м - 1 разрядов узла 10 установки и индикации номера бита 10 и узла 25о Лля этого при помощи кнопок т и узла 9 устанавливается начальный код номера-бита j на выходах В и Bfl этого узла, подключенных к каскадному компаратору Кбдов (блоки Ik и 23) и конечный код номера бита m на выходе С узла 10, подключенном к первому входу компаратора 2k кодов на 2П - 1 разрядов.

Нажимается кнопка Пуск. На - входе разрешения сравнения кодов каскадного компаратора кодов на 2П - 1 разрядов (блоки k и 23) появляется Когда код на выходе каскадного счетчика (блоки 7 и 22) станет равен коду номера бита j, на выходе каскадного компаратора (блоки 14 и 23) появится импульс А + А В + В , равный по длительности периоду сигнала тактовой частоты ff-, который поступает на синхровход D-григгера узла 25, на D-вход которого подан сигнал уровня 1 с выхода RS-триггера этой схемы с,

По фронту сигнала А + А В + В на выходе D-триггера 25 будет сформирован фронт сигнала Строб, срез которого будет сформирован по фронту импульса А + А С, поступающему с выхода компаратора 2k кодов на 2П - 1 разрядов в момен когда текущий код номера бита на выходе, каскадного счетчика (блоки 7 и 22) станет равен коду конечного бита По

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор кодового слова | 1988 |

|

SU1603361A1 |

| Устройство для контроля многовыходных цифровых узлов | 1984 |

|

SU1176333A1 |

| Устройство для контроля знаний обучаемых | 1987 |

|

SU1524082A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| АВТОМАТИЗИРОВАННОЕ РАБОЧЕЕ МЕСТО ОПЕРАТОРА УПРАВЛЕНИЯ ВОЗДУШНЫМ ДВИЖЕНИЕМ | 2001 |

|

RU2219586C2 |

| Устройство для сопряжения внешних устройств с накопителем на магнитной ленте | 1984 |

|

SU1348842A1 |

| Устройство для анализа логических состояний | 1980 |

|

SU1096648A1 |

| Устройство для ввода информации | 1979 |

|

SU855649A1 |

| Единый генератор псевдослучайных последовательностей (ПСП) приемника сигналов Глобальных Навигационных Спутниковых Систем (ГНСС) | 2022 |

|

RU2789320C1 |

| Устройство для сопряжения цифровой вычислительной машины с магнитофоном | 1984 |

|

SU1188745A1 |

Изобретение относится к радиоизмерительной технике и может быть использовано в генераторах тест- сигналов. Цель изобретения - расшире- , ние класса решаемых задач за счёт увеличения набора генерируемых кодовых последовательностей. Поставленная цель достигается за счет введения элемента ИЛИ, коммутатора, обратной связи, дешифратора состояния регистра, сумматора по модулю два, счетчика по модулю 2П - п - 1 с предустановкой, компаратора кодов на 2 - п - 1 разрядов,компаратора кодов на 2°. - 1 разрядов, узла переключения структуры последовательности, второго элемента И, элемента ИСКЛЮЧАЮЩЕЕ ИЛИ. 2 ил. : :

Сигналы Ввод нулей и Ввод ошибок могут быть сформированы при помощи двух кнопок, снабженных анти- дребезговыми схемами, выходные импульсы которых подключены на синх

Длительность импульса СтроЬ будет кратна периоду сигнала Јт, что позволяет использовать его для введения блоков бинарных ошибок или нулей в структуру выходной ПСП.

В однократном режиме ввода ошибок после выработки сигнала А+А В + в срабатывают узел 16 формирования импульса и узел 12 запуска установки бита и снимают сигнал разрешения сравнения кодов уровня 1 с входа каскадного компаратора (блоки 14 и 23). На этом однократный ввод бинарных ошибок или нулей в ПСП заканчивается до следующего накатия кнопки Пуск Периодический ввод в структуру ПСП блоков бинарных ошибок Или Нулей осуществляется при помощи коммутатора узла 9, подклю- чающего на вход схемы нормирования импульса Пуск наряду с импульсом кнопки Пуск узла 9 сигнал Строб с выхода узла задания режимов 25.

Схема формирования импульса / Пуск в многократном режиме формируется импульс Пуск по длительности и амплитуде при наличии на ее входе сигнала Строб в режиме периодического ввода ошибок или нулей или Пуск в режиме однократного ввода. При этом период ввода блоков бинарных ошибок или нулей s структуру ПСП будет составлять 2П - 1 тактовых интервалов, а начало этого периодического процесса будет инициироваться нажатием кнопки Пуск.

Сигнал режима Периодический/однократный может быть подан с соответствующего счетного триггера узла 9 состояние которого может изменяться сигналом соответствующей кнопкио

Режим генерации сложного сигнала типа кодовое слово - ПСП - кодовое слово, выбранное по номеру бита из ПСП, реализуется следующим образом. При помощи схемы побитной выборочной установки содержания кодового слова (узлы 5, 12, 8, 11, 6, 7, 14, 13, 1C 15, 16, 17) устанавливается п-разряд ное кодоЁое слово в регистре 4 памят

ГКС.

При помощи кнопки и счетного триггера установки режима генерации сложного сигнала генерируется сигнал уровня 1 на входе коммутатора режима узла управления генерацией, который подключает к входу выбора информационного входа первого разряда регистра 4 памяти вместо сигнала с выхода стартового RS-триггера узла

0

0

5

0

5

9, сигнал Строб, поступающий с выхода узла 25.

В режиме генерации сложного сигнала регистр памяти разрядов будет генерировать кодовое слово, когда сигнал Строб имеет О, или ПСП, когда сигнал Строб будет иметь уровень 1. Выбирается режим однократного запуска генерации сложного сигнала или режим периодической его генерации при помощи сигнала режима Периодический/однократный.

При помощи схемы установки и индикации номера бита устанавливаются код j номера бита начала генерации ПСП на группе выходов В + .В узла 10 и код m на группе выходов С номера бита конца генерации ПСП в - составе сложного сигнала с циклом повторения 211 - 1 тактовых интервалов. Нажимается кнопка Пуск, после чего начинается выработка сложного составного сигнала. Причем после выдачи отрезка ПСП регистр 4 памяти будет генерировать кодовое слово, соответствующее содержанию последнего случайного числа, формируемого в этом регистре в режиме генерации ПСП, а следующий процесс начала генерации ПСП после выдачи отрезка кодового слова запустится с этого же случайного числа, если интервал выдачи кодового слова 6yflet кратен длине регистра 4 памяти на п разрядов.

Формула изобретения

Генератор кодового слова, содер- ,жащий генератор импульсов высокой частоты, делитель частоты с переменным коэффициентом деления, первый элемент И, сдвиговый регистр счетчик по модулю п, узел установки и индикации номера бита, узел установки и индикации бита, узел задания режимов, узел формирования импульса Пуск, узел запуска установки бита, узел запуска генерации кодового слова, компаратор кодов на п разрядов,. узел индикации бита, узел записи бита, узел выбора частоты, узел установки текущего бита, узел формирования импульса записи, причем выход генератора высокой частоты подключен к информационному входу делителя частоты с переменным коэффициентом деления, выход переклю

чения состояния узла задания режимо подключен к входу переключения состояния узла установки и индикаци бита, выход установки номера бита узла задания режимов подключен к входу установки номера бита узла установки и индикации номера бита, выход задания коэффициента деления узла задания режимов подключен к управляющему входу делителя частоты с переменным коэффициентом деления, выход узла запуска генерации кодового слова подключен к входу управления узла выбора частоты, пер вому входу первого элемента И, входу разрешения запуска узла запуска установки бита, тактовый вход которого и первый информационный вход узла выбора частоты подключены к выходу генератора импульсов высокой частоты, выход делителя частоты с переменным коэффициентом деления подключен к второму входу узла выбора частоты, выход разрешения установки бита которого подключен к входу управления узла задания бита, вход Равно которого и в.ход Равно узла формирования импульса записи подключены к соответствующему выходу компаратора кодов на п разрядов, первый и второй информационные входы которого подключены соответственно к выходу узла установки и индикации номера бита и выходу счетчика по модулю п, счетный вход которого, тактовый вход сдвигового регистра и тактовый вход узла формирования импульса записи подключены к выходу тактовой частоты узла выбора частоты, выход пуска узла задания режимов подключе к входу узла формирования импульса Пуск, выход которого подключен к входу пуска узла запуска установки бита, выход которого подключен к входу разрешения сравнения компаратора кодов на п разрядов, вход управления узла запуска генерации кодового слова подключен к выходу начальной установки узла задания режимов, выход узла установки и индкации бита подключен к входу устаноки текущего бита узла установки текущего бита, вход разрешения установки которого подключен к выходу узла записи бита, выход узла формирования импульса записи подключен к входу сброса узла запуска установ

to

20

25

15 75526918

ки бита и входу управления узла иь дикации бита, информационный вход которого и второй вход первого элемента И подключены к выходу сдвигового регистра, входы установки и сброса текущего бита которого подключены соответственно к выходам установки и сброса узла установки текущего бита, отличающийся тем, что, с целью расширения класса решаемых задач за счет увеличения набора выходных кодовых последовательностей, в него введены элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, второй элемент И, узел переключения структуры последовательности, компаратор кодов на 2П - 1 разрядов, компаратор кодов на 2 - п - 1 разрядов, счетчик

30

35

40

45

50

55

по модулю 2 - п - 1 по модулю два, дешифратор состояний регистра, элемент ИЛИ и коммутатор обратной связи, причем вход выбора сигналов обратной связи коммутатора обратной ,связи подключен к выходу задания сигналов обратной связи узла задания режимов, выход выбора режимов псевдослучайная последовательность - кодовое слово которого подключен к входу выбора режимов псевдослучайная последовательность - кодовое слово сдвигового регистра, выход разрешения счета узла задания режимов подключен к входам разрешения счета счетчика по модулю п и счетчика по модулю 211 - п - 1 с предустановкой, выход разрешения выдачи ошибок и нулей узла задания режимов подключен к входу переключения узла переключения структуры последовательности / выход сигнала врезки нулей которого подключен к первому входу второго элемента И, выход управления коммутацией сложного сигнала узла переключения структуры последовательности подключен к входу разрешения переключения узла задания режимов, выход разрешения ввода ошибок узла переключения структуры последовательности подключен к первому входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход Равно компаратора кодов на 2 -п- 1 i i разрядов подключен к одноименным входам узла формирования импульса записи и узла переключения структуры последовательности, вход равенства текущего и установленного битов которого подключен к выходу компараФиг. 7

| Кипятильник для воды | 1921 |

|

SU5A1 |

| т°- | |||

| - r..V , Авторское свидетельство СССР № 160336, кло G 06 F 1/02, 1982, прототип , | |||

Авторы

Даты

1992-08-15—Публикация

1989-10-06—Подача