П

4ib &9 to СП Is9 Ч

емым объектом. Логический анализатор содержит блок 1 управления,блрк 2 ввода, счетчик 3 адреса, счетчик 4 каналов, регистр 5 исходного кода, дешифратор 6, элемент ИЛИ 7, формирователь сигнатур 8, первый коммутатор 9 данных, коммутатор 10 синхросигналов записи, второй коммутатор 11 данных, блок 12 оперативной памяти, регистр 13 количества реакций, счетчик 14 реакций, формирователь импульсов 15, первый блок 16 индикации, магистральный коммутатор 17, переключатель 18 кода ввода-вывода, мультиплексор 19, блок 20 памяти заданных условий, блок 21 сравнения, второй

блок 22 индикации. Логический анализатор обеспечивает сбор данных и од- новременнук генерацию стимулирующих воздействий идентичными каналами с внешней и внутренней синхронизадаей, организацию запуска и останова по последовательностям кодовых слов, гибкое изменение, в соответствии с проверяемой схемой, соотношения входов/выходов при постоянном значении общего количества каналов, использование сжатой формы представления тестов для обучения, а также возможность самообучения, t з.п. ф-лы, 6 ил., 5 табл.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Устройство для контроля постоянной памяти | 1987 |

|

SU1451781A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1383368A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1120338A1 |

| Многоканальный сигнатурный анализатор | 1987 |

|

SU1529221A1 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| Сигнатурный анализатор | 1986 |

|

SU1386995A1 |

| Устройство для контроля и диагностики цифровых узлов | 1987 |

|

SU1587513A1 |

| Устройство для контроля логических блоков | 1986 |

|

SU1386998A1 |

. Изобретение относится к вычислительной технике и предназначено для контроля диагностики неисправностей цифровых устройств. Целью изобретения является расширение области применения и класса решаемых задач за счет обеспечения синхронизации с внешним объектом и организации обучения и самообучения в диалоговом взаимодействии-с исследу

. . 1

Изобретение относится к вычислительной технике и предназначено для

контроля и диагностики неисправностей цифровых устройств.

Целью изобретения является расширение области применения и класса решаемых задач за счет обеспечения

синхронизации с внешним объектом и организации обучения и самообучения

в диалоговом взаимодействии с исследуемым объектом.

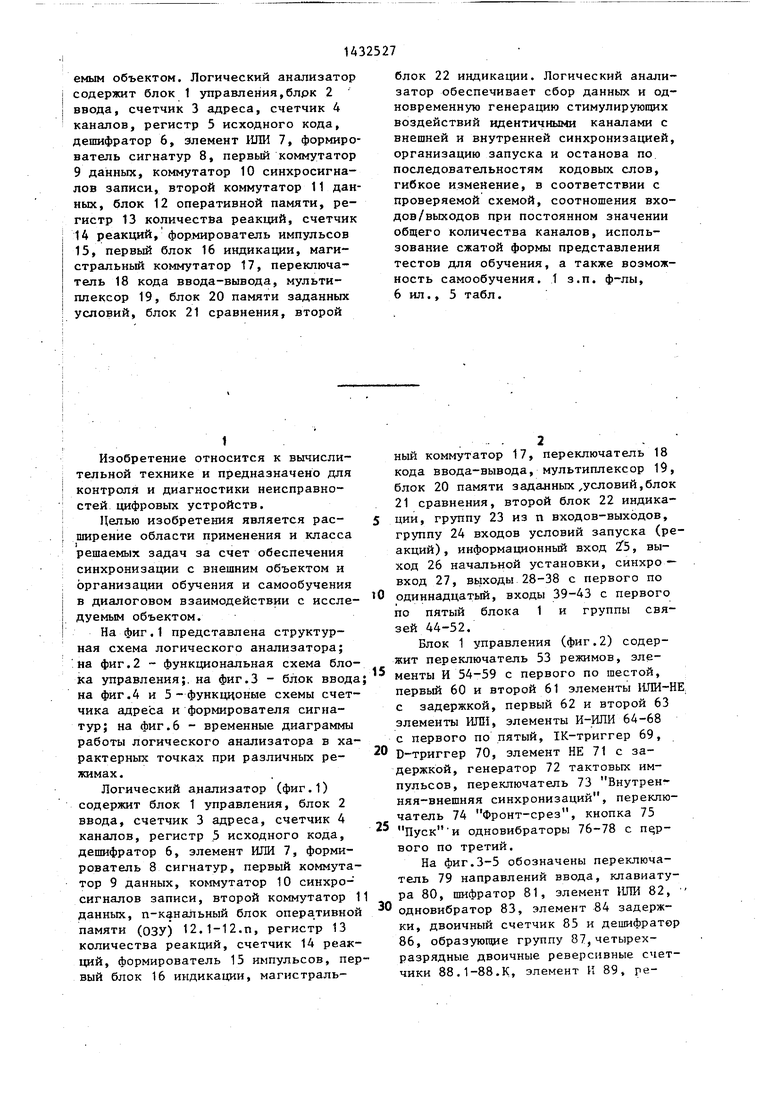

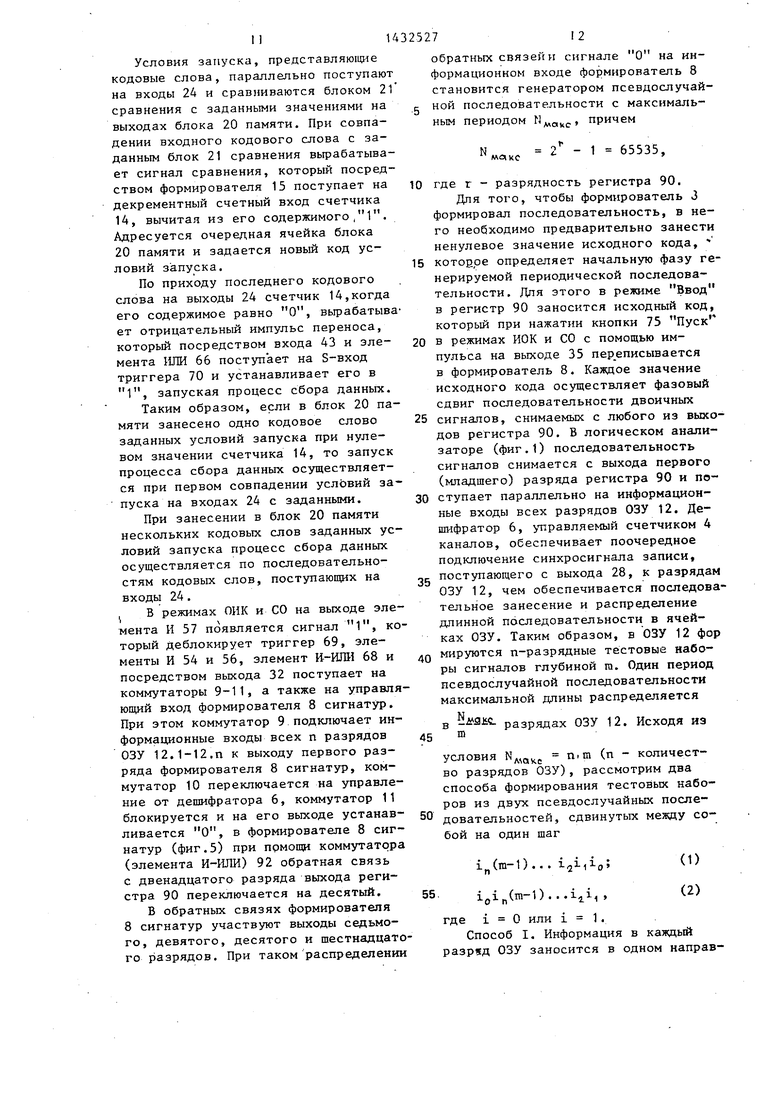

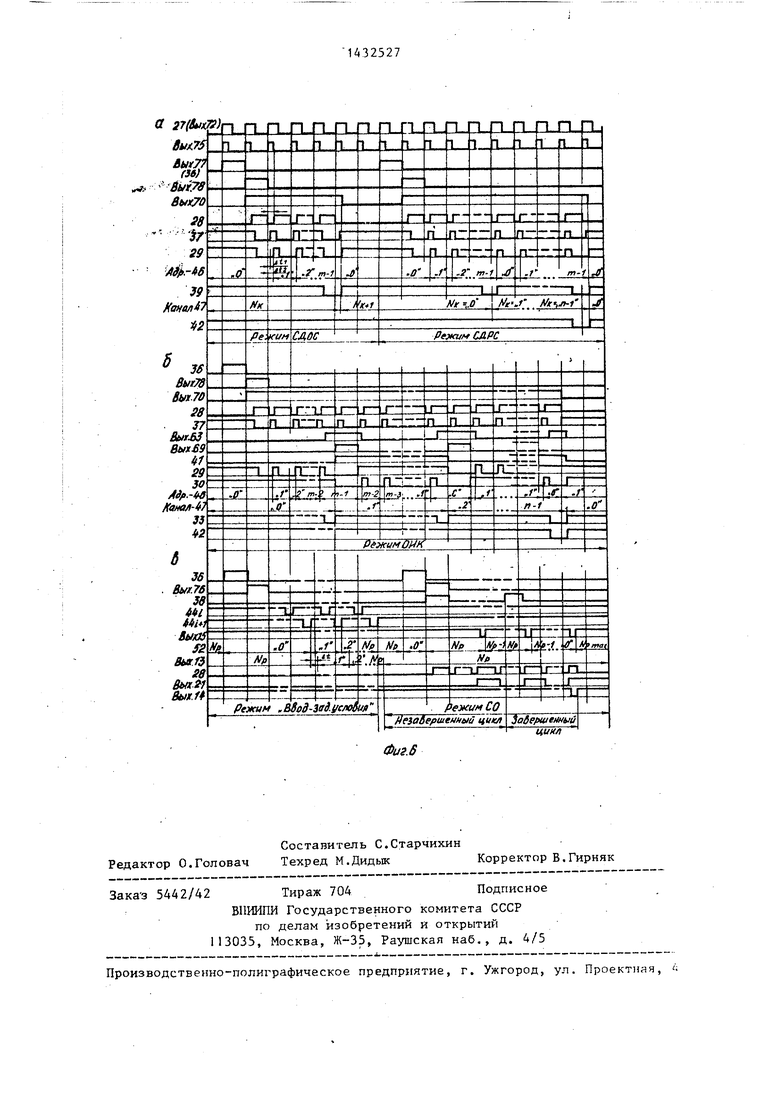

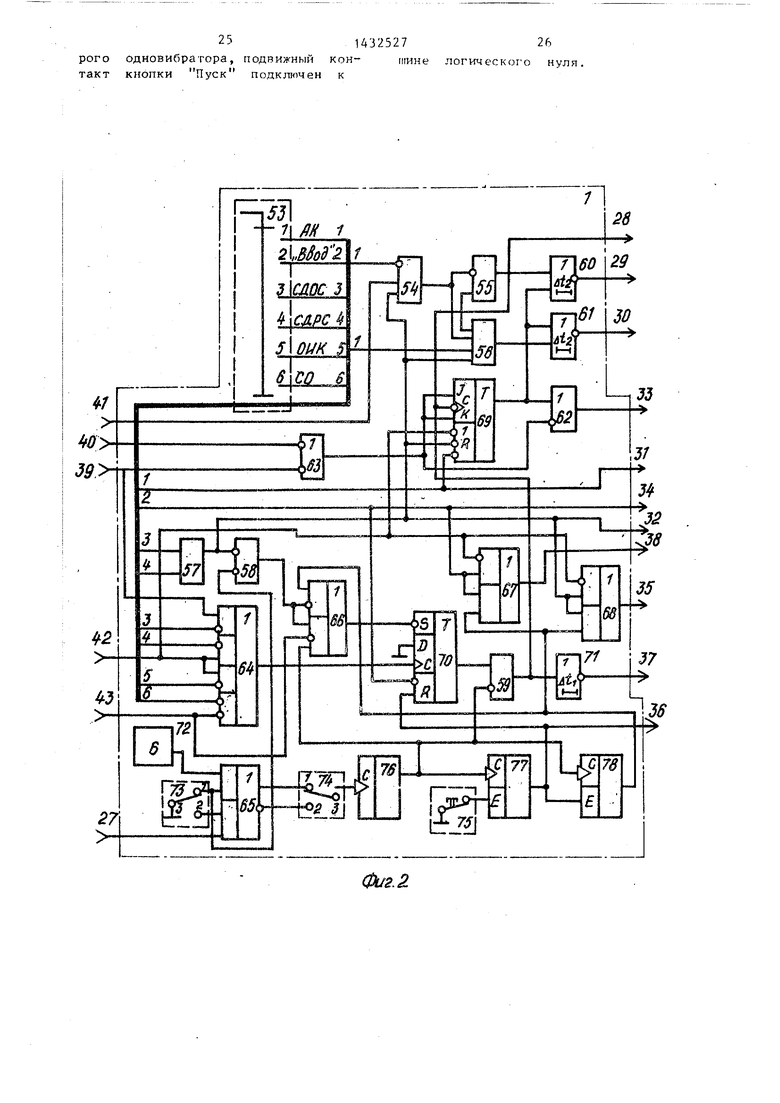

На фиг.1 представлена структурная схема логического анализатора; на фиг.2 функциональная схема блока управления;, на фиг.З - блок ввода; на фиг,4 и 5 - функццоные схемы счетчика адреса и формирователя сигнатур; на фиг.6 - временные диаграммы работы логического анализатора в характерных точках при различных режимах,

Логический анализатор (фиг,1) содержит блок 1 управления, блок 2 ввода, счетчик 3 адреса, счетчик 4 каналов, регистр 5 исходного кода, дешифратор 6, злемент ИЛИ 7, формирователь 8 сигнатур, первый коммутатор 9 данных, коммутатор 10 синхросигналов записи, второй коммутатор 11 данных, п-канальный блок оперативной памяти (ОЗУ) 12.1-12.П, регистр 13 количества реакций, счетчик 14 реакций, формирователь 15 импульсов, первый блок 16 индикации, магистральный коммутатор 17, переключатель 18 кода ввода-вывода, мультиплексор 19, блок 20 памяти заданных ,условий,блок 21 сравнения, второй блок 22 индикации, группу 23 из п входов-выходов, группу 24 входов условий запуска (реакций) , информационный вход 2f5, выход 26 начальной установки, синхро - вход 27, выходы 28-38 с первого по

одиннадцатый, входы 39-43 с первого по пятый блока 1 и группы связей 44-52,

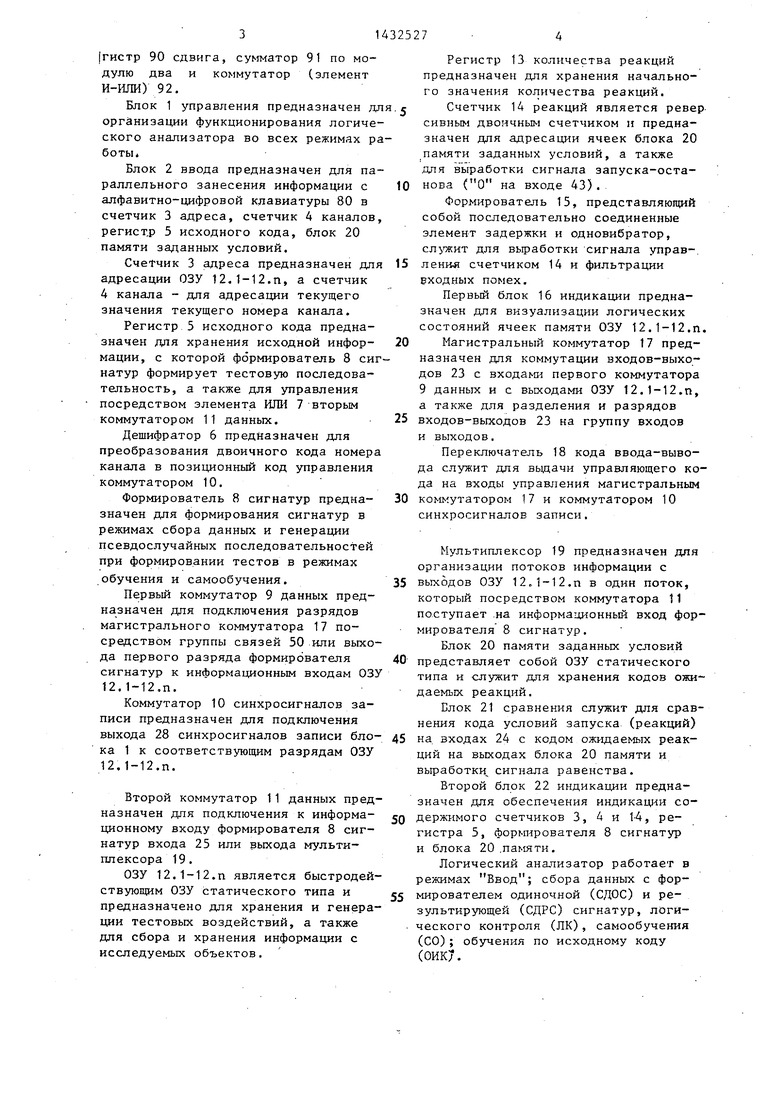

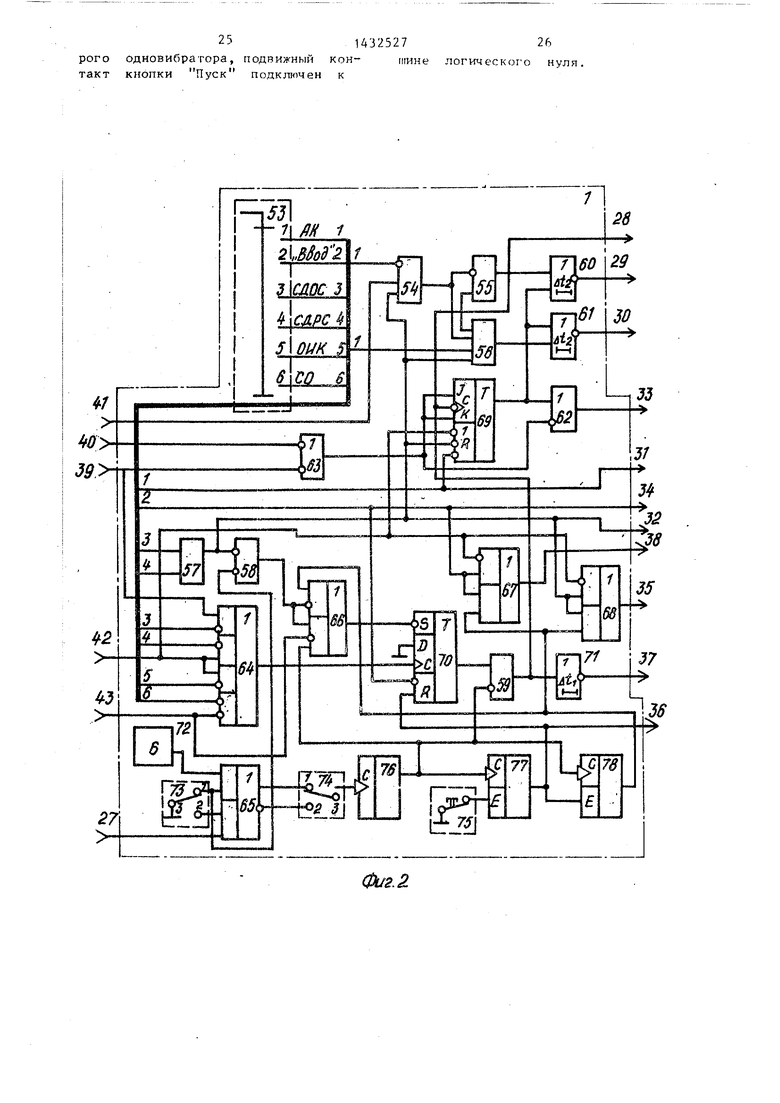

Блок 1 управления (фиг.2) содержит переключатель 53 режимов, элементы И 54-59 с первого по шестой, первый 60 и второй 61 элементы ИГШ-НЕ, с задержкой, первый 62 и второй 63 элементы ИЛИ, элементы И-ИЛИ 64-68 с первого по пятый, 1К-триггер 69,

D-триггер 70, злемент НЕ 71 с задержкой, генератор 72 тактовых импульсов, переключатель 73 Внутренняя-внешняя синхронизации, переключатель 74 Фронт-срез, кнопка 75 одновибраторы 76-78 с вого по третий.

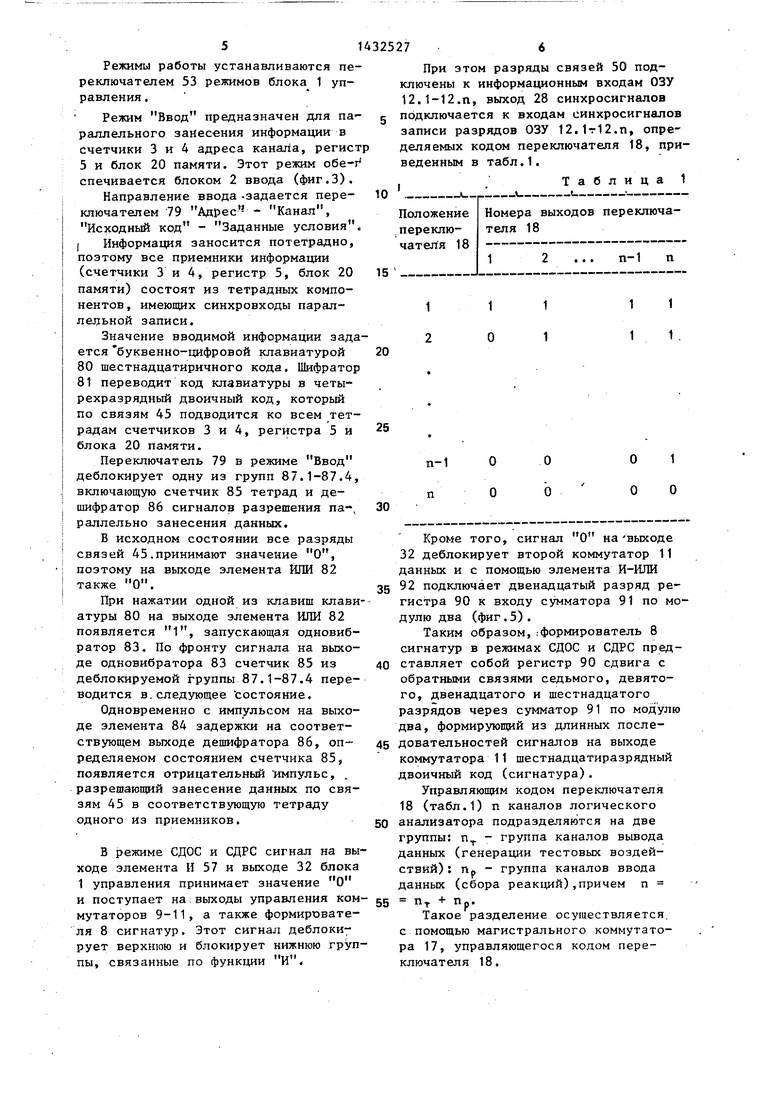

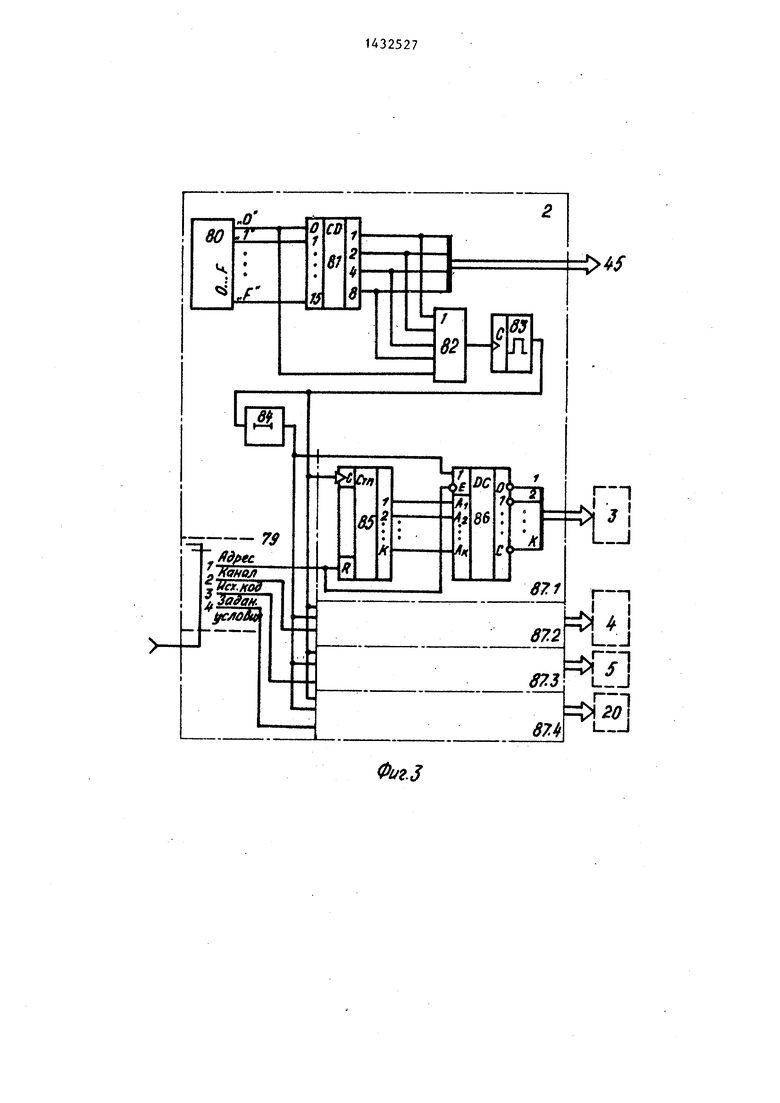

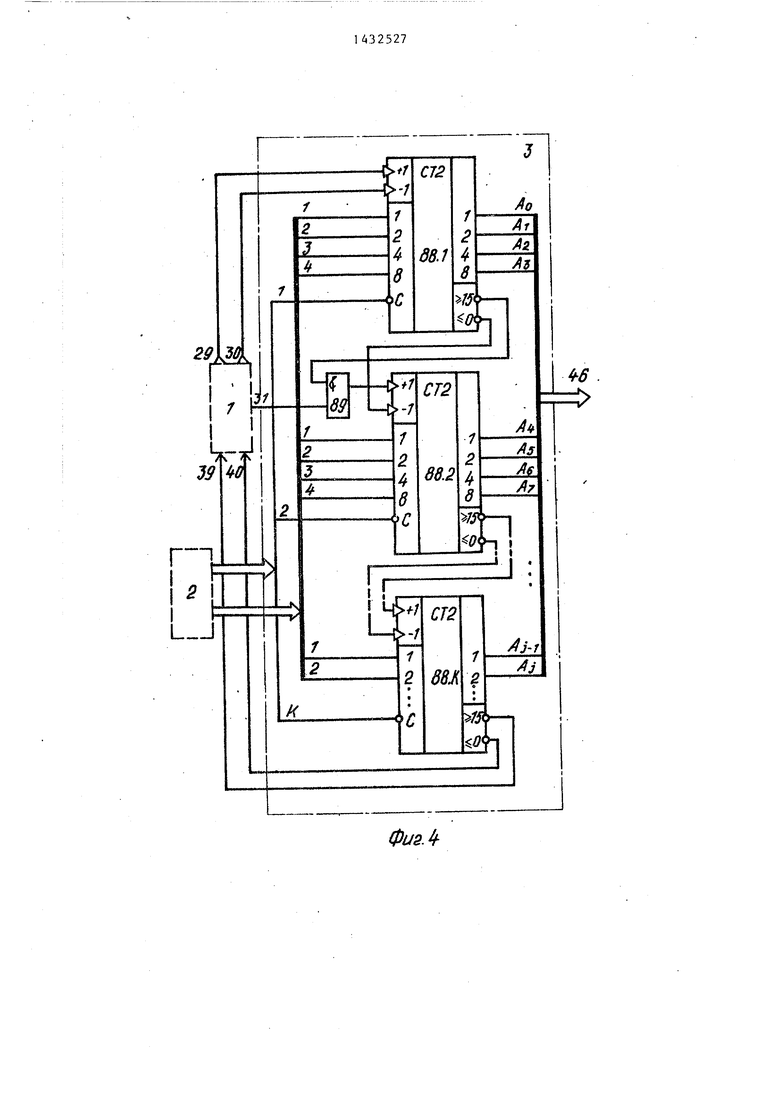

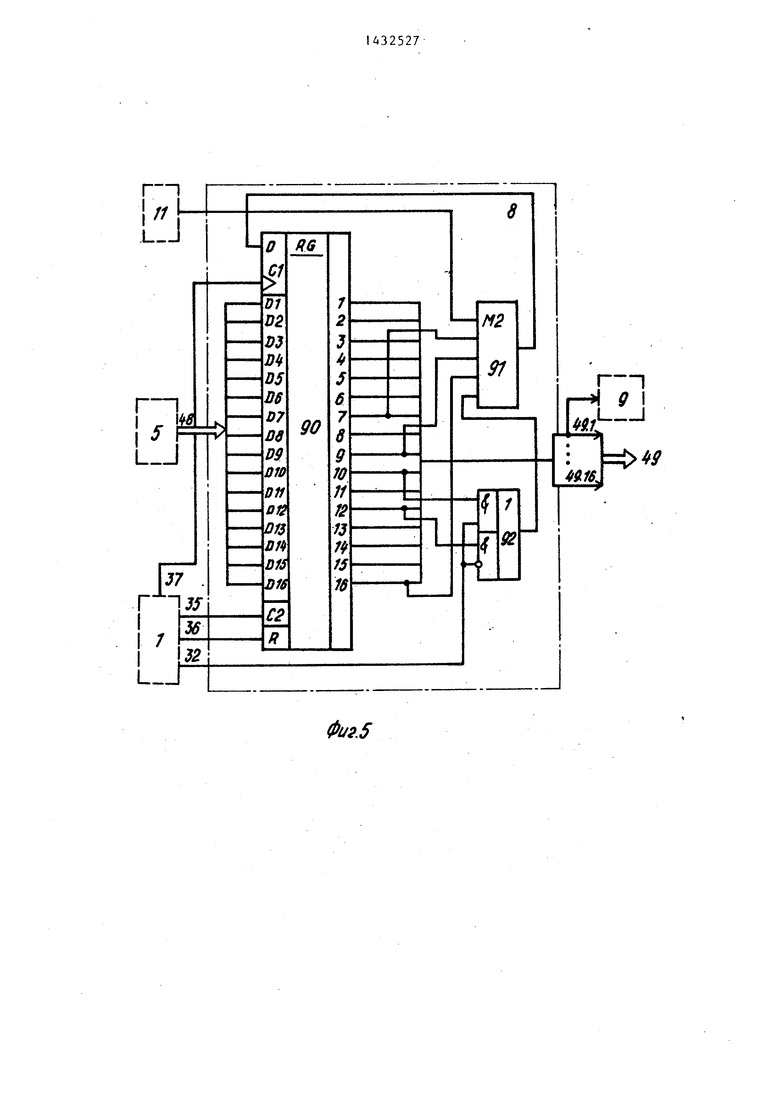

На фиг.3-5 обозначены переключатель 79 направлений ввода, клавиатура 80, шифратор 81, элемент ИЛИ 82, одновибратор 83, элемент 84 задержки, двоичный счетчик 85 и дешифратор 86, образующие группу 87,четырехразрядные двоичные реверсивные счетчики 88,1-88.К, элемент И 89, ре гистр 90 сдвига, сумматор 91 по модулю два и коммутатор (элемент И-ИЛИ) 92.

Блок 1 управления предназначен дл организации функционирования логического анализатора во всех режимах работы.

Блок 2 ввода предназначен для параллельного занесения информации с алфавитно-цифровой клавиатуры 80 в счетчик 3 адреса, счетчик 4 каналов, регистр 5 исходного кода, блок 20 памяти заданных условий.

Счетчик 3 адреса предназначен для адресации ОЗУ 12.1-12.П, а счетчик 4 канала - для адресации текущего значения текущего номера канала.

Регистр 5 исходного кода предназначен для хранения исходной инфор- мации, с которой формирователь 8 сигнатур формирует тестовую последовательность, а также для управления посредством элемента ИЛИ 7 вторым коммутатором 11 данных.

Дешифратор 6 предназначен для преобразования двоичного кода номера канала в позиционный код управления коммутатором 10.

Формирователь 8 сигнатур предна- значен для формирования сигнатур в режимах сбора данных и генерации псевдослучайных последовательностей при формировании тестов в режимах обучения и самообучения.

Первый коммутатор 9 данных предназначен для подключения разрядов магистрального коммутатора 17 посредством группы связей 50 или выхода первого разряда формирователя сигнатур к информационным входам ОЗУ 12.1-12.п.

Коммутатор 10 синхросигналов записи предназначен для подключения выхода 28 синхросигналов записи бло- ка 1 к соответствующим разрядам ОЗУ 12.1-12.п.

Второй коммутатор 11 данных предназначен для подключения к информа- ционному входу формирователя В сигнатур входа 25 или вькода мультиплексора 19.

ОЗУ 12.1-12.П является быстродействующим ОЗУ статического типа и предназначено для хранения и генерации тестовых воздействий, а также для сбора и хранения информации с исследуемых объектов.

Регистр 13 количества реакций предназначен для хранения начального значения количества реакций.

Счетчик 14 реакций является ревер сивным двоичным счетчиком и предназначен для адресации ячеек блока 20 памяти заданных условий, а также для в ыработки сигнала запуска-останова (О на входе 43).

Формирователь 15, представляющий собой последовательно соединенные элемент задержки и одновибратор, служит для выработки сигнала управ-. ленил счетчиком 14 и фильтрации входных помех.

Первый блок 16 индикации предназначен для визуализации логических состояний ячеек памяти ОЗУ 12.1-12.п Магистральный коммутатор 17 предназначен для коммутации входов-выходов 23 с входами первого коммутатора 9 данных и с выходами ОЗУ 12.1-12.п, а также для разделения и разрядов входов-выходов 23 на группу входов и выходов.

Переключатель 18 кода ввода-вывода служит для вьщачи управляющего кода на входы управления магистральным коммутатором 17 и коммутатором 10 синхросигналов записи.

Мультиплексор 19 предназначен для организации потоков информации с выходов ОЗУ 12.1-12.П в один поток, который посредством коммутатора 11 поступает .на информадионньш вход формирователя 8 сигнатур.

Блок 20 памяти заданных условий представляет собой ОЗУ статического типа и служит для хранения кодов ожидаемых реакций.

Блок 21 сравнения служит для сравнения кода условий запуска (реакций) на. входах 24 с кодом ожидаемых реакций на выходах блока 20 памяти и выработки сигнала равенства.

Второй блок 22 индикации предназначен для обеспечения индикации содержимого счетчиков 3, 4 и 1-4, регистра 5, формирователя 8 сигнатур и блока 20.памяти.

Логический анализатор работает в режимах сбора данных с формирователем одиночной (сдое) и результирующей (СДРС) сигнатур, логического контроля (ЛК), самообучения (СО); обучения по исходному коду (ОИК7.

Режимы работы устанавливаются переключателем 53 режимов блока 1 управления .

Режим Ввод предназначен для параллельного занесения информации в счетчики 3 и 4 адреса канала, регист 5 и блок 20 памяти. Этот режим обе-г спечивается блоком 2 ввода (фиг.З).

Направление ввода -задается переключателем 79 Адрес - Канал, Исходный код - Заданные условия Информация заносится потетрадно, позтому все приемники информации (счетчики 3 и 4, регистр 5, блок 20 памяти) состоят из тетрадных компонентов , имеющих синхровходы параллельной записи.

Значение вводимой информации задается буквенно-цифровой клавиатурой

80шестнадцатиричного кода. Шифратор

81переводит код клавиатуры в четырехразрядный двоичный код, который по связям 45 подводится ко всем тетрадам счетчиков 3 и 4, регистра 5 и блока 20 памяти.

Переключатель 79 в режиме Ввод деблокирует одну из групп 87.1-87.4, включающую счетчик 85 тетрад и дешифратор 86 сигналов разрешения па-, раллельно занесения данных.

В исходном состоянии все разряды связей 45.принимают значение О, позтому на выходе элемента ИЛИ 82 также О.

При нажатии одной из клавиш клавиатуры 80 на выходе элемента ШШ 82 появляется 1, запускающая одновиб- ратор 83. По фронту сигнала на выходе одновибратора 83 счетчик 85 из деблокируемой группы 87.1-87.4 переводится в. следующее состояние.

Одновременно с импульсом на выходе элемента 84 задержки на соответствующем выходе дешифратора 86, определяемом состоянием счетчика 85, появляется отрицательный 1мпульс, разрешающий занесение данных по связям 45 в соответствующую тетраду одного из приемников.

В режиме СДОС и СДРС сигнал на выходе элемента И 57 и выходе 32 блока 1 управления принимает значение О и поступает на.выходы управления коммутаторов 9-11, а тарсже формирователя 8 сигнатур. Этот сигнал деблокирует верхнюю и блокирует нижнюю группы, связанные по функции

При этом разряды связей 50 подключены к информационным входам ОЗУ 12.1-12.П, выход 28 синхросигналов подключается к входам синхросигналов записи разрядов ОЗУ 12.1т12.п, определяемых кодом переключателя 18, приведенным в табл.1. ,Таблица1

1 О

п-1

О

S

0

5

0

5

Кроме того, сигнал О на выходе 32 деблокирует второй коммутатор 11 данных и с помощью элемента И-ИЖ 92 подключает двенадцатый разряд регистра 90 к входу сумматора 91 по модулю два (фиг.5).

Таким образом, , формирователь 8 сигнатур в режимах СДОС и СДРС представляет собой регистр 90 сдвига с обратными связями седьмого, девятого, двенадцатого и шестнадцатого разрядов через сумматор 91 по модулю два, формирую1щй из длинных последовательностей сигналов на выходе коммутатора 11 шестнадцатиразрядный двоичный код (сигнатура).

Управляющим кодом переключателя 18 (табл.1) п каналов логического анализатора подразделяются на две группы; п - группа каналов вьшода данных (генерации тестовых воздействий) : Пр - группа каналов ввода данных (сбора реакций),причем п

Пт + Пр.

Такое разделение осуществляется, с помощью магистрального коммутатора 17, управляющегося кодом переключателя 18.

Сигнал 1 i-разряда переключателя 18 переводит тристабильный элемент i-разряда магистрального коммутатора 17 в третье высокоимпеданс- ное состояние, при этом i-разряд вывода 23 становится входом и подключается к i-разряду группы связей 50. Одновременно 1 i-разряда переключателя 18 разрешает подключение выхода 28 к входу синхросигналов записи i-разряда ОЗУ 12.

Таким образом,i-канап при 1 на выходе i-разряда переключателя 18 является каналом для ввода данных (npi).

Очевидно, что О на выходе i- разряда переключателя 18 подключает i-разряд вывода 23 к разряду группы связей 51, блокирует подачу синхро- Iсигнала записи к i-разряду ОЗУ 12, и i-кавал становится каналом вывода да данных (n-1-i) .

Из табл.1 видно, что в положении 1 переключателя 18 все п каналов являются каналами ввода-, а в положении п - каналами вывода данных.

Такое техническое решение позволяет гибко изменять конфигурацию логического анализатора в зависимости от соотношения входов-выходов конкретно диагностируемого объекта.

Для уменьшения количества положений переключателя 18 с целью упрощения схемы можно реализовать группово переключение направления каналов.

В режимах СДОС и СДРС существуют два варианта синхронизации логического анализатора с исследуемым объектом: внутренняя и внешняя- синхронизация.

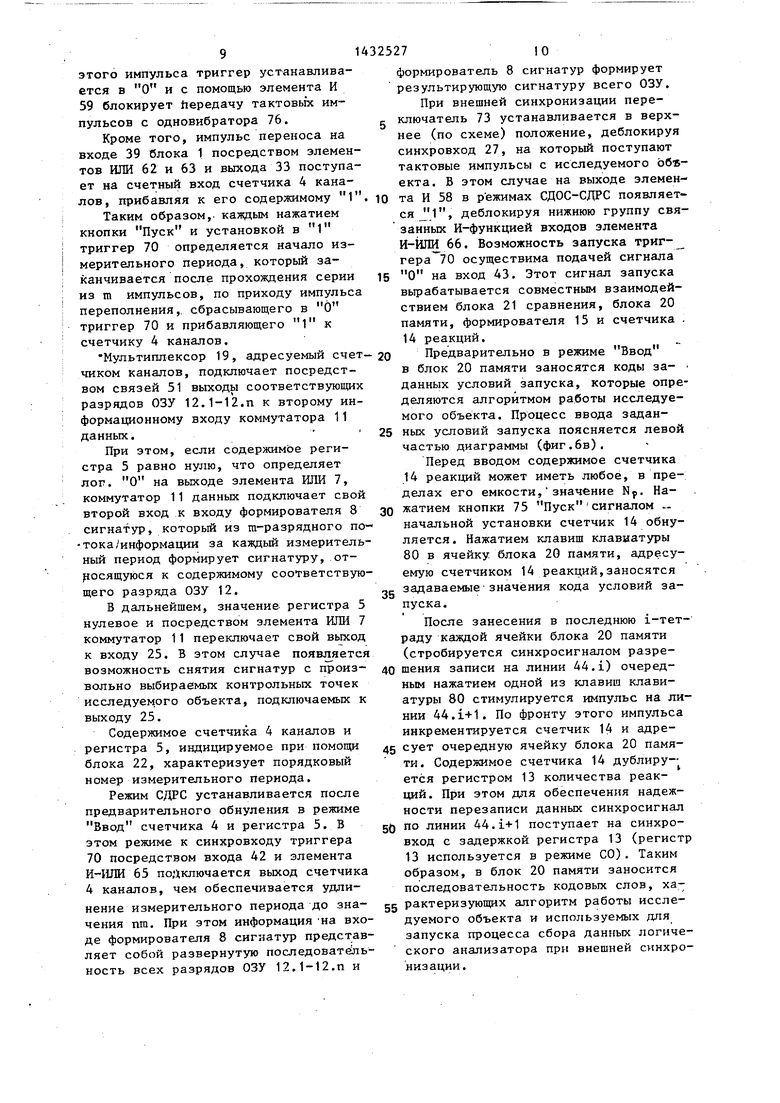

При внутренней синхронизации пе-- реключатель 72 (фиг.2) устанавливается в нижнее положение, чем обеспечивается при помощи элемента И-1ШИ 65 подключение выхода генератора 72 тактовых импульсов к входу одновибрато- ра 76. По фронту входных тактовых импульсов одновибратор 76 генерирует импульсы стабильной длительности, частота которых равна частоте входных импульсов (фиг.ба).

При нажатии кнопки 75 Пуск синхронные одновибраторы 77 и 78 генерируют по одному импульсу.

Импульс, генерируемый одновибра- тором 77, служит для начальной установки-триггера 70, формирователя 8, счетчика 14 и элементов памяти

0

5

0

5

0

5

0

5

0

5

исследуемого объекта посредстном .чм- хода 26.

Второй импульс, запаздывающий rui один период тактовых импульсов по отношению к первому, генерируемый одно- вибратором 78, посредством элемента H-IUBi 66 поступает на S-вход триггера 70 и устанавливает его в 1. Элемент И 59 деблокируется, и тактовые импульсы с выхода одновибратора 76 поступают на выход 28 синхросигн.-ишв записи и посредством инвертора 11 с задержкой it, - на синхровход формирователя 8 сигнатур посредством выхода 37.

В режимах СДОС и СДРС О на выходе элемента И 57 удерживает триггер 69 в состоянии О, блокирует элемент И 56 и посредством элемента И 54 деблокирует элемент И 55, бла- :годаря чему тактовые импульсы с задержкой ut посредством выхода 29 ,поступают на инкрементный счетный вход счетчика 3 адреса.

Запись информации осуществляется потенциалом 1 на выходе 28 (фиг.ба) и входах синхросигналов записи соответствующих разрядов ОЗУ 12.1-12.П.

После установки на выходе 28 значения О спустя промежуток времени t, фронт импульса на выходе 37 формирователя 8 сигнатур принимает очередной информационный бит, на выходе 29 к содержимому счетчика 3 приближается +1 и он адресует очередную ячейку ОЗУ 12.1-12.П, в которую спустя промеж-уток времени - &t, потенциалом 1 на выходе 28 разрешается запись нового информационного слова.

. Для временного согласования работы необходимо соблюдение условия

ut f,t ЛС, ,

где bt - длительность импульса одновибратора 76.

Емкость счетчика равна глубине га памяти ОЗУ 12.1-12.п.

В конце адресации последней ячейки ОЗУ счетчик 3 вырабатывает отри- цательный импульс переноса, который посредством входа 39 блока 1 поступает на первый вход элемента H-I-UIII 64. В режиме СДОС с помощью второго сверху (по схеме) входа разрешается прохождение импульса переноса на /синхвовход триггера 70. По фронту

этого импульса триггер устанавливается в О и с помощью элемента И 59 блокирует передачу тактовьгх импульсов с одновибратора 76.

Кроме того, импульс переноса на входе 39 блока 1 посредством элементов ИЛИ 62 и 63 и выхода 33 поступает на счетный вход счетчика 4 каналов, прибавляя к его содержимому 1

Таким образом,, каяиым нажатием кнопки Пуск и установкой в 1 триггер 70 определяется начало измерительного периода, который заканчивается после прохождения серии из m импульсов, по приходу импульса

переполнения,, сбрасывающего в О триггер 70 и прибавляющего 1 к счетчику А каналов,

Мультиплексор 19, адресуемый счет чиком каналов, подключает посредством связей 51 выходы соответствующих разрядов ОЗУ 12.1-12.п к второму информационному входу коммутатора 11 данных.. ,

При этом, если содержимое регистра 5 равно нулю, что определяет лог. О на выходе элемента ЕЛИ 7, коммутатор 11 данных подключает свой второй вход к входу формирователя 8 сигнатур, которьй из т-разрядного по тока, информации за каждый измеритель ньш период формирует сигнатуру, от- росящуюся к содержимому соответствующего разряда ОЗУ 12.

В дальнейшем, значение регистра 5 нулевое и посредством элемента ИЛИ 7 коммутатор 11 переключает свой выход к входу 23. В этом случае появляется возможность снятия сигнатур с произвольно выбираемых контрольных точек исследуем.ого объекта, подключаемых к выходу 25.

Содержимое счетчика 4 каналов и регистра 5, индицируемое при помощи блока 22, характеризует порядковый номер измерительного периода.

Режим СДРС устанавливается после предварительного обнуления в режиме Ввод счетчика 4 и регистра 5. В этом режиме к синхровходу триггера 70 посредством входа 42 и элемента И-ИЛИ 65 пoг,i ключaeтcя вькод счетчика 4 каналов, чем обеспечивается удлинение измерительного периода до значения nm. При этом информация на входе формирователя 8 сигнатур представляет собой развернутую последовательность всех разрядов ОЗУ 12.1-12.П и

25

20

43252710

формирователь 8 сигнатур формирует результирующую сигнатуру всего ОЗУ.

При внешней синхронизации пере- g ключатель 73 устанавливается в верхнее (по схеме) положение, деблокируя синхровход 27, на которьй поступают тактовые импульсы с исследуемого обв- екта. В этом случае на выходе элемен- 10 та И 58 в режимах СДОС-СДРС появляет- , деблокируя нижнюю группу связанных И-функцией входов элемента И-ИПИ 66. Возможность запуска триг- гера 70 осуществима подачей сигнала 15 О на вход 43. Этот сигнал запуска вырабатывается совместным взаимодействием блока 21 сравнения, блока 20 памяти, формирователя 15 и счетчика . 14 реакций.

Предварительно в режиме Ввод в блок 20 памяти заносятся коды за- данных условий запуска, которые определяются алгоритмом работы исследуемого объекта. Процесс ввода заданных условий запуска поясняется левой частью диаграммы (фиг.бв).

Перед вводом содержимое счетчика 14 реакций может иметь любое, в пре-;

30

ЗВ

делах его емкости, значение Np. Нажатием кнопки 75 Пуск сигналом .- начальной установки счетчик 14 обнуляется . Нажатием клавиш клавиатуры 80 в ячейку блока 20 памяти, адре.су- емую счетчиком 14 реакций,заносятся задаваемые значения кода условий запуска.

После занесения в последнюю i-тет раду каждой ячейки блока 20 памяти (стробируется синхросигналом разре40 шения записи на линии 44.1) очередным нажатием одной из клавиш клавиатуры 80 стимулируется импульс на линии 44.1+1. По фронту этого импульса инкрементируется счетчик 14 и адре45 сует очередную ячейку блока 20 памяти. Содержимое счетчика 14 дублируется регистром 13 количества реакций. При этом для обеспечения надежности перезаписи данных синхросигнал

50 по линии 44.1+1 поступает на синхровход с задержкой регистра 13 (регист 13 используется в режиме СО), Таким образом, в блок 20 памяти заносится последовательность кодовых слов, у.а55 рактеризующих алгоритм работы исследуемого объекта и используемых для запуска процесса сбора данных логического анализатора при внешней синхронизации.

11

Условия запуска, представляю 1;ие кодовые слова, параллельно поступаю на входы 24 и сравниваются блоком 2 сравнения с заданными значениями на выходах блока 20 памяти. При совпадении входного кодового слова с заданным блок 21 сравнения вьфабатыва ет сигнал сравнения, который посредством формирователя 15 поступает на декрементный счетный вход счетчика 14, вычитая из его содерзкимого ,1. Адресуется очередная ячейка блока 20 памяти и задается новый код условий запуска.

По приходу последнего кодового слова на выходы 24 счетчик 14,когда его содержимое равно О, вьфабатыв ет отрицательный импульс переноса, которьй посредством входа 43 и элемента IfflH 66 поступает на S-вход триггера 70 и устанавливает его в 1, запуская процесс сбора данных.

Таким образом, если в блок 20 памяти занесено одно кодовое слово заданных условий запуска при нулевом значении счетчика 14, то запуск процесса сбора данных осуществляется при первом совпадении условий запуска на входах 24 с заданными.

При занесении в блок 20 памяти нескольких кодовых слов заданных условий запуска процесс сбора данных осуществляется по последовательностям кодовых слов, поступающих на входы 24.

В режимах ОИК и СО на выходе эле

мента И 57 появляется сигнал 1, который деблокирует триггер 69, элементы И 54 и 56, элемент Й-ИЛИ 68 и посредством выхода 32 поступает на коммутаторы 9-11, а также на управляющий вход формирователя 8 сигнатур. При этом коммутатор 9 подключает информационные входы всех п разрядов ОЗУ 12.1-12,п к выходу первого разряда формирователя 8 сигнатур, коммутатор 10 переключается на управление от дешифратора 6, коммутатор 11 блокируется и на его выходе устанавливается О, в формирователе 8 сигнатур (фиг.5) при помощи коммутатора (элемента И-ИЛИ) 92 обратная связь с двенадцатого разряда выхода регистра 90 переключается на десятый,

В обратных связях формирователя 8 сигнатур участвуют выходы седьмого, девятого, десятого и шестнадцатого разрядов. При таком распределении

5

2527

12

обратных связей и сигнале О на информационном входе формирователь 8 становится генератором псевдослучайной последовательности с максимальным периодом N,g, причем

,кc 2 - 1 65535,

где г - разрядность регистра 90.

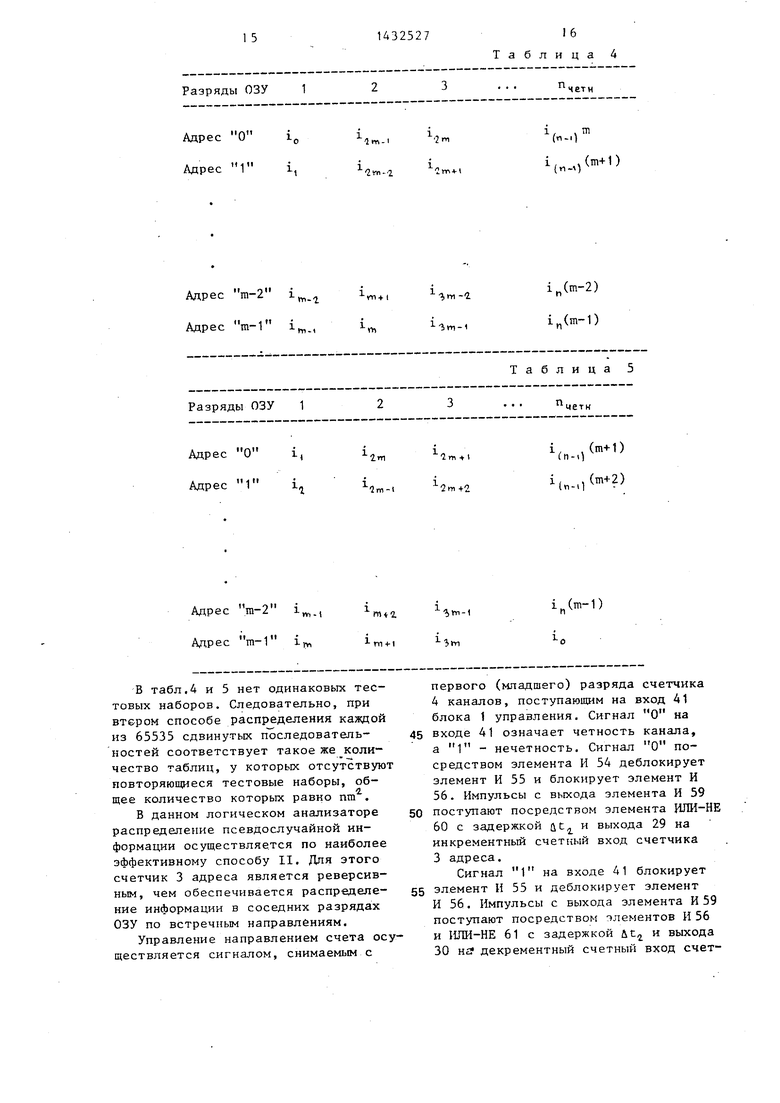

Для того, чтобы формирователь 3 формировал последовательность, в него необходимо предварительно занести ненулевое значение исходного кода, - которое определяет начальную фазу генерируемой периодической последовательности. Дпя этого в режиме Ввод в регистр 90 заносится исходный код, который при нажатии кнопки 75 Пуск в режимах ИОК и СО с помощью импульса на выходе 35 пер еписывается в формирователь 8. Каждое значение исходного кода осуществляет фазовый сдвиг последовательности двоичных сигналов, снимаемых с любого из выходов регистра 90. В логическом анализаторе (фиг.1) последовательность сигналов снимается с выхода первого (младшего) разряда регистра 90 и поступает параллельно на информационные входы всех разрядов ОЗУ 12. Дешифратор 6, управляемый счетчиком 4 каналов, обеспечивает поочередное подключение синхросигнала записи, поступающего с выхода 28, к разрядам ОЗУ 12, чем обеспечивается последова тельное занесение и распределение длинной последовательности в ячейках ОЗУ. Таким образом, в ОЗУ 12 фор мируются п-разр5вдные тестовые наборы сигналов глубиной га. Один период псевдослучайной последовательности максимальной длины распределяется

N в - З-ЬС- разрядах ОЗУ 12. Исходя из

п

условия N, nim (п - количество разрядов ОЗУ), рассмотрим два способа формирования тестовых наборов из двух псевдослучайных поспе довательностей, сдвинутых между собой на один шаг

i(m-l)..

i(,i(m-1)

.

(1)

(2)

где i О или .

Способ I. Информация в каждый разряд ОЗУ заносится в одном направ13143252714

ЛЕНИН с фиксированного значения ад- с адресом т-1. Остальные наборы этих реса (например, с нулевого).таблиц, сдвинутые параллельно на

Последовательности (1) и (2) рас- один шаг, повторяются, пределяется соответственно табл.2 и ,.

3, где стрелками указаны направления занесения информации в разряды ОЗУ. Сравнивая содержимое табл.2, видим,

,что они отличаются только одним тестовым набором, размещенным в ячейке ю только одним набором.

Т а б л и ц а 2

Следовательно, кажцая и сдвинутых последовательнос теризуется своей таблицей наборов, отличающейся от о

Разряды ОЗУ

О 1

т

2т № + 1 . 1m+i

Адрес m-2 i, Адрес m-l i

Ст-Ч

-am

Способ II. Информация в смежные разряды памяти заносится во встречных направлениях, например, в четные разряды ОЗУ информация заносит - ся, начиная с нулевого адреса, а в

только одним набором.

Следовательно, кажцая из 65 535 сдвинутых последовательностей характеризуется своей таблицей тестовых наборов, отличающейся от остальных

П

Nn.,) i(«.,)

1,(ш-1)

Im

gg нечетные - в обратном направлении, начиная с адреса m-l.

При данном способе последователв- ности (1) и (2) распределяются в соответствии с табл,4 и 5.

Адрес m-2 i, i, Цт-i

Адрес m-2 i., i i., Адрес m-1 „, i-гм

В табл.4 и 5 нет одинаковьк тестовых наборов. Следовательно, при втером способе распределения каждой из 65535 сдвинутых последовательностей соответствует такое же количество таблиц, у которых отсутствуют повторяющиеся тестовые наборы, общее количество которых равно пт .

В данном логическом анализаторе распределение псевдослучайной информации осуществляется по наиболее эффективному способу И. Для этого счетчик 3 адреса является реверсивным, чем обеспечивается распределение информации в соседних разрядах ОЗУ по встречным направлениям.

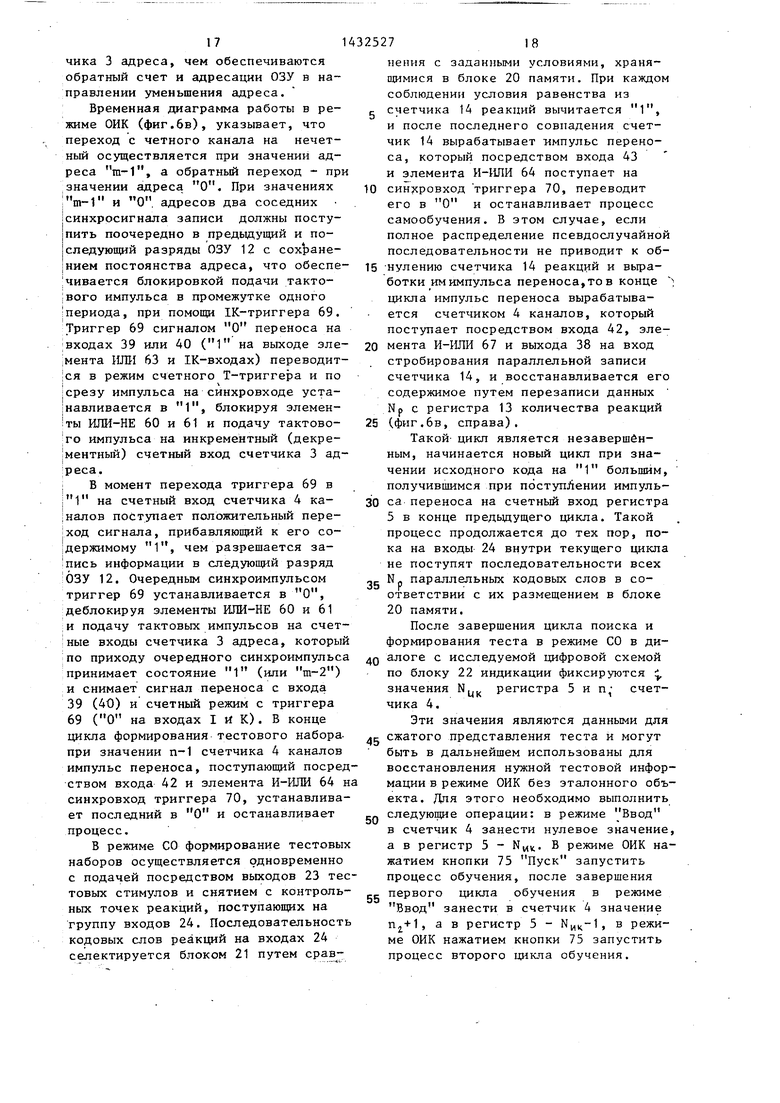

Управление направлением счета осуществляется сигналом, снимаемым с

i.(m-2)

i,(m-1)

первого (младшего) разряда счетчика 4 каналов, поступающим на вход 41 блока 1 управления. Сигнал О на

входе 41 означает четность канала, а 1 - нечетность. Сигнал О посредством элемента И 54 деблокирует элемент И 55 и блокирует элемент И 56. Импульсы с выхода элемента И 59

поступают посредством элемента ИЛИ-НЕ 60 с задержкой ut и выхода 29 на инкрементный счетный вход счетчика 3 адреса.

Сигнал 1 на входе 41 блокирует

элемент И 55 и деблокирует элемент И 56. Импульсы с выхода элемента И 59 поступают посредством элементов И 56 и 1ШИ-НЕ 61 с задержкой и выхода 30 н декрементный счетный вход счетчика 3 адреса, чем обеспечиваются обратный счет и адресации ОЗУ в направлении уменьшения адреса.

Временная диаграмма работы в режиме ОИК (фиг.бв), указывает, что переход с четного канала на нечетный осуществляется при значении адреса т-1, а обратный переход - при значении адреса О, При значениях и О, адресов два соседних iсинхросигнала записи должны посту- |пить поочередно в предыдущий и по- Iследующий разряды ОЗУ 12 с |нием постоянства адреса, что обеспе- чивается блокировкой подачи такто- ;вого импульса в промежутке одного :периода, при помощи 1К-триггера 69. Триггер 69 сигналом О переноса на ;входах 39 или 40 (1 на выходе эле- :мента ИЛИ 63 и 1К-входах) переводит- ;ся в режим счетного Т-триггера и по Iсрезу импульса на синхровходе уста- |Навливается в 1, блокируя элемен- ты ИЛИ-НЕ 60 и 61 и подачу тактово- ;го импульса на инкрементный (декре- :ментный) счетный вход счетчика 3 адреса.

: В момент перехода триггера 69 в на счетный вход счетчика 4 ка- iналов поступает положительный пере- ;ход сигнала, прибавляюпщй к его со- 1держимому 1, чем разрешается за- :пись информации в следуюищй разряд :63У 12. Очередным синхроимпульсом триггер 69 устанавливается в О, деблокируя элементы ИЛИ-НЕ 60 и 61 :и подачу тактовых импульсов на счет- Iные входы счетчика 3 адреса, который по приходу очередного синхроимпульса принимает состояние 1 (или т-2) и снимает сигнал переноса с входа 39 (40) и счетный режим с триггера 69 (О на входах I И К). В конце цикла формирования тестового набора при значении п-1 счетчика 4 каналов импульс переноса, поступающий посредством входа 42 и элемента И-ИЛИ 64 н синхровход триггера 70, устанавливает последний в О и останавливает процесс,

В режиме СО формирование тестовых наборов осуществляется одновременно с подачей посредством выходов 23 тестовых стимулов и снятием с контрольных точек реакций, поступающих на группу входов 24. Последовательность кодовых слов реакций на входах 24 селектируется блоком 21 путем срав

5

0

5

0

0

нения с заданными условиями, хранящимися в блоке 20 памяти. При каждом соблюдении условия равенства из счетчика 14 реакций вычитается 1, и после последнего совпадения счетчик 14 вырабатывает импульс переноса, который посредством входа 43 и элемента И-НЛИ 64 поступает на синхровход триггера 70, переводит его в О и останавливает процесс самообучения. В этом случае, если полное распределение псевдослучайной последовательности не приводит к об- нулению счетчика 14 реакций и вьфа- ботки им импульса переноса, то в конце ; цикла импульс переноса вырабатывается счетчиком 4 каналов, который поступает посредством входа 42, элемента И-ИЛИ 67 и выхода 38 на вход стробирования параллельной записи счетчика 14, и восстанавливается его содержимое путем перезаписи данных NP с регистра 13 количества реакций (фиг.бв, справа).

Такой- цикл является незавершённым, начинается новый цикл при значении исходного кода на 1 большим, получившимся при поступлении импульса переноса на счетный вход регистра 5 в конце предыдущего цикла. Такой процесс продолжается до тех пор, пока на входы 24 внутри текущего цикла не поступят последовательности всех

сос их размещением в 20 памяти.

После завершения цикла поиска и формирования теста в режиме СО в диалоге с исследуемой цифровой схемой по блоку 22 индикации фиксируются :J,

g Np параллельных кодовых слов в

ответствии с их размещением в блоке

0

5

N

UK

регистра 5 и п; счетзначениячика 4.

Эти значения являются данными для g сжатого представления теста и могут быть в дальнейшем использованы для восстановления нужной тестовой информации в режиме ОИК без эталонного объекта. Для этого необходимо выполнить следующие операции: в режиме Ввод в счетчик 4 занести нулевое значение, а в регистр 5 - В режиме ОИК нажатием кнопки 75 Пуск запустить процесс обучения, после завершения первого цикла обучения в режиме Ввод занести в счетчик 4 значение , а в регистр 5 - , в режиме ОИК нажатием кнопки 75 запустить процесс второго цикла обучения.

Полученная тестовая информация может быть использована для диагностирования неисправного цифрового объекта в рейшмах СЛРС и СДОС по методу сигнатурного анализа.

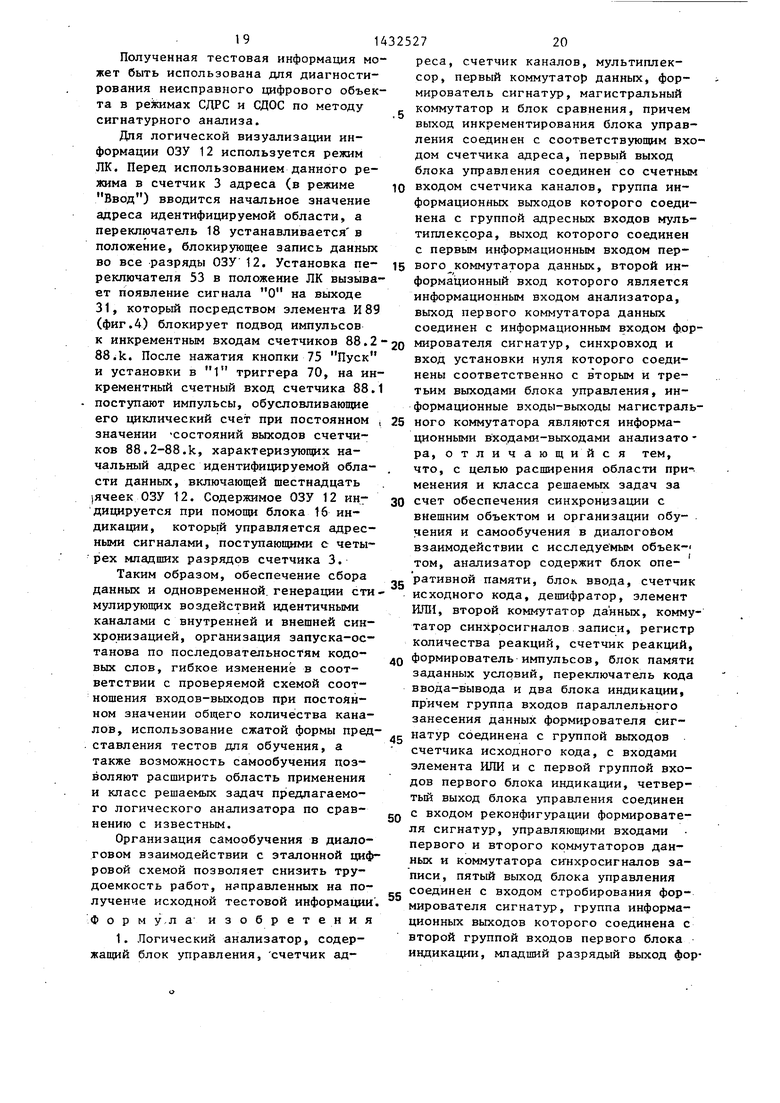

Для логической визуализации информации ОЗУ 12 используется режим ЛК. Перед использованием данного режима в счетчик 3 адреса (в режиме Ввод) вводится начальное значение адреса идентифицируемой области, а переключатель 18 устанавливается в положение, блокирующее запись данных во все разряды ОЗУ 12. Установка переключателя 53 в положение ЛК вызывает появление сигнала О на выходе 31, которьй посредством элемента И 89 (фиг.4) блокирует подвод импульсов к инкрементным входам счетчиков 88.2- 88.k. После нажатия кнопки 75 Пуск и установки в 1 триггера 70, на ин- крементный счетный вход счетчика 88.1 поступают импульсы, обусловливающие его циклический счет при постоянном , значении -состояний выходов счетчиков 88.2-88.k, характеризующих начальный адрес идентифицируемой области данных, включающей шестнадцать ячеек ОЗУ 12. Содержимое ОЗУ 12 индицируется при помощи блока t6 индикации, которьтй управляется адресными сигналами, поступающими с четырех младших разрядов счетчика 3.

Таким образом, обеспечение сбора данных и одновременной, генерации стимулирующих воздействий идентичными каналами с внутренней и внешней синхронизацией, организация запуска-останова по последовательностям кодовых слов, гибкое изменение в соответствии с проверяемой схемой соотношения входов-выходов при постоянном значении общего количества каналов, использование сжатой формы пред- ставления тестов для обучения, а также возможность самообучения позволяют расширить область применения и класс решаемых задач предлагаемого логического анализатора по сравнению с известным.

Организация самообучения в диалоговом взаимодействии с эталонной цифровой схемой позволяет снизить трудоемкость работ, направленных на получение исходной тестовой информации. Форму,ла изобретения

0 входом счетчика каналов, группа информационных выходов которого соединена с группой адресных входов мультиплексора, выход которого соединен с первым информационным входом пер5 вого коммутатора данных, второй информационный вход которого является информационным входом анализатора, выход первого коммутатора данных соединен с информационным входом фор0 мирователя сигнатур, синхровход и вход установки нуля которого соединены соответственно с вторым и третьим выходами блока управления, информационные входы-выходы магистраль5 ного коммутатора являются информационными входами-выходами анализатора, отличающийся тем, что, с целью расширения области при-, менения и класса решаемых задач за

0 счет обеспечения синхронизации с внешним объектом и организации обучения и самообучения в диапогобом взаимодействии с исследуе мым объек- том, анализатор содержит блок опес ративной памяти, блок ввода, счетчик исходного кода, дешифратор, элемент ШП1, второй коммутатор данных, коммутатор синхросигналов записи, регистр количества реакций, счетчик реакций,

Q формирователь импульсов, блок памяти заданных условий, переключатель кода ввода-вывода и два блока индикации, причем группа входов параллельного занесения данных формирователя сигg натур соединена с группой выходов счетчика исходного кода, с входами элемента ИЛИ и с первой группой входов первого блока индикации, четвер- тьй выход блока управления соединен

Q с входом реконфигурации формирователя сигнатур, управляющими входами первого и второго коммутаторов данных и коммутатора синхросигналов записи, пятый выход блока управления

55

соединен с входом стробирования формирователя сигнатур, группа информационных выходов которого соединена с второй группой входов первого блока индикации, младший разрядый выход фор

21

мирователя сигнатур соединен с дополнительным информационным входом второго коммутатора данных, группа информационных входов которого соединена с группой выходов магистрального коммутатора, а группа выходов второг коммутатора - с группой информационных входов блока оперативной памяти группа адресных входов которого соединена с группой-информационных ходов счетчика адреса, первой группой входов второго блока индикации и третьей группой входов первого блока индикации, группа выходов блок оперативной памяти соединена с второй группой входов второго блока индикации и группами информационных входов магистрального коммутатора и мультиплексора, группа синхровходов блока оперативной памяти соединена с группой выходов коммутатора синхросигналов записи, управляющих входов которого соединена с группой выходов дешифратора, группа входов которого соединена с четвертой группой входов первого блока и одикадии и с группой информационных выходов счетчика каналов, младший разрядный выход которого соединен с входом задания направления счета блока управления , синхровход записи данных коммутатора синхросигналов записи соединен с шестым выходом блока управле- йия, группа выходов переключателя кода ввода-вывода соединена с группой управляющих входов магистрального коммутатора и группой входов блокировки синхронизации коммутатора синхросигналов записи, первая, вто ,рая и третья группы выходов блока ввода соединены с группами разрешающих входов соответственно счетчика адреса, счетчика канадюв и счетчика исходного кода,вход декрементирова- ния счетчика адреса соединен с седьмым выходбм блока управления,, четвертая группа выходов блока ввода соединена с группами входов параллельного занесения информации счетчика адреса, счетчика каналов, счетчика исходного кода и блока памяти заданных условий, пятая группа выходов блока ввода соединена с группой входов записи блока памяти заданных условий, разрешаюищй вход блока ввода соединен с восьмым выходом блока управления, выход переполнения счетчика каналов соединен со счетным

0

5

2527

5

0

5

0

5

0

5

22

входом счетчика исходного кода и с входом стробирования блока управления, вход блокировки переноса счетчика адреса соединен с одиннадцатым выходом блокировки переноса блока управления, выходы положительного и отрицательного переносов счетчика адреса соединены с соответствующими входами блока управления, третий выход блока управления соединен с выходом начальной установки анализатора и с входом установки нуля счетчика реакций, выход переноса которого соединен с управляющим входом выполнения условий запуска блока управления, девятый выход которого соединен с входом стробирования параллельной записи счетчика реакций, группа информационных входов которого соединена с группой выходов регистра количества реакций, группа информационньк выходов счетчика реакций соединена с группами информационных входов регистра количества реакций и блока памяти заданных,условий, а также с пятой группой входов первого блока индикации, старший разрядный выход пятой группы выходов блока ввода соединен с входом стробирования записи регистра количества реакций и с входом инкре- ментирования счетчика реакций, группа выходов блока памяти заданных условий соединена с щестой группой входов первого блока индикации и с первой группой входов блока сравнения, выход которого соединен с входом формирователя импульсов, выход которого подключен к входу декре- ментирования счетчика реакций, вторая группа входов блока сравнения образует группу входов условий запуска анализатора. выход элемента ИЛИ

соединен с управляющим входом первого коммутатора данных, синхровход блока управления является синхровхо- дом анализатора.

23

нуля, первый контакт переключателя режимов соединен с первым входом первого элемента И, первым входом третьего элемента И, первым входом сброса JK-триггера и образует выход блока, второй контакт переключателя режимов соединен с первым входом сброса D-триггера, вторым и третьим входами четвертого элемента И-ИЛИ и образует восьмой вьпсод блока, третий контакт переключателя режимов соединен с первым входом четвертого элемента И и вторым входом первого элемента И-ИЛИ, четвертый контакт переключателя режимов соединен с вторым входом четвертого элемента И и с третьим входом первого элемента И-ИЛИ, пятый и шестой контакты переключате- Jia режимов соединены соответственно с шестыми седьмым входами первого элемента И-ШШ, первый вход которого соединен с вторым входом второго элемента ИЛИ и образует вход положительного переноса блока, четвертый и пятый входы первого элемента И-ИЛИ объединены, подключены к третьему входу сброса JK-триггера, к первым входам четвертого и пятого элементов И-ИЛИ и образуют вход стробирования блока, восьмой вход первого элемента И-ИЛИ соединен с четвертым входом третьего элемента И-ИЛИ и образует вход условий запуска блока, выход первого элемента И-ИЛИ соединен с синхровходом D-триггера, второй вход первого элемента И,является управляющим входом направления счета блока, третий вход первого элемента И соединен с выходом четвертого элемента И, первым входом пятого элемента И,вторым входом третьего элемента И, вторым входом сброса JK-триггера, вторым и третьим входами пятого элемента И-ИЛИ и образует четвертый выход блока, выход первого элемента И соединен с первым входом второго элемента И и третьим входом третьего элемента И, второй вход второго элемента И соединен с четвертым входом третьего элемента И , синхровходом JK-триггера, выходом шестого элемента И, входом элемента НЕ и образует шестой выход блока, выход второго элемента И соединен с первым входом первого элемента ИЛИ-НЕ, второй вход которого соединен с выходом JK-триггера и с первыми входами первого элемента ИЛИ и второго элемента

43252724

ИЛИ-НЕ, выход первого элемента ИЛИ-НЕ является десятым выходом блока, выход третьего элемента И соединен с с вторым входом второго элемента ИЛИ-НЕ, выход которого является седьмым выходом блока, первый вход второго элемента ИЛИ является входом отрицательного переноса блока, выход

10 второго элемента ИЛИ соединен с J- и К-входами JK-триггера и с вторым входом первого элемента ИЛИ, выход которого является первым выходом блока, второй вход пятого элемента И

15 соединен с первым неподвижньм контактом первого переключателя и вторым входом второго элемента ИЛИ, выход пятого элемента И соединен с вторым и третьим входами третьего

20 элемента И-ИЛИ, первый вход которого соединен с выходом третьего од- новибратора и с четвертыми входами четвертого и пятого элементов И-ИЛИ, выход третьего элемента И-ИЛИ соеди25 нен с единичным входом D-триггера, информационный вход которого соединен с пшной логического нуля, а вто- ,рой вход сброса подключен к выходу второго одновибратора, входу разре30 шения третьего одновибратора и образует третий выход блока, выход D- триггера соединен с первым входом шестого элемента И, второй вход которого соединен с пятым входом третье-с го элемента И-ИЛИ, и выходом перво40

45

50

55

го одновибратора и с синхровходами второго и третьего одновибраторов, выход четвертого элемента И-ИШ1 является девятым выходом блока, выход пятого элемента И-ИЛИ является пятым выходом блока, выход элемента НЕ является вторым выходом блока, выход генератора тактовых импульсов подключен к первому входу второго элемента И-ИЛИ, третий вход которого соединен с вторым неподвижным контактом первого переключателя, подвижный контакт которого соединен с шиной логического нуля, четвертый вход второго элемента И-ГЛИ является синхровходом блока, прямой и инверсный выходы второго элемента И-ИЛИ под- ,ключены соответственно к первому и второму неподвижным контактам второго переключателя, подвижный контакт которого соединен с синхровхо - дом первого одновибратора, неподвижный контакт кнопки Пуск со- единен с входом разрешения вто25143252726

рого одновибратора, подвижный кон- тине логического нуля. такт кнопки Пуск подключен к

, Jl

I 1

«/

Фиг. 2.

0Lf2.3

ФизЛ

0l/2.S

1

Q 1

II

:t

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля и диагностики цифровых блоков | 1982 |

|

SU1067506A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-10-23—Публикация

1986-05-13—Подача