л ....ППЛП..ПП.ПП .....П..П пп „ппп.гшил

| название | год | авторы | номер документа |

|---|---|---|---|

| Обнаружитель битовой ошибки в последовательном цифровом тестовом потоке | 1985 |

|

SU1322355A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ РАДИОТЕЛЕМЕТРИЧЕСКИХ СИГНАЛОВ | 1994 |

|

RU2126139C1 |

| УСТРОЙСТВО ДЛЯ АВТОМАТИЧЕСКОГО КОНТРОЛЯ МЕТАНА И ДРУГИХ ГОРЮЧИХ ГАЗОВ | 1991 |

|

RU2013565C1 |

| Устройство для сжатия и передачи телеметрической информации | 1987 |

|

SU1640729A1 |

| СПОСОБ ПЕРЕДАЧИ ИНФОРМАЦИИ | 2000 |

|

RU2197061C2 |

| Устройство для измерения динамической погрешности аналого-цифровых преобразователей | 1987 |

|

SU1529453A1 |

| Устройство для передачи и приема сигналов | 1981 |

|

SU1068051A3 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ДАННЫХ | 2004 |

|

RU2271612C1 |

| УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ДАННЫХ | 2004 |

|

RU2260251C1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ДАННЫХ | 2004 |

|

RU2272360C1 |

Изобретение относится к цифровым системам передачи-приема информации и может быть использовано при измерении величины битовой ошибки п цифровой системе связи и в цифровой системе записи воспроизведения телеметрической информации. Цель изобретения состоит в повышении достоверности приема информации путем управления глубиной регенерации входного последовательного цифрового потока. В состав устройства входят формирователь импульсов, аналого-цифровой преобразователь, два компаратора, делитель частоты, синхронизатор, два одновиб- ратора, два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, три инвертора, триггер, элемент И, генератор псевдослучайной последовательности. РаСота устройства основана на сравнении бит за битом вторым элементом ИСКЛЮЧАЮЩЕЕ ИЛИ априорно известного двоичного числа, записанного в регистры генератора псевдослучайной последовательности, с копией этого сигнала, восстановленной с регулируемым уровнем регенерации и сфазированной с точностью до бита. 2 ил. (Л С

VI СЛ 00

о

СЛ

VJ

ю

Изобретение относится к цифровым системам передачи - приема информации и может быть использовано при измерении величины битовой ошибки в цифровой системе связи и в цифровой системе записи - воспроизведения телеметрической информации, касается усовершенствования известного устройства по авт. св. ГФ 1322355.

Известно устройство, содержащее синхронизатор телеметрического формата, первый и второй одновибраторы, генератор псевдослучайной последовательности, первый и второй элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, первый, второй и третий инверторы, элемент И.

Недостатком данного устройства являет- ся его низкая надежность, которая зависит от точности фазирования регенерированного испытательного сигнала с копией этого сигнала. Точность фазирования, в свою очередь, зависит от величины битовой ошибки (в нашем случае до двух ошибочных битов в последовательности), превышение которой не допускается, то есть приводит к необходимости назначать глубину регенерации (изменения характеристик) входного сигнала, в противном случае устройство неработоспособно. Все это ограничивает область достоверного выделения битозой ошибки. Однако использование корректирующего кода при передаче данных позволит без существенных изменений характеристик сигнала повысить надежность устройства при работе в широком диапазоне изменения величины битовых ошибок.

Цель изобретения - повышение достоверности приема информации путем управления глубиной регенерации входного цифрового потока.

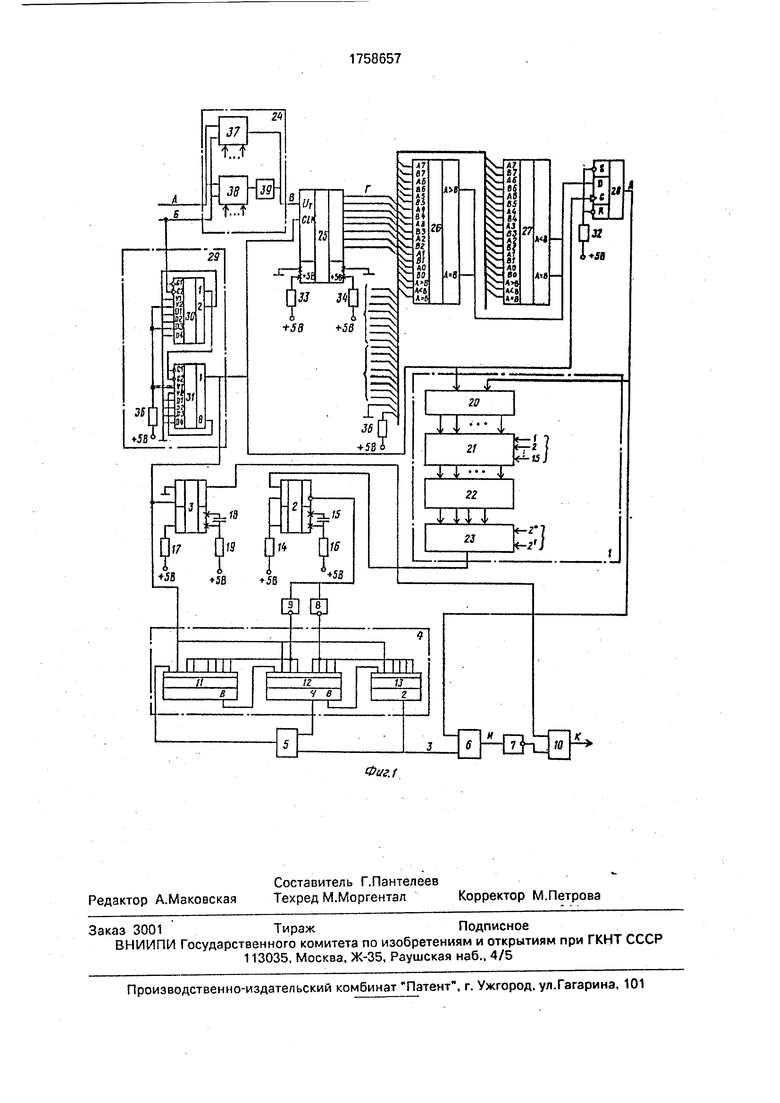

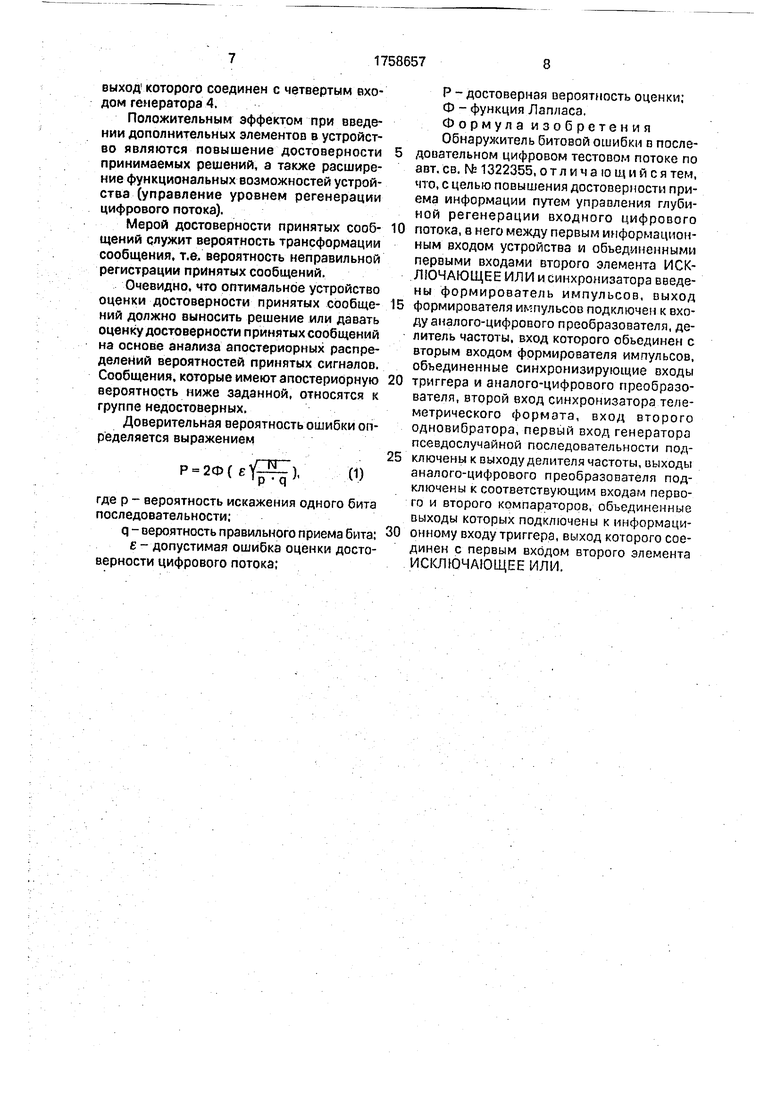

На фиг. 1 приведена функциональная схема устройства; на фиг. 2 - временная диаграмма его работы.

Устройство (фиг. 1) содержит синхронизатор 1 телеметрического формата, первый 2 и второй 3 одновибраторы, генератор 4 псевдослучайной последовательности, первый 5 и второй б элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, первый 7, второй 8, третий 9 инверторы, элемент И 10, формирователь 24 импульсов, аналого-цифровой преобразователь 25, первый 26 и второй 27 компараторы, триггер 28, делитель 29 частоты, содержащий четвертый 30 и пятый 31 регистры. Генератор 4 псевдослучайной последовательности содержит первый, второй и третий регистры 11-13.

Для работы первого одновибратора 2 к нему подключены первый резистор 14, первая емкость 15 и второй резистор 16. К второму одновибратору 3 подключены третий

резистор 17, вторая емкость 18 и четвертый резистор 19. К триггеру 28 подключен пятый резистор 32. К аналого-цифровому преобразователю 25 подключены шестой 33 и седь5 мой 34 резисторы, к делителю 29 частоты - восьмой резистор 35, к первому 26 и второму 27 компараторам - девятый резистор 36. Синхронизатор 1 телеметрического формата состоит из пятнадцатиразрядного

0 сдвигового регистра 20, пятнадцатиразрядного блока 21 сравнения, блока 22 суммирования и цифрового компаратора 23.

С помощью переключателя в синхронизаторе 1 телеметрического формата

5 перемычками задают код искомой подпоследовательности в потоке телеметрической информации и параллельный код порога для цифрового компаратора 23 (допустимая величина несовпадения искомой

0 последовательности с телеметрической информацией).

Формирователь 24 импульсов состоит из первого 37, второго 38 корреляционных приемников, аналогового инвертора 39,

5 причем объединенные первые, а также объединенные вторые входы первого 37 и второго 38 выделителей сигналов являются соответственно первым и вторым входами устройства. Выход второго приемника 38

0 сигнала подключен к входу аналогового инвертора 39, выход которого объединен с выходом первого приемника 37 сигнала и подключен к первому входу блока 25.

Блок 24 служит для формирования им5 пульса, амплитуда которого соответствует величине совпадения подпоследовательности с поступающей информацией, а также задержке на 15 бит входного последовательного потока. Выходы блока 24 являются

0 соответственно первым и вторым входами устройства, выход блока 24 - входом блока 25. В качестве первого 37 и второго 38 приемников сигналов могут быть использованы, например, корреляционные приемники,

5 в которых перемычками задают код искомой подпоследовательности в потоке телеметрической информации.

Блок 25 предназначен для преобразования напряжения, поступающего на его вход,

0 в параллельный двоичный код.

Первый 26 и второй 27 компараторы предназначены для выявления соответствия 0-разрядных кодовых сигналов их копиям, для чего входы для исследования

5 сигналов (АО...А7) первого компараторов 26 подключены к соответствующим (1-8) выходами блока 25, причем на входы первого компаратора 26 сигнала (ВО-В7) поступает код, соотгзетствующий логической 1 (в иашем случае 11101000), входы оторого 27

компаратора 27 (AQ-A7) соединены с выходами (1-8) блока 25, а на входи ВО-В7 поступает код, соответствующий логическому О (в нашем случае 00010111), Сигналы (код) на входах BQ-B7 первого 2G и второго 27 компараторов задаются перемычками.

Делитель 29 частоты обеспечивает задержку синхроимпульса на длину слова (15 бит), для чего первый (Q1) выход четвертого регистра 30 соединен с объединенными (С1, С2) входами пятого регистра 31, второй выход (Q2) четвертого регистра 30 соединен с входом записи (VI), объединенные входы (С1, С2) подключены к второму входу чувствительного элемента, первый вход пятого регистра 31 соединен с объединенными входами, вторым синхронизатора 1 телеметрического формата, входом второго од- новибратора 3, первым входом генератора 4 псевдослучайной последовательности, четвертым (С) входом триггера 28.

Триггер 28 предназначен для фазирования входного последовательного цифрового потока с задержанным с точностью до бита, для чего первый вход D триггера 28 соединен с выходами первого 26 и второго 27 компараторов, а второй вход триггера 28 подключен к выходу делителя 29 частоты.

Второй одновибраторЗ служит для формирования коротких импульсов, определяющих время анализа каждого бита тестового сигнала, для чего второй вход элемента И 10 подключен к выходу второго одновибратора 2,

ЭлементИ 10 служит для формирования сигнала ошибки, причем на первый вход этого элемента поступает сигнал сравнения битов через третий инвертор 7 с выхода второго 6 элемента ИСКЛЮЧАЮЩЕЕ ИЛИ.

Работа устройства основана на сравнении бит за битом вторым элементом 6 ИСКЛЮЧАЮЩЕЕ ИЛИ априорно известного двоичного числа, записанного в регистры генератора 4 псевдослучайной последовательности, с копией этого сигнала, сфазирозанной с точностью до бита и восстановленного с регулируемым уровнем регенерации з любом диапазоне величин битовой ошибки.

Последовательный цифровой поток (сигнал А на фиг, 2) в виде псевдослучайной последовательности, порожденной, например, примитивным многочленом Р(х) X + X 1, поступает на первый вход чувствительною элемента 24, на второй вход которого поступают сигналы битовой синхронизации (сигнал Б на фиг. 2). Под возведением шума канала имеют место ошибки (ложные вставки и выпадения битов) в цифровом потоке, в результате чего

уровень сигнала (сигнал В на фиг. 2) на выходе чувствительного элемента 24 изменяется, причем сигнал положительной полярности соответствует выделению логичесхой 1, отрицательной - О.

Блок 25 формирует (сигнал Г, фиг. 2) 8-разрядный параллельный двоичный прямой код, в результате сравнения которого в первом 26 и втором 27 компараторах появ0 ляется сигнал высокого либо низкого уровня, который поступает на вход D триггера 28, на второй вход (С) которого поступает сигнал синхронизации с выхода делителя 29 частоты, в результате чего на выходе тригге5 ра 28 появляется сфазированный до бита сигнал (сигнал Д, фиг, 2), который поступает на первый вход синхронизатора 1 телеметрического формата.

Синхронизатор 1 телеметрического

0 формата реагирует на пятнадцатиразрядную последовательность вида 001001000111000 и допускает до двух ошибочных битов в этой последовательности. После обнаружения этой подпоследователь5 ности синхронизатором 1 телеметрического формата сигнал с его выхода поступает на вход первого опновибратора 2 (сигнал Е, фиг. 2), на инверсном выходе которого формируется отрицательный сигнал, поступающий на

0 второй и третий инверторы 8 и 9 (сигнал Ж, фиг. 2).

После появления сигнала на выходах второго и третьего инверторов 8 и 9 в первый, второй и третий регистры 11-13

5 генератора 4 псевдослучайной последовательности осуществляется запись числа 1111111111. На третий вход генератора 4 поступают сигналы синхронизации с выхода делителя 29 частоты.

0 Сигнал с первого выхода генератора 4. сфазиров&нный с испытательным сигналом (сигнал 3, фиг. 2), поступает на первый вход второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 6, на второй вход которого поступает тест-сиг5 нал. Сигнал с выхода второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 6 поступает на первый инвертор 7 (сигнал И, фиг. 2), на выходе которого формируется сигнал сравнения битов двух потоков, Сигнал ошибки формиру0 ется на выходе элемента И 10 (сигнал К, фиг. 2), причем на первый вход этого элемента поступает сигнал сравнения битов.

На второй вход элемента И 10 поступают короткие импульсы, формируемые вто5 рым одчовибратором 3. Импульсы с выхода второго одновибратора 3 появляются в середине сравниваемых битов. Первый и второй входы генератора 4 псевдослучайной последовательности подключены к входам первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 5.

выход которого соединен с четвертым входом генератора 4.

Положительным эффектом при введении дополнительных элементов в устройство являются повышение достоверности принимаемых решений, а также расширение функциональных возможностей устройства (управление уровнем регенерации цифрового потока).

Мерой достоверности принятых сообщений служит вероятность трансформации сообщения, т.е. вероятность неправильной регистрации принятых сообщений.

Очевидно, что оптимальное устройство оценки достоверности принятых сообщений должно выносить решение или давать оценку достоверности принятых сообщений на основе анализа апостериорных распределений вероятностей принятых сигналов. Сообщения, которые имеют апостериорную вероятность ниже заданной, относятся к группе недостоверных.

Доверительная вероятность ошибки определяется выражением

Р 2Ф(еЧ),(1)

где р - вероятность искажения одного бита последовательности;

q - вероятность правильного приема бита; Ј - допустимая ошибка оценки достоверности цифрового потока;

Р - достоверная вероятность оценки; Ф - функция Лапласа. Формула изобретения Обнаружитель битовой ошибки в последовательном цифровом тестовом потоке по авт. св. tsfe 1322355, от л и ч а ю щий с я тем, что, с целью повышения достоверности приема информации путем управления глубиной регенерации входного цифрового

потока, в него между первым информационным входом устройства и объединенными первыми входами второго элемента ИСКЛЮЧАЮЩЕЕ ИЛ И и синхронизатора введены формирователь импульсов, выход

формирователя импульсов подключен к входу аналого-цифрового преобразователя, делитель частоты, вход которого объединен с вторым входом формирователя импульсов, объединенные синхронизирующие входы

триггера и аналого-цифрового преобразователя, второй еход синхронизатора телеметрического формата, вход второго одновибратора, первый вход генератора псевдослучайной последовательности подключены к выходу делителя частоты, выходы аналого-цифрового преобразователя подключены к соответствующим входам первого и второго компараторов, обьединенные выходы которых подключены к информационному входу триггера, выход которого соединен с первым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ.

| Обнаружитель битовой ошибки в последовательном цифровом тестовом потоке | 1985 |

|

SU1322355A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-08-30—Публикация

1990-11-02—Подача