Предлагаемое изобретение относится к электронным схемам общего назначения, в частности к схемам кодирования, декодирования и преобразования данных при их передаче между удаленными друг от друга абонентами.

Известно устройство [1] для кодирования-декодирования данных, содержащее подключенные к противоположным сторонам линии связи блок передачи данных и блок приема данных, блок передачи данных содержит первый и второй элементы Исключающее ИЛИ, первый усилитель и первый сдвиговый регистр, входы второго элемента Исключающее ИЛИ подключены к выходам первого сдвигового регистра, а выход - к первому входу первого элемента Исключающее ИЛИ, вход последовательных данных первого сдвигового регистра соединен с выходом первого элемента Исключающее ИЛИ и с входом первого усилителя, вход синхронизации первого сдвигового регистра является входом синхронизации устройства, второй вход первого элемента Исключающее ИЛИ является входом данных устройства, выход первого усилителя подключен к линии связи, блок приема данных содержит генератор с фазовой автоподстройкой частоты, второй сдвиговый регистр, третий и четвертый элементы Исключающее ИЛИ и второй усилитель, вход которого подключен к линии связи, а выход - к входу генератора с фазовой автоподстройкой частоты, выход которого соединен с входом синхронизации второго сдвигового регистра и является выходом синхронизации устройства, выходы второго сдвигового регистра соединены с входами третьего элемента Исключающее ИЛИ, выход которого подключен к первому входу четвертого элемента Исключающее ИЛИ, выход которого является выходом данных устройства, а второй вход соединен с входом последовательных данных второго сдвигового регистра и с выходом второго усилителя.

В устройстве [1] блоки передачи и приема данных выполняют, соответственно, функции скремблера и дескремблера. Входные данные преобразуются скремблером к виду, при котором их можно рассматривать как псевдослучайные. Дескремблер выполняет обратное преобразование, т.е. восстанавливает исходные данные. Скремблирование данных позволяет заменить длинные последовательности нулей псевдослучайными битами, что исключает возможность потери синхронизации между блоками приема и передачи данных. Кроме того, разравнивается энергетический спектр передаваемого сигнала, что способствует уменьшению уровня перекрестных помех, наводимых на соседние витые пары проводов кабеля линии связи.

Недостатком устройства [1] является размножение ошибок, которые могут возникнуть при передаче сигнала по линии связи. Так, одиночная ошибка преобразуется в троекратную, так как ошибочный бит сначала непосредственно передается на выход данных устройства, а затем, продвигаясь по второму сдвиговому регистру, еще два раза искажает выходные данные.

Известно устройство [2] для кодирования-декодирования данных, содержащее подключенные к противоположным сторонам линии связи блок передачи данных и блок приема данных, блок передачи данных содержит генератор псевдослучайной последовательности битов, первый элемент Исключающее ИЛИ и первый усилитель, генератор псевдослучайной последовательности битов содержит первый сдвиговый регистр и второй элемент Исключающее ИЛИ, входы которого подключены к выходам первого сдвигового регистра, а выход - к первому входу первого элемента Исключающее ИЛИ и к входу последовательных данных первого сдвигового регистра, вход синхронизации которого является входом синхронизации устройства, второй вход первого элемента Исключающее ИЛИ является входом данных устройства, выход первого усилителя подключен к линии связи, блок приема данных содержит генератор с фазовой автоподстройкой частоты, второй сдвиговый регистр, третий и четвертый элементы Исключающее ИЛИ и второй усилитель, вход которого подключен к линии связи, а выход - к входу генератора с фазовой автоподстройкой частоты, выход которого является выходом синхронизации устройства, выходы второго сдвигового регистра соединены с входами третьего элемента Исключающее ИЛИ, выход которого подключен к первому входу четвертого элемента Исключающее ИЛИ.

В устройстве [2] сдвиговый регистр блока приема данных (дескремблера) логически изолирован от линии связи, поэтому не происходит размножения ошибок, поступающих из линии связи. Однако для поддержания синхронной работы сдвиговых регистров скремблера и дескремблера (в случае нарушения синхронизации устройства или при начальном включении его приемной части) необходимо периодически прерывать передачу полезных данных и передавать по линии связи служебные информационные кадры, содержащие достаточно длинные цепочки синхронизирующих битов. Это уменьшает эффективную скорость передачи данных по линии, усложняет протокол обмена и требует значительного времени ожидания дескремблером служебного кадра в случае потери синхронизации. В течение этого времени передача данных невозможна.

Цель изобретения - повышение скорости передачи данных через устройство и уменьшение потерь данных при восстановлении потерянной синхронизации.

Цель достигается тем, что в устройстве для передачи данных, содержащем подключенные к противоположным сторонам линии связи блок передачи данных и блок приема данных, блок передачи данных содержит генератор псевдослучайной последовательности битов, первый элемент Исключающее ИЛИ и первый усилитель, генератор псевдослучайной последовательности битов содержит первый сдвиговый регистр и второй элемент Исключающее ИЛИ, входы которого подключены к выходам первого сдвигового регистра, а выход - к первому входу первого элемента Исключающее ИЛИ и к входу последовательных данных первого сдвигового регистра, вход синхронизации которого является входом синхронизации устройства, второй вход первого элемента Исключающее ИЛИ является входом данных устройства, выход первого усилителя подключен к линии связи, блок приема данных содержит генератор с фазовой автоподстройкой частоты, второй сдвиговый регистр, третий и четвертый элементы Исключающее ИЛИ и второй усилитель, вход которого подключен к линии связи, а выход - к входу генератора с фазовой автоподстройкой частоты, выход которого является выходом синхронизации устройства, выходы второго сдвигового регистра соединены с входами третьего элемента Исключающее ИЛИ, выход которого подключен к первому входу четвертого элемента Исключающее ИЛИ, блок передачи данных дополнительно содержит третий сдвиговый регистр, первый дешифратор, первый триггер и первый инвертор, выход которого подключен к входу синхронизации первого триггера, вход первого инвертора соединен с входами синхронизации первого и третьего сдвиговых регистров, управляющий вход первого сдвигового регистра соединен с первым выходом первого дешифратора, вход последовательных данных третьего сдвигового регистра соединен с выходом первого элемента Исключающее ИЛИ и с входом данных первого триггера, выход которого соединен с входом первого усилителя, входы параллельных данных первого сдвигового регистра соединены с остальными выходами первого дешифратора, группа входов которого поразрядно соединена с группой выходов третьего сдвигового регистра, блок приема данных дополнительно содержит четвертый сдвиговый регистр, второй дешифратор, второй и третий триггеры и второй инвертор, выход которого подключен к входу синхронизации второго триггера и к входам синхронизации второго и четвертого сдвиговых регистров, управляющий вход второго сдвигового регистра соединен с первым выходом второго дешифратора, вход последовательных данных четвертого сдвигового регистра соединен с вторым входом четвертого элемента Исключающее ИЛИ и с выходом второго триггера, вход данных которого соединен с выходом второго усилителя, входы параллельных данных второго сдвигового регистра соединены с остальными выходами второго дешифратора, группа входов которого поразрядно соединена с группой выходов четвертого сдвигового регистра, вход последовательных данных второго сдвигового регистра соединен с первым входом четвертого элемента Исключающее ИЛИ, выход которого соединен с входом данных третьего триггера, вход синхронизации которого соединен с выходом синхронизации устройства и с входом второго инвертора, выход третьего триггера является выходом данных устройства.

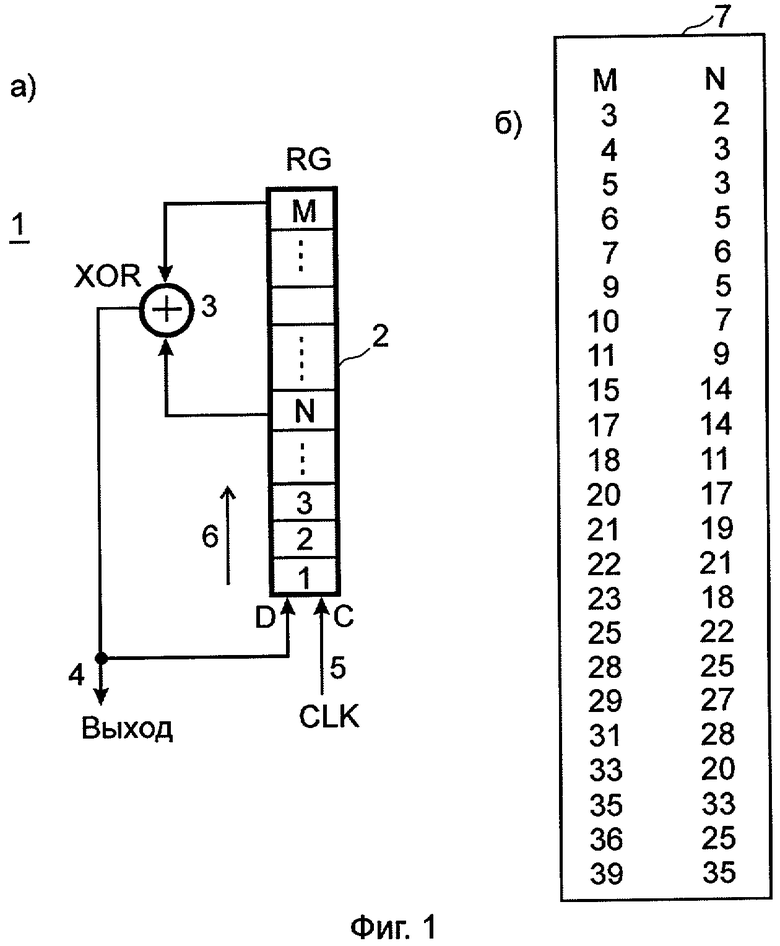

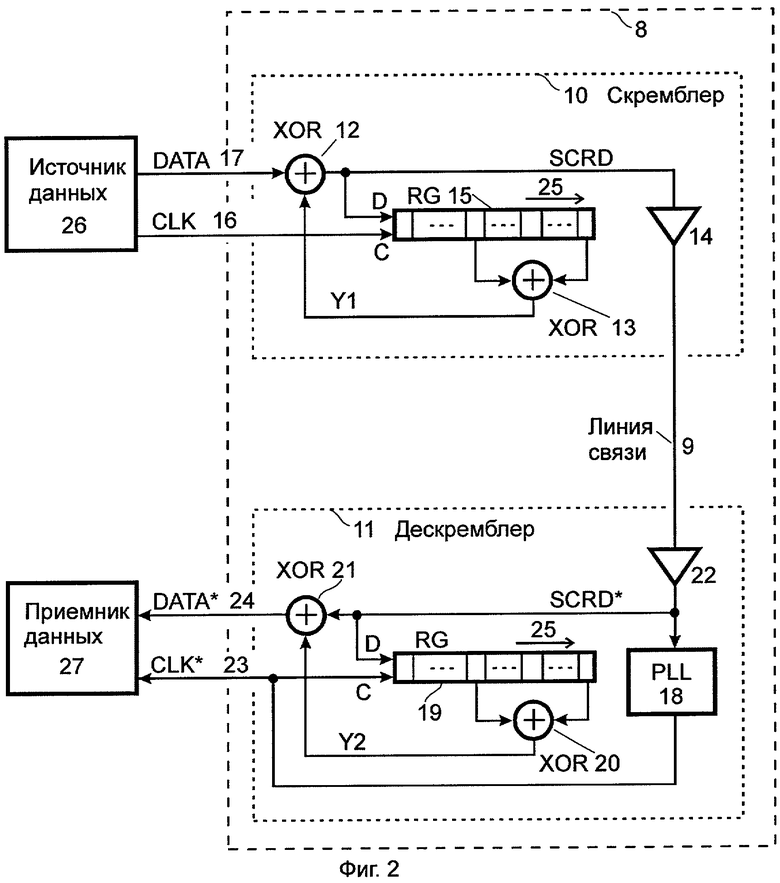

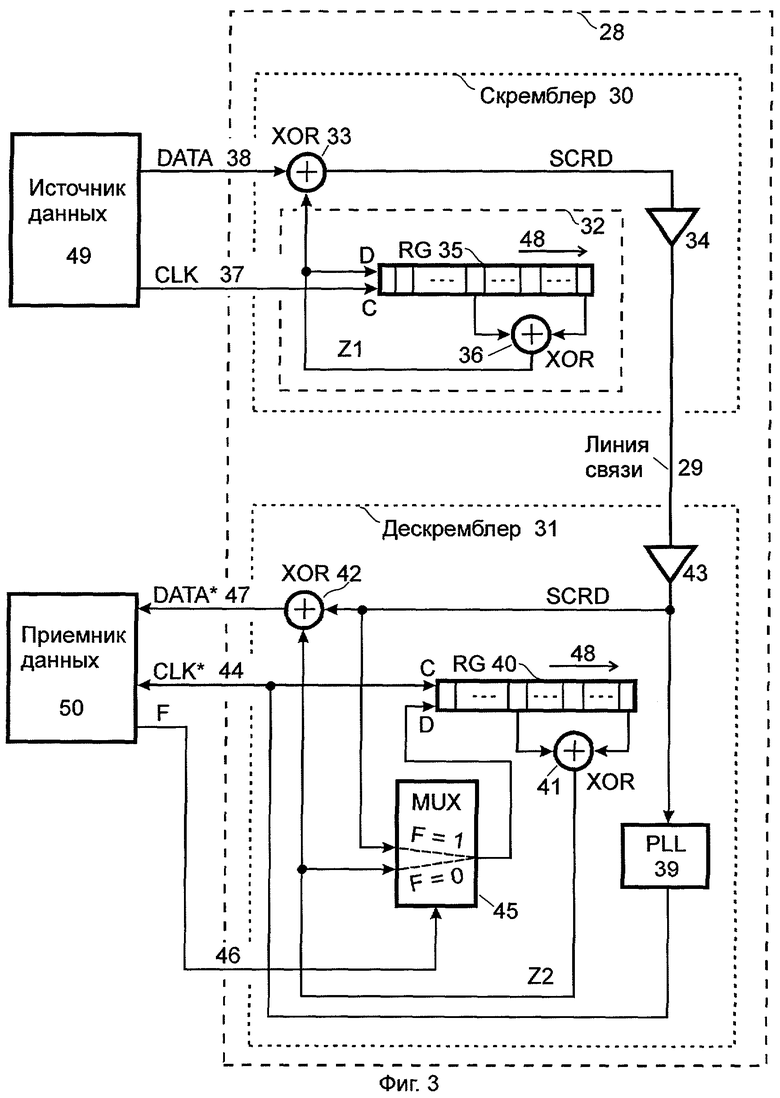

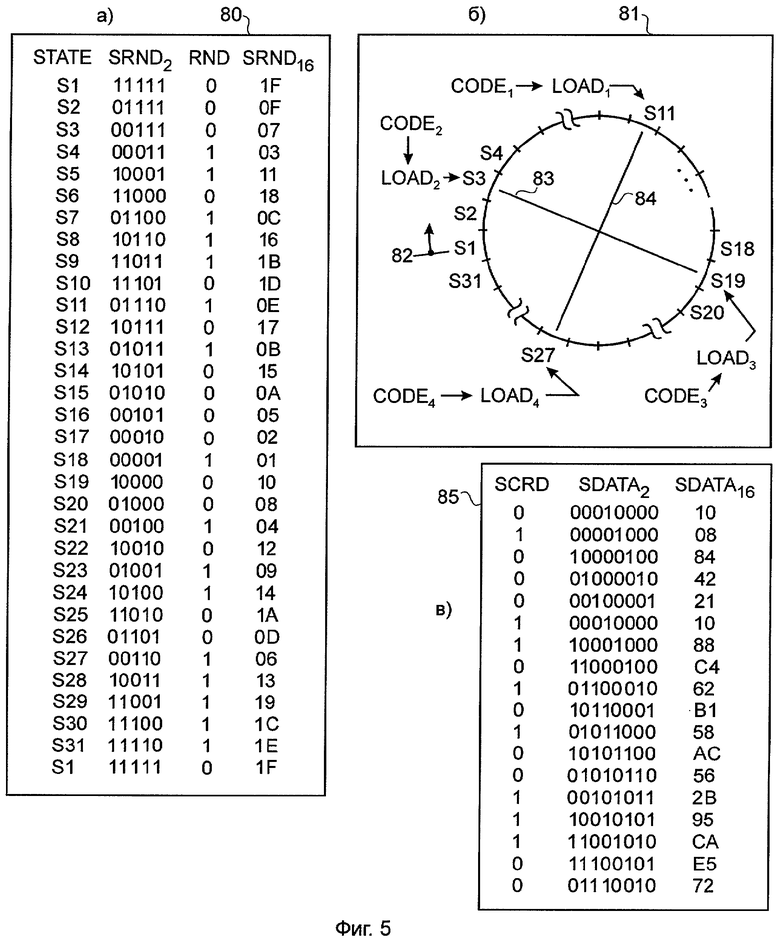

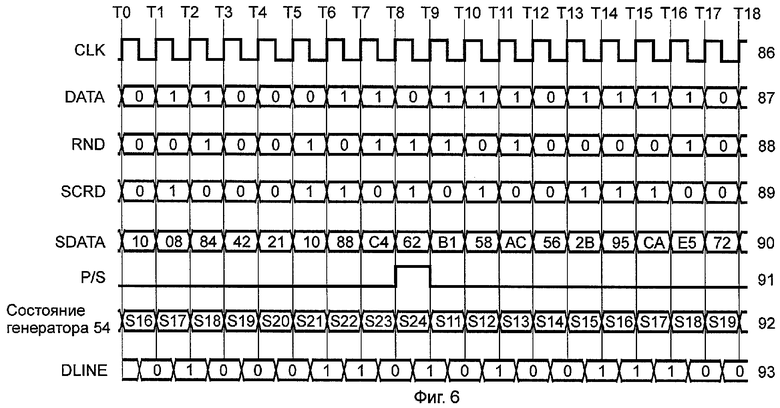

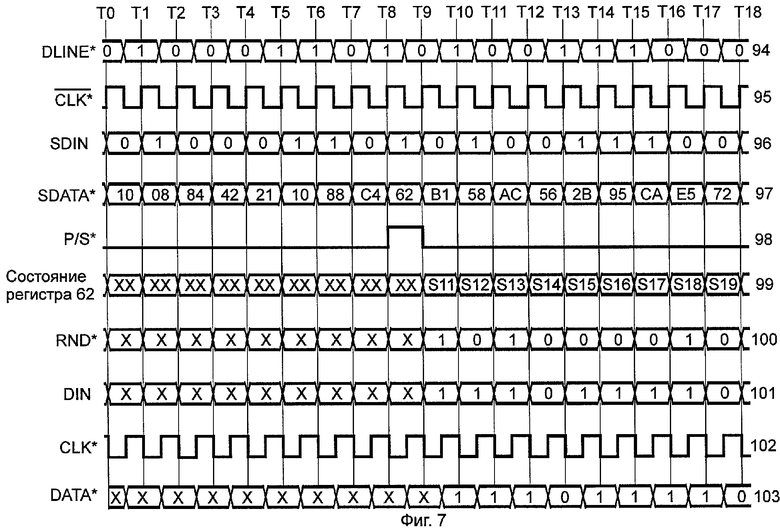

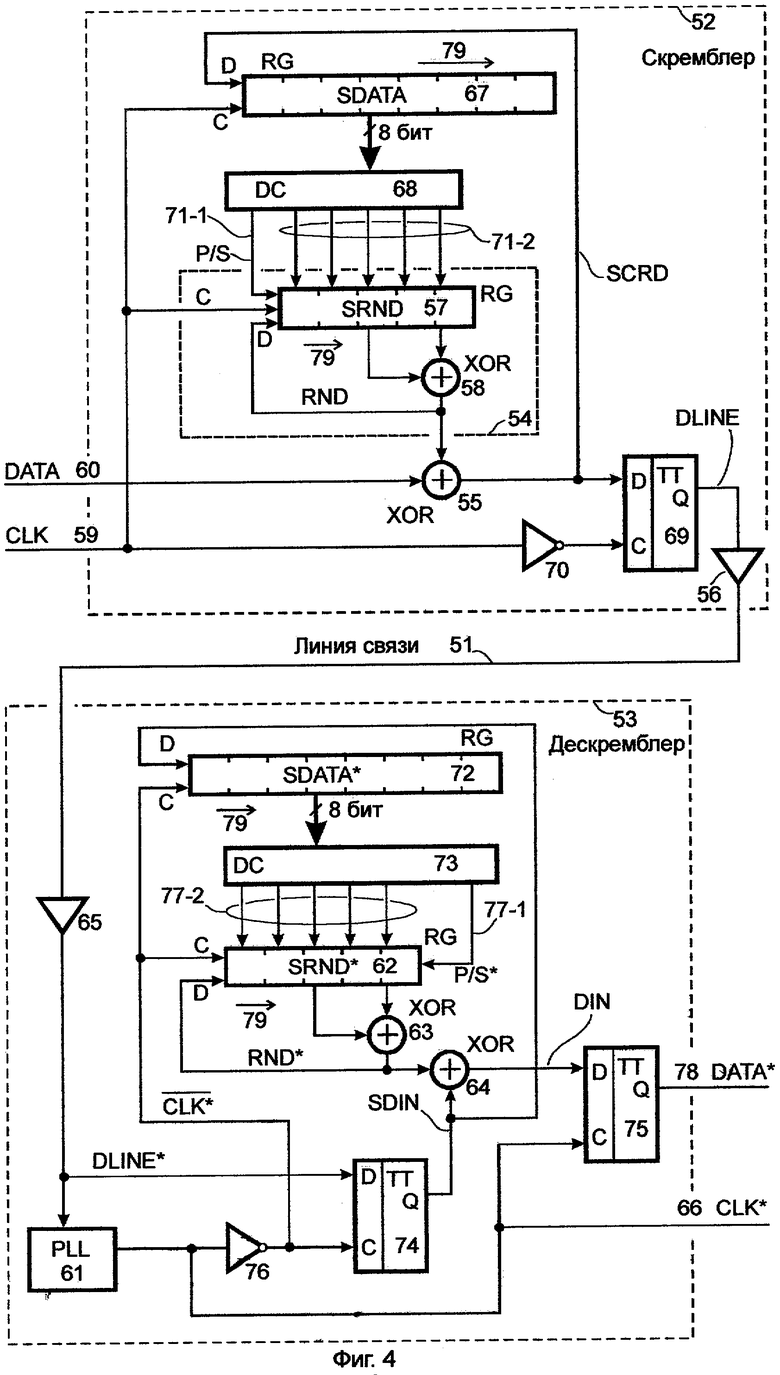

На фиг.1, а и б представлены функциональная схема известного генератора псевдослучайной последовательности битов и таблица - указатель точек подключения цепи обратной связи этого генератора; на фиг.2 - функциональная схема известного устройства [1] для кодирования-декодирования данных; на фиг.3 - функциональная схема известного устройства [2] для кодирования-декодирования данных; на фиг.4 - функциональная схема предлагаемого устройства для кодирования-декодирования данных; на фиг.5, а-в - таблица состояний генератора псевдослучайной последовательности битов, диаграмма состояний этого генератора и пример кодовой ситуации, поясняющий работу предлагаемого устройства; на фиг.6 - временные диаграммы работы блока передачи данных предлагаемого устройства; на фиг.7 - временные диаграммы работы блока приема данных предлагаемого устройства.

Генератор 1 псевдослучайной последовательности битов (фиг.1, д) содержит сдвиговый регистр 2, выходы разрядов М и N которого соединены с входами элемента Исключающее ИЛИ 3, выход которого соединен с входом последовательных данных сдвигового регистра 2 и является выходом 4 генератора 1 псевдослучайной последовательности битов, вход 5 синхронизации сдвигового регистра 2 является входом синхронизации генератора 1 псевдослучайной последовательности битов. Направление сдвига данных в регистре 2 показано стрелкой 6. Номера разрядов М и N регистра 2 выбираются из приведенной на фиг.1, б таблицы 7 - указателя точек подключения цепи обратной связи.

Известное [1] устройство 8 для кодирования-декодирования данных (фиг.2) содержит подключенные к противоположным сторонам линии связи 9 блок 10 передачи данных (скремблер) и блок 11 приема данных (дескремблер), блок 10 передачи данных содержит первый 12 и второй 13 элементы Исключающее ИЛИ, первый 14 усилитель и первый 15 сдвиговый регистр, входы второго 13 элемента Исключающее ИЛИ подключены к выходам первого 15 сдвигового регистра, а выход - к первому входу первого 12 элемента Исключающее ИЛИ, вход последовательных данных первого 15 сдвигового регистра соединен с выходом первого 12 элемента Исключающее ИЛИ и с входом первого 14 усилителя, вход синхронизации первого 15 сдвигового регистра является входом 16 синхронизации устройства, второй вход первого 12 элемента Исключающее ИЛИ является входом 17 данных устройства, выход первого 14 усилителя подключен к линии связи 9, блок 11 приема данных содержит генератор 18 с фазовой автоподстройкой частоты, второй 19 сдвиговый регистр, третий 20 и четвертый 21 элементы Исключающее ИЛИ и второй 22 усилитель, вход которого подключен к линии связи 9, а выход - к входу генератора 18 с фазовой автоподстройкой частоты, выход которого соединен с входом синхронизации второго 19 сдвигового регистра и является выходом 23 синхронизации устройства, выходы второго 19 сдвигового регистра соединены с входами третьего 20 элемента Исключающее ИЛИ, выход которого подключен к первому входу четвертого 21 элемента Исключающее ИЛИ, выход которого является выходом 24 данных устройства, а второй вход соединен с входом последовательных данных второго 19 сдвигового регистра и с выходом второго 22 усилителя. Направления сдвига данных в регистрах 15 и 19 показаны стрелками 25. Внешний источник 26 данных (например, первый компьютер) подключен к входам 16 и 17 устройства 8. Внешний приемник 27 данных (например, второй компьютер) подключен к выходам 23 и 24 устройства 8.

Известное [2] устройство 28 для кодирования-декодирования данных (фиг.3) содержит подключенные к противоположным сторонам линии связи 29 блок 30 передачи данных (скремблер) и блок 31 приема данных (дескремблер), блок 30 передачи данных содержит генератор 32 псевдослучайной последовательности битов, первый 33 элемент Исключающее ИЛИ и первый 34 усилитель, генератор 32 псевдослучайной последовательности битов содержит первый 35 сдвиговый регистр и второй 36 элемент Исключающее ИЛИ, входы которого подключены к выходам первого 35 сдвигового регистра, а выход - к первому входу первого 33 элемента Исключающее ИЛИ и к входу последовательных данных первого 35 сдвигового регистра, вход синхронизации которого является входом 37 синхронизации устройства 28, второй вход первого элемента Исключающее ИЛИ является входом 38 данных устройства 28, выход первого 34 усилителя подключен к линии связи 29, блок 31 приема данных содержит генератор 39 с фазовой автоподстройкой частоты, второй 40 сдвиговый регистр, третий 41 и четвертый 42 элементы Исключающее ИЛИ и второй 43 усилитель, вход которого подключен к линии связи 29, а выход - к входу генератора 39 с фазовой автоподстройкой частоты, выход которого является выходом 44 синхронизации устройства 28, выходы второго сдвигового регистра 40 соединены с входами третьего 41 элемента Исключающее ИЛИ, выход которого подключен к первому входу четвертого 42 элемента Исключающее ИЛИ.

В блоке 30 передачи данных выход первого 33 элемента Исключающее ИЛИ соединен с входом первого 34 усилителя. Блок 31 приема данных содержит также мультиплексор 45, выход которого соединен с входом последовательных данных регистра 40, а управляющий вход является управляющим входом 46 устройства 28. Первый вход данных мультиплексора 45 соединен с первым входом четвертого 42 элемента Исключающее ИЛИ. Второй вход данных мультиплексора 45 соединен со вторым входом четвертого 42 элемента Исключающее ИЛИ и с выходом второго 43 усилителя. Выход четвертого 42 элемента Исключающее ИЛИ является выходом 47 данных устройства 28. Вход синхронизации регистра 40 соединен с выходом 44 синхронизации устройства 28. Направления сдвига данных в регистрах 35 и 40 показаны стрелками 48. Внешний источник 49 данных (например, первый компьютер) подключен к входам 37 и 38 устройства 28. Внешний приемник 50 данных (например, второй компьютер) подключен к выходам 44 и 47 и к входу 46 устройства 28.

Предлагаемое устройство для кодирования-декодирования данных (фиг.4) содержит подключенные к противоположным сторонам линии связи 51 блок 52 передачи данных (скремблер) и блок 53 приема данных (дескремблер), блок 52 передачи данных содержит генератор 54 псевдослучайной последовательности битов, первый 55 элемент Исключающее ИЛИ и первый 56 усилитель, генератор 54 псевдослучайной последовательности битов содержит первый 57 сдвиговый регистр и второй 58 элемент Исключающее ИЛИ, входы которого подключены к выходам первого 57 сдвигового регистра, а выход - к первому входу первого 55 элемента Исключающее ИЛИ и к входу последовательных данных первого 57 сдвигового регистра, вход синхронизации которого является входом 59 синхронизации устройства, второй вход первого 55 элемента Исключающее ИЛИ является входом 60 данных устройства, выход первого 56 усилителя подключен к линии связи 51, блок 53 приема данных содержит генератор 61 с фазовой автоподстройкой частоты, второй 62 сдвиговый регистр, третий 63 и четвертый 64 элементы Исключающее ИЛИ и второй 65 усилитель, вход которого подключен к линии связи 51, а выход - к входу генератора 61 с фазовой автоподстройкой частоты, выход которого является выходом 66 синхронизации устройства, выходы второго 62 сдвигового регистра соединены с входами третьего 63 элемента Исключающее ИЛИ, выход которого подключен к первому входу четвертого 64 элемента Исключающее ИЛИ, блок 52 передачи данных дополнительно содержит третий 67 сдвиговый регистр, первый 68 дешифратор, первый 69 триггер и первый 70 инвертор, выход которого подключен к входу синхронизации первого 69 триггера, вход первого инвертора соединен с входами синхронизации первого 57 и третьего 67 сдвиговых регистров, управляющий вход первого 57 сдвигового регистра соединен с первым 71-1 выходом первого 68 дешифратора, вход последовательных данных третьего 67 сдвигового регистра соединен с выходом первого 55 элемента Исключающее ИЛИ и с входом данных первого 69 триггера, выход которого соединен с входом первого 56 усилителя, входы параллельных данных первого 57 сдвигового регистра соединены с остальными 71-2 выходами первого 68 дешифратора, группа входов которого поразрядно соединена с группой выходов третьего 67 сдвигового регистра, блок 53 приема данных дополнительно содержит четвертый 72 сдвиговый регистр, второй 73 дешифратор, второй 74 и третий 75 триггеры и второй 76 инвертор, выход которого подключен к входу синхронизации второго 74 триггера и к входам синхронизации второго 62 и четвертого 72 сдвиговых регистров, управляющий вход второго 62 сдвигового регистра соединен с первым 77-1 выходом второго 73 дешифратора, вход последовательных данных четвертого 72 сдвигового регистра соединен с вторым входом четвертого 64 элемента Исключающее ИЛИ и с выходом второго 74 триггера, вход данных которого соединен с выходом второго 65 усилителя, входы параллельных данных второго 62 сдвигового регистра соединены с остальными 77-2 выходами второго 73 дешифратора, группа входов которого поразрядно соединена с группой выходов четвертого 72 сдвигового регистра, вход последовательных данных второго 62 сдвигового регистра соединен с первым входом четвертого 64 элемента Исключающее ИЛИ, выход которого соединен с входом данных третьего 75 триггера, вход синхронизации которого соединен с выходом 66 синхронизации устройства и с входом второго 76 инвертора, выход третьего 75 триггера является выходом 78 данных устройства. Стрелками 79 обозначено направление сдвига данных в регистрах 57, 62, 67 и 72.

В таблице 80 (фиг.5, а) представлен список состояний генератора 54 псевдослучайной последовательности битов; диаграмма 81 состояний этого генератора (фиг.5, б) отражает перемещение указателя 82 текущего состояния по кольцевому пути; линии 83 и 84 разделяют диаграмму на четыре сектора. В таблице 85 (фиг.5, в) приведен пример кодовой ситуации, поясняющий работу предлагаемого устройства.

Временные диаграммы 86 и 87 (фиг.6) соответствуют сигналам на входах 59 и 60 предлагаемого устройства; диаграмма 88 - сигналу на выходе элемента Исключающее ИЛИ 58; диаграмма 89 - сигналу на выходе элемента Исключающее ИЛИ 55; диаграмма 90 - сигналам на выходах регистра 67; диаграмма 91 - сигналу на управляющем входе регистра 57; диаграмма 92 - состояниям генератора 54 псевдослучайной последовательности битов; диаграмма 93 - сигналу на входе усилителя 56.

Временная диаграмма 94 (фиг.7) соответствуют сигналу на выходе усилителя 65; диаграмма 95 - сигналу на выходе инвертора 76; диаграмма 96 - сигналу на выходе триггера 74; диаграмма 97 - сигналам на выходах регистра 72; диаграмма 98 - сигналу на управляющем входе регистра 62; диаграмма 99 - состояниям регистра 62 генератора псевдослучайной последовательности битов блока 53; диаграмма 100 - сигналу на выходе элемента Исключающее ИЛИ 63; диаграмма 101 - сигналу на выходе элемента Исключающее ИЛИ 64; диаграмма 102 - сигналу на входе инвертора 76; диаграмма 103 - сигналу на выходе 78 устройства.

Ниже приведено краткое описание работы известных устройств [1, 2].

Скремблеры и дескремблеры обычно содержат генераторы псевдослучайных последовательностей битов или фрагменты таких генераторов. Пример построения генератора псевдослучайной последовательности битов приведен на фиг.1 (см. кн. П.Хоровиц, У.Хилл "Искусство схемотехники": В трех т. - М.: Мир, 1993, - 2 т.). Генератор 1 выполнен на основе сдвигового регистра 2 с логическим элементом Исключающее ИЛИ (XOR) 3 в цепи обратной связи.

В исходном состоянии в регистре 2 присутствует любой ненулевой код (цепь начальной установки регистра не показана). Под действием положительных фронтов синхросигнала CLK на входе 5 этот код циркулирует в генераторе и одновременно видоизменяется. В каждом такте (периоде сигнала CLK) код продвигается в регистре 2 в направлении, указанном стрелкой 6, при этом в освободившийся разряд регистра заносится бит данных с выхода 4. В качестве выхода генератора можно использовать выход элемента Исключающее ИЛИ 3 или выход любого разряда регистра.

В общем случае при использовании M-разрядного регистра 2 цепь обратной связи подключается к разрядам с номерами М и N (М > N). Для того чтобы на выходе генератора формировалась псевдослучайная последовательность битов с периодом повторения, равным 2M - 1, следует выбирать точки подключения цепи обратной связи в соответствии с таблицей 7 (фиг.1, б), которая описывает ряд генераторов различной разрядности. При работе генератора в регистре 2 формируются все возможные M-разрядные коды за исключением нулевого. (Отметим, что во всех описанных далее устройствах можно применять усовершенствованные генераторы, не имеющие запрещенных состояний, см., например, кн. Шевкопляс Б.В. "Микропроцессорные структуры. Инженерные решения": Справочник. - Дополнение первое. - М.: Радио и связь, 1993, - 256 с.).

Псевдослучайная последовательность битов с периодом повторения, равным 2м - 1, обладает следующими свойствами.

1. В полном цикле (2M - 1 тактов) число лог. 1, формируемых на выходе 4 генератора 1, на единицу больше, чем число лог. 0. Добавочная лог. 1 появляется за счет исключения состояния, при котором в регистре 2 присутствовал бы нулевой код. Это можно интерпретировать так, что вероятности появления лог. 0 и лог. 1 на выходе 4 генератора 1 практически одинаковы.

2. В полном цикле (2M - 1 тактов) половина серий из последовательных лог. 1 имеет длину 1, одна четвертая серий - длину 2, одна восьмая - длину 3 и т. д. Такими же свойствами обладают и серии из лог. 0 с учетом пропущенного лог. 0. Это говорит о том, что вероятности появления "орлов" и "решек" не зависят от исходов предыдущих "подбрасываний". Поэтому вероятность того, что серия из последовательных лог. 1 или лог. 0 закончится при следующем подбрасывании, равна 1/2.

3. Если последовательность полного цикла (2M - 1 тактов) сравнивать с этой же последовательностью, но циклически сдвинутой на любое число тактов W (W не является нулем или числом, кратным 2M - 1), то число несовпадений будет на единицу больше, чем число совпадений.

Наиболее распространены две основные схемы устройств для кодирования-декодирования данных (устройств типа "скремблер - дескремблер"): с неизолированными и изолированными (от линии связи) генераторами псевдослучайных последовательностей битов.

В устройстве 8 (фиг.2 [1]) скремблер 10 и дескремблер 11 выполнены с использованием фрагментов рассмотренных ранее генераторов 1 псевдослучайных последовательностей битов (см. фиг.1). В цепь обратной связи генератора на основе сдвигового регистра 15 введен дополнительный элемент Исключающее ИЛИ 12. В дескремблере применен аналогичный генератор на основе сдвигового регистра 19 с разомкнутой цепью обратной связи.

Все процессы, протекающие в устройстве 8, синхронизируются от тактового генератора, размещенного во внешнем источнике данных 26 (возможно также его размещение в блоке 10). Тактовый генератор формирует сигнал CLK - непрерывную последовательность тактовых импульсов со скважностью, равной двум. В каждом такте на вход 17 скремблера 10 подается очередной бит передаваемых данных DATA, а в сдвиговом регистре 15 накопленный код продвигается на один разряд вправо.

Если предположить, что источник данных 26 посылает в скремблер 10 длинную последовательность лог. 0 (DATA ≡ 0), то элемент Исключающее ИЛИ 12 можно рассматривать как повторитель сигнала Y1 с выхода элемента Исключающее ИЛИ 13. В этой ситуации регистр 15 фактически замкнут в кольцо и генерирует точно такую же псевдослучайную последовательность битов, как и в рассмотренной ранее схеме генератора 1 (фиг.1). Если от источника данных 26 поступает произвольная битовая последовательность, то она взаимодействует с последовательностью битов с выхода элемента Исключающее ИЛИ 13. В результате формируется новая (скремблированная) последовательность битов данных SCRD, по структуре близкая случайной. Эта последовательность, в свою очередь, продвигается по регистру 15, формирует поток битов Y на выходе элемента Исключающее ИЛИ 13 и т. д.

Скремблированная последовательность битов SCRD проходит через усилитель 14, передается по линии связи 9 (например, по витой паре проводов многожильного кабеля городской телефонной сети) и поступает в дескремблер 11, где проходит через усилитель 22. С помощью генератора 18 с фазовой автоподстройкой частоты из входного сигнала SCRD* (с выхода усилителя 22) выделяется тактовый сигнал CLK*, который передается на синхронизирующий вход С регистра 19 и на выход 23 устройства 8.

Генератор 18 с фазовой автоподстройкой частоты может быть выполнен по одной из известных схем (см., например, пат. США №6215835 В1). Он предназначен для формирования высокостабильного синхросигнала CLK* на основе непрерывного слежения за входным сигналом SCRD*. В данном случае отрицательный фронт сигнала CLK* привязан к моментам изменения сигнала SCRD* (0 → 1 или 1 → 0), так что положительный фронт сигнала CLK* формируется в середине битового интервала сигнала SCRD*, что соответствует его установившемуся значению. Сдвиг данных в регистре 19 и прием очередного бита SCRD* в освободившийся разряд происходят по положительному фронту сигнала CLK*. Дескремблированные данные DATA* поступают в приемник данных 27 и фиксируются в нем по положительным фронтам сигнала CLK*.

Благодаря достаточной инерционности генератора 18 сигнал CLK* практически нечувствителен к "дрожанию фазы" сигнала SCRD* и иным его кратковременным искажениям, вызванным помехами в линии связи 9. (Такое использование стандартного генератора с фазовой автоподстройкой частоты в телекоммуникационных системах является общепринятым и далее не детализируется).

Потоки данных DATA и DATA* совпадают с точностью до задержки передачи. Действительно, в установившемся режиме в сдвиговых регистрах 15 и 19 присутствуют одинаковые коды, так как на входы D этих регистров поданы одни и те же данные SCRD = SCRD* (с учетом задержки передачи), а тактовая частота одна и та же. Поэтому Y2 = Y1, и с учетом этого DATA* = SCRD* ⊕ Y2 = SCRD ⊕ Y2 = (DATA ⊕ Y1) ⊕ Y2 = DATA ⊕ Y1 ⊕ Y1 = DATA ⊕ 0 = DATA.

Рассмотренный способ скремблирования-дескремблирования данных не требует применения какой-либо специальной процедуры начальной синхронизации (как в устройстве [2]). После заполнения сдвигового регистра 19, как было показано, генераторы псевдослучайных битовых последовательностей на основе регистров 15 и 19 работают синхронно (их состояния всегда одинаковы) и формируют одинаковые сигналы Y1 и Y2. При появлении одиночной ошибки в линии связи 9 кодовая синхронизация (идентичность содержимого регистров 15 и 19) временно нарушается, но затем автоматически восстанавливается, как только правильные данные вновь заполнят регистр 19. Однако в процессе продвижения ошибочного бита по сдвиговому регистру 19, а именно в периоды его попадания сначала на один, а затем на другой вход элемента Исключающее ИЛИ 20 сигнал Y2 дважды принимает неправильное значение. Это приводит к размножению одиночной ошибки - она впервые появляется в сигнале DATA* в момент поступления из линии и затем возникает еще два раза при последующем двукратном искажении сигнала Y.

В устройстве 28 (фиг.3 [2]) применены изолированные от линии связи 29 генераторы псевдослучайных битовых последовательностей. Их начальная кодовая синхронизация осуществляется с использованием аппаратных средств дескремблера и программных средств источника 49 и приемника 50 данных.

К аппаратным средствам относятся мультиплексор 45 (MUX) и программно-управляемый выход 46 приемника 50 данных, на котором формируется управляющий сигнал F. При нормальной работе системы "скремблер-дескремблер" приемник данных 50 постоянно поддерживает на выходе сигнал F = 0. На выход мультиплексора 45 транслируется сигнал Z2 с выхода элемента Исключающее ИЛИ 41, генератор псевдослучайной битовой последовательности на основе регистра 40 изолирован от внешних воздействий.

Предположим, что в исходном состоянии дескремблер не синхронизирован со скремблером. Такая ситуация может возникнуть, например, после включения напряжения питания аппаратуры приемной стороны, после ошибки в работе генератора 39 дескремблера из-за воздействия помех на линию связи или по иным причинам. В отсутствие кодовой синхронизации между скремблером и дескремблером содержимое регистров 35 и 40 не совпадает, поток принимаемых данных DATA* ошибочен и не совпадает с потоком передаваемых данных DATA.

При обнаружении устойчивого хаотического потока данных DATA* (в котором нет обусловленного протоколом обмена разделения на информационные кадры и т.п.) приемник формирует сигнал F = 1. Вследствие этого мультиплексор 45 начинает транслировать на вход D регистра 40 сигнал скремблированных данных SCRD*, как в ранее рассмотренном устройстве (см. фиг.2).

Протокол обмена предусматривает пересылку данных в виде последовательности кадров. Группы обычных кадров перемежаются со служебными кадрами. Например, после группы из 1000 обычных кадров следует один служебный. Он, в частности, содержит синхронизирующую последовательность из некоторого числа (например, 256) нулевых битов. При выдаче этих битов (DATA = 0) в скремблер элемент Исключающее ИЛИ 33 выполняет функцию повторителя сигнала Z1 с выхода элемента Исключающее ИЛИ 36. Поэтому в данном случае скремблированный сигнал SCRD представляет собой фрагмент "истинной" псевдослучайной битовой последовательности, в том смысле, что она не смешана с потоком произвольных данных DATA и порождается только генератором 32 скремблера.

Эта последовательность загружается в регистр 40 и проходит через него, так как F = 1. После того как содержимое регистров 35 и 40 оказывается одинаковым, сигнал Z2 начинает повторять сигнал Z1. Кодовая синхронизация достигнута. На вход приемника 50 данных подается непрерывная последовательность лог. 0, так как DATA* = DATA ≡ 0. После уверенного обнаружения достаточно длинной (например, содержащей 220 бит) последовательности лог. 0 приемник 50 формирует сигнал F = 0 и тем самым возвращает генератор псевдослучайной последовательности битов дескремблера в режим изолированной работы. Теперь кодовая синхронизация не только достигнута, но и "сохранена" благодаря логической изоляции регистра 40 от линии связи 29. После окончания передачи служебного (синхронизирующего) кадра источник 49 данных приступает к передаче группы из 1000 обычных кадров согласно принятому в системе протоколу обмена.

Таким образом, в устройстве [2] для поддержания синхронной работы сдвиговых регистров скремблера и дескремблера (в случае нарушения синхронизации устройства или при начальном включении его приемной части) необходимо периодически прерывать передачу полезных данных и передавать по линии связи служебные информационные кадры, содержащие достаточно длинные цепочки синхронизирующих битов (DATA ≡ 0.). В результате уменьшается эффективная скорость передачи данных по линии, усложняется протокол обмена. Кроме того, с увеличением интервалов между служебными кадрами (что желательно для более эффективной передачи полезных данных) увеличивается время его ожидания дескремблером в случае потери кодовой синхронизации. В течение этого времени передача полезных данных невозможна.

В отличие от устройства [2] в предлагаемом устройстве (фиг.3) восстановление кодовой синхронизации в случае ее потери происходит без передачи по линии связи каких-либо служебных синхронизирующих кодовых последовательностей. Поэтому поток полезных данных не прерывается, время восстановления синхронизации уменьшается.

В общем виде идея построения предлагаемого устройства состоит в следующем. Скремблер и дескремблер содержат изолированные от линии связи генераторы псевдослучайной последовательности битов с одинаковой структурой обратных связей. Скремблированный поток битов постоянно анализируется скремблером и дескремблером с целью отыскания в нем определенных кодов. Обнаружение каждого такого кода скремблером и дескремблером приводит к одновременной установке обоих генераторов псевдослучайной последовательности битов в определенное состояние, соответствующее этому коду. Таким образом, генераторы в случайные моменты одновременно устанавливаются в одинаковые состояния по мере передачи полезных данных. Эти события происходят сравнительно редко, т.е. большую часть времени генераторы работают в режиме "естественного" последовательного перехода от предыдущего состояния к последующему, как было показано при описании генератора 1 (фиг.1). Если кодовая синхронизация не была нарушена, то моменты установки генераторов лишь подтверждает ее. Если кодовая синхронизация была ранее потеряна, то она восстанавливается при первом же обнаружении одного из заданных кодов в потоке скремблированных данных.

Ниже рассмотрена работа составных частей предлагаемого устройства.

Сдвиговые регистры 67 и 72 предназначены для временного хранения фрагментов SDATA и SDATA* потока скремблированных данных. В установившемся режиме эти фрагменты одинаковы (совпадают с точностью до задержки передачи). Прием очередного бита в регистр 67 (72) происходит по положительному фронту сигнала на синхронизирующем входе С. Одновременно с приемом очередного бита с входа D ранее хранимые данные сдвигаются на один разряд вправо (по стрелке 79). В данном примере построения устройства разрядность регистра 67 (72) выбрана равной восьми, хотя она может быть большей или меньшей. Динамику работы регистра 67 можно проследить по таблице 85 его состояний (фиг.5, в).

Генератор 54 псевдослучайной последовательности битов скремблера 52 содержит сдвиговый регистр 57 и элемент Исключающее ИЛИ 58. Аналогичный генератор псевдослучайной последовательности битов дескремблера 53 содержит сдвиговый регистр 62 и элемент Исключающее ИЛИ 63.

Сдвиговые регистры 57 и 62 предназначены для временного хранения псевдослучайных кодов SRND и SRND*. В установившемся режиме эти коды одинаковы (совпадают с точностью до задержки передачи). Прием очередного бита в регистр 57 (62) с входа D происходит по положительному фронту сигнала на синхронизирующем входе С при условии, что на его управляющем входе P/S (P/S*), задающем режим параллельного или последовательного приема данных, присутствует сигнал лог. 0. Одновременно с приемом очередного бита с входа D происходит сдвиг ранее хранимого кода на один разряд вправо (по стрелке 79). Если на управляющем входе P/S (P/S*) регистра 57 (62) присутствует сигнал лог. 1, то по положительному фронту сигнала на синхронизирующем входе С в регистр принимается параллельный код с группы входов 71 (77). В данном примере построения устройства разрядность регистра 57 (62) выбрана равной пяти, хотя она может быть большей или меньшей. При этом точки подключения элемента Исключающее ИЛИ 58 (63) к регистру 57 (72) выбираются в соответствии с таблицей, представленной на фиг.1, б.

Начальное состояние регистра 57 может быть любым, в том числе нулевым. Выход из нулевого состояния происходит при записи в регистр параллельного кода с входов 71. Программа инициализации скремблера предусматривает выдачу на его вход 60 некоторого кода CODE1, который распознается дешифратором 68. Если в регистре 57 первоначально присутствовал нулевой код, то код CODE1 без изменения проходит через элемент Исключающее ИЛИ 55 и последовательно загружается в регистр 67. Дешифратор 68 реагирует на него переводом регистра 57 в режим параллельной загрузки (P/S = 1) и формированием ненулевого кода LOAD1, который затем принимается в регистр 57 с входов 71. Таким образом, генератор 54 выходит из запрещенного состояния 000...0. Если первоначальное состояние регистра 57 было ненулевым, то выдача кода CODE1 на вход 60 оказывается бесполезной, но не приводит к каким-либо нежелательным последствиям. Возможна также и аппаратная установка регистра 57 в ненулевое состояние (соответствующий вход регистра 57 не показан).

Начальное состояние регистра 62 также может быть любым, в том числе нулевым. Это состояние обновляется (становится заведомо ненулевым) при обнаружении дешифратором 73 в скремблированном потоке данных одного из заранее заданных кодов (CODE1 и, возможно, других).

Элемент Исключающее ИЛИ 55 (58, 63, 64) формирует на выходе сигнал лог. 1 только в том случае, когда входные сигналы имеют противоположные логические значения (лог. 0 и лог. 1). Элементы Исключающее ИЛИ 58 и 63 формируют выходные сигналы RND и RND* генераторов псевдослучайных последовательностей битов скремблера 52 и дескремблера 53. Элементы Исключающее ИЛИ 55 и 64 формируют скремблированный SCRD и дескремблированный DIN сигналы данных.

Триггеры D-типа 69, 74 и 75 принимают биты данных с входа D по положительному фронту сигнала на входе синхронизации С. Триггеры 69 и 75 формируют выходные сигналы DLINE и DATA*, в которых на границах между битовыми интервалами сигнал может измениться только один раз, в то время как входные сигналы SCRD и DIN этих триггеров на границах между битовыми интервалами могут многократно изменяться из-за неодновременного протекания переходных процессов (гонок сигналов) в цепях 57-58-55; 60-55 и 62-63-64; 74-64. Триггер 74 практически полностью устраняет джиттер входного сигнала ("дрожание" фронтов на границах между битовыми интервалами) благодаря тому, что прием бита в этот триггер происходит в центре битового интервала, когда переходные процессы сигнала DLINE* уже закончились. Остаточный джиттер сигнала SDIN на выходе триггера 74 определяется неидеальностью сигнала CLK* на выходе генератора 61. Исходные состояния триггеров 69, 74 и 75 произвольны.

Инвертор 70 (76) преобразует входной сигнал лог. 0 в выходной сигнал лог. 1 и наоборот входной сигнал лог. 1 в выходной сигнал лог. 0.

Генератор 61 с фазовой автоподстройкой частоты может быть выполнен по одной из известных схем (см., например, пат. США №6215835 В1). Он предназначен для формирования высокостабильного синхросигнала CLK* на основе непрерывного слежения за входным сигналом DLINE*. Положительный фронт сигнала CLK* привязан к моментам изменения сигнала DLINE* (0 → 1 или 1 → 0), так что отрицательный фронт сигнала CLK* формируется в середине битового интервала сигнала DLINE*, что соответствует его установившемуся значению.

Благодаря достаточной инерционности генератора 61 сигнал CLK* практически нечувствителен к джиттеру сигнала DLINE* и иным его кратковременным искажениям, вызванным помехами в линии связи 51. (Такое использование стандартного генератора с фазовой автоподстройкой частоты в телекоммуникационных системах является общепринятым и далее не детализируется).

Дешифратор 68 (73) предназначен для выделения в потоке скремблированных данных, проходящем через сдвиговый регистр 67 (72), определенных кодов CODE1, CODE2, ..., CODEJ. При обнаружении дешифратором 68 (73) указанных кодов на его выходах 71 (77) формируется соответствующий M-разрядный код LOAD1, LOAD2, ..., LOADj для последующей паралллельной загрузки сдвигового регистра 57 (62). В данном примере построения устройства J = 4, М = 5. При обнаружении любого кода CODE1, CODE2, ..., CODEJ дешифратор 68 (73) формирует также единичный сигнал на входе P/S (P/S*) управления режимом работы регистра 57 (62), подготавливая его к параллельному приему данных по положительному фронту очередного синхроимпульса на входе С.

Усилитель 56 (65) предназначен для передачи (приема) скремблированного сигнала данных в линию (из линии) 51. Параметры усилителей 56 и 65 определяются типом линии связи 51, которая может быть выполнена в виде витой пары проводов, коаксиального или оптоволоконного кабеля и т.п.

Далее приведено описание работы предлагаемого устройства.

Входные данные DATA и сопровождающий их сигнал CLK синхронизации поступают на входы 60 и 59 устройства. Положительные фронты сигнала CLK (моменты Т0, Т1, ..., Т18 на фиг.6) соответствуют границам между битовыми интервалами сигнала данных DATA, как показано на диаграммах 86 и 87. По положительным фронтам сигнала CLK изменяется содержимое регистра 67 (диаграмма 90), генератор 54 переходит в новое состояние (диаграмма 92). При этом формируется очередной псевдослучайный бит RND (диаграмма 88), который складывается по модулю два с битом данных DATA и преобразуется в скремблированный бит данных SCRD (диаграмма 89). По окончании переходных процессов, в момент формирования отрицательного фронта сигнала CLK, бит SCRD принимается в триггер 69 (диаграмма 93 сигнала DLINE) и через усилитель 56 передается в линию связи 51.

В интервале времени Т8-Т9 дешифратор 68 формирует сигнал лог. 1 на входе P/S управления режимом работы регистра 57 (диаграмма 91), подготавливая его к приему параллельных данных в момент Т9.

В отсутствие параллельной загрузки генератор 54 псевдослучайной последовательности битов последовательно, циклически проходит через ряд состояний S1, S2, S3, ..., S31, S1, S2 и т.д., как показано на фиг.5, а, б (таблица 80, диаграмма 81). В состоянии S1 (см. первую строку таблицы 80, а также указатель 82 на диаграмме 81) в регистре 57 хранится пятиразрядный двоичный код 111112= 1F16, на выходе RND генератора 54 сформирован сигнал лог. 0. В следующем такте указатель 82 перемещается по часовой стрелке и фиксируется на соседней позиции, генератор 54 переходит в состояние S2, при котором SRND = 011112 = 0F16, RND = 0 и т.д. Этот процесс циклически повторяется, указатель 82 вращается по кругу, последовательно проходя все возможные состояния Si.

Параллельная загрузка регистра 57 в произвольном такте приводит к принудительной установке генератора в одно из заданных состояний, в данном примере в состояния S3, S11, S19 или S27. Эти состояния предпочтительно выбираются так, чтобы на диаграмме 81 дуги S3-S11, S11-S19, S19-S27 и S27 - S3 имели примерно равную длину (см. указатели 83 и 84, которые разделяют окружность на четыре примерно равные части). В процессе работы устройства генератор 54 сравнительно редко, с равной вероятностью устанавливается в эти состояния, а в промежутках между такими установками продолжает равномерное вращение по часовой стрелке.

Выбор нескольких (а не одного) заданных состояний, в которые генератор переходит в моменты его параллельной загрузки, целесообразен в тех случаях, когда число состояний генератора достаточно велико, и в течение полного оборота указателя 82 вероятность параллельной загрузки регистра 57 близка к единице. Поэтому если указатель 82 периодически "срывается" с равномерного вращения в одно и то же заданное состояние, то вероятность того, что он успеет совершить хотя бы один полный оборот, становится невысокой. Иными словами, некоторые состояния генератора 54 будут использоваться реже, чем другие, а тогда отмеченные ранее (при описании генератора 1, см. фиг.1) свойства "канонической" псевдослучайной последовательности битов будут в некоторой степени утеряны, что нежелательно. Наличие нескольких фиксированных точек установки, равномерно распределенных по диаграмме 81, выравнивает вероятности использования всех возможных состояний генератора 54.

Как показано на диаграммах 90 и 91, одним из кодов, вызывающих принудительную установку генератора 54 в фиксированное состояние, является код SDATA = CODE1 = 6216 = 011000102. Этот код присутствует в регистре 67 в интервале времени Т8-Т9 и, как уже отмечалось, дешифратор 68 реагирует на него подготовкой регистра 57 к приему параллельного кода LOAD1 с входов 71. Этот код в данном примере равен 0E16 = 011102 и соответствует состоянию S11 генератора 54 (см. табл. 80 на фиг.5 а). Таким образом, в момент Т9 цепь последовательных переходов ... S16, S17, ..., S23, S24 разрывается и вместо перехода в очередное состояние S25 генератор 54 "перескакивает" в состояние S11. После этого формируется новая цепь последовательных переходов: S11, S12, ..., S18, S19, ... - вплоть до возникновения очередной ситуации, при которой эта цепь разрывается, а затем образуется следующая цепь с одним из начальных состояний S3, S11, S19 или S27 и т.д.

Принятые из линии 51 скремблированные данные DLINE* синхронизируют генератор 61 с фазовой автоподстройкой частоты, в результате на его выходе формируется сигнал CLK*, а на выходе инвертора 76 - его инверсное значение (диаграммы 94, 102, 95 на фиг.7). Сигнал SDIN (диаграмма 96) на выходе триггера 74 повторяет сигнал DLINE* с задержкой на половину периода синхросигнала, при этом сигнал SDIN, как уже отмечалось, практически не содержит фазовых искажений (джиттера). Скремблированные данные SDIN последовательно проходят через регистр 72. После его заполнения данные SDATA* (диаграмма 97) совпадают с данными SDATA в регистре 67 скремблера 52.

Это следует из того, что, во-первых, источник данных для обоих регистров общий - выход элемента Исключающее ИЛИ 55, и, во-вторых, ничто не препятствует одновременному (с точностью до задержки передачи) заполнению обоих регистров одинаковыми данными. Так как дешифраторы 73 и 57 идентичны, а данные на их входах одинаковы, то сигналы на выходах этих дешифраторов также совпадают (с точностью до задержки передачи). Из этого следует, что рассмотренный ранее процесс установки генератора 54 в определенное состояние протекает также и в дескремблере 53, а именно: в интервале времени Т8-Т9 (фиг.7) на входе P/S* регистра 62 формируется сигнал лог. 1 (диаграмма 98), в момент Т9 в регистр 62 принимается параллельный код ОЕ16, соответствующий состоянию S11.

Независимо от предыстории состояния генератора псевдослучайной последовательности битов дескремблера 53, начиная с момента Т9 этот генератор синхронизируется с генератором 54 скремблера 52 в том смысле, что формируемые обоими генераторами последовательности битов совпадают. Неопределенные состояния и сигналы в начальный период, когда кодовая синхронизация между генераторами отсутствовала, помечены на диаграммах 99, 100, 101 и 103 символами "X".

Начиная с момента Т9 скремблирующая RND (диаграмма 88 на фиг.6) и дескремблирующая RND* (диаграмма 100 на фиг.7) последовательности битов совпадают, поэтому сигнал DIN (диаграмма 101) дескремблированных данных совпадает с сигналом DATA (диаграмма 87) на входе 60 устройства с точностью до задержки передачи. Выходной сигнал DATA* (диаграмма 103) данных, "очищенный" от возможных многократных переключений на границах между битовыми интервалами, поступает на выход 78 устройства и сопровождается сигналом CLK*. Таким образом, входные сигналы DATA и CLK преобразуются в совпадающие с ними (с точностью до задержки передачи) выходные сигналы DATA* и CLK*.

Частота следования моментов синхронной установки регистров 57 и 62 в одинаковые состояния (моментов синхронизации) зависит от скорости передачи данных, а также от разрядности и числа J кодов CODE1, CODE2, ..., CODEJ, распознаваемых дешифраторами 68 и 73.

При J = 1 и разрядности регистра 67 (72), равной 8, в скремблированном потоке данных, в среднем в каждой цепи из 256 бит, будет встречаться один искомый код, равный CODE1. При скорости передачи данных, равной 10 Мбит/с, средняя частота следования моментов синхронизации составляет 10 000 000/256=39 062,5 Гц. При J = 4 частота моментов синхронизации увеличивается в четыре раза и составляет 156 250 Гц.

Для уменьшения вероятности ложного распознавания кодов CODE1, CODE2, ..., CODEJ дешифратором 73 дескремблера в связи с поступлением из линии связи в регистр 72 ошибочных битов разрядность этого регистра можно увеличить, например, до 20 бит.

Применение предлагаемого устройства позволяет повысить скорость передачи полезных данных и уменьшить их потери при восстановлении нарушенной синхронизации благодаря исключению из потока данных служебной синхронизирующей информации.

Источники информации

1. Патент США №5530959 (Fig. 1).

2. Патент США №5530959 (Fig. 5) (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ДАННЫХ | 2004 |

|

RU2262205C1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ДАННЫХ | 2004 |

|

RU2271612C1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ДАННЫХ | 2004 |

|

RU2272360C1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ДАННЫХ | 2001 |

|

RU2205445C1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ДАННЫХ | 2001 |

|

RU2214061C2 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ДАННЫХ | 2003 |

|

RU2242789C1 |

| УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ДАННЫХ | 2002 |

|

RU2214046C1 |

| УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ - ДЕКОДИРОВАНИЯ ДАННЫХ | 2002 |

|

RU2214044C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ДЛИНЫ ДВУХПРОВОДНОЙ ЛИНИИ ПЕРЕДАЧИ ДАННЫХ | 2002 |

|

RU2233554C1 |

| УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ - ДЕКОДИРОВАНИЯ ДАННЫХ | 2002 |

|

RU2206181C1 |

Изобретение относится к устройствам для кодирования - декодирования данных и может быть использовано в синхронных телекоммуникационных системах. Достигаемый технический результат - повышение скорости передачи данных через устройство и уменьшение потерь данных при восстановлении потерянной синхронизации - обеспечивается благодаря распознаванию в скремблированном потоке данных определенных кодов и, как следствие этого, установке генераторов псевдослучайных последовательностей битов скремблера и дескремблера в одинаковые состояния без использования каких-либо специально вводимых в поток данных служебных синхронизирующих кодов. Устройство содержит подключенные к противоположным сторонам линии связи блок передачи данных (скремблер 52) и блок приема данных (дескремблер 53), которые содержат логически изолированные от линии связи генераторы псевдослучайной последовательности битов, выполненные, соответственно, на основе сдвиговых регистров (57,62) и элементов Исключающее ИЛИ (58, 63). Устройство содержит также элементы Исключающее ИЛИ (55, 64), усилители (56,65,76), генератор с фазовой автоподстройкой частоты (61), сдвиговые регистры (67,72), дешифраторы (68,73), триггеры (69,74,75), инверторы (70,76). 7 ил.

Устройство для кодирования-декодирования данных, содержащее подключенные к противоположным сторонам линии связи блок передачи данных и блок приема данных, блок передачи данных содержит генератор псевдослучайной последовательности битов, первый элемент Исключающее ИЛИ и первый усилитель, генератор псевдослучайной последовательности битов содержит первый сдвиговый регистр и второй элемент Исключающее ИЛИ, входы которого подключены к выходам первого сдвигового регистра, а выход - к первому входу первого элемента Исключающее ИЛИ и к входу последовательных данных первого сдвигового регистра, вход синхронизации которого является входом синхронизации устройства, второй вход первого элемента Исключающее ИЛИ является входом данных устройства, выход первого усилителя подключен к линии связи, блок приема данных содержит генератор с фазовой автоподстройкой частоты, второй сдвиговый регистр, третий и четвертый элементы Исключающее ИЛИ и второй усилитель, вход которого подключен к линии связи, а выход - к входу генератора с фазовой автоподстройкой частоты, выход которого является выходом синхронизации устройства, выходы второго сдвигового регистра соединены с входами третьего элемента Исключающее ИЛИ, выход которого подключен к первому входу четвертого элемента Исключающее ИЛИ, отличающееся тем, что блок передачи данных дополнительно содержит третий сдвиговый регистр, первый дешифратор, первый триггер и первый инвертор, выход которого подключен к входу синхронизации первого триггера, вход первого инвертора соединен с входами синхронизации первого и третьего сдвиговых регистров, вход последовательных данных третьего сдвигового регистра соединен с выходом первого элемента Исключающее ИЛИ и с входом данных первого триггера, выход которого соединен с входом первого усилителя, при обнаружении в потоке данных третьего сдвигового регистра определенных кодов первый дешифратор формирует единичный сигнал на управляющем входе первого сдвигового регистра, после чего осуществляет его параллельную загрузку, блок приема данных дополнительно содержит четвертый сдвиговый регистр, второй дешифратор, второй и третий триггеры и второй инвертор, выход которого подключен к входу синхронизации второго триггера и к входам синхронизации второго и четвертого сдвиговых регистров, вход последовательных данных четвертого сдвигового регистра соединен с вторым входом четвертого элемента Исключающее ИЛИ и с выходом второго триггера, вход данных которого соединен с выходом второго усилителя, при обнаружении в потоке данных четвертого сдвигового регистра определенных кодов второй дешифратор формирует единичный сигнал на управляющем входе второго сдвигового регистра, после чего осуществляет его параллельную загрузку, вход последовательных данных второго сдвигового регистра соединен с первым входом четвертого элемента Исключающее ИЛИ, выход которого соединен с входом данных третьего триггера, вход синхронизации которого соединен с выходом синхронизации устройства и с входом второго инвертора, выход третьего триггера является выходом данных устройства.

| US 5530959 A, 25.06.1996.RU 2214046 C1, 10.10.2003.RU 2206181 C1, 10.06.2003.US 2003/0145196 A1, 31.07.2003.WO 01/95495 A1, 13.12.2001.US 4790013, 06.12.1988.WO 03/096604 A1, 20.11.2003.JP 3088443, 12.04.1991. |

Авторы

Даты

2005-09-10—Публикация

2004-04-12—Подача