СЛ tsD

СО 4

ел

СО

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1987 |

|

SU1494778A1 |

| Программируемый контроллер | 1985 |

|

SU1509887A2 |

| Устройство адресации памяти | 1988 |

|

SU1532935A1 |

| Устройство для определения области работоспособности радиоэлектронных схем | 1986 |

|

SU1386947A1 |

| Устройство для реализации логических функций | 1989 |

|

SU1619247A1 |

| Устройство для распаковки команд | 1984 |

|

SU1196865A1 |

| Устройство для отображения символьной информации на экране видеоконтрольного блока | 1991 |

|

SU1836678A3 |

| Устройство управления углом опережения зажигания двигателя внутреннего сгорания | 1986 |

|

SU1381536A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ РАДИОТЕЛЕМЕТРИЧЕСКИХ СИГНАЛОВ | 1994 |

|

RU2126139C1 |

Изобретение может быть использовано в измерительных системах для метрологической аттестации быстродействующих и высокоточных аналого-цифровых преобразователей (АЦП) в динамическом режиме. Повышение достоверности контроля достигается за счет введения в устройство, содержащее генератор 1 эталонного сигнала, генератор 6 синхроимпульсов, блок 5 управления, вычислительный блок 10, блок 9 памяти, блок 8 адресации и блок 7 блокировки, новых блоков, что позволило обеспечить условия аттестации, адекватные реальным условиям эксплуатации АЦП, при условии фильтрации цифровых отсчетов, соответствующих значениям испытательного сигнала за пределами динамического диапазона АЦП. 1 з.п. ф-лы, 4 ил.

Фиг.1

Изобретение относится к цифровой измерительной технике и может быть использовано для измерения динамической погрешности быстродействующих и высокочастотных аналого-цифровых преобразователей (АЦП) в измерительных системах, их метрологической аттестации в динамическом режиме.

Цель изобретения - повьпиение дос- товерности контроля.

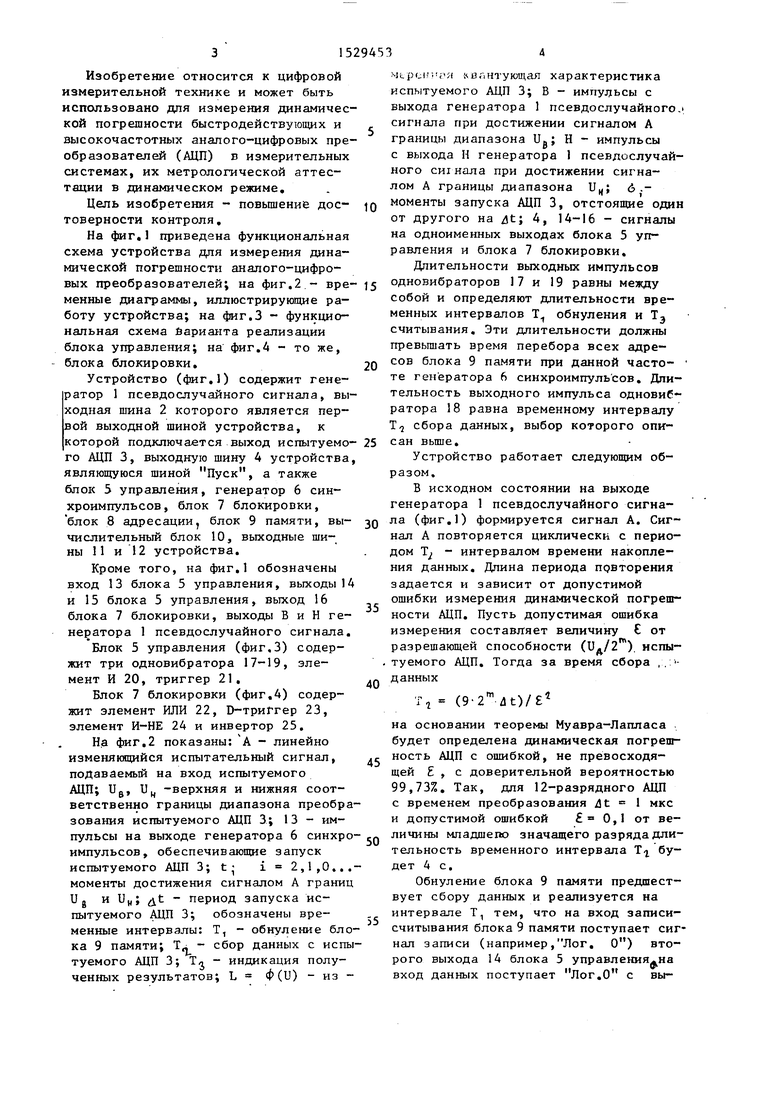

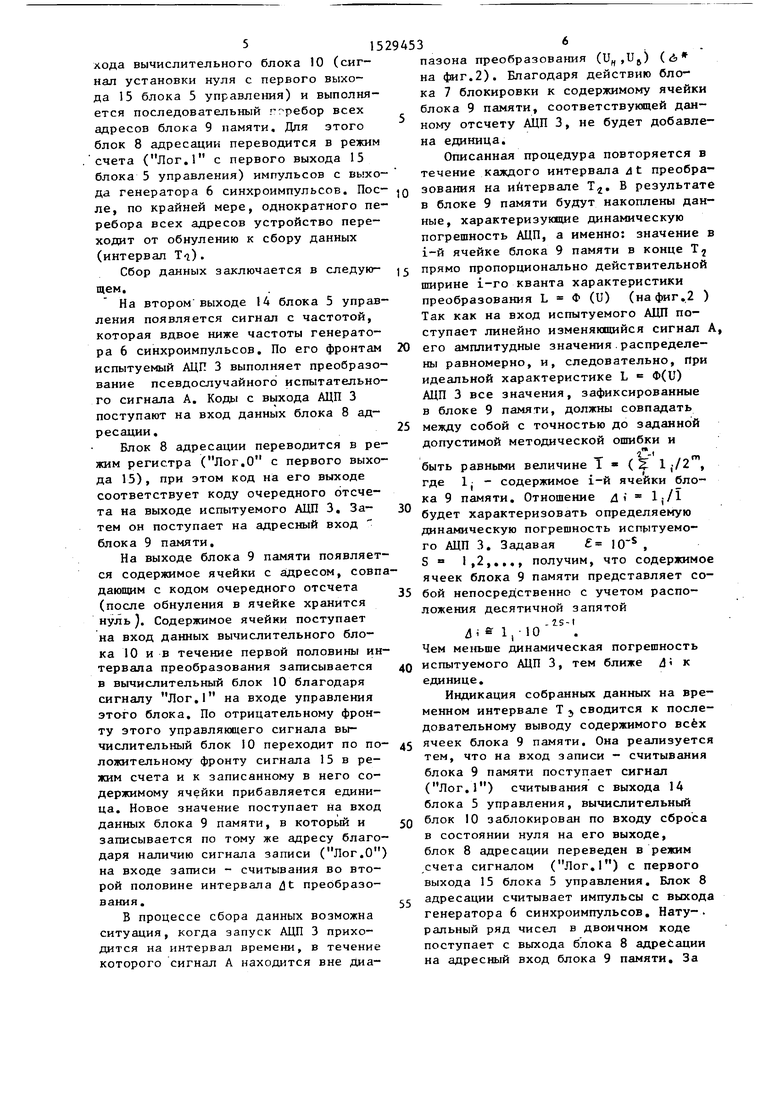

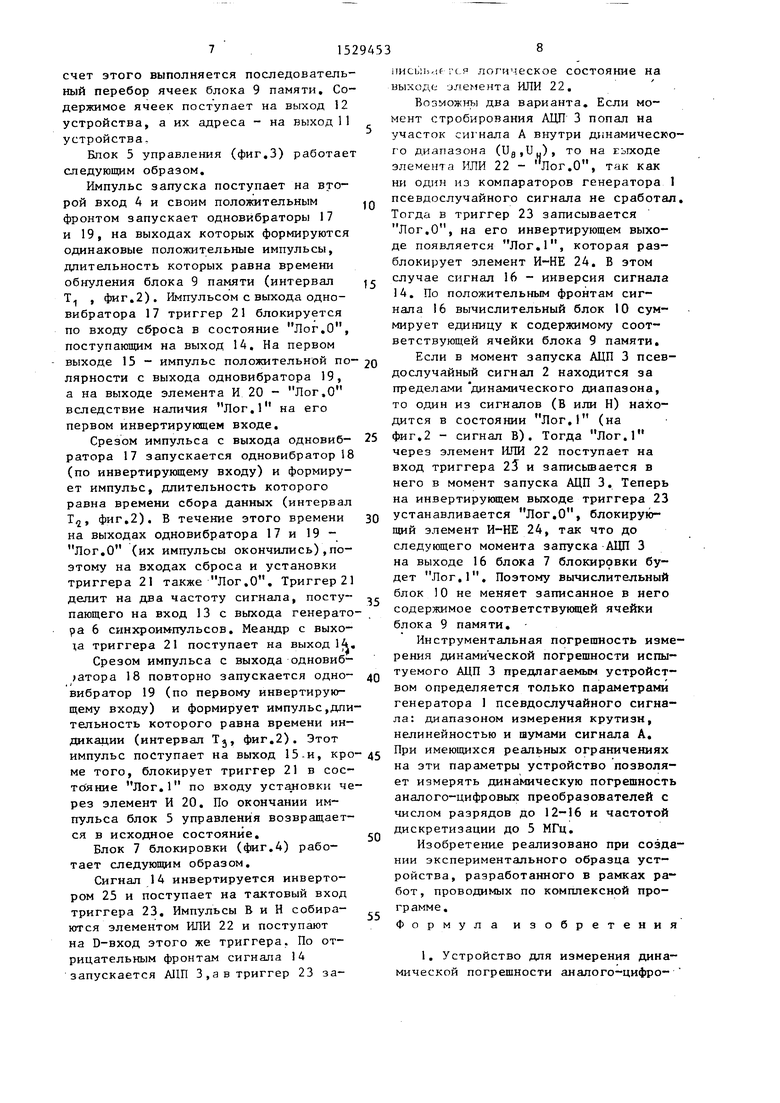

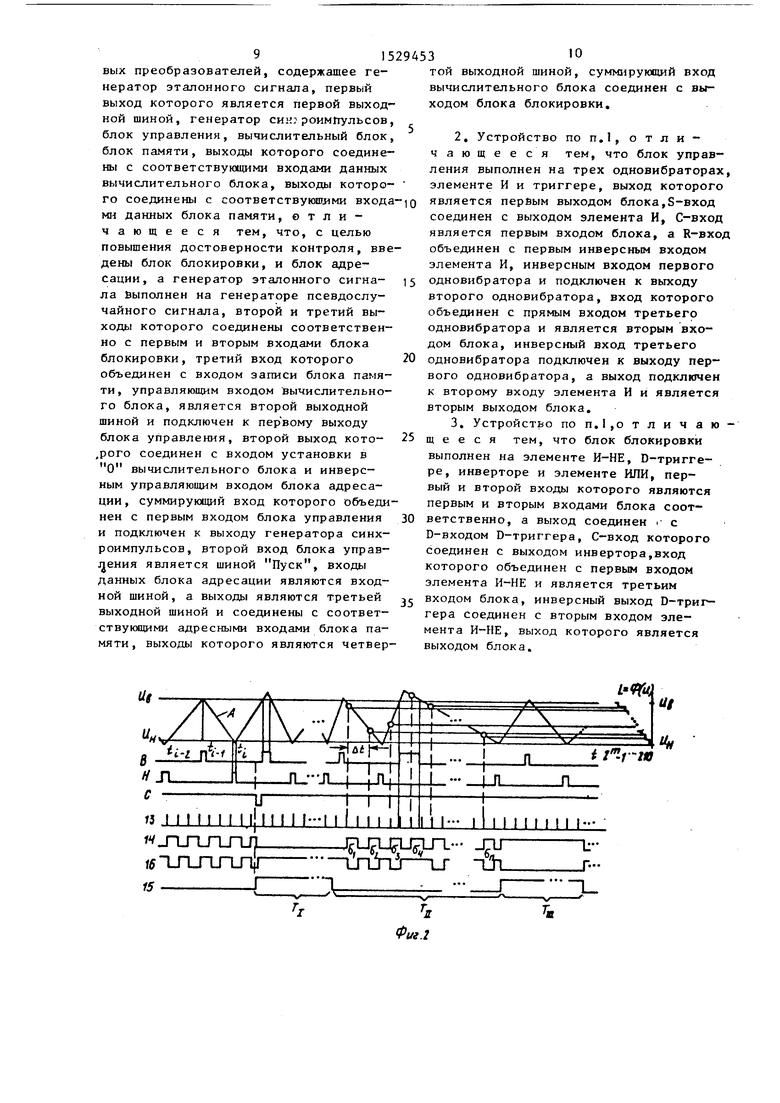

На фиг,1 приведена функциональная схема устройства для измерения динамической погрешности аналого-цифровых преобразователей; на фиг.2 - вре- менные диаграммы, иллюстрирующие работу устройства; на фиг.З - функциональная схема йарианта реализации блока управления; на фиг.4 - то же, блока блокировки.

Устройство (фиг,1) содержит генератор 1 псевдослучайного сигнала, выходная шина 2 которого является первой выходной шиной устройства, к которой подключается выход испытуемо- го АЦП 3, выходную шину 4 устройства являющуюся шиной Пуск, а также блок 5 управления, генератор 6 синхроимпульсов, блок 7 блокировки, блок 8 адресации, блок 9 памяти, вы- числительный блок 10, выходные шины 11 и 12 устройства.

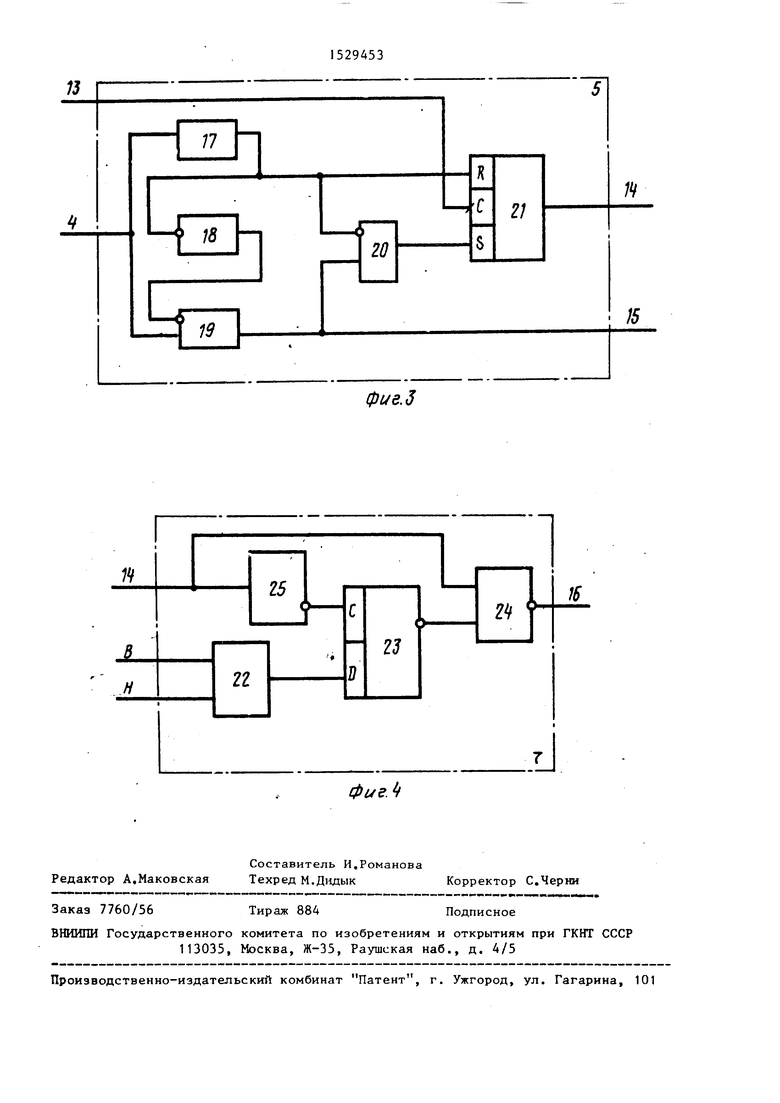

Кроме того, на фиг.1 обозначены вход 13 блока 5 управления, выходы 14 и 15 блока 5 управления, выход 16 блока 7 блокировки, выходы В и Н генератора 1 псевдослучайного сигнала. Блок 5 управления (фиг.З) содержит три одновибратора 17-19, элемент И 20, триггер 21.

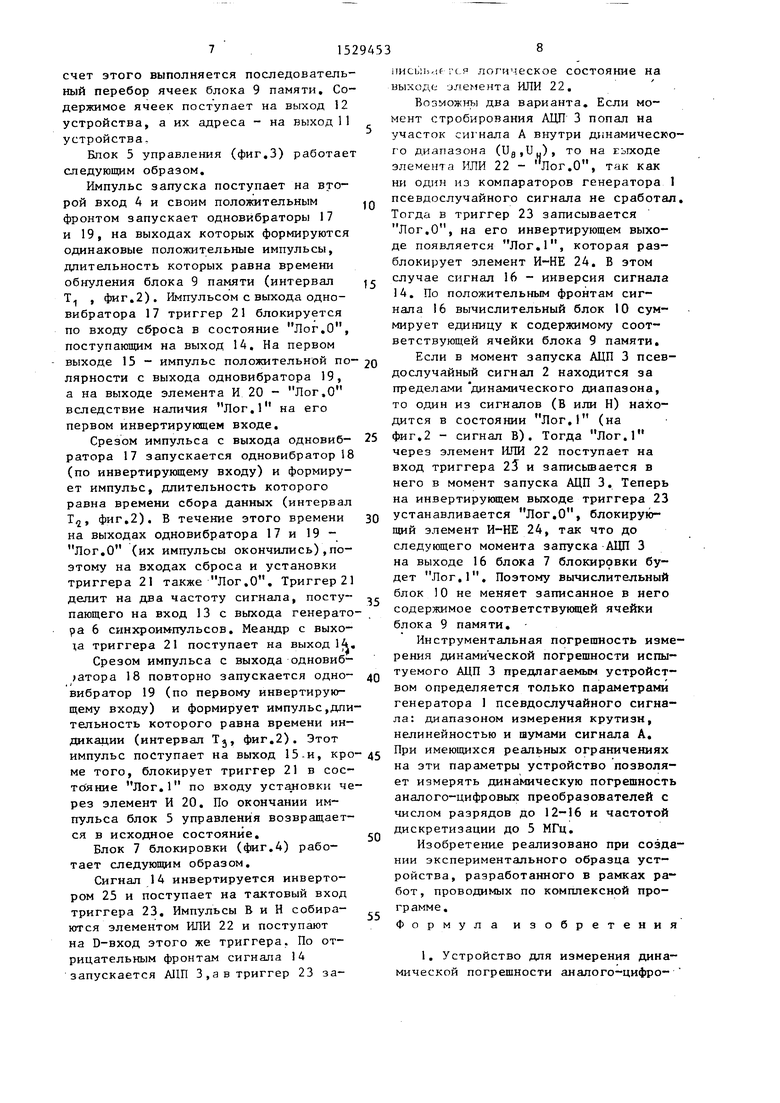

Блок 7 блокировки (фиг,4) содержит элемент ИЛИ 22, D-триГгер 23, элемент И-НЕ 24 и инвертор 25,

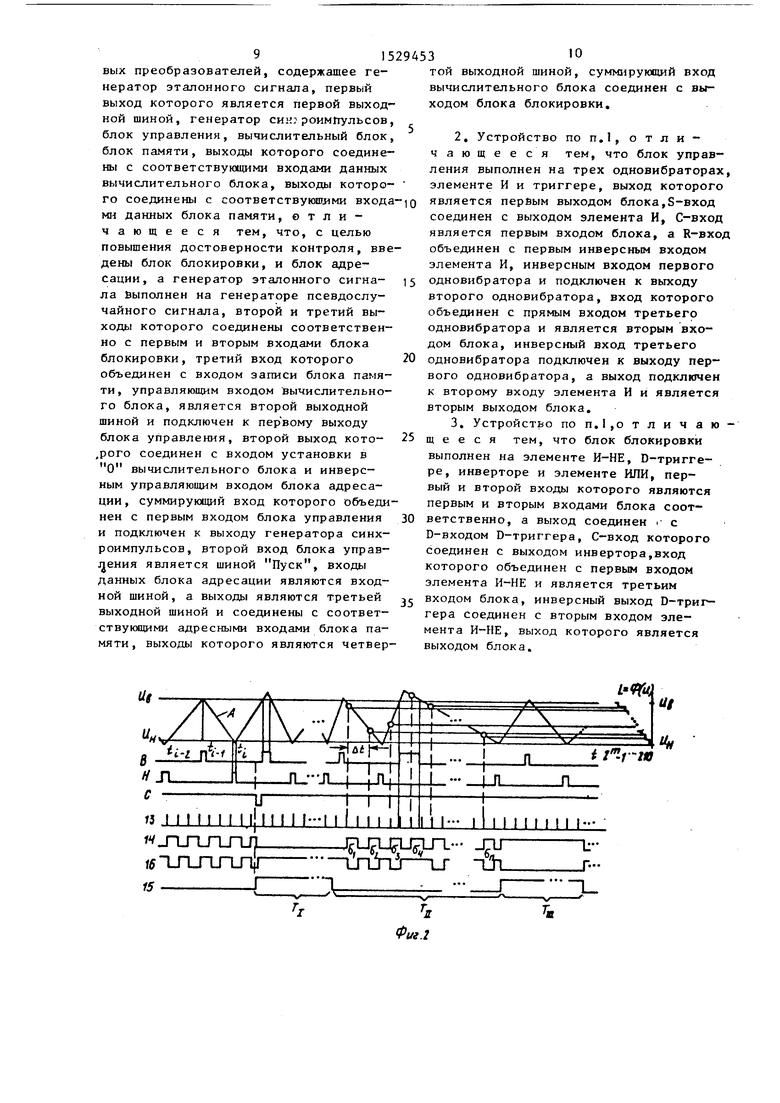

На фиг.2 показаны: А - линейно изменяющийся испытательный сигнал, подаваемый на вход испытуемого АЦП; Ug, U( -верхняя и нижняя соответственно границы диапазона преобразования испытуемого АЦП 3; 13 - импульсы на выходе генератора 6 синхро импульсов, обеспечивающие запуск испытуемого АЦП 3; t- i 2,1,0... моменты достижения сигналом А границ Ug и и„; t - период запуска испытуемого АЦП 3; обозначены вре- менные интервалы: Т, - обнуление блока 9 памяти; Т - сбор данных с испытуемого АЦП 3; Т - индикация полученных результатов; L Ф(и) - из 4tpcir.4 i кипнтующап характеристика испытуемого АДП 3; В - импульсы с выхода генератора 1 псевдослучайного сигнала при достижении сигналом А границы диапазона Ug; Н - импульсы с выхода Н генератора 1 псевдослучайного сигнала при достижении сигналом А границы диапазона 6.- моменты запуска АЦП 3, отстоящие один от другого на /jt; 4, 14-16 - сигналы на одноименных выходах блока 5 управления и блока 7 блокировки.

Длительности выходных импульсов одновибраторов 17 и 19 равны между собой и определяют длительности временных интервалов Т обнуления и Т считывания. Эти длительности должны превышать время перебора всех адресов блока 9 памяти при данной часто- те генератора 6 синхроимпульсов. Длительность выходного импульса одновибратора 18 равна временному интервалу Т-2 сбора данных, выбор которого описан Bbmie.

Устройство работает следующим образом.

В исходном состоянии на выходе генератора 1 псевдослучайного сигнала (фиг,1) формируется сигнал А. Сигнал А повторяется циклически с периодом Т - интервалом времени накопления данных. Длина периода повторения задается и зависит от допустимой ошибки измерения динамической погрешности АЦП, Пусть допустимая ошибка измерения составляет величину € от разрешающей способности (), испытуемого АЦП, Тогда за время сбора ,.;- данных

Т, ()/

на основании теоремы Муавра-Лапласа будет определена динамическая погрешность АЦП с ошибкой, не превосходящей , с доверительной вероятностью 99,73%, Так, для 12-разрядного АЦП с временем преобразования 4t 1 мкс и допустимой ошибкой 0,1 от величины младшепо значащего разряда длительность временного интервала Т будет 4 с.

Обнуление блока 9 памяти предшествует сбору данных и реализуется на интервале Т, тем, что на вход записи- считывания блока 9 памяти поступает сигнал записи (например,Лог, О) второго выхода 14 блока 5 управления на вход данных поступает Лог,0 с вы-

хода вычислительного блока 10 (сигнал установки нуля с первого выхода 15 блока 5 управления) и выполняется последовательный гг ребор всех адресов блока 9 памяти. Для этого блок 8 адресации переводится в режим счета (Лог,1 с первого выхода 15 блока 5 управления) импульсов с выхо

да генератора 6 синхроимпульсов. Пос- д зования на ийтервале Т. В результате

20

25

30

ле, по крайней мере, однократного перебора всех адресов устройство переходит от обнулению к сбору данных (интервал TI).

Сбор данных заключается в следующем.

На втором выходе 14 блока 5 управления появляется сигнал с частотой, которая вдвое ниже частоты генератора 6 синхроимпульсов. По его фронтам испытуемый АЦП 3 выполняет преобразование псевдослучайного испытательного сигнала А. Коды с выхода АЦП 3 поступают на вход данных блока 8 адресации.

Блок 8 адресации переводится в режим регистра (Лог.О с первого выхода 15), при этом код на его выходе соответствует коду очередного отсчета на выходе испытуемого АЦП 3, Затем он поступает на адресный вход блока 9 памяти.

На выходе блока 9 памяти появляется содержимое ячейки с адресом, совпадающим с кодом очередного отсчета с (после обнуления в ячейке хранится нуль}. Содержимое ячейки поступает на вход данных вычислительного блока 10 и в течение первой половины интервала преобразования записывается дО в вычислительный блок 10 благодаря сигналу Лог.1 на входе управления этого блока. По отрицательному фронту этого управляющего сигнала вычислительный блок 10 переходит по по- дЗ ложительному фронту сигнала 15 в режим счета и к записанному в него содержимому ячейки прибавляется единица. Новое значение поступает на вход данных блока 9 памяти, в который и записывается по тому же адресу благодаря наличию сигнала записи (Лог.О) на входе записи - считывания во второй половине интервала t преобразования.

В процессе сбора данных возможна ситуация, когда запуск АЦП 3 приходится на интервал времени, в течение которого сигнал А находится вне Диав блоке 9 памяти будут накоплены данные, характеризующие динамическую погрешность АЦП, а именно: значение в i-й ячейке блока 9 памяти в конце Т 15 прямо пропорционально действительной ширине i-ro кванта характеристики преобразования L Ф (U) (нафиг.2 ) Так как на вход испытуемого АЦП поступает линейно изменяющийся сигнал А, его амплитудные значения.распределе50

55

ны равномерно, и, следовательно. При идеальной характеристике L Ф(и) АЦП 3 все значения, зафиксированные в блоке 9 памяти, должны совпадать между собой с точностью до заданной допустимой методической ошибки и

- т

быть равными величине Т « ( 1 ,, где 1 - содержимое i-й яче йки блока 9 памяти. Отношение л Ij/ будет характеризовать определяемую динамическую погрешность испытуемого АЦП 3. Задавая 10 , S 1,2,..., получим, что содержимое ячеек блока 9 памяти представляет собой непосредственно с учетом расположения десятичной запятой

-1S-I

4 1,10

Чем меньше динамическая погрешность испытуемого АЦП 3, тем ближе й к единице.

Индикация собранных данных на временном интервале Т з сводится к последовательному выводу содержимого всех ячеек блока 9 памяти. Она реализуется тем, что на вход записи - считывания блока 9 памяти поступает сигнал (Лог.1) считывания с выхода 14 блока 5 управления, вычислительный блок 10 заблокирован по входу сброса в состоянии нуля на его выходе, блок 8 адресации переведен в режим счета сигналом (Лог,1) с первого выхода 15 блока 5 управления. Блок 8 адресации считывает импульсы с выхода генератора 6 синхроимпульсов, Нату-. ральный ряд чисел в двоичном коде поступает с выхода блока 8 адре(:ации на адресный вход блока 9 памяти. За

пазона преобразования (U ,Uj) ( d на фиг.2). Благодаря действию блока 7 блокировки к содержимому ячейки блока 9 памяти, соответствующей данному отсчету АЦП 3, не будет добавлена единица.

Описанная процедура повторяется в течение каждого интервала 4t преобра-

зования на ийтервале Т. В результате

в блоке 9 памяти будут накоплены данные, характеризующие динамическую погрешность АЦП, а именно: значение в i-й ячейке блока 9 памяти в конце Т прямо пропорционально действительной ширине i-ro кванта характеристики преобразования L Ф (U) (нафиг.2 ) Так как на вход испытуемого АЦП поступает линейно изменяющийся сигнал А, его амплитудные значения.распределе5

0

с О З

0

5

ны равномерно, и, следовательно. При идеальной характеристике L Ф(и) АЦП 3 все значения, зафиксированные в блоке 9 памяти, должны совпадать между собой с точностью до заданной допустимой методической ошибки и

- т

быть равными величине Т « ( 1 ,, где 1 - содержимое i-й яче йки блока 9 памяти. Отношение л Ij/ будет характеризовать определяемую динамическую погрешность испытуемого АЦП 3. Задавая 10 , S 1,2,..., получим, что содержимое ячеек блока 9 памяти представляет собой непосредственно с учетом расположения десятичной запятой

-1S-I

4 1,10

Чем меньше динамическая погрешность испытуемого АЦП 3, тем ближе й к единице.

Индикация собранных данных на временном интервале Т з сводится к последовательному выводу содержимого всех ячеек блока 9 памяти. Она реализуется тем, что на вход записи - считывания блока 9 памяти поступает сигнал (Лог.1) считывания с выхода 14 блока 5 управления, вычислительный блок 10 заблокирован по входу сброса в состоянии нуля на его выходе, блок 8 адресации переведен в режим счета сигналом (Лог,1) с первого выхода 15 блока 5 управления. Блок 8 адресации считывает импульсы с выхода генератора 6 синхроимпульсов, Нату-. ральный ряд чисел в двоичном коде поступает с выхода блока 8 адре(:ации на адресный вход блока 9 памяти. За

счет этого выполняется последовательный перебор ячеек блока 9 памяти. Содержимое ячеек поступает на выход 12 устройства, а их адреса - на выход 11 устройства.

Блок 5 управления (фиг.З) работает следующим образом.

Импульс запуска поступает на второй вход 4 и своим положительным фронтом запускает одновйбраторы 17 и 19, на выходах которых формируются одинаковые положительные импульсы, длительность которых равна времени обнуления блока 9 памяти (интервал Т , фиг.2). Импульсом с выхода одно- вибратора 17 триггер 21 блокируется по входу сброса в состояние Лог.О, поступающим на выход 14. На первом выходе 15 - импульс положительной по- лярности с выхода одновибратора 19, а на выходе элемента И 20 - Лог.О вследствие наличия Лог.1 на его первом инвертирующем входе.

Срезом импульса с выхода одновиб- ратора 17 запускается одновибратор 18 (по инвертирующему входу) и формирует импульс, длительность которого равна времени сбора данных (интервал Т, фиг.2). В течение этого времени на выходах одновибратора 17 и 19 - Лог.О (их импульсы окончились),поэтому на входах сброса и установки триггера 21 также Лог.О. Триггер 21 делит на два частоту сигнала, посту- пающего на вход 13 с выхода генератора 6 синхроим-пульсов. Меандр с выхо- ;а триггера 21 поступает на выход 14,

Срезом импульса с выхода одновибратора 18 повторно запускается одно- вибратор 19 (по первому инвертирующему входу) и формирует импульс,дпи тельность которого равна времени индикации (интервал Tj, фиг.2). Этот импульс поступает на выход 15-и, кро ме того, блокирует триггер 21 в сос- Т(5яние Лог.1 по входу установки через элемент И 20. По окончании импульса блок 5 управления возвращается в исходное состояние.

Блок 7 блокировки (фиг.4) работает следующим образом.

Сигнал 14 инвертируется инвертором 25 и поступает на тактовый вход триггера 23. Импульсы В и Н собира- ются элементом ИЛИ 22 и поступают на D-вход этого же триггера. По отрицательным фронтам сигнала I4 запускается АЦП 3,а в триггер 23 заiiHCb b if ГС..Р логическое состояние на ныходе элемента ИЛИ 22.

Возможнъ два варианта. Если момент стробирования АЦП 3 попал на участок сигнала А внутри динамического диапазона (Ug,Uu), то на Еыходе элемента ИЛИ 22 - Лог.О, так как ни один из компараторов генератора псевдослучайного сигнала не сработал Тогда в триггер 23 записывается Лог.О, на его инвертирующем выходе появляется Лог.1, которая разблокирует элемент И-НЕ 24. В этом случае сигнал 16 - инверсия сигнала 14. По положительным фронтам сигнала 16 вычислительный блок 10 суммирует единицу к содержимому соответствующей ячейки блока 9 памяти.

Если в момент запуска АЦП 3 псевдослучайный сигнал 2 находится за пределами динамического диапазона, то один из сигналов (В или Н) находится в состоянии Лог.1 (на фиг.2 - сигнал В). Тогда Лог.1 через элемент ИЛИ 22 поступает на вход триггера 25 и записьшается в него в момент запуска АЦП 3. Теперь на инвертирующем выходе триггера 23 устанавливается Лог.О, блокирующий элемент И-НЕ 24, так что до следующего момента запуска АЦП 3 на выходе 16 блока 7 блокировки будет Лог.1. Поэтому вычислительный блок 10 не меняет записанное в него содержимое соответствующей ячейки блока 9 памяти.

Инструментальная погрешность изме рения динамической погрещности испытуемого АЦП 3 предлагаемым устройством определяется только параметрами генератора 1 псевдослучайного сигнала: диапазоном измерения крутизн, нелинейностью и шумами сигнала А. При имеющихся реальных ограничениях на эти параметры устройство позволяет измерять динамическую погрешность аналого-цифровых преобразователей с числом разрядов до 12-16 и частотой дискретизации до 5 МГц.

Изобретени.е реализовано при создании экспериментального образца устройства, разработанного в рамках работ, проводимых по комплексной программе. Формула изобретения

вых преобразователей, содержащее генератор эталонного сигнала, первый выход которого является первой выходной шиной, генератор син: роимГтульсов, блок управления, вычислительный блок, блок памяти, выходы которого соединены с соответствующими входами данных вычислительного блока, выходы которотой выходной шиной, суммируюций вход вычислительного блока соединен с выходом блока блокировки.

2, Устройство по п.I, о т л и - чающееся тем, что блок управления выполнен на трех одновибраторах, элементе И и триггере, выход которого го соединены с соответствуюшлми входа-ю является первым выходом блока,S-вход мн данных блока памяти, в т л и -соединен с выходом элемента И, С-вход

чающееся тем, что, с целью повышения достоверности контроля, введены блок блокировки, и блок адре15

сации, а генератор эталонного сигнала Выполнен на генераторе псевдослучайного сигнала, второй и третий выходы которого соединены соответственно с первым и вторым входами блока блокировки, третий вход которого объединен с входом записи блока памяти, управляющим входом вычислительного блока, является второй выходной шиной и подключен к пер вому выходу блока управления, второй выход кото- ,рого соединен с входом установки в О вычислительного блока и инверсным управляющим входом блока адресации, суммирующий вход которого объединен с первым входом блока управления 30 и подключен к выходу генератора синхроимпульсов, второй вход блока управ- JJeния является шиной Пуск, входы данных блока адресации являются входявляется первым входом блока, а R-вход объединен с первым инверсным входом элемента И, инверсным входом первого одновибратора и подключен к выходу второго одновибратора, вход которого объединен с прямым входом третьего одновибратора и является вторым входом блока, инверсный вход третьего 20 одновибратора подключен к выходу первого одновибратора, а выход подключен к второму входу элемента И и является вторым выходом блока.

3, Устройство по п.1,о т л и ч а ю - щ е е с я тем, что блок блокировки выполнен на элементе И-НЕ, D-тригге- ре, инверторе и элементе ИЛИ, первый и второй входы которого являются первым и вторым входами блока соответственно, а выход соединен г с D-входом D-триггера, С-вход которого соединен с выходом инвертора,вход которого объединен с первым входом элемента И-НЕ и является третьим

25

ной шиной, а выходы являются третьей входом блока, инверсный выход D-триг- выходной шиной и соединены с соответ- гера соединен с вторым входом элемента И-НЕ, выход которого является выходом блока.

ствующими адресными входами блока памяти, выходы которого являются четвертой выходной шиной, суммируюций вход вычислительного блока соединен с выходом блока блокировки.

5

0

является первым входом блока, а R-вход объединен с первым инверсным входом элемента И, инверсным входом первого одновибратора и подключен к выходу второго одновибратора, вход которого объединен с прямым входом третьего одновибратора и является вторым входом блока, инверсный вход третьего 0 одновибратора подключен к выходу первого одновибратора, а выход подключен к второму входу элемента И и является вторым выходом блока.

3, Устройство по п.1,о т л и ч а ю - щ е е с я тем, что блок блокировки выполнен на элементе И-НЕ, D-тригге- ре, инверторе и элементе ИЛИ, первый и второй входы которого являются первым и вторым входами блока соответственно, а выход соединен г с D-входом D-триггера, С-вход которого соединен с выходом инвертора,вход которого объединен с первым входом элемента И-НЕ и является третьим

5

фиг.З

| Способ измерения динамической погрешности аналого-цифровых преобразователей | 1985 |

|

SU1302431A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для снятия характеристик аналого-цифровых преобразователей | 1981 |

|

SU991600A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-12-15—Публикация

1987-07-22—Подача