Изобретение относится к электротехнике и может быть использовано для автоматического включения на параллельную работу синхронных генераторов.

Известен синхронизатор по авт. св. СССР № 126937, кл. Н 02 J 3/42, 1969, содержащий преобразователь угла сдвига фаз 6 синхронизируемых напряжений в импульсную последовательность, фильтр, предназначенный для выделения напряжения, пропорционального углу сдвига фаз д, измерительно-вычислительный блок, осуществляющий двойное дифференцирование напряжения на выходе фильтра с целью определения частоты ah и ускорения Јs скольжения и обеспечивающий построение расчетного угла сдвига фаз 5раСч и логический блок, вырабатывающий команду на включение генераторного выключателя, если текущая частота скольжения а)$ не превышает допустимого значения ОДдоп а

текущий угол сдвига фаз д становится равным расчетному драсч.

Основным недостатком данного устройства является низкая точность его работы, обусловленная последовательным включением фильтра и двух дифференцирующих операционных усилителей, Такая цепь всегда имеет на своем выходе большой уровень помех, поскольку первое дифференцирование отменяет операцию сглаживания, выполненную фильтром. В результате второе дифференцирование применяется фактически к исходной импульсной последовательности, что приводит к образованию больших сигналов помехи по переднему и заднему фронтам ее импульсов и снижает точность работы синхронизатора.

Наиболее близким по технической сущности к предлагаемому является синхронизатор с постоянным временем опережения по авт. ев, СССР № 940269, кл. Н 02 J 3/42, 1980. Этот синхронизатор содержит блок

VI

о

со

преобразования угла сдвига фаз синхронизируемых напряжений в импульсную последовательность, активный фильтр на базе трех операционных усилителей, два суммирующих операционных усилителя, образующих совместно с активным фильтром измерительно-вычислительный блок и логический блок. При этом блок преобразования, измерительно-вычислительный бл ок и логический блок включены между собой последовательно. °

Импульсная последовательность с выхода блока преобразования и активном фильтре, передаточная функция которого соответствует звену третьего порядка вида

W(p) -тЈ. (1)

а р3 + b р2 + с р + 1

преобразуется в напряжения на первом, второй и третьем выходах фильтра, которые пропорциональны, соответственно, ускорению скольжения Јs частоте скольжения а)$ и текущему углу сдвига фаз д. В суммирующих операционных усилителях на основе этих сигналов производится вычисление расчетных значений угла сдвига фаз и частоты скольжения (драсч , мьрасч) для известного времени срабатывания генераторного выключателя TBK/I в соответствии с формулами

5Расч 5 +

Јs ЕВКП .

ОДзрасч ftJs Ь ES Гвкл .

(2)

Выходные напряжения суммирующих операционных усилителей вместе с напряжениями, пропорциональными бДОп и о%ДОп подаются на логический блок, который проверяет выполнение условий

Орасч ддоп - Ј spac4 Ј08доп (3)

Если условие (3) выполняются, логический блок подает команду на включение генераторного выключателя.

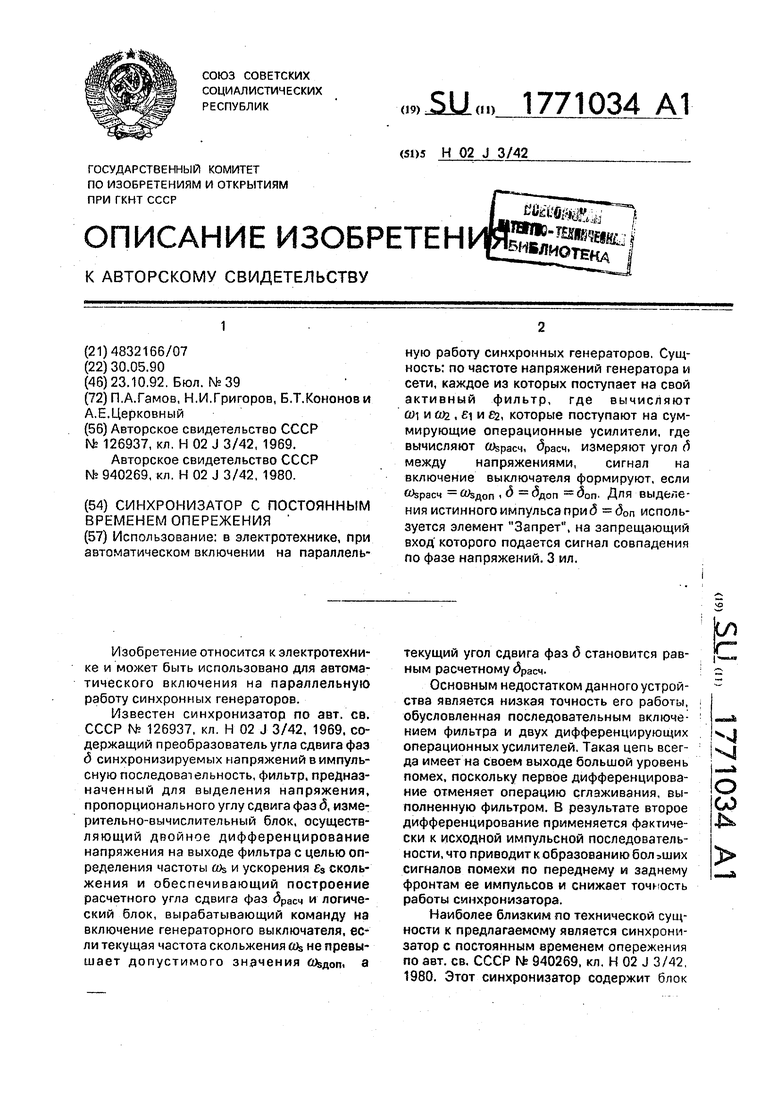

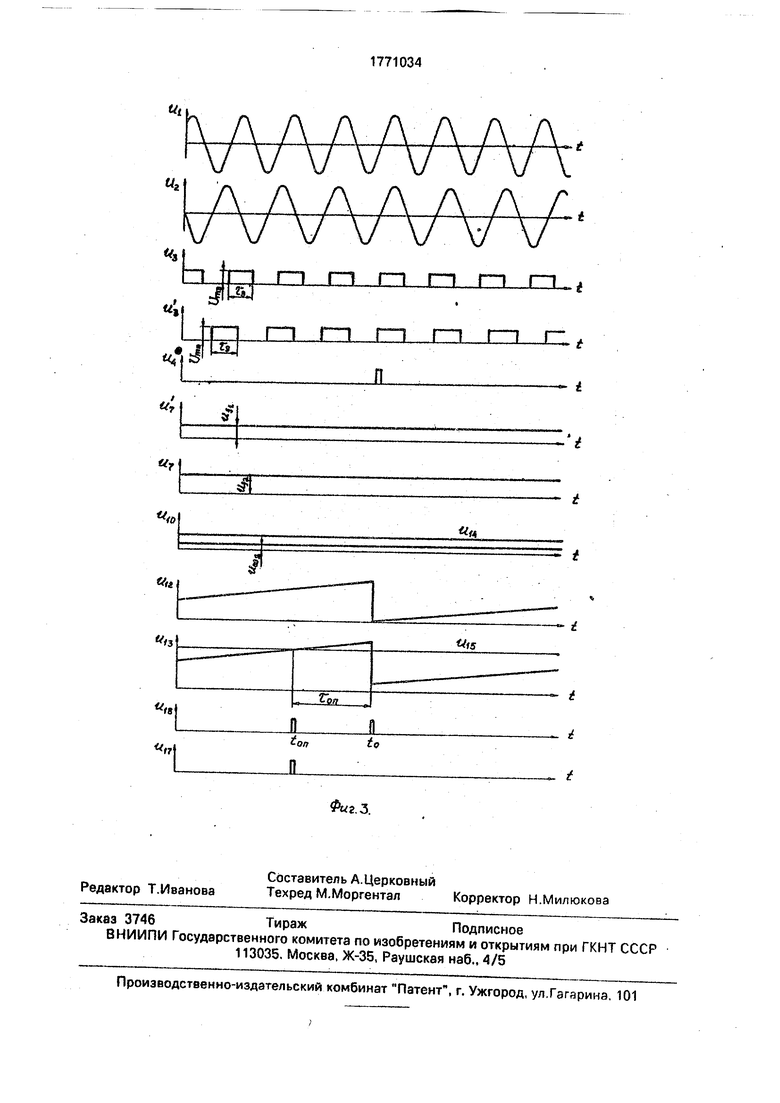

Основным недостатком прототипа является низкая точность его работы, обусловленная специфическими особенностями преобразования в активном фильтре импульсной последовательности в пропорциональное углу сдвига фаз напряжения при углах сдвига фаз равных 0 или 2л, Эта особенность поясняется временными диаграммами, приведенными на фиг. 1.

На фиг. 1 синусоиды синхронизируемых напряжений не показаны. Им соответствуют импульсные последовательности U1 иУа,

импульсы которых жестко привязаны по фазе к соответствующим синусоидам, а именно: импульсы формируются в моменты времени, когда аргументы синусоид принимают значения, кратные 2л. Импульсная последовательность Us - сигнал на одном из выходов триггера, являющегося выходным элементом блока преобразования угла сдвига фаз синхронизируемых напряжений

0 в импульсную последовательность.

Рабочие формулы (2) синхронизатора- прототипа составлены в предположении, что напряжение на третьем выходе активного фильтра, где оно пропорционально теку5 щему углу сдвига фаз, изменяется по линейному закону в соответствии с диаграммой U4. При этом скачок напряжения в момент времени tpaC4 соответствует совпадению входных напряжений по фазе,

0 то есть переходу текущего угла сдвига фаз д от 2л: к 0.

Фактический сигнал на третьем выходе активного фильтра изменяется во времени в соответствии с диаграммой Us. Поскольку

5 фильтр реагирует только на появление или исчезновение сигнала на его входе, то установление напряжения в ноль на его выходе произойдет в момент времени гфакт, когда во входной импульсной последовательности

0 скачком уменьшится длительность импульса. Установившееся значение на выходе фильтра будет достигнутое запаздыванием, заданным передаточной функцией (1). В результате фиксации момента перехода угла

5 д от 2л к 0 на выходе фильтра произойдет с ошибкой гош. При больших частотах скольжения CDs, когда период скольжения Ts мал, величины Гоши Ts оказываются соизмери- тельными, а построение расчетного угла

0 (Зрасч происходит в зоне тош. Это приводит к появлению ошибки в подаче команды на включение генераторного выключателя, то есть снижает точность работы синхронизатора прототипа.

5 Цель изобретения - повышение точности работы синхронизатора.

Поставленная цель достигается тем, что синхронизатор с постоянным временем опережения, содержащий два суммирую0

5

щих операционных усилителя, логический .блок, активный фильтр, состоящий из трех последовательно соединенных интегрирующих операционных усилителей, выходы каждого из которых подключены к трем входам первого усилителя, выходы второго и третьего усилителей являются, соответственно, первым и вторым выходами активного фильтра, первый выход которого подключен к прямому входу первого суммирующего усилителя, отличающийся тем, что с целью повышения точности дополнительно введены два формирователя эталонных по амплитуде и длительности импульсов, блок контроля совпадения напряжений по фазе, второй активный фильтр, функциональная схема которого идентична схеме первого активного фильтра, два суммирующих операционных усилителя, интегрирующий операционный усилитель и элемент Запрет, причем входы формирователей эталонных импульсов предназначены для подключения на синхронизируемые напряжения, выходы формирователей подключены, соответственно, к четвертым входам первых усилителей первого и второго активных фильтров, являющимся входами первого и второго активных фильтров, первый выход второго активного фильтра подключен к инверсному входу первого суммирующего усилителя, выход которого подключен к первому входу соответственно второго и третьего суммирующих усилителей, вторые выходы активных фильтров подключены, соответственно к прямому и инверсному входам четвертого суммирующего усилителя, выход которого через интегрирующий операционный усилитель подключен ктретьему входу третьего суммирующего усилителя и непосредственно - ко вторым входам, соответственно, второго и третьего суммирующих усилителей, выходы которых подключены, соответственно, к первому и второму входам логического блока, третий и четвертый входы которого предназначены для подключения, соответственно, к задат- чикэм величин о/здоп и (5ДОп, выход которого подключен к прямому входу элемента Запрет, выход которого является выходом синхронизатора, к запрещающему входу элемента Запрет и обнуляющему входу интегрирующего операционного усилителя подключен выход блока контроля совпадения напряжения по фазе, входы которого подключены, соответственно, к входам формирователей эталонных импульсов.

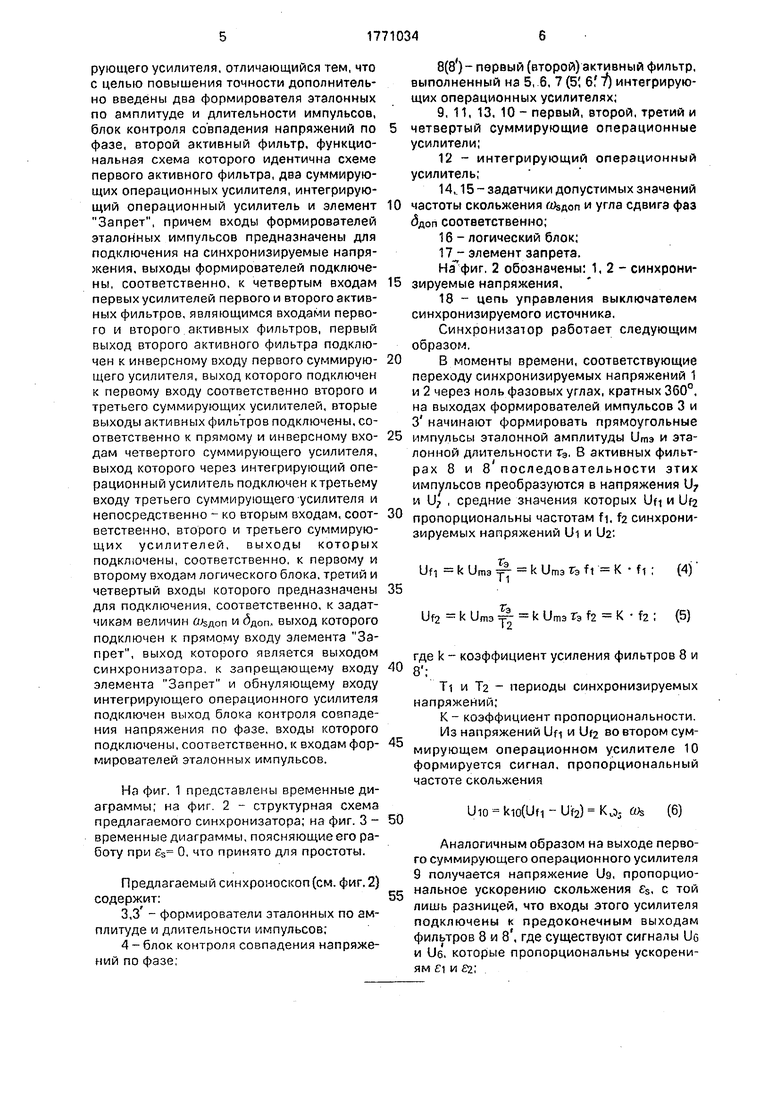

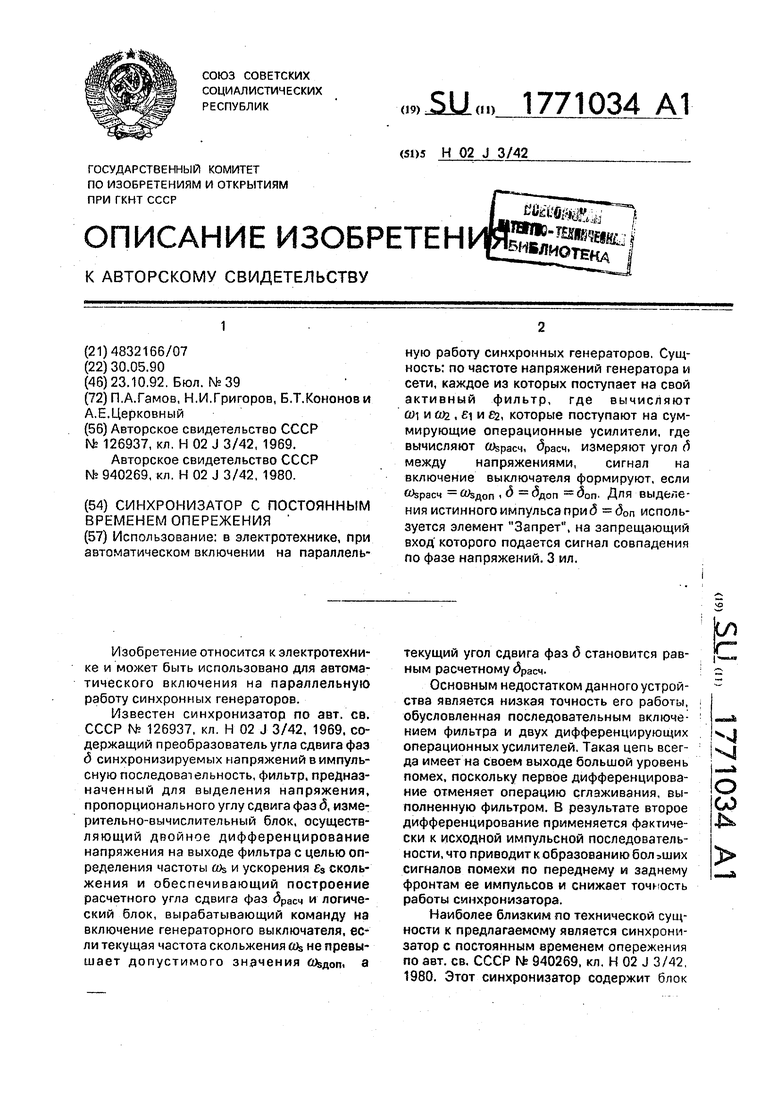

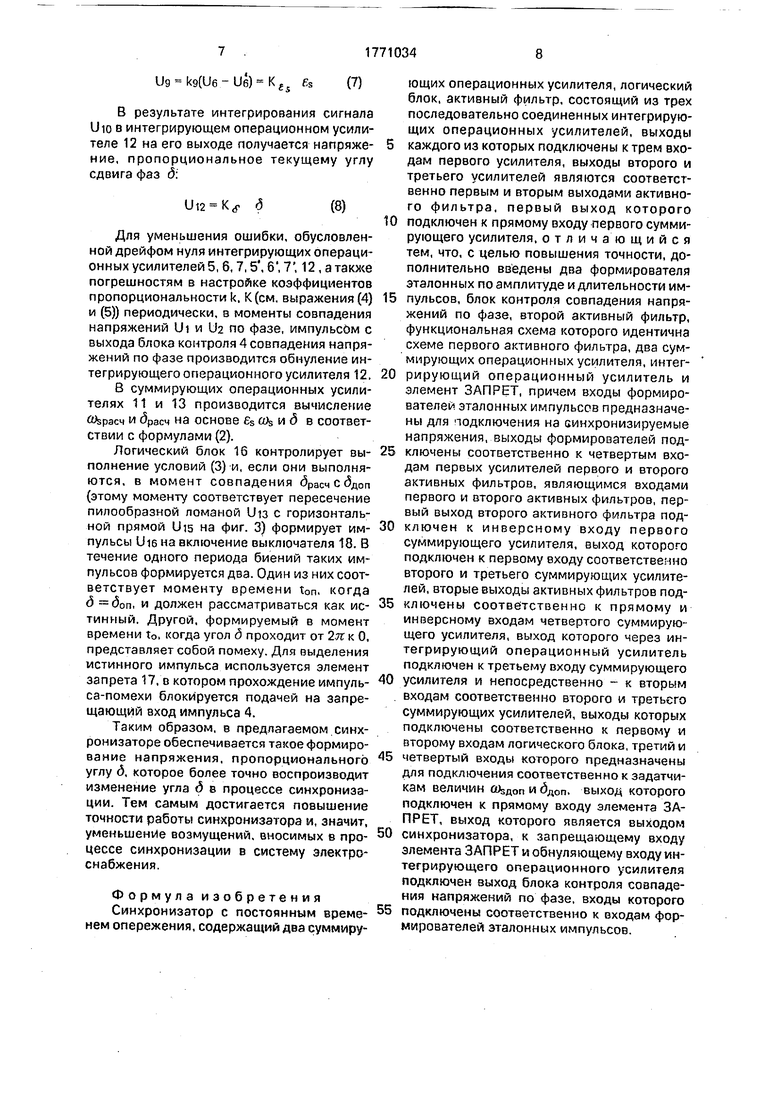

На фиг. 1 представлены временные диаграммы; на фиг. 2 - структурная схема предлагаемого синхронизатора; на фиг. 3 - временные диаграммы, поясняющие его работу при es 0, что принято для простоты.

Предлагаемы и синхроноскоп (см. фиг, 2} содержит:

3,3 - формирователи эталонных по амплитуде и длительности импульсов;

4-блок контроля совпадения напряжений по фазе;

8(8) - первый (второй) активный фильтр, выполненный на 5, 6, 7 (5; 6f i) интегрирующих операционных усилителях;

9, 11, 13, 10 - первый, второй, третий и четвертый суммирующие операционные усилители;

12 - интегрирующий операционный усилитель;

14,. 15 - задатчики допустимых значений частоты скольжения %доп и угла сдвига фаз 5Доп соответственно; 16 - логический блок; элемент запрета. НгГфиг. 2 обозначены: 1,2- синхрони- зируемые напряжения,

18 - цепь управления выключателем синхронизируемого источника,

Синхронизатор работает следующим образом,

в моменты времени, соответствующие переходу синхронизируемых напряжений 1 и 2 через ноль фазовых углах, кратных 360°, на выходах формирователей импульсов 3 и 3 начинают формировать прямоугольные импульсы эталонной амплитуды Uma и эталонной длительности гэ. В активных фильтрах 8 и 8 последовательности этих импульсов преобразуются в напряжения U7 и U , средние значения которых Ufi и Ufa пропорциональны частотам fi, fa синхронизируемых напряжений Ui и Ua:

35

Гэ

Uf, k Ums k Uma ГЭ f 1 К f 1 ; (4)

Гэ

Ufa k Umo k Ums ГЭ f2 К f2 I (5)

где k - коэффициент усиления фильтров 8 и 8.

Tj и Та - периоды синхронизируемых напряжений;

К - коэффициент пропорциональности.

Из напряжений Ufi и Ufa во втором суммирующем операционном усилителе 10 формируется сигнал, пропорциональный частоте скольжения

50

U ю - kio(Ufi - Ufa) Ю- «MS (6)

Аналогичным образом на выходе первого суммирующего операционного усилителя 9 получается напряжение Ug, пропорцио- нальное ускорению скольжения es- с той лишь разницей, что входы этого усилителя подключены к предоконечным выходам фильтров 8 и 8, где существуют сигналы UG и lie, которые пропорциональны ускорениям е и S2.;

Ug k9(Ue - Ue)

Кг5 Ј«

(7)

В результате интегрирования сигнала Uю в интегрирующем операционном усилителе 12 на его выходе получается напряжение, пропорциональное текущему углу сдвига фаз д:

Ui2 д

(8)

Для уменьшения ошибки, обусловленной дрейфом нуля интегрирующих операционных усилителей 5, б, 7,5, 6, 7, 12, а также погрешностям в настройке коэффициентов пропорциональности к. К (см. выражения (4) и (5)) периодически, в моменты совпадения напряжений Ui и Ua по фазе, импульсом с выхода блока контроля 4 совпадения напряжений по фазе производится обнуление интегрирующего операционного усилителя 12,

В суммирующих операционных усилителях 11 и 13 производится вычисление й зрасч и (5расч на основе es (DS и д в соответствии с формулами (2).

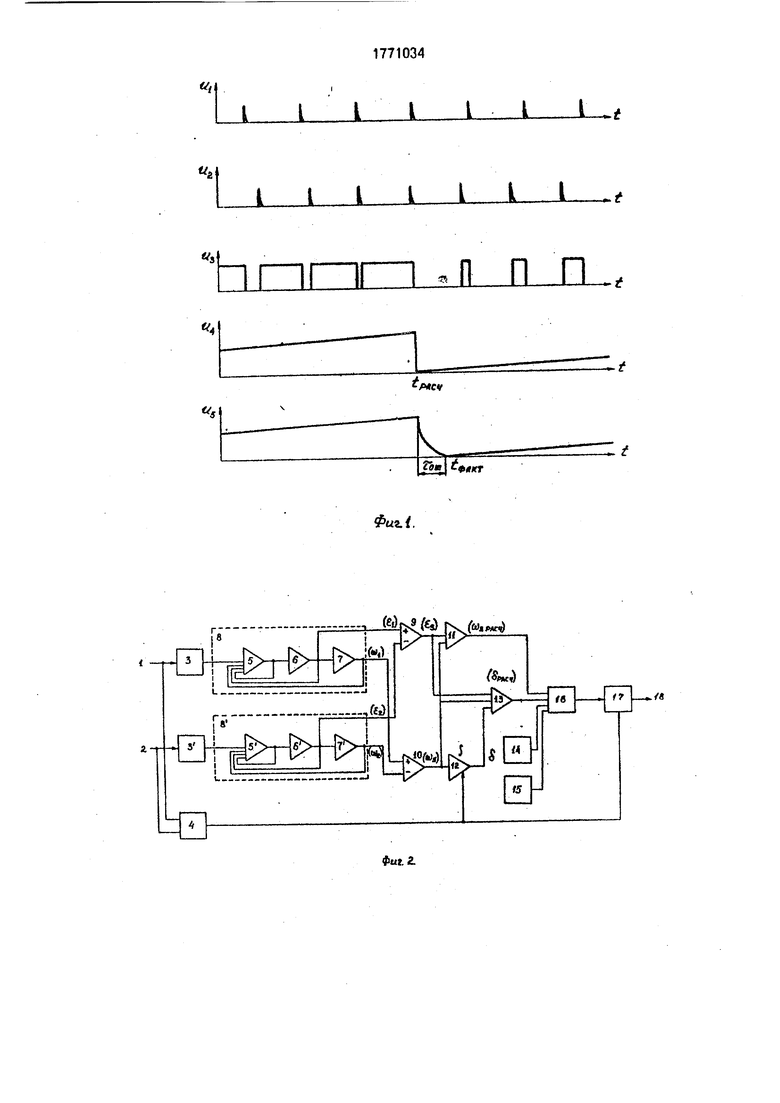

Логический блок 16 контролирует выполнение условий (3) и, если они выполняются, в момент совпадения 5расч с (Здоп (этому моменту соответствует пересечение пилообразной ломаной Uia с горизонтальной прямой U is на фиг. 3) формирует импульсы UIG на включение выключателя 18. В течение одного периода биений таких импульсов формируется два. Один из них соответствует моменту времени ton, когда д доп, и должен рассматриваться как истинный. Другой, формируемый в момент времени to, когда угол д проходит от 2тг к О, представляет собой помеху. Для выделения истинного импульса используется элемент запрета 17, в котором прохождение импульса-помехи блокируется подачей на запрещающий вход импульса 4.

Таким образом, в предлагаемом синхронизаторе обеспечивается такое формирование напряжения, пропорционального углу д, которое более точно воспроизводит изменение угла д в процессе синхронизации. Тем самым достигается повышение точности работы синхронизатора и, значит, уменьшение возмущений, вносимых в процессе синхронизации в систему электроснабжения.

Формула изобретения Синхронизатор с постоянным временем опережения, содержащий два суммирующих операционных усилителя, логический блок, активный фильтр, состоящий из трех последовательно соединенных интегрирующих операционных усилителей, выходы

каждого из которых подключены к трем входам первого усилителя, выходы второго и третьего усилителей являются соответственно первым и вторым выходами активного фильтра, первый выход которого

подключен к прямому входу первого суммирующего усилителя, отличающийся тем, что, с целью повышения точности, дополнительно введены два формирователя эталонных по амплитуде и длительности импульсов, блок контроля совпадения напряжений по фазе, второй активный фильтр, функциональная схема которого идентична схеме первого активного фильтра, два суммирующих операционных усилителя, интегрирующий операционный усилитель и элемент ЗАПРЕТ, причем входы формирователей эталонных импульсов предназначены для подключения на синхронизируемые напряжения, выходы формирователей подключены соответственно к четвертым входам первых усилителей первого и второго активных фильтров, являющимся входами первого и второго активных фильтров, первый выход второго активного фильтра подключей к инверсному входу первого суммирующего усилителя, выход которого подключен к первому входу соответственно второго и третьего суммирующих усилителей, вторые выходы активных фильтров подключены соответственно к прямому и инверсному входам четвертого суммирующего усилителя, выход которого через интегрирующий операционный усилитель подключен к третьему входу суммирующего

усилителя и непосредственно - к вторым входам соответственно второго и третьего суммирующих усилителей, выходы которых подключены соответственно к первому и второму входам логического блока, третий и

четвертый входы которого предназначены для подключения соответственно к задатчи- кам величин и дкоп. выход которого подключен к прямому входу элемента ЗАПРЕТ, выход которого является выходом

синхронизатора, к запрещающему входу элемента ЗАПРЕТ и обнуляющему входу интегрирующего операционного усилителя подключен выход блока контроля совпадения напряжений по фазе, входы которого

подключены соответственно к входам формирователей эталонных импульсов.

/

| название | год | авторы | номер документа |

|---|---|---|---|

| Синхронизатор с постоянным временем опережения | 1980 |

|

SU940269A1 |

| Синхронизатор с постоянным временем опережения | 1991 |

|

SU1775794A2 |

| Цифровой синхронизатор | 1978 |

|

SU736267A1 |

| Автоматический синхронизатор с постоянным временем опережения | 1979 |

|

SU888269A2 |

| Устройство для автоматической синхронизации синхронного генератора | 1980 |

|

SU875534A1 |

| Преобразователь угла поворота вала в код | 1983 |

|

SU1146803A1 |

| Устройство для уравнивания частот синхронных генераторов | 1979 |

|

SU788271A1 |

| Автоматический синхронизатор с постоянным временем опережения | 1977 |

|

SU705597A1 |

| Способ автоматического включения резервного питания потребителей с двигательной нагрузкой | 1985 |

|

SU1297169A1 |

| Устройство точной синхронизации | 1987 |

|

SU1561145A1 |

Использование: в электротехнике, при автоматическом включении на параллельную работу синхронных генераторов. Сущность: по частоте напряжений генератора и сети, каждое из которых поступает на свой активный фильтр, где вычисляют (о и G& , Ј1 и Ј2, которые поступают на суммирующие операционные усилители, где вычисляют Одзрасч, 5расч, измеряют угол д между напряжениями, сигнал на включение выключателя формируют, если «Узрасч %доп 5доп 5ОП, Для выделения истинного импульса при б д0п используется элемент Запрет, на запрещающий вход которого подается сигнал совпадения по фазе напряжений. 3 ил.

U U U

111111

)™ф

JlL

5л

и,

тип

m n n n n

«4

Ж

- t

| Автоматический синхронизатор с постоянным временем опережения | 1959 |

|

SU126937A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Синхронизатор с постоянным временем опережения | 1980 |

|

SU940269A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1992-10-23—Публикация

1990-05-30—Подача