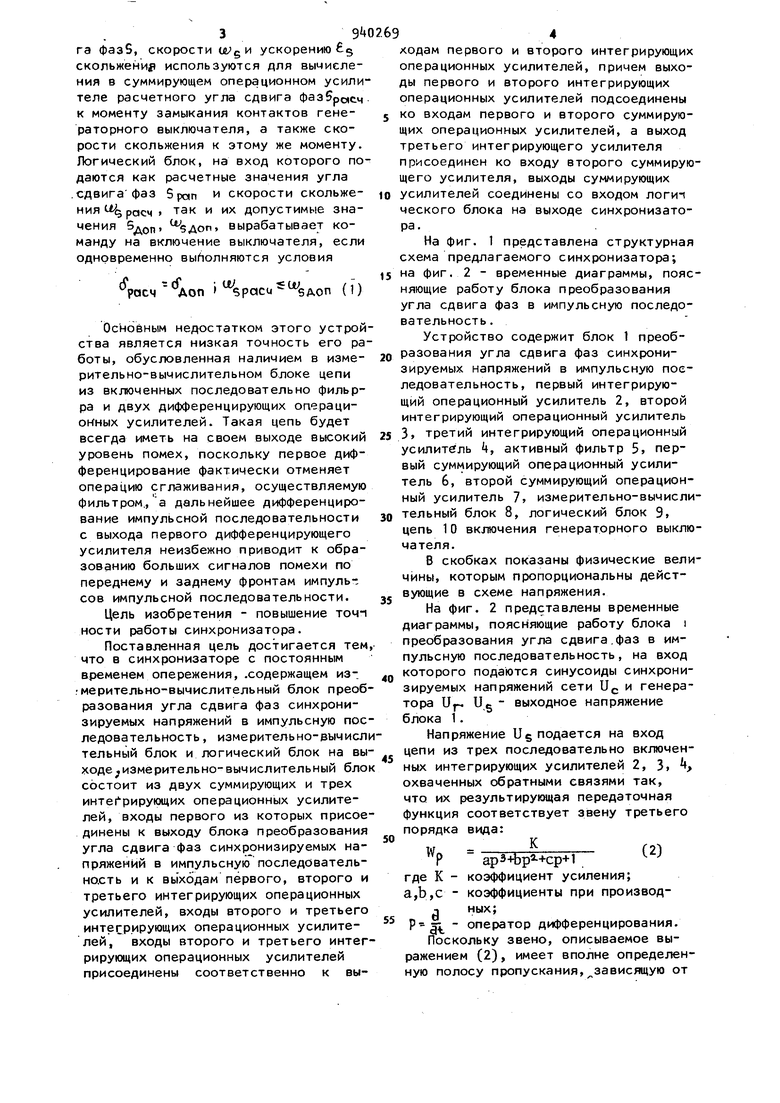

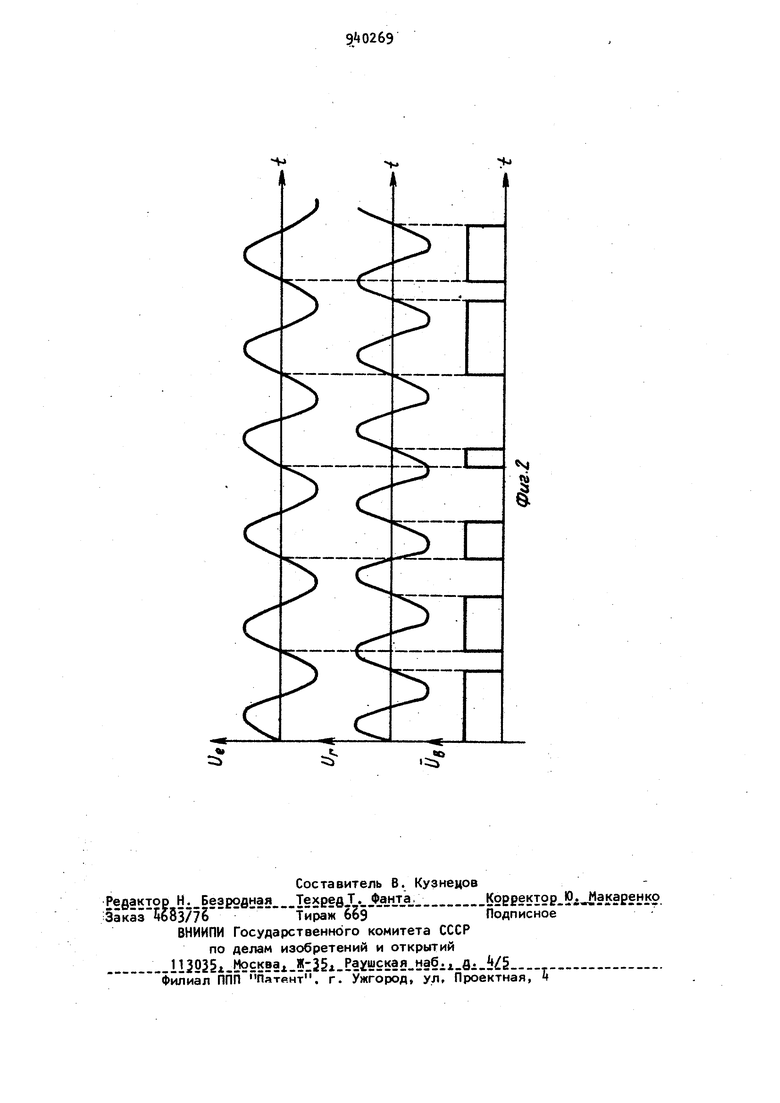

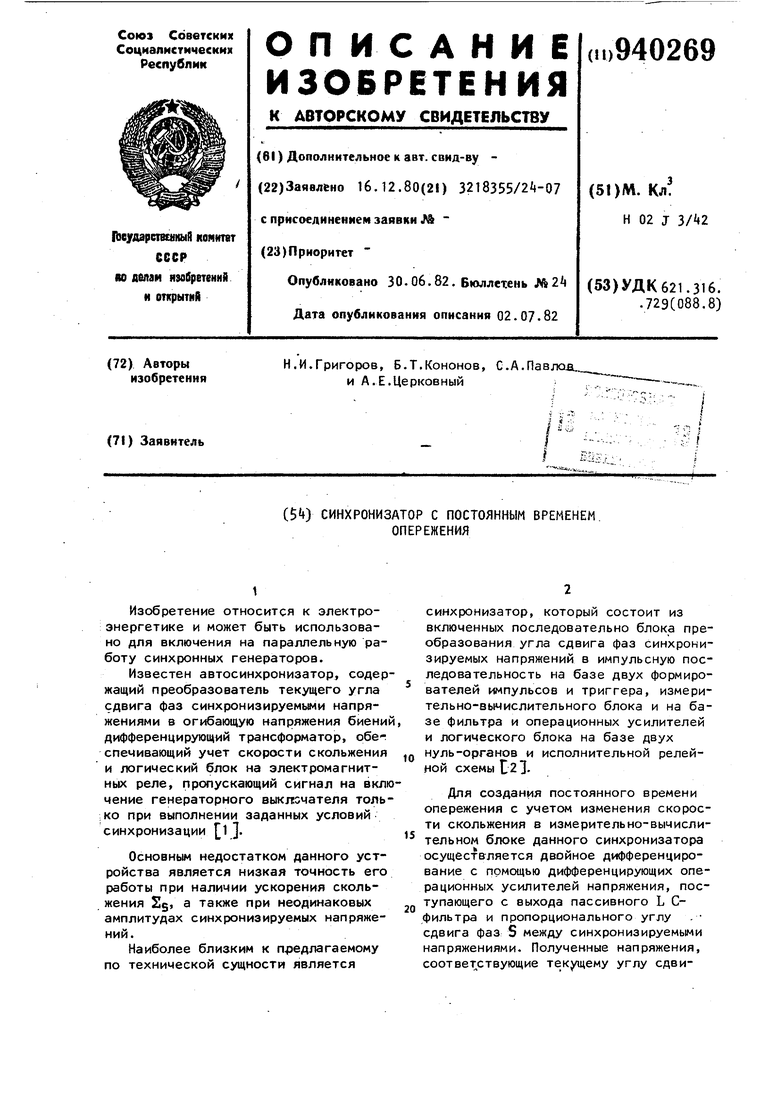

Изобретение относится к электроэнергетике и может быть использовано для включения на параллельную работу синхронных генераторов. Известен автосинхронизатор, содер жащий преобразователь текущего угла сдвига фаз синхронизируемьми напряжениями в огибающую напряжения биени дифференцирующий трансформатор, обег спечивающий учет скорости скольжения и логический блок на электромагнитных реле, пропускающий сигнал на вкл чение генераторного выключателя толь :ко при выполнении заданных условий синхронизации р . Основньи недостатком данного устройства является низкая точность его работы при наличии ускорения скольжения Sg а также при неодинаковых амплитудах синхронизируемых напряжений. Наиболее близким к п эедлагаемому по технической сущности является синхронизатор, который состоит из включенных последовательно блока преобразования угла сдвига фаз синхронизируемых напряжений в импульсную последовательность на базе двух формирователей импульсов и триггера, измерительно-вьнислительного блока и на базе фильтра и операционных усилителей и логического блока на базе двух нуль-органов и исполнительной релейной схемы Г23. Для создания постоянного времени опережения с учетом изменения скорости скольжения в измерительно-вычислительном блоке данного синхронизатора осуществляется двойное дифференцирование с помощью дифференцирующих операционных усилителей напряжения, поступающего с выхода пассивного L Сфильтра и пропорционального углу сдвига фаз S между синхронизируемыми напряжениями. Полученные напряжения, соответ ствующие текущему углу сдвига фаз5, скорости ускорению вд скольженир используются для вычисления в суммирующем операционном усили теле расчетного угла сдвига фаз5ро|сч к моменту замыкания контактов генераторного выключателя, а также скорости скольжения к этому же моменту. Логический блок, на вход которого по даются как расчетные значения угла .сдвигафаз Span и скорости скольжения ut расч , так и их допустимые значения 5доп , вырабатывает команду на включение выключателя, если одновременно выполняются условия л tf %pc cu sAoп расч АОП Основным недостатком этого устрой ства является низкая точность его ра боты, обусловленная наличием в измерительно-вычислительном б.локе цепи из включенных последовательно фильрра и двух дифференцирующих операционных усилителей. Такая цепь будет всегда иметь на своем выходе высокий уровень помех, поскольку первое дифференцирование фактически отменяет операцию сглаживания, осуществляемую фильтром., а дальнейшее дифференцирование импульсной последовательности с выхода первого дифференцирующего усилителя неизбежно приводит к образованию больших сигналов помехи по переднему и заднему фронтам импуль-сов импульсной последовательности. Цель изобретения - повышение точ1 ности работы синхронизатора. Поставленная цель достигается тем что в синхронизаторе с постоянным временем опережения, .содержащем из;мерительно-вычислительный блок преоб разования угла сдвига фаз синхронизируемых напряжений в импульсную пос ледовательность , измерительно-вычисл тельный блок и логический блок на вы ходе изме ритель но-выч исл итель ный бло состоит из двух суммирующих и трех инте рирующих операционных усилителей, входы первого из которых присое динены к выходу блока преобразования угла сдвига фаз синхронизируемых напряжений в импульсную последовательность и к вь|х6дам первого, второго и третьего интегрирующих операционных усилителей, входы второго и третьего интегрирующих операционных усилителей, входы второго и третьего интег рирующих операционных усилителей присоединены соответственно к выходам первого и второго интегрирующих операционных усилителей, причем выходы первого и второго интегрирующих операционных усилителей подсоединены ко входам первого и второго суммирующих операционных усилителей, а выход третьего интегрирующего усилителя присоединен ко входу второго суммирующего усилителя, выходы суммирующих усилителей соединены со входом логич ческого блока на выходе синхронизатора. На фиг. 1 представлена структурная схема предлагаемого синхронизатора; на фиг. 2 - временные диаграммы, поясняющие работу блока преобразования угла сдвига фаз в импульсную последовательность. Устройство содержит блок 1 преобразования угла сдвига фаз синхронизируемых напряжений в импульсную последовательность, первый интегрирующий операционный усилитель 2, второй интегрирующий операционный усилитель 3, третий интегрирующий операционный усилитель k, активный фильтр 5 первый суммирующий операционный усилитель 6, второй суммирующий операционный усилитель 7 измерительно-вычислительный блок 8, логический блок 9, цепь 10 включения генераторного выключателя. В скобках показаны физические величины, которым пропорциональны действующие в схеме напряжения. На фиг. 2 представлены временные диаграммы, поясняющие работу блока i преобразования угла сдвига,фаз в импульсную последовательность, на вход которого подаются синусоиды синхронизируемых напряжений сети Uj. и генератора Up Ug - выходное напряжение блока 1. Напряжение Ug подается на вход цепи из трех последовательно включенных интегрирующих усилителей 2, 3, Ч охваченных обратными связями так, что их результирующая передаточная функция соответствует звену третьего порядка вида: ap +bpi+cp+l где К - коэффициент усиления; а,Ь,с - коэффициенты при производ ных; оператор дифференцирования. Поскольку звено, описываемое выражением (2), имеет вполне определенную полосу пропускания,зависящую от выбора коэффициентовй,b ,с , его мож но рассматривать как активный фильтр Напряжение Da на выходе фильтра пропорционально текущему углу сдвига фаз Е между синхронизируемыми напряжениями Ug и и. Поскольку напряжелие Ug является одновременно выходным напряжением третьего интегрирующ го операционного усилителя, то это значит, что на вход данного усилителя с выхода второго интегрирующего усилителя поступает напряжение Uj , пропорциональное скорости скольжения Ijtj,. Рассуждая аналогично, получаем, что на вход второго интегрирующего усилителя поступает напряжение Ugg, пропорциональное ускорению скольжения 6,5В суммирующих усилителях производится вычисление S и WJ р по формуламс 4.г P«cM- 4t,,,. %ac4% Mev/i Здесь t - время вклочения генераторного выклочателя. Выходное напряжение суммирующих операционных усилителей вместе с напряжениями, пропорциональными 5доп MU/gAQf,, подаются на входы логическо го блока 9. реализующего условие (1) Все блоки синхронизатора могут быть выполнены на базе интегральных микросхем любой серии, содержащей в своем составе операционные усилители триггеры и логические элементы И-НЕ, ИЛИ-НЕ. Предлагаемый синхронизатор учитыв ет как скорость, так и ускорение ско жения без использования дифференци- рующих устройств и потому выгодно от личает по точности от известных устройств . Формула изобретения Синхронизатор с постоянным време-i нем опережения, содержащий блок преобразования угла сдвига фаз синхронизируемых напряжений в импульсную последовательность, измерительно-вычислительный блок и логический блок на вы ходе синхронизатора, отличающийся тем, что, с целью повышения точности работы, измерительно- вычислительный блок состоит из двух суммирующих и трех интегрирующих операционных усилителей, входы первого из которых присоединены к входу блока преобразования угла сдвига фаз синхронизируемых напряжений в импульсную последовательность и к выходам первого, второго и третьего интегрирующих операционных усилителей, входы второго и третьего интегрирующих операционных усилителей присоединены соответственно к выходам первого и второго интегрирующх операционных усилителей, причем выходы первого и второго интегрирующих операционных усилителей соединены .с входами первого и второго суммирующих операционных усилителей, а выход третьего интегрирующего усилителя присоединен к входу второго суммирующего усилителя, выходы суммирующих усилителей соединены с входом логического блока. Источники информации, принятые во внимание при экспертизе 1.Барзам А. Б. Системная автоматика. М. , Энергия, 1964, с.170-1792.Авторское свидетельство СССР № 126937, кл. Н 02 У , 1969

| название | год | авторы | номер документа |

|---|---|---|---|

| Синхронизатор с постоянным временем опережения | 1990 |

|

SU1771034A1 |

| Синхронизатор с постоянным временем опережения | 1991 |

|

SU1775794A2 |

| Устройство для автоматической синхронизации | 1982 |

|

SU1098067A1 |

| Устройство для автоматической синхронизации синхронного генератора | 1980 |

|

SU875534A1 |

| Устройство точной синхронизации | 1987 |

|

SU1561145A1 |

| Автоматический синхронизатор с постоянным временем опережения | 1979 |

|

SU888269A2 |

| Цифровой синхронизатор | 1978 |

|

SU736267A1 |

| Импульсный синхронизатор | 1979 |

|

SU862314A1 |

| Синхронизатор с постоянным временем опережения | 1985 |

|

SU1319166A2 |

| Способ автоматического включения резервного питания потребителей с двигательной нагрузкой | 1985 |

|

SU1297169A1 |

SftrfV.

Авторы

Даты

1982-06-30—Публикация

1980-12-16—Подача