1

Изобретение относится к-электроэнергетике и может быть использовано в энергосистемах для автоматического включения синхронных генераторов на параллельную работу,

Известно устройство дл.ч синхронизации синхронных генераторов,. содержащее формирователь импульсов, под- ключенный на напряжение генераторов, к выходу которого подключен блок контроля разности фаз частот напря.жений и выходной блок включения 1 .

В известном устройстве блок контроля разности фаз и частот состоит из счетчика разности фаз, дешифратора фиксированных значений разности фаз, счетчика разности частот,де шифратора фиксированного значения разности частот и cxeivbi антисовпадения на выходе. Синхронизатор батывает команду на включение выключателя генератора при уменьшении разности фаз синхронизируемых напряжений до фиксированного значения в случае, если частота скольжения меньше или равна допустимой. Известное устройство является, по существу, синхронизатором с постоянным углом опережения. Точность работы устройства зависит от того, насколько текущее значение частоты скольжения отличается от заданного. Чем больше это отличие, тем бо.пьше величина ошибки синхронизатора по уг.пу включения,

Цель изобретения - повышение точности во всем диапазоне допусти -ых частот скольжения.

Поставленная цель достигается

- тем, что в синхронизатор, содержащкй формирователи импу.пьсов, блок контроля разности частот и выходной блок включения, введены генератор и делитель высокочастотных импульсов, схема совпадений, блок включения и два идентичных блока сдвига фазы синхронизируемых напряжений, каждый из которых состоит из триггера, четырех логических схем И,

20 схемы запрета, счетчик постоянного интервала времени с дешифратором и реверсивный счетчик с деапифраторог, а в состав блока контроля разности частот включены логическая схема

25 ИЛИ, схема задержки и регистр разности частот с дешифратором. Входы формирователей импульсов подключены на напряжение сети и генератора соответственно, а их выхо.цы присоединены к счетным входам триггерог

блоков сдвига фазы напряжения сети к генератора, в каждом из блоков первый выход триггера присоединен к одному из входов первой и четвер™ той логических схем И, а второй выход - к одному из входов третьей логической схемы И и к установочным входам счетчика постоянного интервала времени и реверсивного счетчика. Другой вход первой логической схеь 1 И присоединен к выходу генератора высокочастотных импульсов, а ее выход - к, одному из входов второй логической схемы И и входу .cxeNM запрета, другой вход второй логической схемы И и запрещающий вход схемы запрета присоединены к выходу дешифратора счетчика постоянного интервала времени, выход схемы запрета присоединен к считывающему входу счетчика постоянного интервала времени, выход которого присоединен ко входу соответствующего дешифратора, а выход второй логической схемы И присоединен к суммирующему входу реверсивного счетчика, к вычитающему входу которого присоединен выход третьей логической схемы И, второй вход которой через делитель высокочастотных импульсов присоединен к выходу генератора высокочастотных импульсов. Один выход реверсивного счетчика присоединен ко второму входу четвертой логической схемы И, а его другой выход - ко входу соответствующего дешифратора, выход которого присоединен к одному из входов схемы совпадения и логической схемы ИЛИ блока контроля разности частот, вторые входы схемы совпа,цения и логической схемы ИЛИ присоединены к выходам дешифратора реверсивного счетчика второго блока сдвига фазы. Выход логической схеNttj ИЛИ через схему задержки присоединен к установочному входу регистра разности частот, суммирующий вход регистра присоединен к выходу четвертой логической схемы И блока сдвига фазы одного из синхронизируемых напряжений, а вычитающий вход регистра разности частот - к выходу четвертой логической схемы И второго блока сдвига фазы, выход регистра разности частот присоединен к одному из входов выходного блока включения, другой вход которого присоединен к выходу схемы совпадения.

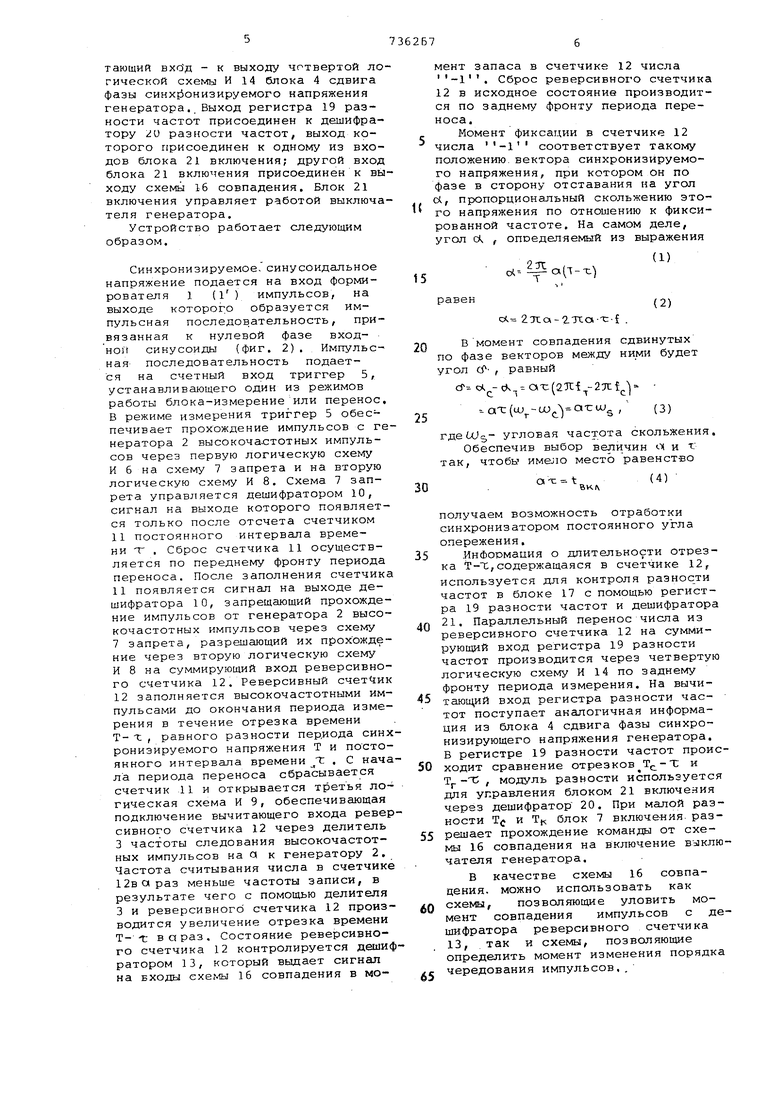

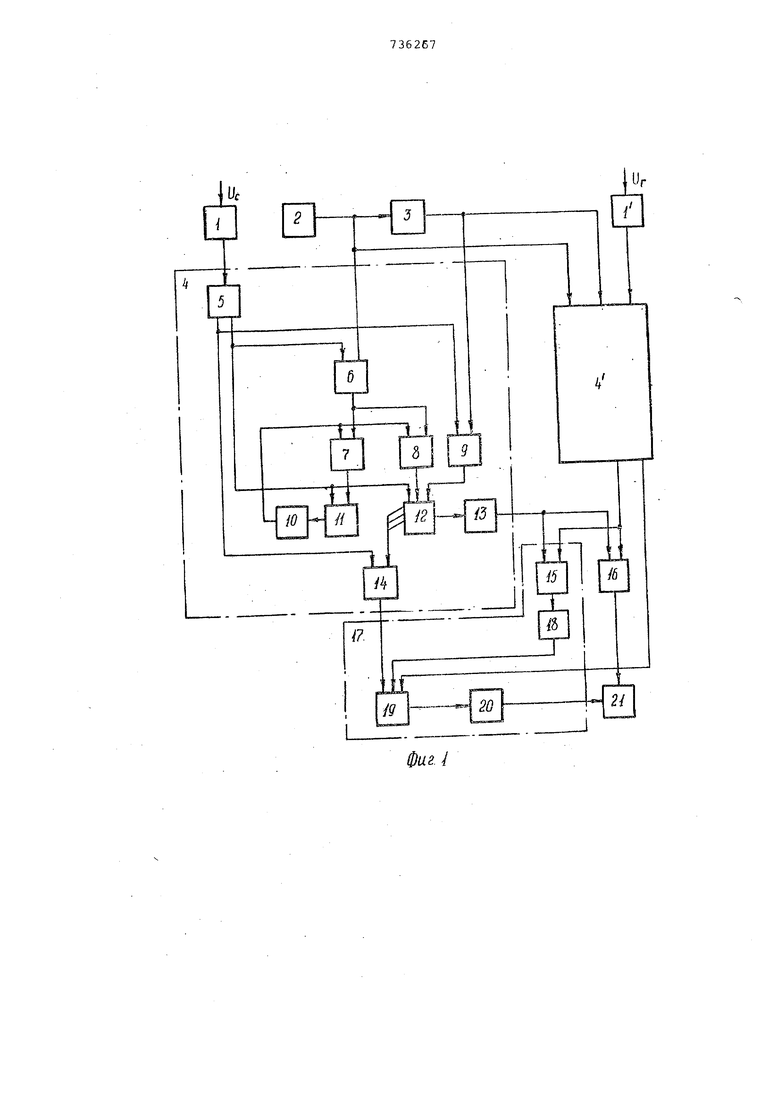

На фиг, 1 представлена структурная схема цифрового синхронизатора; на фиг. 2 - временные диаграммы, объясняющие его работу.

Устройство включает формирователи 1 и l имульсов, генератор 2 высокочастотных импульсов, делитель

3высокочастотных импульсов, блоки

4и 4 сдвига фазы синхронизируемых

напряжений, триггер 5, первую логическую схему И 6, схему 7 запрета, вторую логическую схему И 8,третью логическую схему И 9, дешифратор

10счетчика постоянного интервала времени, счетчик 11 постоянного интервала времени, реверсивный счетчик 12, дешифратор 13 реверсивного счетчика,четвертую логическую схему И 14, логическую схему ИЛИ 15, схему 16 совпадения, блок 17 контроля разности частот, схему 18 задержки, регистр 19 разнорти частот, дешифратор 20 разности частот, блок 21 включения.

Входы формирователей 1 и 1 присоединены к напряжению сети и генератора соответственно, а выходы к счетным входам триггеров блоков сдвига фазы синхронизируемых напряжений 4 и 4 соответственно, В каждом из блоков первый выход триггера 5 присоединен к одним из входов первой и четвертой логических схем И 6 и 14, а второй - к одному из входов третьей логической схемы И 9 и к установочным входам счетчика

11и 12,Выход генератора 2 высокочатотных импульсов присоединен к другому входу первой логической схемы

И б и через делитель 3 высокочастотных импульсов - к другому входу третьей логической схемы И 9, Выход первой логической схемы И 6 присоединен к одним из входов второй логической схемы И 8 и схемы 7 запрети. Выход схемы 7 запрета присоединен ко входу счетчика 11 постоянного интервала времени, выход которого присоединен к дешифратору 10, Выход дешифратора 10 присоединен к другому входу второй логической И 8 и к запрещающему входу схемы 7 запрета. Выход второй логической схемы И 8 присоединен к суммирующему входу реверсивного счетчика 12, вычитающий вход которого присоединен к выходу третьей логической схемы И 9, Первый выход реверсивного счетчика 12 присоединен к другому входу четвёртой логической схемы И 14, а второй выход - к дешифратору 13. Выход дешифратора 13 присоединен к одним из входов схемы 16 совпадения и логической схемы ИЛИ 15 блока 17 контроля разности частот, другие входы этих схем присоединены к выходу дешифратора 13 реверсивного счетчика блока 4 сдвига фазы синхронизируемого напряжения генератора. Выход логической схемы ИЛИ 15 через схему 18 задержки присоединен к установочному, входу регистра 19 разности частот, суммирующий вход которого присоединен к выходу четвертой логической схемы И 14 блока 4 сдвига фазы синхронизируемого напряжения сети, а вычитающий вход - к выходу чптвертой логической схемы И 14 блока 4 сдвига фазы синхЕ5онизируемого напряжения генератора. Выход регистра 19 разности частот присоединен к дешифратору 0 разности частот, выход которого присоединен к одному из входов блока 21 включения; другой вход блока 21 включения присоединен к выходу схемы 16 совпадения. Блок 21 включения управляет работой выключателя генератора.

Устройство работает следующим образом.

Синхронизируемое- синусоидальное напряжение подается на вход формирователя 1 ) импульсов, на выходе которог.о образуется импульсная последовательность, привязанная к нулевой фазе входHO1I синусоиды (фиг. 2) . Импульсная последовательность подается на счетный вход триггер 5, устанавливающего один из режимов работы блока-измерение или перенос, В режиме измерения триггер 5 обеспечивает прохождение импульсов с генератора 2 высокочастотных импульсов через первую логическую схему И б на схему 7 запрета и на вторую логическую схему И 8. Схема 7 запрета управляется дешифратором 10, сигнал на выходе которого появляется только после отсчета счетчиком 11 постоянного интервала времени т , Сброс счетчика 11 осуществляется по переднему фронту периода переноса. После заполнения счетчика

11появляется сигнал на выходе дешифратора 10, запрещающий прохождение импульсов от генератора 2 высокочастотных импульсов через схему

7 запрета, разрешающий их прохождение через вторую логическую схему И 8 на суммирующий вход реверсивного счетчика 12. Реверсивный

12заполняется высокочастотными импульсами до окончания периода измерения в течение отрезка времени

Т- т. , равного разности периода синхронизируемого напряжения Т и постоянного интервала времени Т . С начала периода переноса сбрасывается счетчик 11 и открывается третья логическая схема И 9, обеспечивающая подключение вычитающего входа реверсивного счетчика 12 через делитель 3 частоты следования высокочастотных импульсов на а к генератору 2, Частота считывания числа в счетчике 12вараз меньше частоты записи, в результате чего с помощью делителя 3 и реверсивного) счетчика 12 производится увеличение отрезка времени Т- -с в а раз . Состояние реверсивного счетчика 12 контролируется дешифратором 13, который выдает сигнал на входы схемы 16 совпадения в момент запаса в счетчике 12 числа . Сброс реверсивного счетчика 12 в исходное состояние производится по зaднe тy фронту периода переноса,

- Момент фиксации в счетчике 12 числа -1 соответствует такому положению, вектора синхронизируемого напряжения, при котором он по фазе в сторону отставания на угол ОС, пропорциональный скольжению этого напряжения по отношению к фиксированной частоте. На самом деле, угол сЛ , опоеделяемый из выражения

(1)

(Т-х)

15

равен

(2)

с. 27T:a-2.-Ka--c-i .

вмомент совпадения сдвинутых по фазе векторов между ними будет угол cf , равный

,-cK, aT::(2ati -23cy- -ас(ш -и; уа-сси / (3)

гдеСОс,- угловая частота скольжения.

Обеспечив выбор величин t) и t так, чтобы имело место равенство

(4)

ат: t

BKN

получаем возможность отработки синхронизатором постоянного угла опережения,

Информация о дпительности отрезка Т-Х,содержащаяся в счетчике 12, используется для контроля разности частот в блоке 17 с помощью регистра 19 разности частот и дешифратора

21. Параллельный перенос числа из реверсивного счетчика 12 на суммирующий вход регистра 19 разности частот производится через четвертую логическую схему И 14 по заднему фронту периода измерения. На вычихающий вход регистра разности частот поступает аналогичная информация из блока 4 сдвига фазы синхронизирующего напряжения генератора, В регистре 19 разности частот происходит сравнение отрезков и Тр-С , модуль разности используется для управления блоком 21 включения через дешифратор 20, При малой разности Tj и Т блок 7 включе-ния. разрешает прохождение команды от схемы 16 совпадения на включение в: ключателя генератора,

В качестве схемы 16 совпацения. можно использовать как

схемы, позволяющие уловить момент совпадения импульсов с дешифратора реверсивного счетчика 13, так и схемы, позволяющие определить момент изменения порядка

чередования импульсов,.

65

Сброс регистра 19 разности частот производится импульсами с дешифраторов 13 реверсивных счетчиков через схему ИЛИ 15 и схему 18 задержки .

Задержка импульсов необходима для сохранения информации в регистре 19 разуости частот непосредственно перед моментом синхронизации. При величине периода генератора высокочастотных импульсов равной Тр,, величина задержки равна 2oiTft .

Настоящий синхронизатор отличается высокой точностью построения времени опережения, его работа не зависит от колебаний напряжения сети и генератора, синхронизатор позволяет успешно обеспечить включение генераторов на параллельную работу во всем диапазоне допустимых эначе;НИИ скоростей скольжения.

Формула изобретения

Цифровой синхронизатор, содержащий формирователи импульсов и блок контроля разности частот, и выходной блок включения, о т л и ч а ющ и и с я тем, что, с целью повышения точности во всем диапазоне

он

допустимых частот скольжения,

снабжен генератором и делителем высокочастотных импульсов, схемой совпадения, двумя идентичными блоками сдвига фазы синхронизируемых напрял ений, каждый из которых состоит из триггера, четырех логич€;ски-Х схем И, запрета, счетчика постоянного интервала времени с дешифратором и реверсивного счетчика с дешифратором, а в состав блока контроля разности частот включены логическая схема ИЛИ, схема задержки и регистр, разности с дешифратором, причем входьи форгиирователей импульсов подключены на напряжение сети и генератора соответственно, а их выходщ присоединены к счетным входам триггеров блоков сдвига, фазы напряжений сети и генератора, в каждом из блоков первый выход триггера присоединен к одному из входов первой и четвертой логических схем И, а второй выход - к одному из входов трет1зей логической схемы Инк установочным входам счетчика постоянного интервала времени и реверсивного счетчика, другой вход первой лО1ическсй схемы И присоединен к выходу генератора высокочастотных импульсов, а ее выход - к одног- у из входов второй логической схемы И и схемы запрета, другой вход второй логи 1еской схемы И и запрещающий вход схемы запрета присоединены к выходу дешифратора счетчика постоянноIO интервала времени, выход схемы запрета присоединен к считывающему входу счетчика постоянного интервала времени, выход которого присоединен ко соответствующего дешифратора, а выход второй логической схег-ы И присоединен к сумг ирующему входу реверсивного счетчика, к вычитающему входу которого присоединен выход третьей логической схемы И, второй вход которой через делитель высокочастотных импульсов присоединен к выходу генератора высокочастотных импульсов, один из выходов реверсивного счетчика присоединен ко второг-гу входу четвертой логической схемы И, а его другой выход - к входу соответствующего дешифратора, выход которого присоединен к одному из входов схемы совпадения и логической cxetvcj ИЛИ блока контроля разности частот, вторые входы схемы совпадения и логической схе.иы ИЛИ присоединены к выходам дешифратора реверсивного счетчик второго блока сдвиг.а фазы, выход логической схемы ИЛИ через схему задержки присоединен к ycTaHOBO4HONTy входу регистра разности частот,суммирующий вход регистра присоединен к выходу четвертой логической схемы И блока сдвига фазы одного из синхронизируемых напряжений, а вычитающий вход регистра разности частот к выходу четвертой логической схемы И второго блока сдвига фазы, выход регистра разности частот присоединен к одному из входов выходного блока включения, другой вход которого присоединен к выходу i схегиы совпадения.,

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 394890, кл. Н 02 3 3/42, 1973.

Фиг.

Ус

г,,

riefieHoc

j Измерение

(k

.Г-

(fu Цо

изнерение

Uwepeaue Перенос

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации генераторов переменного тока | 1987 |

|

SU1495905A1 |

| Устройство для синхронизации генераторов переменного тока | 1980 |

|

SU983892A1 |

| Импульсный синхронизатор | 1984 |

|

SU1224900A1 |

| Автоматический синхронизатор с постоянным временем опережения | 1980 |

|

SU888270A2 |

| Импульсный синхронизатор | 1988 |

|

SU1555762A2 |

| Синхронизатор с постоянным временем опережения | 1985 |

|

SU1293790A1 |

| Устройство синхронизации генераторов | 1974 |

|

SU531230A1 |

| Устройство для считывания информации с печатных плат | 1982 |

|

SU1072072A1 |

| Устройство для коррекции шкалы времени | 1982 |

|

SU1095431A1 |

| Устройство для точной автоматической синхронизации | 1985 |

|

SU1330702A2 |

Авторы

Даты

1980-05-25—Публикация

1978-02-22—Подача