Предлагаемое изобретение относится к информационно-преобразовательной и измерительной технике и может быть использовано в качестве вторичного преобразователя в системах фазового регулирования, а также в устройствах, измеряющих фазовый сдвиг двух периодических сигналов и формирующих результат измерения в виде аналогового сигнала, знак которого зависит от знака фазового сдвига.

Известен фазометр, со держащий усилители-ограничители, дифференциальную цепь, триггер, фильтр нижних частот, блок вычитаний, фильтр верхних частот, индикатор. Недостатком известного фазометра является низкая точность, обусловленная наличием аналоговых элементов.

Известен преобразователь фаза-напряжение, содержащий входные формирователи, два триггера, коммутатор, инвертор, переключатель, два интегратора и пороговое устройство. Недостатком известного преобразователя является низкое быстродействие, обусловленное наличием временной задержки интеграторов.

Наиболее близким по достигаемому результату и технической сущности к предлагаемому изобретению является инфранизкочастотный фазометр, содержащий пять формирователей, блок управления, блок знака, три резистора, сумматор, последовательно соединенные триггер, элемент совпадения, счетчик, первый блок памяти и первый преобразователь цифра- аналог, а также генератор импульсов, выходом подсоединенный к второму входу элемента совпадения, источник напряжения, который через коммутатор знака соединен с опорным входом первого преобразователя цифра-аналог, второй блок памяти, усилитель и второй преобразователь цифра-аналог, опорный вход которого сое&

В

VI

V4 СЛ О СО

Ы

динен с выходом усилителя, причем входы первого и второго формирователей являются входами фазометра, а их выходы соединены соответственно через третий и четвертый формирователи с соответствующими входами управления блока знака и соответственно с входами управления первого блока памяти, кроме того выходы первого и второго формирователей соединены через блок управления с соответствующими входами триггера, первый выход блока управления соединен также со входом управления счетчика, а второй выход блока управления - с третьим входом блока знака и входом пятого формирователя, выход которого соединен одновременно со входами управления первого и второго преобразователей цифра-аналог и со входом управления второго блока памяти, информационные входы которого соединены соответственно с выходами блока знака, а выход второго блока памяти -с управляющим входом коммутатора знака.

В известном фазометре получение результата измерения, определяющего фазовый сдвиг и представленного в аналоговом виде, осуществляется путем получения цифровых эквивалентов интервала времени т, пропорционального сдвигу фаз и периода входных сигналов Т с последующим функциональным преобразованием в аналоговую величину, пропорциональную отношению г/Т, то есть фазовому сдвигу. Основными элементами функционального преобразователя в данном фазометре являются два преобразователя цифра-аналог, три резистора, усилитель и сумматор, кроме этого для нормального функционирования известного фазометра необходимо подключить с выхода счетчика к информационным входам второго преобразователя цифра-аналог вполне определенное заранее рассчитанное число разрядов. Следовательно, недостатком известного фазометра является сложность его реализации.

Целью предлагаемого изобретения является упрощение устройства.

Достигаемый при этом положительный эффект заключается в повышении надежности, экономичности фазометра в процессе его изготовления и эксплуатации.

Сущность предлагаемого изобретения заключается в том, что в инфранизкоча- стотном фазометре, содержащем пять формирователей, блок управления, блок знака, последовательно соединенные триггер, элемент совпадения, счетчик, первый блок памяти и первый преобразователь цифра-аналог, а также генератор импульсов, выходом подсоединенный к второму входу элемента совпадения, источник напряжения, который через коммутатор знака соединен с опорным входом первого преобразователя цифра-аналог, второй блок памяти, усилитель и второй преобразователь цифра-аналог, опорный вход которого соединен с выходом усилителя, причем входы первого и второго формирователей являются входами фазометра, а их выходы соединены соответственно через третий и четвертый формирователи с соответствующими входами управления блока знака и соответственно со входами управления первого блока памяти, кроме того выходы первого и второго формирователей соединены через блок управления с соответствующими входами триггера, первый выход блока управления соединен также со входом управления счетчика, а второй выход блока управления - с третьим входом блока знака и входом пятого формирователя, выход которого соединен одновременно со входами управления первого и второго преобразователей цифра-аналог и со входом управления второго блока памяти, информационные входы которого соединены соответственно с выходами блока знака, а выход второго блока памяти - с управляющим входом коммутатора знака, преобразователи цифра- аналог выполнены в виде преобразователей цифрового кода в ток, а их объединенные выходы соединены со входом усилителя, выход которого является выходом фазометра,

а все информационные выходы счетчика соединены с информационными входами второго преобразователя цифра-аналог.

Таким образом, в предлагаемом фазометре осуществлена новая организация

функционального преобразования, состоящая в том, что после измерения интервала v времени т, пропорционального сдвигу фаз, и периода Т входных сигналов формируется аналоговая величина, пропорциональная

отношению т /Т, то есть фазовому сдвигу, и использующая лишь два преобразователя цифра-аналог и усилитель. При этом реализуется зависимость вида

„,. К1 N

U« -UwlC2 NT

где Увых - выходное напряжение фазометра, Uie - напряжение на выходе коммутато- ре знака, К1, К2 - масштабные коэффициенты, соответствующих преобразователей цифра-аналог, Nt число импульсов, пропорциональное т, NT- число импульсов, пропорциональное Т.

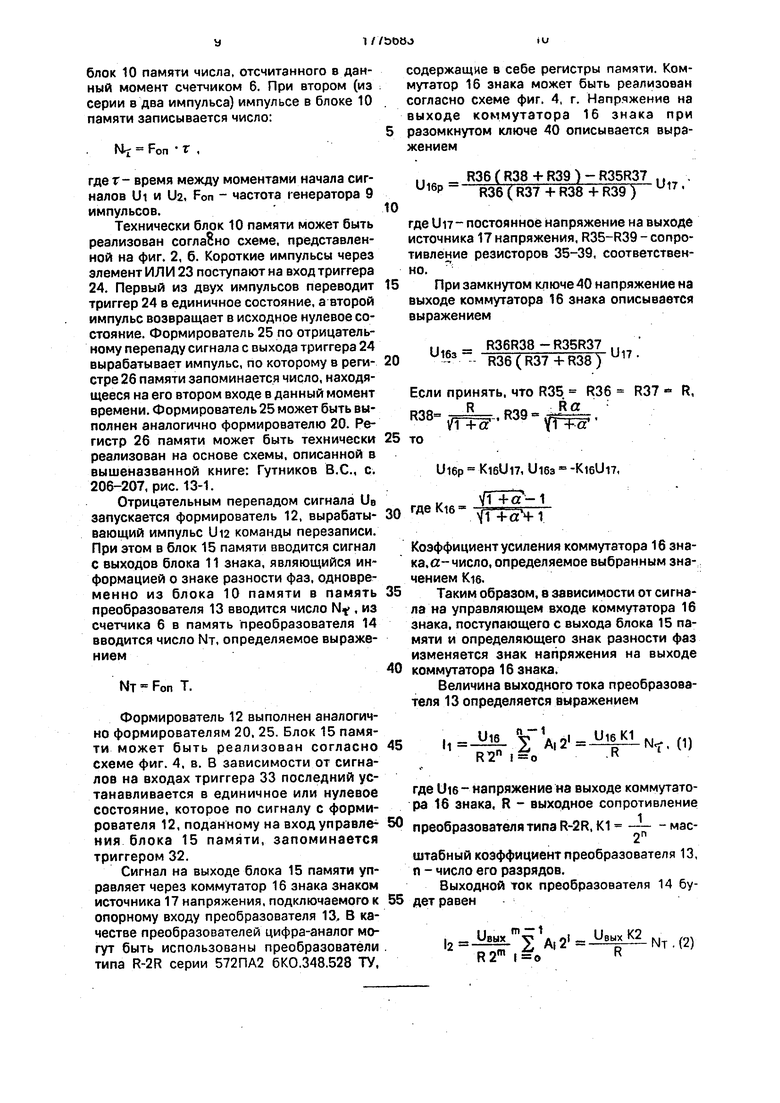

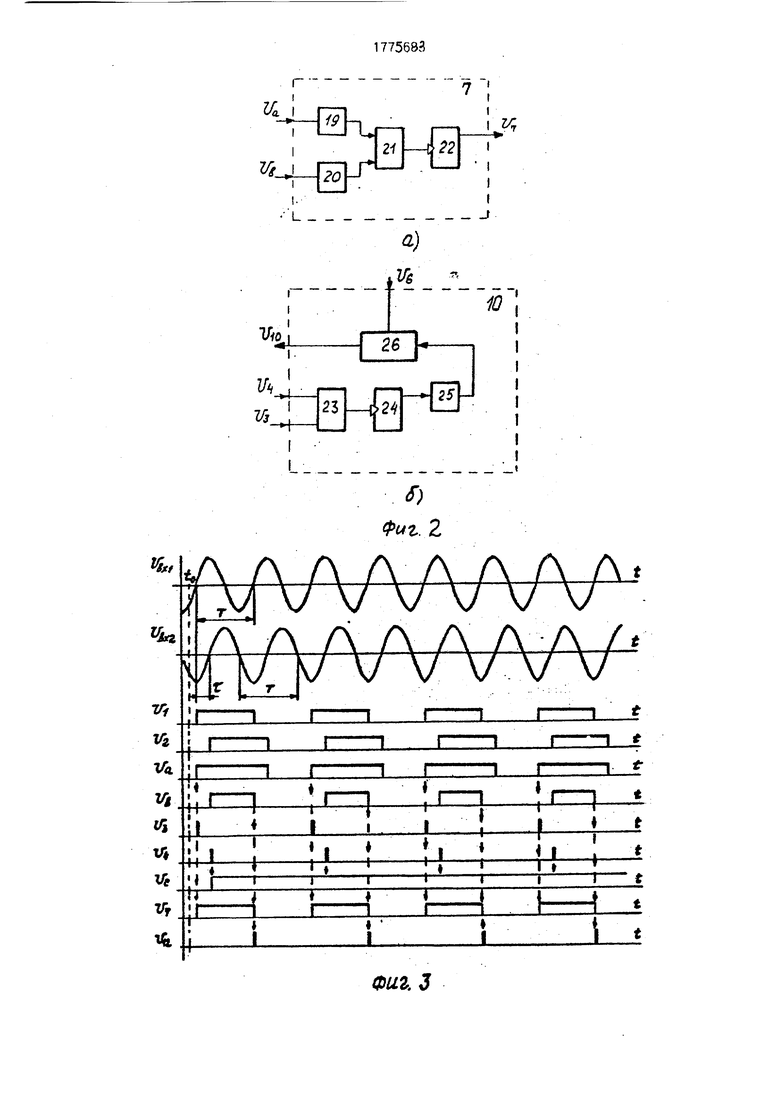

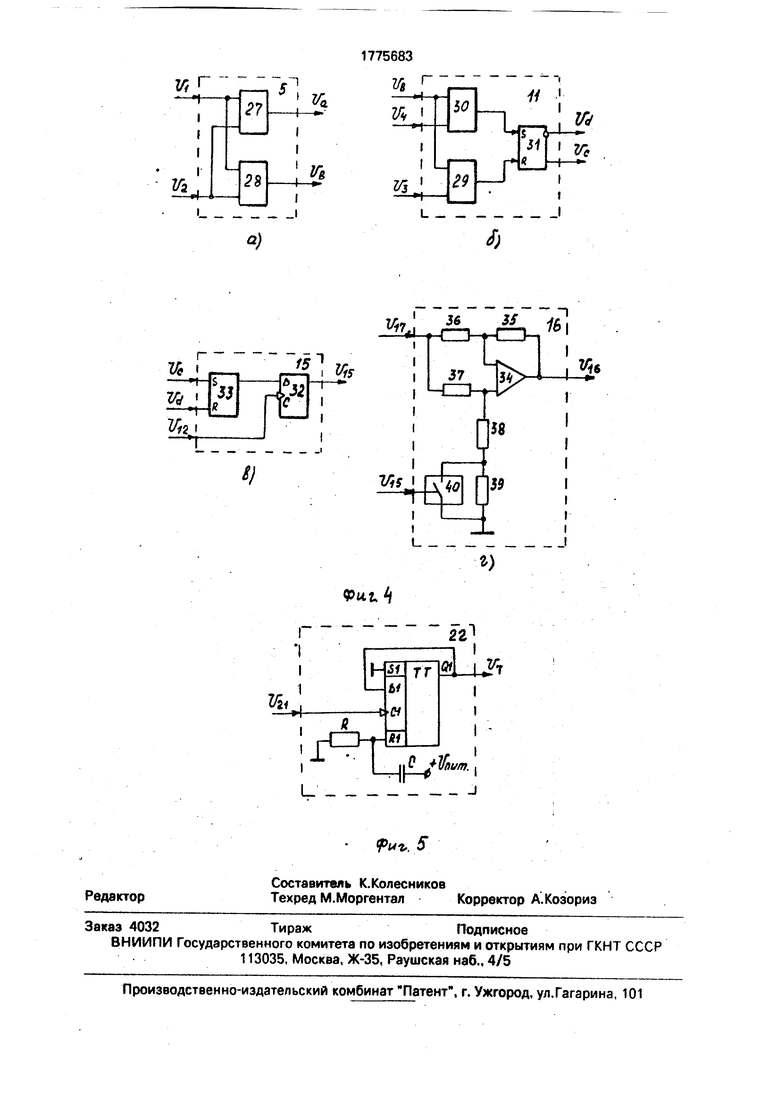

На фиг. 1 изображена структурная схема предлагаемого фазометра; на фиг. 2 а представлена структурная схема триггера; на фиг. 2 б изображена структурная схема первого блока памяти; на фиг. 3 представле- на временная диаграмма работы фазометра и его элементов: на фиг, 4, а изображена структурная схема блока управления; на фиг. 4 б представлена структурная схема блока знака; на фиг. 4 в приведена струк- турная схема второго блока памяти; на фиг.

4г изображена структурная схема коммутатора знака; на фиг. 5 приведена принципиальная схема выходной части триггера.

Входные сигналы (см. фиг. 1) поступа- ют на входы первого и второго формирователей1 1 и 2, выходы которых соединены с входами третьего и четвертого формирователей 3, 4 и одновременно подключены к соответствующим входам блока 5 управле- ния, первый выход которого соединен со вторым выходом управления счетчика 6 и первым входом триггера 7, выход которого соединен с первым входом элемента 8 совпадения, второй вход которого соединен с выходом генератора 9 импульсов, выход элемента 8 совпадения соединен с первым входом счетчика 6, выход которого подключен к первому входу первого блока 10 памяти, второй и третий входы управления которого соединены соответственно с выходами третьего и четвертого формирователей 3, 4 и одновременно с соответствующими первым и вторым входами управления блока 11 знака, третий вход которого соединен с вторым выходом блока

5управления, с вторым входом триггера 7 и с входом пятого формирователя 12, выход которого соединен одновременно с третьим

и вторым входами управления соответст- венно первого и второго преобразователей 13, 14 цифра-аналог и с первым входом управления второго блока 15 памяти, второй и третий информационные входы которого соединены соответственно с первым и вто- рым выходами блока 11 знака, выход второго блока 15 памяти соединен со вторым управляющим входом коммутатора 16 знака, первый вход которого соединен с выходом источника 17 напряжения, выход коммутатора 16 знака соединен со вторым опорным входом первого преобразователя 13 цифра-аналог, первый вход которого подключен к выходу первого блока 10 памяти, первый вход которого соединен с третьим входом (информационными входами) второго преобразователя 14 цифра-аналог, первый опорный вход которого является выходом устройства и подключен к выходу усилителя 18, вход которого соединен с выходами первого и второго преобразователей 13, 14 цифра-аналог.

На фиг. 2 а первый вход триггера 7 соединен с входом формирователя 19. второй вход триггера 7 соединен с входом формирователя 20, выход формирователя 19 соединен с первым входом элемента ИЛИ 21, второй вход которого соединен с выходом формирователя 20, а выход элемента ИЛИ 21 соединен с входом триггера 22, выход которого является выходом триггера 7.

На фиг. 2 б второй вход управления блока 10 памяти соединен с первым входом элемента ИЛИ 23, третий вход управления блока 10 памяти соединен с вторым входом элемента ИЛИ 23, выход которого подключен к входу триггера 24, выход которого соединен с входом формирователя 25. выход которого соединен с первым входом управления регистра 26 памяти, второй вход которого является первым входом блока 10 памяти, выходом которого является выход регистра 26 памяти.

На фиг. 4 а первый вход блока 5 управления соединен с первым входом элемента ИЛИ 27 и с первым входом элемента И 28, второй вход элемента ИЛИ 27 соединен со вторым входом элемента И 28 и является вторым входом блока 5 управления, первый выход которого подключен к выходу момента ИЛИ 27, а второй выход - к выходу элемента И 28.

На фиг. 4 б первый вход управления блока 11 знака соединен с первым входом элемента И 29, второй вход управления блока 11 знака соединен с первым входом элемента И 30, второй вход которого является третьим входом блока 11 знака и соединен со вторым входом элемента И 29, выход которого соединен с R-входом триггера 31, S-вход которого подключен к выходу элемента И 30.

Прямой выход триггера 31 является первым выходом блока 11 знака, второй выход которого соединен с инверсным выходом триггера 31.

На фиг. 4 в первый вход управления блока 15 памяти соединен с входом С синхронизации триггера 32, второй информационный вход блока 15 памяти соединен с S-входом триггера 33, R-вход которого является третьим информационным входом блока 15 памяти, выходом которого является выход триггера 32, D-вход которого соединен с выходом триггера 33.

На фиг. 4 г выход коммутатора 16 знака соединен с выходом операционного усилителя 34 и со входом резистора 35, выход которого соединен с инвертирующим входом усилителя 34 и с выходом резистора 36, вход которого является вторым входом коммутатора 16 знака и соединен с входом резистора 37, выход которого подключен к неинвертирующему входу усилителя 34 и ко входу резистора 38, выход которого соединен с входом резистора 39 и входом ключа 40, выход которого соединен с выходом резистора 39 и подключен к общей точке. Вход управления ключа 40 является первым управляющим входом коммутатора 16 знака.

На фиг, 5 вход триггера 22 соединен с входом синхронизации С1 микросхемы 564ТШ (ТТ) ОСТ П 340.907.80 выход триг- гера 22 соединен с выходом О1 и входом D1 микросхемы ТТ, вход S1 микросхемы ТТ подключен к общей точке, а вход R1 микросхемы ТТ через резистор R соединен с общей точкой и одновременно через конденсатор С подключен к выходу источника питания +ипит.

Устройство работает следующим образом. В начальный момент времени to при подаче питания триггеры 22 и 24 автомати- чески устанавливаются в нулевое положение. Одна из возможных схем реализации триггера 22 представлена ма фиг. 5. В момент включения на вывод Ri через конденсатор С поступает напряжение питания +Unnr, устанавливающее микросхему ТТ в нулевое состояние. Время действия потенциала +Unnr. определяется параметрами R и С. После заряда конденсатора С потенциал +1)пит. снимается с вывода R1 и триггер 22 работает в режиме счетного триггера. В качестве микросхемы ТТ может быть использована микросхема серии 564ТМ2 ОСТ П 340.907-80. Триггер 24 выполнен аналогично триггеру 22.

Формирователи 1 и 2 вырабатывают из входных сигналов UBXI и Usx2 последовательности прямоугольных импульсов длительностью Т и период- м повторения 2Т (Т - период входных сигнумов). В качест- ве формирователей 1 и 2 могут быть исполь- зованы усилители-формирователи. Выходные сигналы формирователей 1, 2 Ui и IJ2 (см. фиг. 3) поступают на входы формирователей 3, 4 и на входы блока 5 управле- ния. Последний вырабатывает два сигнала, получаемых логическим слежением {см. фиг. 3, Ua) и логическим умножением (фиг. 3, UB) Формирователи 3, 4 технически могут быть реализованы на основе одной из известных схем. Блок 5 управления технически может быть реализован согласно схеме, представленной на фиг. 4, а. Элемент У Л И 27 осуществляет логическое сложение сигналов на входах блока 5 управления, а элемент

И 28 - их логическое умножение. Триггер 7 управляется положительным перепадом Ua и отрицательным перепадом сигнала UB. Длительность сигнала на выходе триггера 7 (фиг. 3, U) равна Т и его начало синхронизировано с началом ранее появляющегося сигнала на выходах формирователей 1 или 2. При наличии импульса на выходе триггера 7 через элемент 8 совпадения от генератора 9 импульсов на счетчик 6 проходят импульсы с частотой Fon- При изменении состояния триггера 7 счетчик 6 останавливается и сохраняет свое состояние до момента, пока Ua не обратится в нуль. При этом происходит сброс счетчика б. Технически счетчик 6 может быть реализован, например, на микросхемах 564ИЕ10, 564ИЕ14 ОСТ П 340.907-80. Триггер 7 технически может быть реализован, согласно схеме фиг. 2, а. Формирователь 19 может быть реализован аналогично формирователям 3, 4, а формирователь 20 - на основе известной схемы.

Формирователь 19 вырабатывает короткий импульс в момент положительного перепада входного сигнала Ua, а формирователь 20 - в момент отрицательного перепада входного сигнала UBM Полученные импульсы через элемент ИЛИ 21 поступают на вход триггера 22. Первый из двух поступивших импульсов переводит триггер 22 в единичное состояние, а второй - возвращает в исходное нулевое,

Формирователи 3 и 4 вырабатывают короткие импульсы в моменты положительных перепадов сигналов Ui и U2, соответственно. Эти импульсы поступают на входы управления блока 11 знака. При изменении соотношения между моментами появления сигналов Ui и Ua изменяется состояние информационных выходов блока 11 знака, характеризующее знак разности фаз входных сигналов устройства. Блок 11 знака технически может быть реализован согласно схеме фиг. 4, б. На вход блока 11 знака поступает сигнал UB со второго выхода блока 5 управления, а на входы управления - сигналы Уз, U (см. фиг. 3, Ua, Ш, UB). Если UBxi опережает Uex2 (как показано на фиг. 3), то на S-вход триг гера 31 через элемент И 30 будут проходить импульсы только с формирователя 4. Если Usx2 будет опережать UBxi, то на R-вход триггера 31 через элемент И 29 будут поступать импульсы только с формирователя 3. Таким образом, в зависимости от знака фазы входных сигналов триггер 31 в рассмотренных случаях будет выдавать сигнал с прямого или инверсного своего выхода.

Одновременно импульсы с формирователей 3, 4 служат командой на введение в

блок 10 памяти числа, отсчитанного в данный момент счетчиком 6. При втором (из серии в два импульса) импульсе в блоке 10 памяти записывается число:

Mr

on

где т- время между моментами начала сигналов Ui и U2i Fon - частота генератора 9 импульсов.

Технически блок 10 памяти может быть реализован согласно схеме, представленной на фиг. 2, б. Короткие импульсы через элемент ИЛИ 23 поступают на вход триггера 24. Первый из двух импульсов переводит триггер 24 в единичное состояние, а второй импульс возвращает в исходное нулевое состояние. Формирователь 25 по отрицательному перепаду сигнала с выхода триггера 24 вырабатывает импульс, по которому в регистре 26 памяти запоминается число, находящееся на его втором входе в данный момент времени. Формирователь 25 может быть выполнен аналогично формирователю 20. Регистр 26 памяти может быть технически реализован на основе схемы, описанной в вышеназванной книге: Гутников B.C., с. 206-207, рис. 13-1.

Отрицательным перепадом сигнала UB запускается формирователь 12, вырабатывающий импульс U12 команды перезаписи. При этом в блок 15 памяти вводится сигнал с выходов блока 11 знака, являющийся информацией о знаке разности фаз, одновременно из блока 10 памяти в память преобразователя 13 вводится число Nf , из счетчика б в память преобразователя 14 вводится число NT, определяемое выражением

NT - Fon T.

Формирователь 12 выполнен аналогично формирователям 20. 25. Блок 15 памяти может быть реализован согласно схеме фиг. 4, в. В зависимости от сигналов на входах триггера 33 последний устанавливается в единичное или нулевое состояние, которое по сигналу с формирователя 12, поданному на вход управления блока 15 памяти, запоминается триггером 32.

Сигнал на выходе блока 15 памяти управляет через коммутатор 16 знака знаком источника 17 напряжения, подключаемого к опорному входу преобразователя 13, В качестве преобразователей цифра-аналог могут быть использованы преобразователи типа R-2R серии 572ПА2 6К0.348.528 ТУ,

0

5

0

содержащие в себе регистры памяти. Коммутатор 16 знака может быть реализован согласно схеме фиг. 4, г. Напряжение на выходе коммутатора 16 знака при разомкнутом ключе 40 описывается выражением

и R36 ( R38 + R39 ) - R35R37 ,, , U16p R36 ( R37 + R38 + R39 ) U17

где U и- постоянное напряжение на выходе источника 17 напряжения, R35-R39 - сопротивление резисторов 35-39, соответственно.

При замкнутом ключе 40 напряжение на выходе коммутатора 16 знака описывается выражением

,. R36R38 - R35R37 ., R36(R37-fR38) Un

Если принять, что R35 R36 R38,R39. 25 то

R37- R,

Ui6p Kiel) 17,1Нбз -KieUi, 30 где Kie;

УТТсГ-1 У1

Коэффициент усиления коммутатора 16 знака, а- число, определяемое выбранным значением Kie.

Таким образом, в зависимости от сигнала на управляющем входе коммутатора 16 знака, поступающего с выхода блока 15 памяти и определяющего знак разности фаз изменяется знак напряжения на выходе

коммутатора 16 знака.

Величина выходного тока преобразователя 13 определяется выражением

..- U« У Voi- UieK1 ,ioA|2

R

, О)

где Die - напряжение на выходе коммутатора 16 знака, R - выходное сопротивление

преобразователя типа R-2R, К1 мас2П

штабный коэффициент преобразователя 13, п - число его разрядов.

Выходной ток преобразователя 14 бу- дет равен

m-l

иШIII

у д 21 Ueblx

R2m.io R

К2

NT . (2)

где Увых - напряжение на выходе фазометра, К2 - -масштабный коэффициент

гпЧП

преобразователя 14, m - число его разрядов.

Так как на входе усилителя имеет место соотношение h + «2 - 0, то с учетом (1) и (2) получим:

JJwKL +JJiwKLNT-o. кк

Отсюда

и„ых - Uie

К1 N

К2 NT Uie -у- Uie К Y

Так как величина г пропорциональна фазовому сдвигу р а Т - пропорциональна 2 л, то выражение (3) соответствует

UB«x -Ui6K- -.

Следовательно, устройство измеряет разность фаз и формирует аналоговый сигнал, пропорциональный ее величине и имеющий соответствующий знак.

Таким образом, по сравнению с прототипом предлагаемый фазометр проще по технической реализации, так как исключаются дополнительные три сопротивления и сумматор.

Формула изобретения

Инфраниэкочастотный фазометр, содержащий пять формирователей, блок управления, блок знака, последовательно

соединенные триггер, элемент совпадения, счетчик, первый блок памяти и первый преобразователь цифра-аналог, а также генератор импульсов, выходом подсоединенный к

второму входу элемента совпадения, источник напряжения, который через коммутатор знака соединен с упорным входом первого преобразователя цифра-аналог, второй блок памяти, усилитель и второй преобразователь цифра-аналог, опорный вход которого соединен с выходом усилителя, причем входы первого и второго формирователей являются входами фазометра, а их выходы соединены соответственно через третий и

четвертый формирователи с входами управления блока знака и соответственно с входами управления первого блока памяти, кроме того выходы первого и второго формирователей соединены через блок управления с соответствующими входами триггера, первый выход блока управления соединен также с входом управления счетчика, а второй выход блока управления - с третьим входом блока знака и входом пятого формирователя, выход которого соединен одновременно с входами управления первого и второго преобразователей цифра-аналог и с входом управления второго блока памяти, информационные входы которого соединены соответственно с выходами блока знака, а выход второго блока памяти - с управляющим входом коммутатора знака, отличающийся тем, что. с целью упрощения устройства, в нем преобразователи цифра-аналог выполнены в виде преобразователей цифрового кода в ток, а их объединенные выходы соединены с входом усилителя, выход которого является выходом фазометра, а все ин0 формационные выходы счетчика соединены с информационными входами второго преобразователя цифра-аналог.

| название | год | авторы | номер документа |

|---|---|---|---|

| Инфранизкочастотный фазометр | 1980 |

|

SU924614A1 |

| Устройство для отображения векторных диаграмм на экране электронно-лучевой трубки | 1988 |

|

SU1541663A1 |

| Цифровой одноканальный инфранизкочастотный фазометр | 1987 |

|

SU1472831A1 |

| Анализатор частотного спектра | 1980 |

|

SU900209A1 |

| Фазометр мгновенных значений | 1981 |

|

SU980015A1 |

| Генератор сигналов сложной формы | 1980 |

|

SU983692A1 |

| ЦИФРОВОЙ ФАЗОМЕТР | 2002 |

|

RU2207579C1 |

| Устройство для вычисления массы нефти и нефтепродуктов в резервуарах | 1983 |

|

SU1117653A1 |

| Цифровой фазометр мгновенных значений | 1985 |

|

SU1320770A1 |

| Устройство для регистрации цифровой информации | 1986 |

|

SU1386915A2 |

Использование: предлагаемое изобретение относится к информационно-преобразовательной и измерительной технике и может быть использовано в системах автоматического регулирования и фазового управления. Цель - упрощение устройства. Сущность изобретения заключается в новой организации функционального преобразования промежуточных цифровых результатов в напряжение постоянного тока, пропорциональное фазовому сдвигу. При этом в качестве преобразователей цифра-аналог используются преобразователи цифрового кода в ток. Положительный эффект: простота, надежность, экономичность в процессе изготовления и эксплуатации. 5 ил. .

s

.Л

9л

ы

; L

//

и

9л

ы

(V

ъ

i

WSSLLi

Я

v« i

г

4

| Фазометр | 1986 |

|

SU1318929A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Инфранизкочастотный фазометр | 1980 |

|

SU924614A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1992-11-15—Публикация

1990-01-23—Подача