Изобретение относится к измерительной технике и может быть использовано в устройствах контроля допустимых пределов отклонения частоты следования различных периодических процессов.

Известен селектор импульсов, содержащий формирователь импульсов, модулятор, интегратор, компаратор, узел управления.

Однако работаетон только по пороговому принципу и не позволяет селектировать импульсы с длительностью в определенных заданных пределах,

Известно устройство для контроля заданного временного интервала между импульсами прямоугольной формы, содержащее два формирователя прямоугольных импульсов, интегратор, релаксатор, компаратор и выходной каскад.

Известное устройство обеспечивает контроль заданного временного интервала между нечетными и четными импульсами, .например между 1 и 2, 3 и 4 и т.д. Контроль же заданного временного интервала между четными и нечетными, например между 2 и 3, 3 и 4 и т.д., не возможен. Это объясняется тем, что по заднему фронту нечетных прямоугольных импульсов запускается времязадающая цепочка и начинается контроль за появлением четного прямоугольного импульса в заданном интервале ожидания. Заметим, что четные импульсы формируются из отрицательной составляющей входного сигнала, что также ограничивает область применения известного устройства.

Цель изобретения - расширение диапазона контролируемого временного интервала при сохранении аппаратурных затрат.

Положительный эффект достигается за счет охвата обратной связью интегратора с компаратором. В этом случае при наличии положительного импульса на выходе формирователя прямоугольных импульсов обратная связь является положительной и заявляемое устройство с большой скоростью приходит в исходное устойчивое положение, которое всегда является исходным. Если этот импульс отрицательный, то обратная связь отрицательная. Тогда контур, охваченный этой связью, будет генерировать импульсы прямоугольной формы, начинаЯ с пау.зы. Если очередной импульс приходит в период наличия импульса на выходе этого контура, то изменяется сигнал заявляемого устройства. А схема переходит в исходное состояние, с исчезновением импульса начинается контроль за периодом.появления следующего импульса. Для реализации обратной связи в схему заявляемого устройст ва, по сравнению с прототипом, дополнительно вводится сумматор.

Таким образом заявляемое устройство по сравнению с прототипом представляет собой новую совокупность конструктивных элементов и связей, что является существенным признаком изобретения.

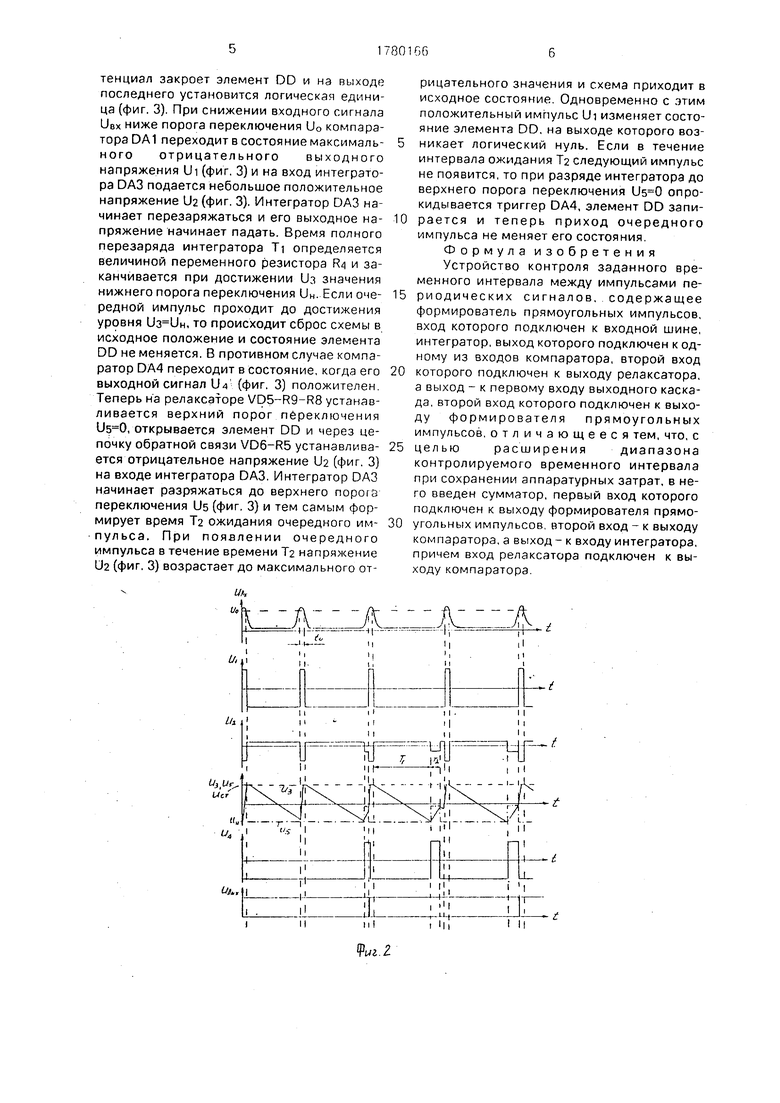

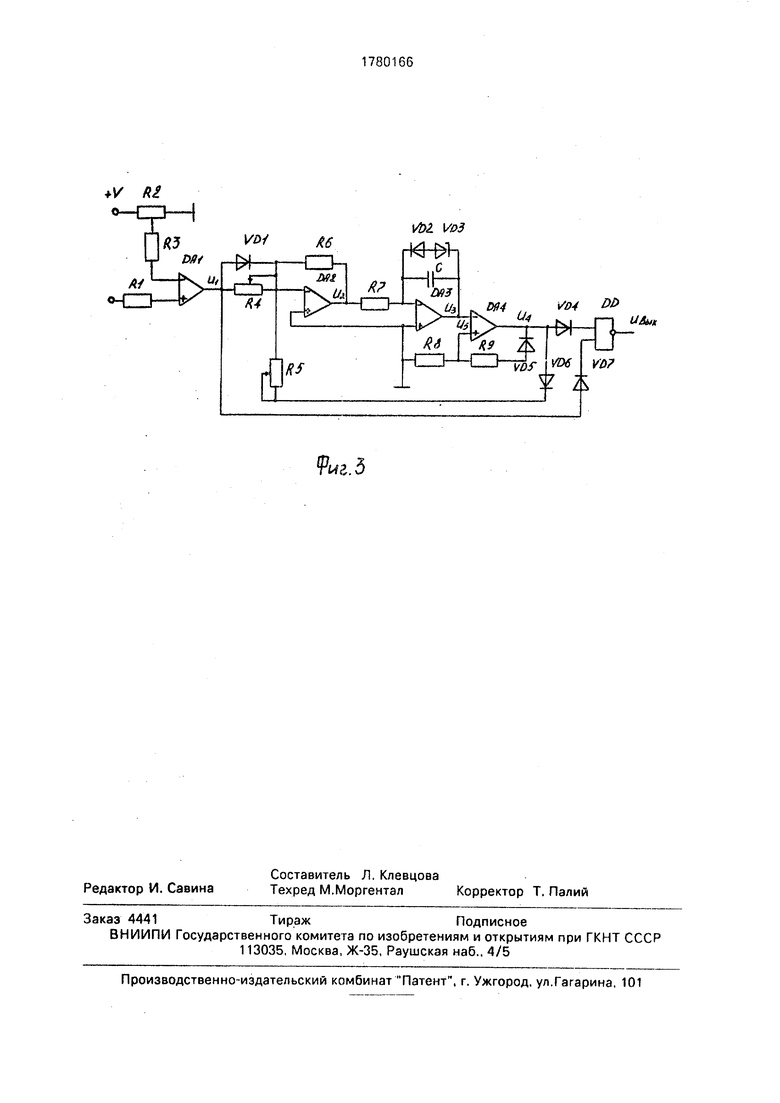

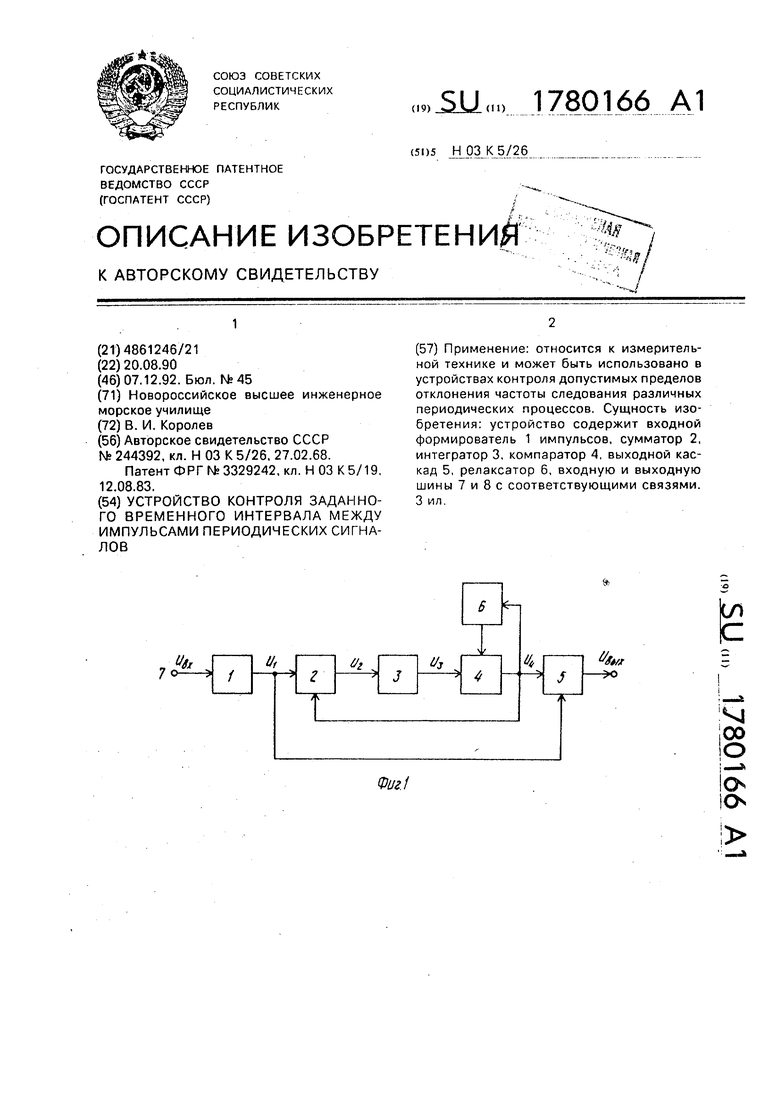

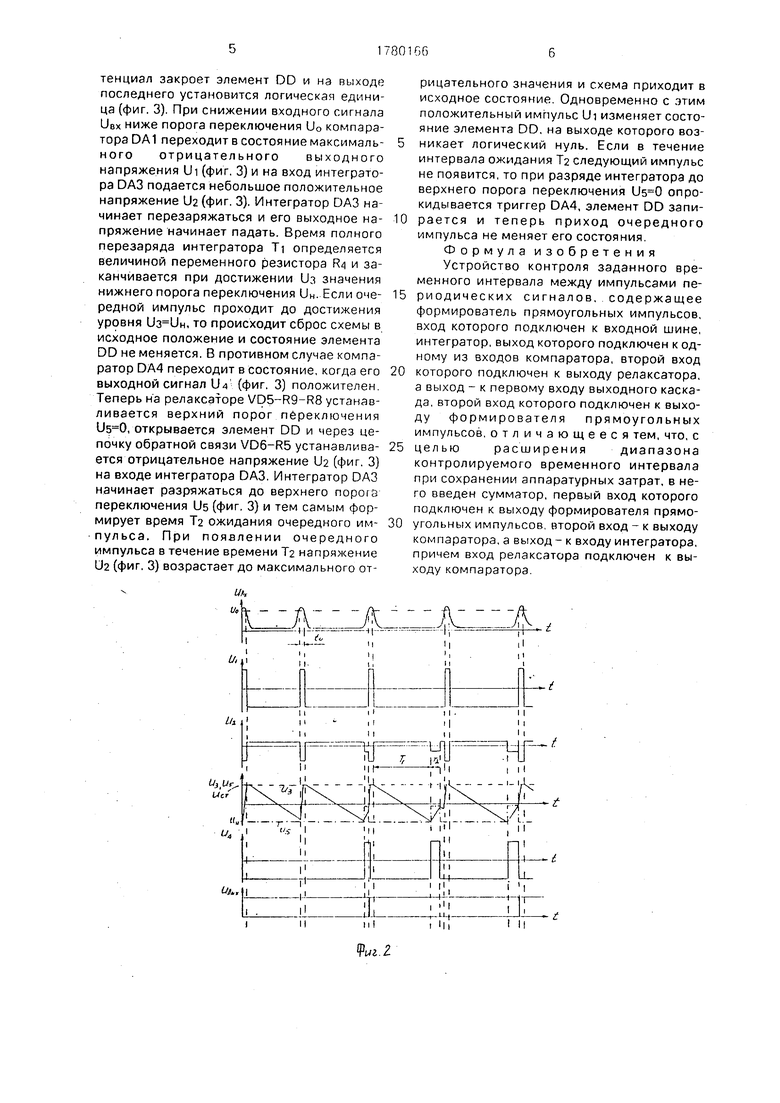

На фиг. 1 и 2 приведены структурные электрические схемы устройства: на фиг. 3 - временные диаграммы, иллюстрирующие его работу.

0 Устройство состоит из последовательно соединенных входного формирователя 1 импульсов прямоугольной формы, сумматора 2. интегратора 3, компаратора 4 и выходного каскада 5, а также релаксатора 6, вход

5 которого соединен с выходом компаратора 4, а выход с его вторым входом, кроме того, второй вход сумматора соединен с выходом компаратора 4 и второй вход выходного каскада 5 соединен с выходом входного фор0 мирователя 1 импульсов прямоугольной формы, входная шина 7 подключена к входному формирователю 1 импульсов, а выходная шина 8 - к выходу выходного каскада 5. Конструктивное выполнение заявляе5 мого устройства рассмотрим по электрической схеме (фиг. 2). Входной формирователь импульсов прямоугольной формы представляет собой компаратор со сдвигом, выполненный на операционном усилителе DA1.

0 Сумматор построен на операционном усилителе DA2. Интегратор представляет собой операционный усилитель DA3, охваченный отрицательной гибкой обратной связью посредством конденсатора С. Компаратор построен на операционном усилителе DA4. Выходной каскад собран надвухпозиционном элементе типа И-НЕ. Релаксатор представляет собой нелинейное устройство, состоящее из диода VD5 и двух регистров R8 и R9.

0Работает устройство следующим образом.

Когда входной периодический сигнал Unx превышает порог Uo (фиг. 3) переключения компаратора DA1, на его выходе устанавливается положительный импульс

5 .длительностью Тц (фиг. 3).. Через диод VD1 Ui подается непосредственно на вход сумматора DA2, на выходе которого устанавливается максимальный отрицательный сигнал U2 (фиг. 3). Интегратор с большой

0 скоростью насыщается до уровня, равного напряжению стабилизации UCT (фиг. 3) стабилитрона VD3. Поскольку UCT больше по абсолютной величине нижнего порога UN переключения компаратора DA4, то на выходе компаратора DA4 устанавливается максимальное отрицательное напряжение (JA (фиг. 3), а релаксатор VD5-R9-R8 сформирует нижний порог переключения, который близок к UCT. Диод VD4 отсекает отрицательный сигнал U, его нулевой потенциал закроет элемент DD и на выходе последнего установится логическая единица (фиг. 3). При снижении входного сигнала UBX ниже порога переключения Uo компаратора DAI переходит в состояние максимальноге отрицательного выходного напряжения Ui (фиг. 3) и на вход интегратора DA3 подается небольшое положительное напряжение U2 (фиг. 3). Интегратор DA3 начинает перезаряжаться и его выходное напряжение начинает падать. Время полного перезаряда интегратора Ti определяется величиной переменного резистора R4 и заканчивается при достижении Уз значения нижнего порога переключения UH. Если очередной импульс проходит до достижения уровня , то происходит сброс схемы в исходное положение и состояние элемента DD не меняется. В противном случае компаратор DA4 переходит в состояние, когда его выходной сигнал U (фиг. 3) положителен. Теперь на релаксаторе Vp5-R9-R8 устанавливается верхний порог переключения , открывается элемент DD и через цепочку обратной связи VD6-R5 устанавливается отрицательное напряжение U2 (фиг. 3) на входе интегратора DA3. Интегратор DA3 начинает разряжаться до верхнего порога переключения Us (фиг. 3) и тем самым формирует время Т2 ожидания очередного импульса. При появлении очередного импульса в течение времени Тз напряжение Ua (фиг. 3) возрастает до максимального отi/л.

рицательного значения и схема приходит в исходное состояние. Одновременно с этим положительный импульс Ui изменяет состояние элемента DD. на выходе которого возникает логический нуль. Если в течение интервала ожидания Т2 следующий импульс не появится, то при разряде интегратора до верхнего порога переключения опрокидывается триггер DA4, элемент DD запирается и теперь приход очередного импульса не меняет его состояния. Формула изобретения Устройство контроля заданного временного интервала между импульсами периодических сигналов, содержащее формирователь прямоугольных импульсов, вход которого подключен к входной шине, интегратор, выход которого подключен к одному из входов компаратора, второй вход которого подключен к выходу релаксатора, а выход - к первому входу выходного каскада, второй вход которого подключен к выходу формирователя прямоугольных импульсов, отличающееся тем, что, с целью расширения диапазона контролируемого временного интервала при сохранении аппаратурных затрат, в него введен сумматор, первый вход которого подключен к выходу формирователя прямоугольных импульсов, второй вход - к выходу компаратора, а выход - к входу интегратора, причем вход релаксатора подключен к выходу компаратора.

+И Kl 1/2)2 VoS Vu4

| название | год | авторы | номер документа |

|---|---|---|---|

| Время-импульсный универсальный интегрирующий преобразователь напряжения с функцией широтно-импульсной модуляции | 2020 |

|

RU2731601C1 |

| ВРЕМЯ-ИМПУЛЬСНЫЙ УНИВЕРСАЛЬНЫЙ ИНТЕГРИРУЮЩИЙ ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ | 2018 |

|

RU2689805C1 |

| Универсальный время-импульсный интегрирующий преобразователь напряжения с четырьмя функциями широтно-импульсной модуляции | 2023 |

|

RU2822374C1 |

| Универсальный время-импульсный интегрирующий преобразователь напряжения с функцией широтно-импульсной модуляции | 2023 |

|

RU2819373C1 |

| Помехоустойчивый триггер | 1988 |

|

SU1688402A1 |

| ФАЗОСДВИГАЮЩЕЕ УСТРОЙСТВО | 2001 |

|

RU2216846C2 |

| Электрокардиостимулятор | 1981 |

|

SU1039505A1 |

| УСТРОЙСТВО ДЛЯ ВЫДЕЛЕНИЯ И ПРЕОБРАЗОВАНИЯ ПОЛЕЗНОЙ (ИНФОРМАЦИОННОЙ) СОСТАВЛЯЮЩЕЙ СИГНАЛА ДАТЧИКА РАСХОДОМЕРА ВИХРЕВОГО ТИПА | 2000 |

|

RU2176380C1 |

| УСТРОЙСТВО ДЛЯ ОХРАНЫ ОБЪЕКТА | 1993 |

|

RU2070116C1 |

| Устройство для определения модуля | 1982 |

|

SU1109763A1 |

Применение: относится к измерительной технике и может быть использовано в устройствах контроля допустимых пределов отклонения частоты следования различных периодических процессов. Сущность изобретения: устройство содержит входной формирователь 1 импульсов, сумматор 2, интегратор 3. компаратор 4, выходной каскад 5, релаксатор 6, входную и выходную шины 7 и 8 с соответствующими связями. 3 ил.^Л(ЯСч00ОФиг.!О 10

%1Ъ

| СЕЛЕКТОР ИМПУЛЬСОВ | 0 |

|

SU244392A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Способ гальванического снятия позолоты с серебряных изделий без заметного изменения их формы | 1923 |

|

SU12A1 |

Авторы

Даты

1992-12-07—Публикация

1990-08-20—Подача