Изобретение относится к вычислительной технике и микроэлектронике и может быть использовано при построении отказоустойчивых цифровых устройств и кодовых преобразователей.

Известно устройство для определения наличия одной единицы в n-разрядном двоичном слове, содержащее группы элементов И-НЕ и ИСКЛЮЧАЮЩЕЕ ИЛИ.

Недостатком устройства является ограниченная область применения, вследствие единственности порога срабатывания (один бит из п бит).

Наиболее близким по функциональным возможностям и конструкции техническим решением к предлагаемому является устройство контроля двоичной информации, содержащее группы элементов И, ИЛИ, НЕ.

Недостатком устройства является невозможность программируемого изменения (настройки сигналами из {0, 1}) порога срабатывания.

Цель изобретения - расширение функциональных возможностей устройства за счет программирования порога срабатывания.

VJ

00

о ю VI

Ч)

Поставленная цель достигается тем, что в программируемое устройство, содержащее п - 1 (п - разрядность входного информационного слова) элементов ИЛИ, введены многофункциональный логический модуль, выход которого соединен с выходом устройства, и два демультиплексора, информационный вход первого из которых соединен с первым информационным входом устройства и Тин верен ым информационным входом второго демультиплексора, 1-й (1 1, 2, ,.., k:; k jlogznf) адресный вход которого соединен с -м настроечным входом устройства и :м адресным входом первого демультиплексора, первый выход которого соединен с первым настроечным входом многофункционального логического модуля, 0 + 1)-й 0 1, 2, ... п - 1) выход соединен с первым входом j-ro элемента ИЛИ, второй вход которого соединен с j-м выходом вто- рого демультиплексораг, а выход соединен с О + 1)-м настроечным входом многофункционального логического модуля, j-й информационный вход которого соединен с 0 + 1)-м информационным входом устройства, кро- ме того, многофункциональный логический модуль содержит мультиплексор, выход которого соединен с выходом модуля, j-й информационный вход которого соединен с j-м адресным входом мультиплексора, первый настроечный вход соединен с первым входом данных мультиплексора, ( + 1)-й, (1 1, 2,..., п - 2) настроечный вход соединен с S-M (2 s 2П 1 -1; I as.i + as.2 + ... + a s.n-1, где as (as,i, as,2, ..., as,j. ..., as,n-i) - двоичное представление числа s; as.j С {О, 1}; j 1, 2, ..., n-1) входом данных мультиплексора, n-й настроечный вход соединен с 2 - м входом данных мультиплексора,

Программируемое устройство содер- жит п-1 (п - разрядность входного информационного слова) элементов ИЛИ, два демультиплексора и многофункциональный логический модуль, выход которого соединен с выходом устройства. Причем информационный вход первого из демуль- типлексоров соединен с первым информационным входом устройства и инверсным информационным входом второго демультиплексора, 1-й (I 1, 2, .... k; k og.n ) адресный вход которого соединен с l-м настроечным входом устройства и i-м адресным входом первого демультиплексора. Первый вход первого демультиплексора соединен с первым настроечным входом многофункционального логического модуля, 0 + 1)-u(j 1,2,.... п - 1) выход соединен с первым входом j-ro элемента ИЛИ, второй вход которого соединен с j-м выходом второго демультиплексора, а выход соединен с О + 1)-м настроечным входом многофункционального логического модуля, j-й информационный вход которого соединен с 0 + 1)м информационным входом устройства. Многофункциональный логический модуль содержит мультиплексор, выход которого соединен с выходом модуля, j-й информационный вход которого соединен с j-м адресным входом мультиплексора. Первый настроечный вход многофункционального логического модуля соединен с первым входом данных мультиплексора, (I + 1}-й (,2, ..,, п - 2) настроечный вход модуля соединен сз-м(2 s.2n 1-1: l as,i + as,2 + ... + as,n-i, где as (as,i, as,2,..., as.j,.... as,n-i) - двоичное представление числа s; as,j E{0,1); j 1,2,..., n-1) входом данных мультиплексора, а n-й настроечный вход соединен входом данных мультиплексора.

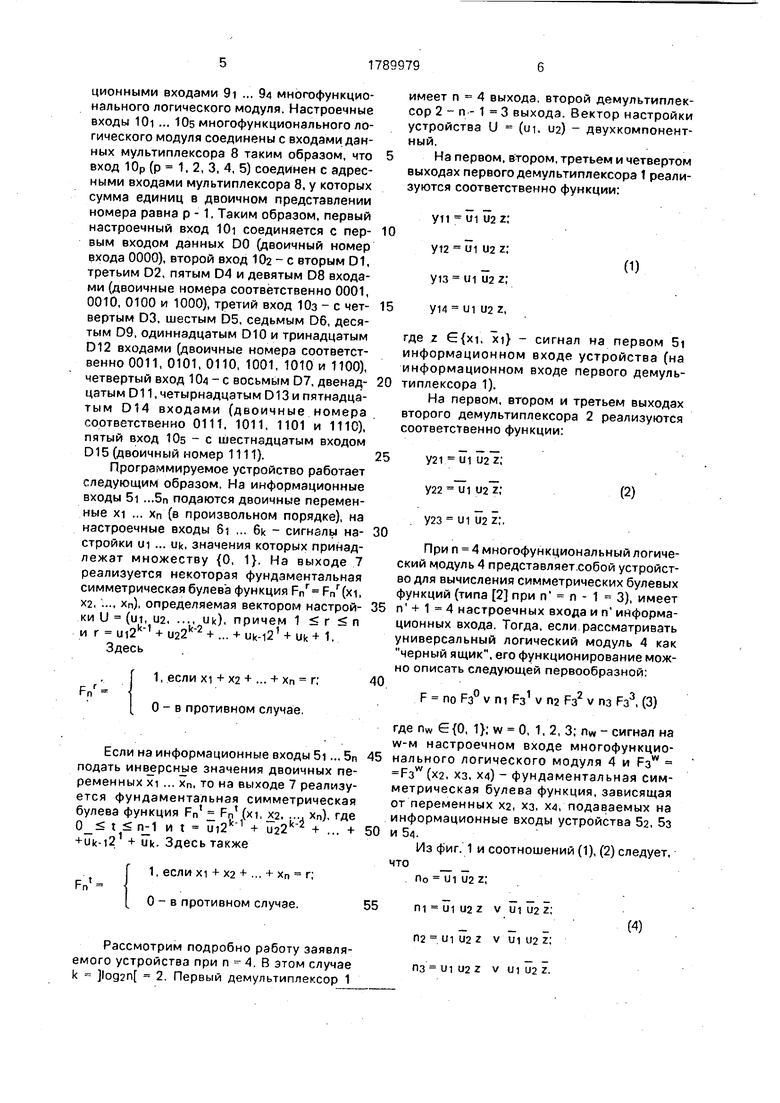

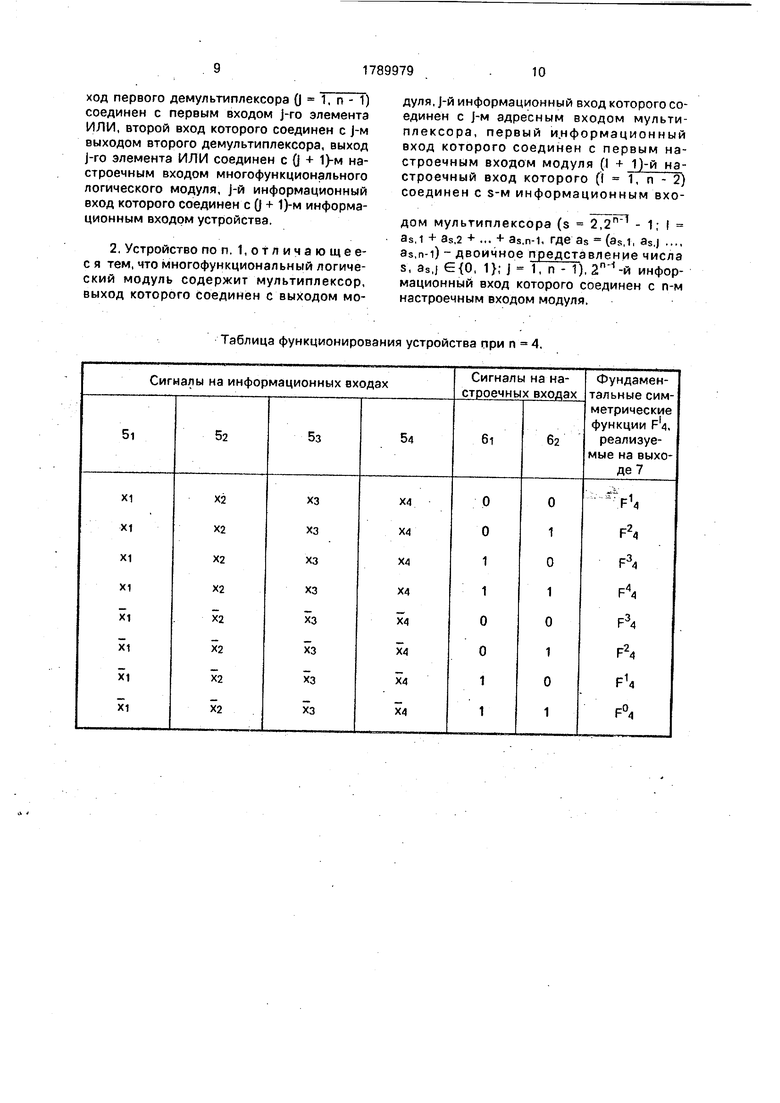

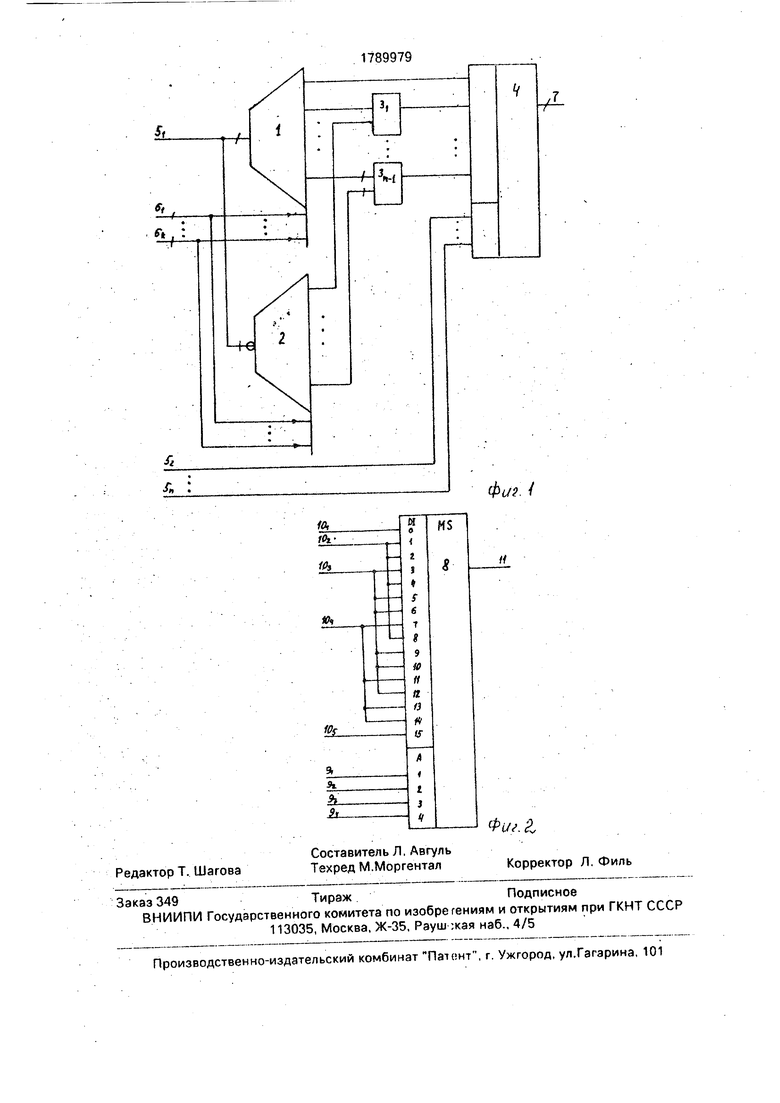

На фиг. 1 представлена схема заявляемого устройства для произвольного значения п; на фиг, 2 - пример построения многофункционального логического модуля на основе мультиплексора при п 5.

Программируемое устройство (фиг. 1) содержит первый 1 и второй 2 демультип- лексоры (второй демультиплексор 2 имеет инверсный информационный вход), п-1 элементов ИЛИ 3i ... Зп-1, многофункциональный логический модуль 4, п информационных входов 5i...5n, k log2n настроечных входов 6i...6k, выход 7. При этом первый информационный вход 5i устройства соединен с информационным входом первого демультиплексора 1 и с инверсным информационным входом второго демультиплексора 2, Информационные входы устройства со второго по п-й 52 ... 5П соединены с информационными входами многофункционального логического модуля 4, выход которого соединен с выходом устройства 7. Настроечные-входы устройства 6i... 6k соединены с адресными входами первого 1 и второго 2 дёмультиплексоров. Первый выход первого демультиплексора 1 соединен с первым настроечным входом многофункционального логического модуля 4, (j + 1)-й О - 1,2, .... п-1) настроечный вход которого соединен с выходом j-ro элемента ИЛИ 3j, первый вход которого соединен с 0 + 1)-м выходом первого демультиплексора 1, второй вход соединен с j-м выходом второго демультиплексора 2.

Многофункциональный логический модуль (фиг. 1) при п 5 (фиг. 2) может быть реализован на основе 2n 1 16-канального мультиплексора 8. При этом адресные входы мультиплексора 8 соединены с информэционными входами 9i ... 94 многофункционального логического модуля. Настроечные входы 10i ... 10g многофункционального логического модуля соединены с входами данных мультиплексора 8 таким образом, что вход Юр (р 1, 2, 3, 4, 5) соединен с адресными входами мультиплексора 8, у которых сумма единиц в двоичном представлении номера равна р -1, Таким образом, первый настроечный вход 10i соединяется с первым входом данных DO (двоичный номер входа 0000), второй вход 102 - с вторым D1, третьим D2, пятым D4 и девятым D8 входами (двоичные номера соответственно 0001, 0010, 0100 и 1000), третий вход Юз - с четвертым D3, шестым D5, седьмым Об, десятым D9, одиннадцатым D10 и тринадцатым D12 входами (двоичные номера соответственно 0011, 0101, 0110, 1001, 1010 и 1100), четвертый вход 104 - с восьмым D7, двенадцатым D11, четырнадцатым D13 и пятнадцатым D14 входами (двоичные номера соответственно 0111. 1011, 1101 и 1110), пятый вход 10s - с шестнадцатым входом D15 (двоичный номер 1111).

Программируемое устройство работает следующим образом. На информационные входы 5i ...5П подаются двоичные переменные xi ... хп (в произвольном порядке), на настроечные входы 6i ... 6k - сигналы настройки ui ... uk, значения которых принадлежат множеству {0, 1}. На выходе .7 реализуется некоторая фундаментальная симметрическая булева функция Fnr Fnr(xi, Х2, .... Хп), определяемая вектором настройки U (ui, из, ..., uk), причем 1 г п и г + + ... + Uk-i2 + Uk + 1.

Здесь

Fnr

1, если xi + X2 + ... + xn r; О - в противном случае,

Если на информационные входы 5i... 5n подать инверсные значения двоичных переменных xi ... хп, то на выходе 7 реализуется фундаментальная симметрическая булева функция Fn Fn (xi, Х2, .... хп), где О t n-1 и t + + ... +

+ Uk-i21 + Uk. Здесь также

Fnr

1, если xi + X2 + ... + xn r; О - в противном случае.

Рассмотрим подробно работу заявляемого устройства при п 4. В этом случае к 1одгп - 2. Первый демультиплексор 1

имеет п 4 выхода, второй демультиплек- сор 2 - п - 1 3 выхода. Вектор настройки устройства U - (UL из) - двухкомпонент- ный.

5На первом, втором, третьем и четвертом выходах первого демультиплексора 1 реализуются соответственно функции:

10

У11 U1 U2Z,yi2 ui U2 z; yi3 ui U2z;

15у 14 U1 U2 Z,

0)

где z G{xi, xi} - сигнал на первом 5i информационном входе устройства (на информационном входе первого демуль- типлексора 1).

На первом, втором и третьем выходах второго демультиплексора 2 реализуются соответственно функции:

25 у21 . ui U2 z;

У22 U1 U2,

(2)

30

У23 1Л U2Z,-,

При п 4 многофункциональный логический модуль 4 представляет .собой устройство для вычисления симметрических булевых функций (типа 2 при п п - 1 3), имеет

п + 1 4 настроечных входа и п информационных входа. Тогда, если рассматривать универсальный логический модуль 4 как черный ящик, его функционирование можно описать следующей первообразной:

F no F3° v щ Рз1 v П2 Fa2 v пз Fs3, (3)

где nw G{0, 1}; w 0, 1,2,3; riw - сигнал на w-м настроечном входе многофункционального логического модуля 4 и Fsw F3W (Х2, хз, Х4) - фундаментальная симметрическая булева функция, зависящая от переменных Х2, хз, Х4, подаваемых на информационные входы устройства 52, 5з

и 54.

Из фиг. 1 и соотношений (1), (2) следует, что . По in U2 z;

55 щ ui U2 zvui «2 z;

П2 U1 U2 ZVU1 U2 Z,

ПЗ U1 U2 ZVUi U2 Z.

(4)

Рассмотрим формирование фундаментальных симметрических булевых функций на выходе 7 устройства.

1) На информационные входы 5i ...64 подаются прямые значения переменных xi ... Х4. Если принять во внимание соотношения (3) и (4), то имеет место

a)ui U2 0, n0 xi,щ xi, П2 пз 0и F - По Рз° v щ Рз1 - xi Рз° v xi Рз F4 F4 (XI, Х2, ХЗ, Х4).

6)U1 0, U2 1, По П3 0, Ш Х1, П2 Х1 И F Щ Рз1 V П2 РЗ2 X1 Рз V Х1 Рз F4 F42 (Х1, Х2, ХЗ, Х4).

B) U1 1,oU2 0, Пр П1 Ј, П2 XJ, ПЗ Х1 И

з2

F4 (Х1. Х2. ХЗ, Х4).

F - n.2 F32 v пз Рз3 xi Рз2 v xi Рз3 F43

г) U1 U2 1Г По П1 П2 О, ПЗ Х1 И

F ПЗ Рз3 Х1 Рз F4 F4 (Х1, Х2. ХЗ, Х4).

2) На информационные входы 51 ...54 подаются инверсные значения переменных

Х1 ... Х4..

Заметим, что многофункциональный логический модуль 4 в таком случае может быть описан первообразной, полученной из (3):

F По Рз3 v щ Рз2 v П2Рз1 v пз Рз°, (5)

так как Fn1 (xi, X2, ..., xn) (xi, , .... хп), где I 0, 1, ..., п.

Учитывая (4) и (5), получаем

a) ui U2 0, п0 xi, Гц XL П2 пз 0 и F - По Рз3 v щ Рз2 - xi Рз3 v xi Рз2 - F43 F4 (Х1, Х2, ХЗ, Х4).

6)U1 0, U2 1, 0, П1 Х1, П2 Х1 И F П1 Рз2 V 02 Рз Х1 Рз V Х1 Рз F4 Р42(Х1, Х2, ХЗ, Х4).

в) 111 1, U2 0, По П1 О, П2 Х1, ПЗ XI И

F п2 Рз1 v пз Рз° - xi Рз1 v xi Рз° - F41 F41 (Х1, Х2, ХЗ, Х4),

г) U1 U2 1Л По П1 П2 О, ПЗ Х1 И

F ПЗ F3° XI Р3° Р4° F4° (Х1, Х2, ХЗ , Х4).

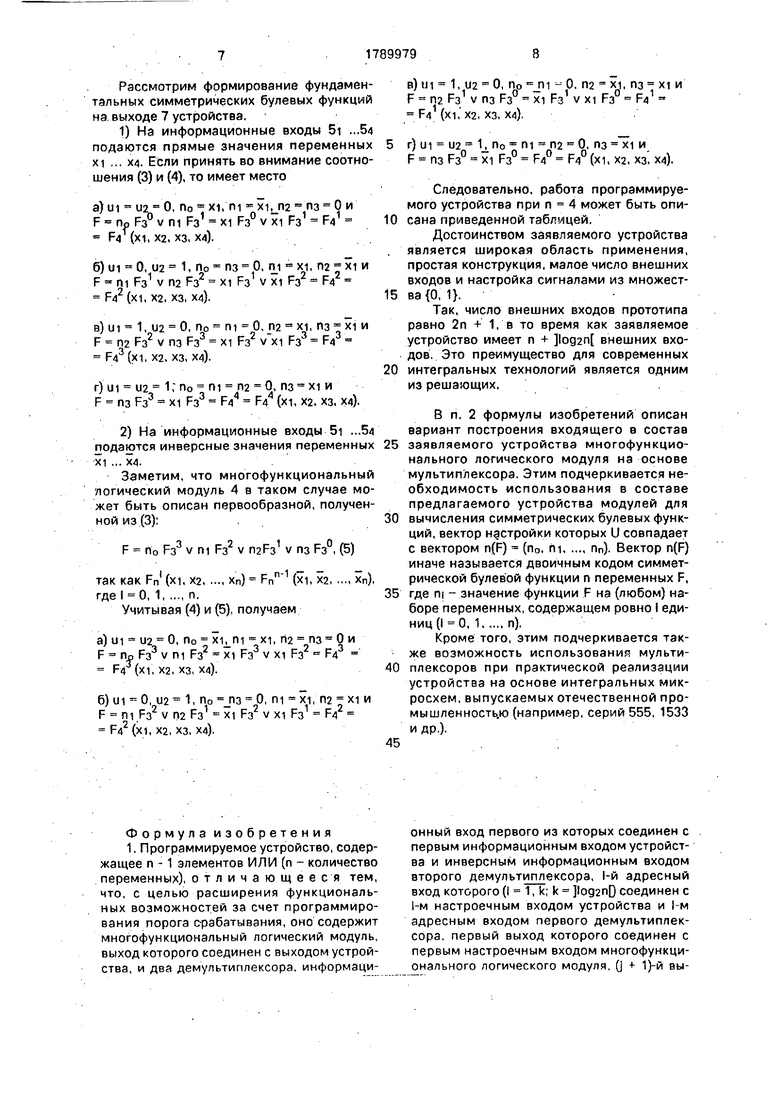

Следовательно, работа программируемого устройства при п 4 может быть опи- сана приведенной таблицей.

Достоинством заявляемого устройства

является широкая область применения,

простая конструкция, малое число внешних

входов и настройка сигналами из множества {0, 1}.

Так, число внешних входов прототипа равно 2п + 1, в то время как заявляемое устройство имеет n + log2n внешних входов. Это преимущество для современных интегральных технологий является одним из решающих,

В п. 2 формулы изобретений описан вариант построения входящего в состав

заявляемого устройства многофункционального логического модуля на основе мультиплексора. Этим подчеркивается необходимость использования в составе предлагаемого устройства модулей для

вычисления симметрических булевых функций, вектор настройки которых U совпадает с вектором n(F) (n0, ni, ..,, nn). Вектор n(F) иначе называется двоичным кодом симметрической булевой функции п переменных F,

где ni - значение функции F на (любом) наборе переменных, содержащем ровно i единиц (I 0, 1,.... п).

Кроме того, этим подчеркивается также возможность использования мультиплексоров при практической реализации устройства на основе интегральных микросхем, выпускаемых отечественной про- мышленностуо (например, серий 555, 1533 и др.).

.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления симметрических булевых функций | 1991 |

|

SU1833860A1 |

| Устройство для вычисления симметрических булевых функций | 1990 |

|

SU1748149A1 |

| Многофункциональный логический модуль | 1991 |

|

SU1793542A1 |

| Устройство для вычисления фундаментальных симметрических булевых функций | 1990 |

|

SU1730616A1 |

| Многофункциональный логический модуль | 1990 |

|

SU1753589A1 |

| Устройство для вычисления симметрических булевых функций | 1988 |

|

SU1587486A1 |

| Устройство для выделения симметрических булевых функций | 1991 |

|

SU1833859A1 |

| Устройство для вычисления симметрических булевых функций | 1989 |

|

SU1765818A1 |

| Устройство для вычисления симметрических булевых функций | 1989 |

|

SU1765819A1 |

| Устройство для вычисления симметрических булевых функций | 1989 |

|

SU1767496A1 |

Изобретение относится к вычислительной технике и микроэлектронике и может быть использовано при построении отказоустойчивых цифровых устройств и кодовых преобразователей. Цель изобретения- расширение функциональных возможностей устройства за счет программирования порога срабатывания, Поставленная цель достигается тем, что программируемое устройство содержит п - 1 (п - разрядность входного информационного слова) элементов ИЛИ, два демультиплексора и многофункциональный логический модуль. содержащий канальный мультиплексор. Программируемое устройство имеет п информационных входов, 1од2п настроечных входов и один выход. Устройство работает следующим образом. На информационные входы подаются двоичные переменные xi ... хп; на настроечные входы - сигналы настройки Ui... Uk (k JIoganQ,, значения которых принадлежат множеству{0,1}. Если(111,.... Uk)-двоичное представление числа г - 1, то на выходе устройства реализуется фундаментальная симметрическая булева функция Fnr (xi, ..., хп), где 1 r n.B том случае, когда на информационные входы подаются отрицания двоичных переменных xi, ..., хп, а на настроечные входы - двоичное представление числа п - t - 1, то на выходе устройства реализуется фундаментальная симметрическая булева функция Рп1-Рп1(х1, .... хп), гдеО 1 п- 1, 2 ил., 1 табл. ел С

Формула изобретения 1. Программируемое устройство, содержащее п -1 элементов ИЛИ (п - количество переменных), отличающееся тем, что, с целью расширения функциональных возможностей за счет программирования порога срабатывания, оно содержит многофункциональный логический модуль, выход которого соединен с выходом устройства, и два демультиплексора. информационный вход первого из которых соединен с первым информационным входом устройства и инверсным информационным входом второго демультиплексора. 1-й адресный вход которого (I 1, k; k log2nD соединен с l-м настроечным входом устройства и 1-м адресным входом первого демультиплексора, первый выход которого соединен с первым настроечным входом многофункционального логического модуля, Q + 1)-й выход первого демультиплексора 0 1, п - 1) соединен с первым входом j-ro элемента ИЛИ, второй вход которого соединен с J-M выходом второго демультиплексора, выход J-ro элемента ИЛИ соединен с (J + 1)-м настроечным входом многофункционального логического модуля, j-й информационный вход которого соединен с (| + 1}-м информационным входом устройства.

дуля, J-й информационный вход которого соединен с J-м адресным входом мультиплексора, первый информационный вход которого соединен с первым настроечным входом модуля (I + 1)-й на- строечный вход которого (I 1, п - 2) соединен с s-м информационным входом мультиплексора (s 2,2 - 1; I as,i + as,2 + ... + as,n-i, где as (as,i, asj .... as,n-i) - двоичное представление числа s, as,j e{0, 1}; j - 1, n - 1), 2пН-й информационный вход которого соединен с п-м настроечным входом модуля.

fti,

tOt10

b

VSL

HS

н

| Патент США № 4087786, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1993-01-23—Публикация

1991-01-24—Подача