а

со

СЛ 00 Ю

Изобретение относится к импульсной технике и микроэлектроники и предназначено для вычисления симметрических булевых функций (с.б.ф.) п переменных.

Цель изобретения - упрощение многофункционального логического модуля.

Многофункциональный логический модуль содержит п информационных шин, п + 1 шин настройки, одну выходную шину, две шины питания, п линеек логических ячеек и выполненные на МОП-тра нзисторах п элементов НЕ. Причем 1-я (I 1,2п) линейка

содержит n- i+1 логических ячеек, j-я Q 1,2) настроечная шина 1-й логической ячейки первой линейки соединена с (l+j-IJ-й шиной настройки модуля, а j-я настроечная шина k-й логической ячейки 1-й линейки (к 1,2n-l+1; I 2,3п) соединена с выходной шиной ()-й логической ячейки(1-1)-й линейки. Выходная шина логической ячейки n-й линейки соединена с выходной шиной модуля. Вторая информационная шина логических ячеек s-й (s 2р-1; р 1,2,...,п/2) линейки соединена с s-й информационной шиной модуля, а первая информационная шина логических ячеек v-й (v - 2r; r 1,2,...,n-ln/2) линейки соединена с v-й информационной шиной модуля. Входная шина 1-го элемента НЕ соединена с 1-й информационной шиной модуля, выходная шина s-ro элемента НЕ соединена с первой информационной шиной логических ячеек s-й линейки, а выходная шина v-ro элемента НЕ соединена с второй информационной шиной логических ячеек v-й линейки. Логические ячейки s-й линейки представляют собой выполненные на МОП-транзисторах элементы 2-2И-2ИЛИ-НЕ, логические элементы v-й линейки представляют собой выполненные на МОП-транзисторах элементы 2-2ИЛИ-2И-НЕ.

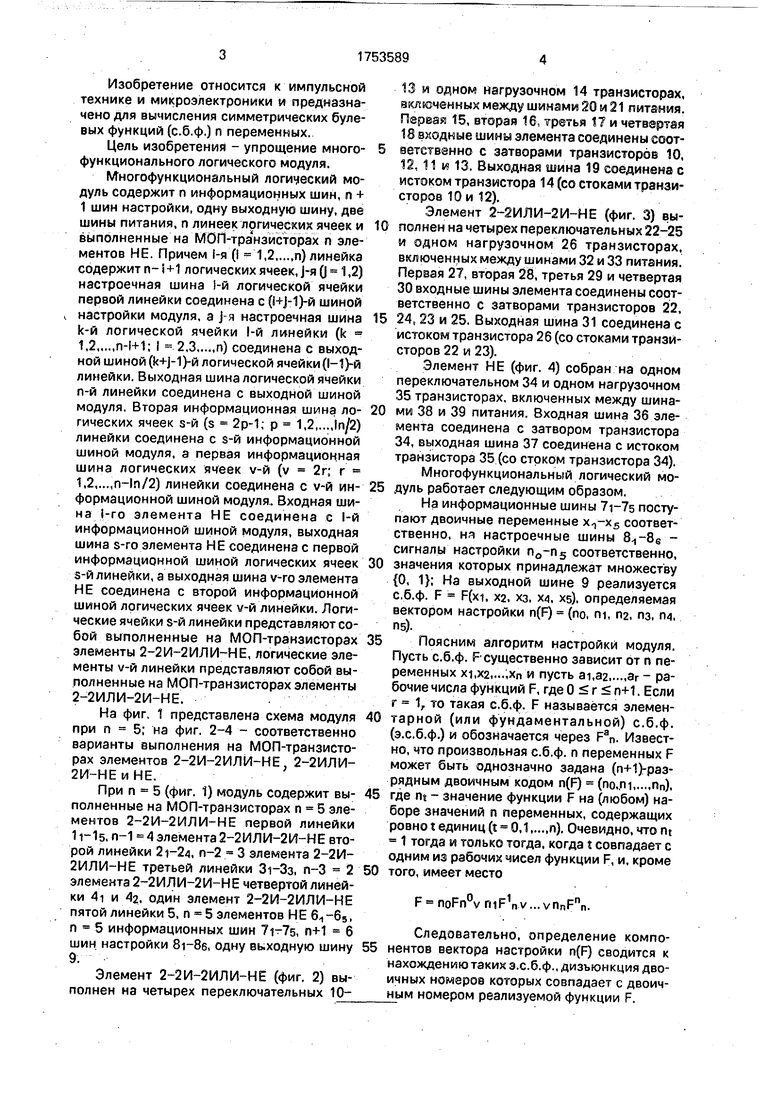

На фиг. 1 представлена схема модуля при п 5; на фиг. 2-4 - соответственно варианты выполнения на МОП-транзисторах элементов 2-2И-2ИЛИ-НЕ, 2-2ИЛИ- 2И-НЕиНЕ.

При п 5 (фиг. 1) модуль содержит выполненные на МОП-транзисторах п 5 элементов 2-2И-2ИЛИ-НЕ первой линейки 11-ls, л-1 4 элемента 2-2ИЛИ-2И-НЕ второй линейки 21-24, п-2 3 элемента 2-2И- 2ИЛИ-НЕ третьей линейки Si-Зз, п-3 2 элемента 2-2ИЛИ-2И-НЕ четвертой линейки 4i и 42, один элемент 2-2И-2ИЛИ-НЕ пятой линейки 5, п 5 элементов НЕ 6-t-65, п 5 информационных шин , п+1 б шин настройки 8i-8e, одну вь-ходную шину 9.

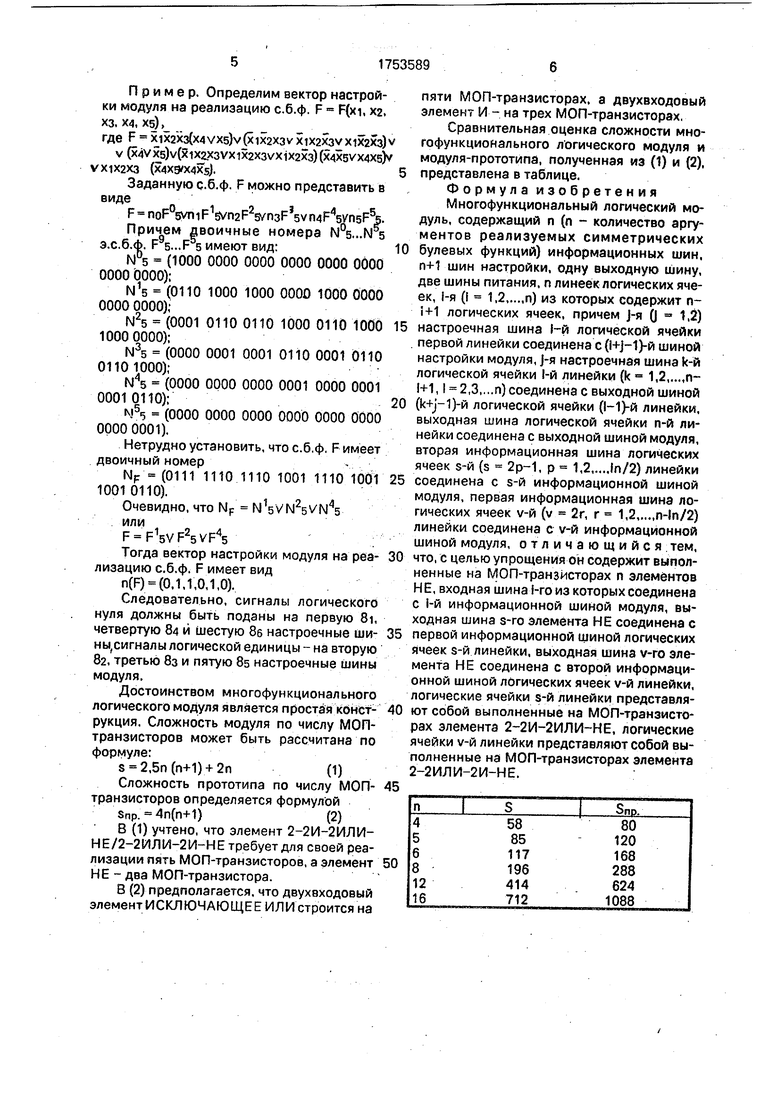

Элемент 2-2И-2ИЛИ-НЕ (фиг, 2) выполнен на четырех переключательных 1013 и одном нагрузочном 14 транзисторах, включенных между шинами 20 и 21 питания. Первая 15, вторая 16, третья 17 и четвертая 18 входные шины элемента соединены еоотаетственно с затворами транзисторов 10, 12,11 и 13. Выходная шина 19 соединена с истоком транзистора 14 (со стоками транзисторов 10 и 12).

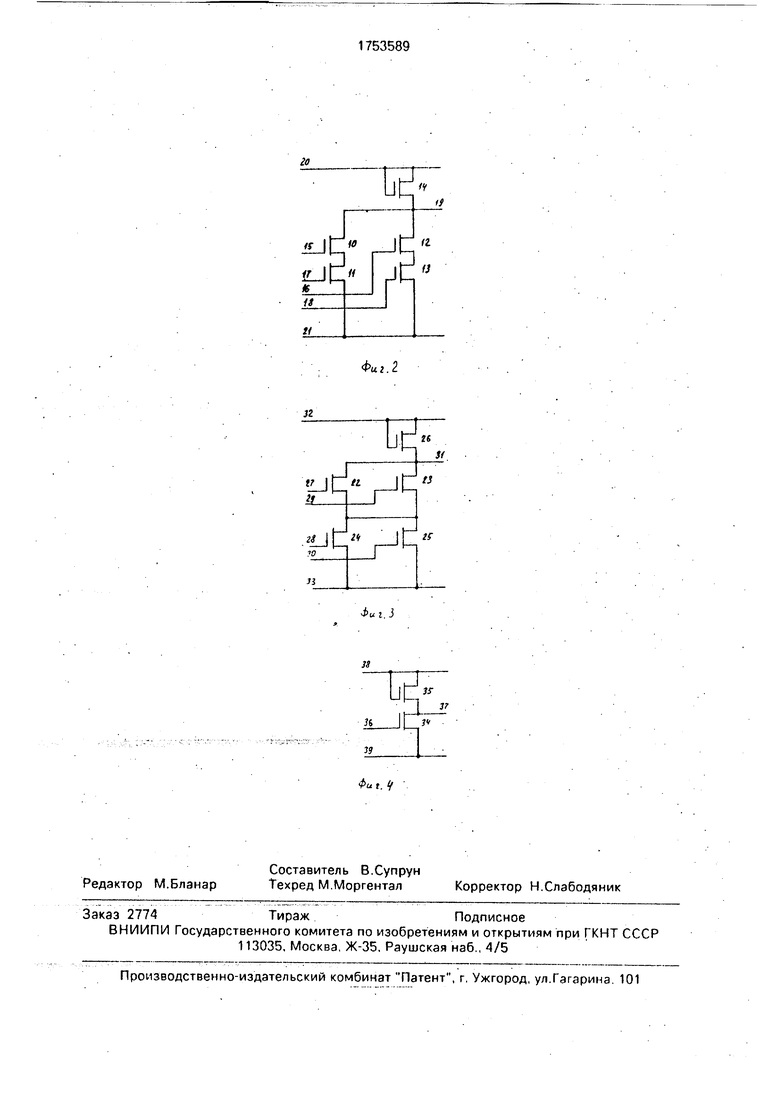

Элемент 2-2ИЛИ-2И-НЕ (фиг. 3) выполней на четырех переключательных 22-25 и одном нагрузочном 26 транзисторах, включенных между шинами 32 и 33 питания. Первая 27, вторая 28, третья 29 и четвертая 30 входные шины элемента соединены соответственно с затворами транзисторов 22,

24,23 и 25. Выходная шина 31 соединена с истоком транзистора 26 (со стоками транзисторов 22 и 23).

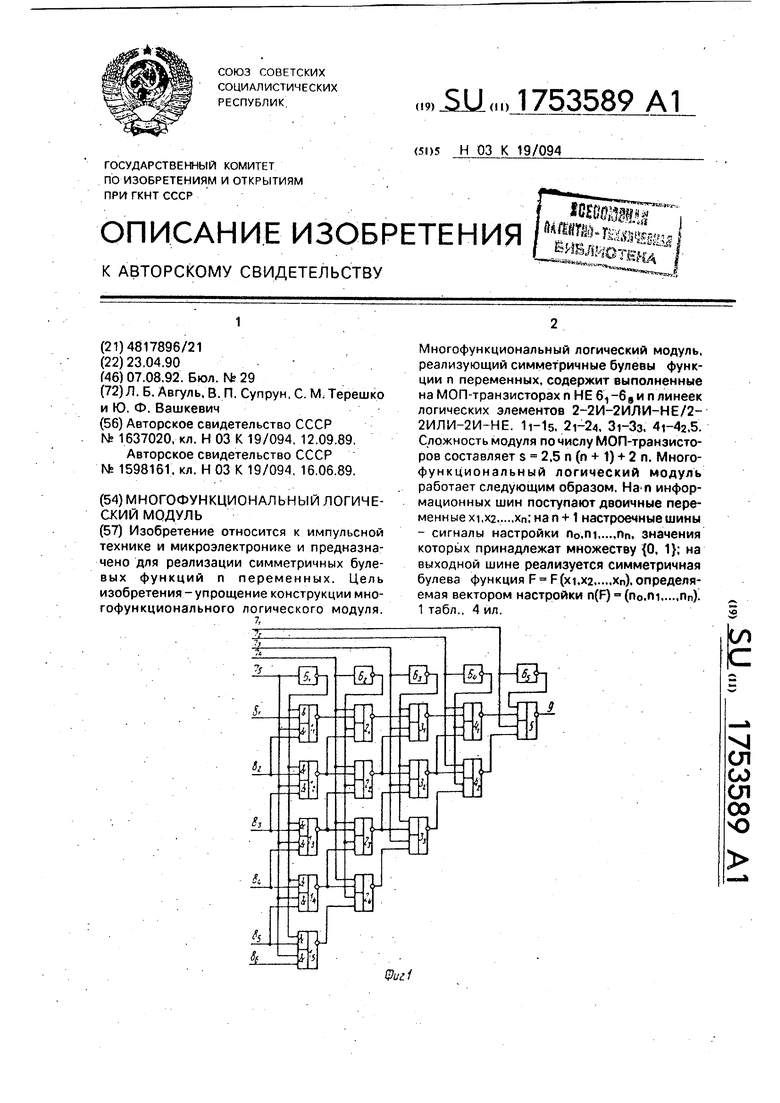

Элемент НЕ (фиг. 4) собран на одном переключательном 34 и одном нагрузочном 35 транзисторах, включенных между шинами 38 и 39 питания. Входная шина 36 элемента соединена с затвором транзистора 34, выходная шина 37 соединена с истоком транзистора 35 (со стоком транзистора 34). Многофункциональный логический модуль работает следующим образом.

На информационные шины 7i-7s поступают двоичные переменные хп-х5 соответственно, ня настроечные шины - сигналы настройки n0-ns соответственно,

значения которых принадлежат множеству {О, 1}; На выходной шине 9 реализуется с.б.ф. F F(xi, Х2, хз, Х4, хб), определяемая вектором настройки n(F) (no, ni, П2, пз, гц, ns).

Поясним алгоритм настройки модуля. Пусть с.б.ф. Р существенно зависит от п переменных xi,x2хп и пусть 31,32,...,аг - рабочие числа функций F, где 0 г п+1. Если г 1, то такая с.б.ф. F называется элементарной (или фундаментальной) с.б.ф. (э.с.б.ф.) и обозначается через Fan. Известно, что произвольная с.б.ф. п переменных F может быть однозначно задана (п+1)-разРЯДНЫМ ДВОИЧНЫМ КОДОМ n(F) (ПО,П1Пп),

где nt - значение функции F на (любом) наборе значений п переменных, содержащих

ровно t единиц (t 0,1п). Очевидно, что nt

1 тогда и только тогда, когда t совпадает с одним из рабочих чисел функции F, и, кроме

того, имеет место

F noFn°v niF n v... vnnFnn.

Следовательно, определение компо- нентов вектора настройки n(F) сводится к нахождению таких э.с.б.ф., дизъюнкция двоичных номеров которых совпадает с двоич- ным номером реализуемой функции F.

10

15

20

25

Пример. Определим вектор настройки модуля на реализацию с.б.ф. F F(xi, Х2,

ХЗ, Х4, Хб),

Где F X1X2X3(X4VX5)V(X1X2X3VX1X2X3VX1X2X3)V V (X4VX5)v(xiX2X3VX1X2X3VX1X2X3) (X4X5VX4X5)v X1X2X3 (Х4ХЭОС4Х5).

Заданную с.б.ф. F можно представить в виде

F noF°5VniF1Svn2F2s/n3F95Vn4F45Vn5F55.

Причем двоичные номера №s...N 5 э.с.б.ф. F 5-..F 5 имеют вид:

NTs (ЮОО 0000 0000 0000 0000 0000 0000 0000);

N 5 (0110 1000 1000 0000 1000 0000

00000000);

N25 (0001 0110 0110 1000 0110 1000 10000000);

N3s (0000 0001 0001 0110 0001 0110 01101000);

N4s - (0000 0000 0000 0001 0000 0001

00010110);

N55 (0000 0000 0000 0000 0000 0000 0000 0001).

Нетрудно установить, что с.б.ф. F имеет двоичный номер

NF - (0111 1110 1110 1001 1110 1001 1001 0110).

Очевидно, что NF N15VN25VN45

или

F F15VF25VF45

Тогда вектор настройки модуля на pea- 30 лизацию с.б.ф. F имеет вид

n(F) (0,1,1,0,1,0).

Следовательно, сигналы логического нуля должны быть поданы на первую 8i, четвертую 84 и шестую 8е настроечные ши- 35 ны,сигналы логической единицы - на вторую 82, третью 8з и пятую 8s настроечные шины модуля.

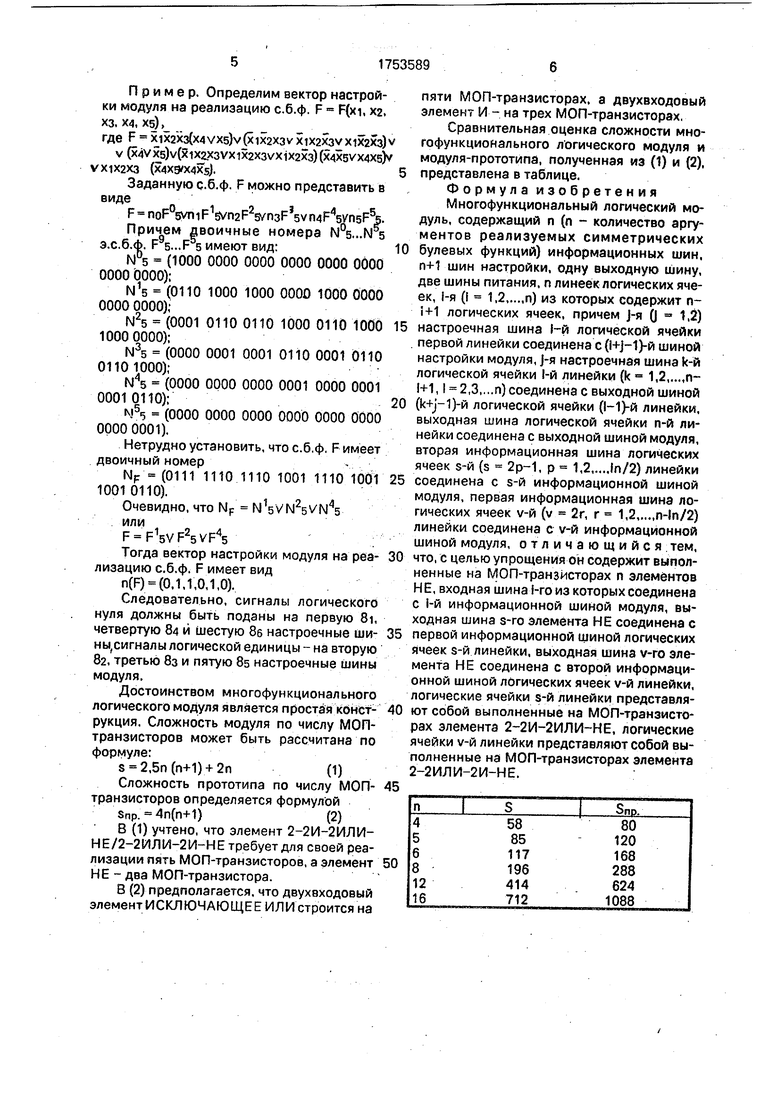

Достоинством многофункционального логического модуля является простая конст- 40 рукция. Сложность модуля по числу МОП- транзисторов может быть рассчитана по формуле:

s 2,5n(n+1) + 2n(1)

Сложность прототипа по числу МОП- 45 транзисторов определяется формулой

Snp. 4n(n+1)(2)

В (1) учтено, что элемент 2-2И-2ИЛИ- НЕ/2-2ИЛИ-2И-НЕ требует для своей реализации пять МОП-транзисторов, а элемент 50 НЕ - два МОП-транзистора.

В (2) предполагается, что двухвходовый элементИСКЛЮЧАЮЩЕЕ ИЛИ строится на

0

5

0

5

0

5

0

пяти МОП-транзисторах, а двухвходовый элемент И - на трех МОП-транзисторах,

Сравнительная оценка сложности многофункционального логического модуля и модуля-прототипа, полученная из (1) и (2), представлена в таблице.

Формула изобретения Многофункциональный логический модуль, содержащий п (п - количество аргументов реализуемых симметрических булевых функций) информационных шин, п+1 шин настройки, одну выходную шину, две шины питания, п линеек логических ячеек, 1-я (i 1.2п) из которых содержит пi+1 логических ячеек, причем j-я (J 1,2) настроечная шина 1-й логической ячейки первой линейки соединена с (1+)-1)-й шиной настройки модуля, j-я настроечная шина к-й логической ячейки 1-й линейки (к 1,2,...,п- 1+1,1 2,3,...п) соединена с выходной шиной ()-й логической ячейки (1-1)-й линейки, выходная шина логической ячейки n-й линейки соединена с выходной шиной модуля, вторая информационная шина логических ячеек s-й (s 2р-1, р 1,2,.,.,1п/2) линейки соединена с s-й информационной шиной модуля, первая информационная шина логических ячеек v-й (v 2r, г 1,2n-ln/2)

линейки соединена с v-й информационной шиной модуля, отличающийся тем, что, с целью упрощения он содержит выполненные на МОП-транзисторах п элементов НЕ, входная шина 1-го из которых соединена с i-й информационной шиной модуля, выходная шина s-го элемента НЕ соединена с первой информационной шиной логических ячеек s-й линейки, выходная шина v-ro элемента НЕ соединена с второй информационной шиной логических ячеек v-й линейки, логические ячейки s-й линейки представляют собой выполненные на МОП-транзисторах элемента 2-2И-2ИЛИ-НЕ, логические ячейки v-й линейки представляют собой выполненные на МОП-транзисторах элемента 2-2ИЛИ-2И-НЕ.

го

ТО

if

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофункциональный логический модуль | 1991 |

|

SU1793542A1 |

| Многофункциональный логический модуль | 1989 |

|

SU1676093A1 |

| Многофункциональный логический модуль | 1989 |

|

SU1598161A1 |

| Многофункциональный логический модуль | 1990 |

|

SU1732462A1 |

| Устройство для вычисления симметрических булевых функций | 1990 |

|

SU1742811A1 |

| Универсальный логический модуль | 1985 |

|

SU1264336A1 |

| Многофункциональный логический модуль | 1989 |

|

SU1637020A1 |

| Устройство для вычисления симметрических булевых функций | 1988 |

|

SU1559337A1 |

| Многовходовый логический модуль | 1990 |

|

SU1793547A1 |

| Мультиплексор | 1990 |

|

SU1774491A1 |

Изобретение относится к импульсной технике и микроэлектронике и предназначено для реализации симметричных булевых функций п переменных. Цель изобретения - упрощение конструкции многофункционального логического модуля. 7Многофункциональный логический модуль, реализующий симметричные булевы функции п переменных, содержит выполненные на МОП-транзисторах п НЕ 6.) -6 9 и п линеек логических элементов 2-2И-2ИЛИ-НЕ/2- 2ИЛИ-2И-НЕ. 1i-15, 2i-24, . 4i-42,5. Сложность модуля по числу МОП-транзисторов составляет s 2,5 n (n + t) + 2 п. Много- функциональный логический модуль работает следующим образом. Нз П информационных шин поступают двоичные переменные xi,x2хп;нап+1 настроечные шины - сигналы настройки n0.ni,...,rin, значения которых принадлежат множеству {0, 1}; на выходной шине реализуется симметричная булева функция F F(xi,X2хп), определяемая вектором настройки n(F) (n0,ninn). 1 табл., 4 ил. сл с

«J

ю

Jp r-J

О|

а

ts

Л

ТЕ

3f

ZZL

J7

| Многофункциональный логический модуль | 1989 |

|

SU1637020A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Многофункциональный логический модуль | 1989 |

|

SU1598161A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-08-07—Публикация

1990-04-23—Подача