Изобретение относится к импульсной технике и микроэлектронике и предназначено для вычисления симметрических булевых функций (с.б.ф) п переменных.

Известен многофункциональный логический модуль на МОП-транзисторах, содержащий п линеек элементов И и п линеек элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 1.

Недостатками модуля являются высокая конструктивная сложность (по числу МОП-транзисторов) и низкое быстродействие, определяемое глубиной схемы и равное 2л т, где т - задержка на вентиль.

Наиболее близким по функциональным возможностям и конструкции техническим решением к предлагаемому является многофункциональный логический модуль, реализующий с.б.ф п переменных и содержащий выполненные на МОП-транзисторах п элементов НЕ и п линеек элементов 2-2ИЛИ- 2И-НЕ/2-2И-2ИЛИ-НЕ 2.

Недостатком известного модуля является низкое быстродействие, определяемое глубиной схемы и равное (n+1) r .

Цель изобретения - повышение быстродействия многофункционального логического модуля.

Цель достигается тем, что в многофункциональный логический модуль на МОП- транзисторах, содержащий n (, n - количество аргументов реализуемых функций) информационных шин, п+1 шин настройки, две шины питания, выходную шину и г элементов И, введены г линеек элементов 3-2И-ЗИЛИ, 1-я (,2,...,г) из которых содержит n-2i+1 элементов 3-2И-ЗИЛИ, г элементов ИЛИ-НЕ и г элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, k-й (,2) вход 1-го из которых соединен с (21+к-2)-й информационной шиной модуля, k-м входом 1-го элемента И и k-м входом 1-го элемента ИЛИ-НЕ, выход которого соединен с первым входом J-ro ,2,...,n-2i+1) элемента 3-2И-ЗИЛИ 1-й линейки, второй вход которого соединен с выходом 1-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, третий вход соединен с выходом 1-го элемента И. (Е+3)-й (,2,3) вход s-го (,2,...,n- -1) элемента 3-2И-ЗИЛИ первой линейки соединен с (Ј+з+1)-й шиной настройки модуVI

ю

со ел .fcb ю

ля, ({+3)-й вход v-ro элемента 3-2И-ЗИЛИ (р+1)-й линейки (v n-2p-1; p-1,2...,r-1) соединен с выходом (fr-v-1)-ro элемента 3-2И- ЗИЛИ р-й линейки, выход элемента 3-2И-ЗИЛИ г-и линейки соединен с выходной шиной модуля.

Многофункциональный логический модуль на МОП-транзисторах содержит п (, n - количество аргументов реализуемых функций) информационных шин, п+1 шин настройки, две шины питания, выходную шину, г элементов И, г линеек элементов 3-2И-ЗИЛИ, 1-я (,2,.,,,r) из которых содержит n-2i+1 элементов 3-2И-ЗИЛИ. г элементов ИЛИ-НЕ и г элементов ИСКЛЮЧАЮЩЕЕ ИЛИ. Причем k-й (k-1,2) вход 1-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с (2i+.k-2)-u информационной шиной модуля, k-м входом 1-го элемента И и k-м входом 1-го элемента ИЛИ-НЕ. Выход 1-го элемента ИЛИ-НЕ соединен с первым входом j-ro ,2,...,n-2i+1) элемента 3-2И-ЗИЛИ 1-й линейки, второй вход которого соединен с выходом 1-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, третий вход соединен с выходом 1-го элемента И. Далее (В-З)-й (1М,2,3) вход s-ro (s: 1,2,...,п-1.) элемента 3-2И-ЗИЛИ первой линейки соединен с (Е+з-1)-й шиной настройки модуля, а (Ј+3)-й вход v-ro элемента 3-2И-ЗИЛИ (р+1)-й линейки (v n-2p-1; ,2,.,.,г-1) соединен с выходом (t+v-1)-го элемента 3-2И-ЗИЛИ р-й линейки. Выход элемента 3-2И-ЗИЛИ r-й линейки соединен с выходной шиной модуля.

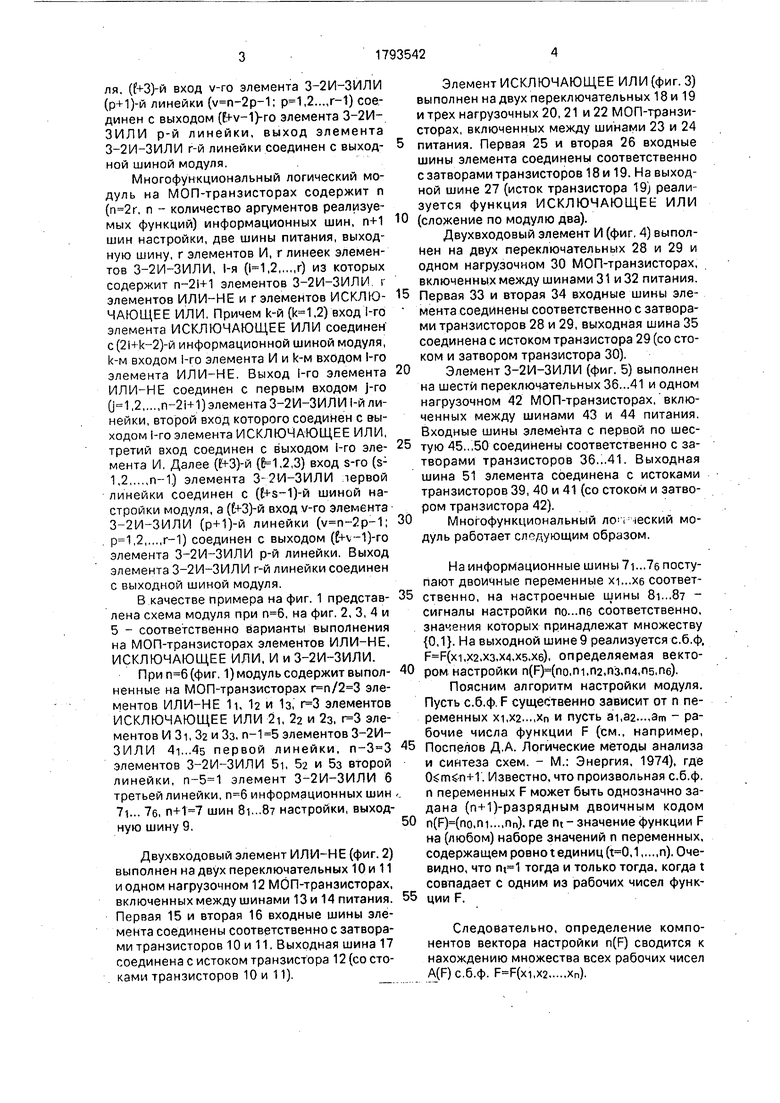

В качестве примера на фиг. 1 представлена схема модуля при , на фиг. 2, 3, 4 и 5 - соответственно варианты выполнения на МОП-транзисторах элементов ИЛИ-НЕ, ИСКЛЮЧАЮЩЕЕ ИЛИ, И и 3-2И-ЗИЛИ.

(фиг. 1) модуль содержит выполненные на МОП-транзисторах элементов ИЛИ-НЕ 1i, 12 и 1з, элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 2i, 2г и 2з, элементов И 3i, Зг и Зз, элементов 3-2И- ЗИЛИ 4i...4s первой линейки, элементов 3-2И-ЗИЛИ 5i, 62 и 5з второй линейки, элемент 3-2И-ЗИЛИ 6 третьей линейки, информационных шин 7i... 7е, шин 81...8 настройки, выходную шину 9.

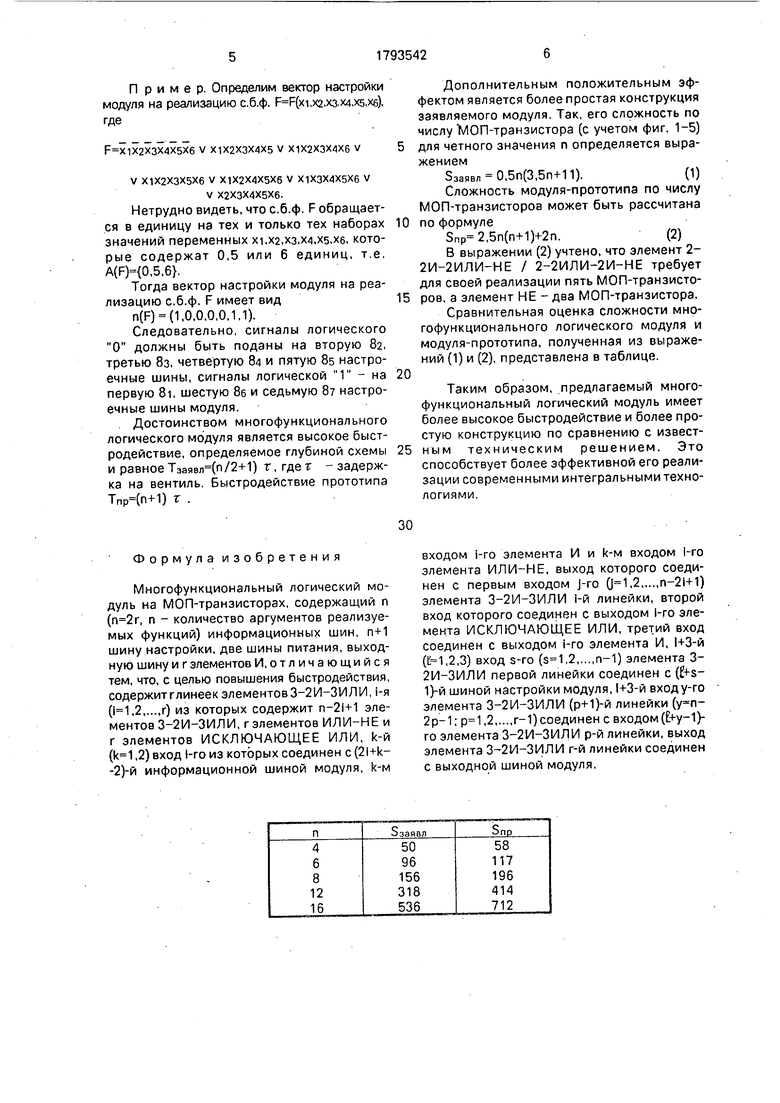

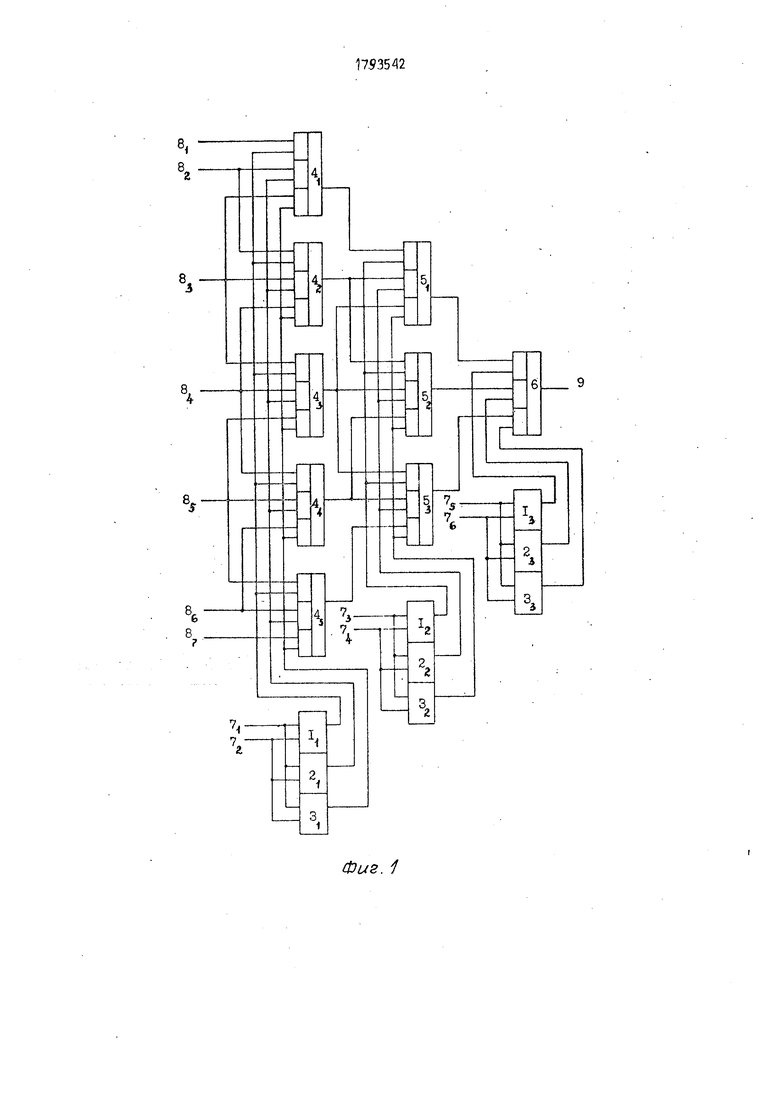

Двухвходовый элемент ИЛИ-НЕ (фиг. 2) выполнен на двух переключательных 10 и 11 йодном нагрузочном 12 МОП-транзисторах, включенных между шинами 13 и 14 питания. Первая 15 и вторая 16 входные шины элемента соединены соответственно с затворами транзисторов 10 и 11. Выходная шина 17 соединена с истоком транзистора 12 (со стоками транзисторов 10 и 11).

Элемент ИСКЛЮЧАЮЩЕЕ ИЛИ (фиг. 3) выполнен на двух переключательных 18 и 19 и трех нагрузочных 20,21 и 22 МОП-транзисторах, включенных между шинами 23 и 24

питания. Первая 25 и вторая 26 входные шины элемента соединены соответственно с затворами транзисторов 18и 19. На выходной шине 27 (исток транзистора 19) реализуется функция ИСКЛЮЧАЮЩЕЕ ИЛИ

(сложение по модулю два).

Двухвходовый элемент И (фиг. 4) выполнен на двух переключательных 28 и 29 и одном нагрузочном 30 МОП-транзисторах, включенных между шинами 31 и 32 питания.

Первая 33 и вторая 34 входные шины эле- мента соединены соответственно с затворами транзисторов 28 и 29, выходная шина 35 соединена с истоком транзистора 29 (со стоком и затвором транзистора 30).

Элемент 3-2И-ЗИЛИ (фиг. 5) выполнен на шести переключательных 36...41 и одном нагрузочном 42 МОП-транзисторах, включенных между шинами 43 и 44 питания. Входные шины элемента с первой по шестую 45..,50 соединены соответственно с затворами транзисторов 36.„41. Выходная шина 51 элемента соединена с истоками транзисторов 39, 40 и 41 (со стоком и затвором транзистора 42).

Многофункциональный ло гческий модуль работает следующим образом.

На информационные шины 7i...7e поступают двоичные переменные xi...X6 соответ- ственно, на настроечные шины 8i...8 - сигналы настройки по...пе соответственно, значения которых принадлежат множеству {0,1}. На выходной шине 9 реализуется с.б.ф. (xi,x2.X3,x4,X5,x6), определяемая векторОМ НаСТрОЙКИ п(Р)(по,П1,П2,ПЗ,П4,П5,Пб).

Поясним алгоритм настройки модуля. Пусть с.б.ф. F существенно зависит от п переменных Х1,Х2...,Хп И ПуСТЬ 31,32...,3т - РЗ- бочие числа функции F (см., например,

Поспелов Д.А. Логические методы анализа и синтеза схем. - М.: Энергия, 1974), где . Известно, что произвольная с.б.ф. п переменных F может быть однозначно задана (п+1)-разрядным двоичным кодом

n(F)(no,ni...,nn), где nt-знзчение функции F на (любом) наборе значений п переменных, содержащем ровно1единиц 0,1,...,п), Очевидно, что тогда и только тогда, когда t совпадает с одним из рабочих чисел функции F.

Следовательно, определение компонентов вектора настройки n(F) сводится к нахождению множества всех рабочих чисел A(F) с.б.ф. (xi,X2,...,xn).

Пример. Определим вектор настройки модуля на реализацию с.б.ф. (х1,Х2,хз.Х4,х5,хб), где

F X1X2X3X4X5X6 V Х1Х2ХЗХ4Х5 V Х1Х2ХЗХ4Х6 V

V Х1Х2ХЗХ5Х6 V Х1Х2Х4Х5Х6 V Х1ХЗХ4Х5Х6 V V Х2ХЗХ4Х5Х6.

Нетрудно видеть, что с.б.ф. F обращается в единицу на тех и только тех наборах значений переменных Х1,Х2,хз,х4,х5,Хб. которые содержат 0,5 или 6 единиц, т.е, A(F){0,5,6}.

Тогда вектор настройки модуля на реализацию с.б.ф. F имеет вид

n(F) (1,0,0.0.0.1.1).

Следовательно, сигналы логического О должны быть поданы на вторую 82, третью 8з, четвертую 8з и пятую 8s настроечные шины, сигналы логической 1 - на первую 8i, шестую 8б и седьмую 8 настроечные шины модуля.

. Достоинством многофункционального логического модуля является высокое быстродействие, определяемое глубиной схемы и равное Тзаявл(п/2+1) г, где г - задержка на вентиль. Быстродействие прототипа Тпр(п+1) г .

0

5

0

5

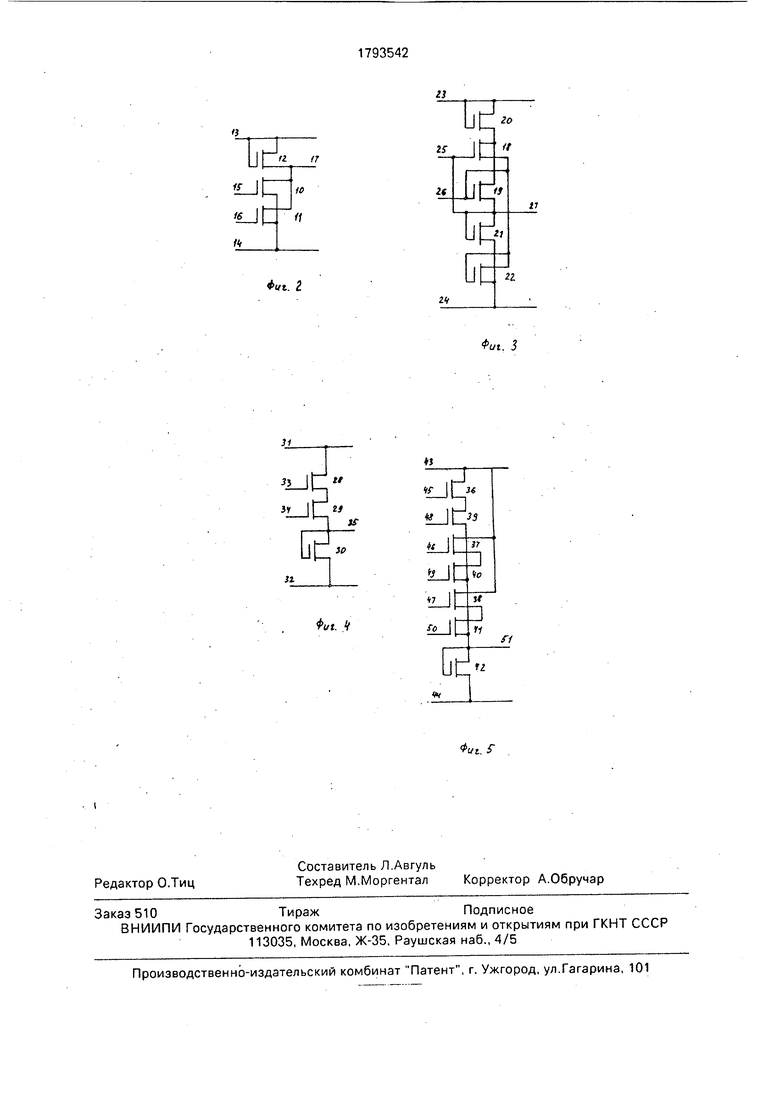

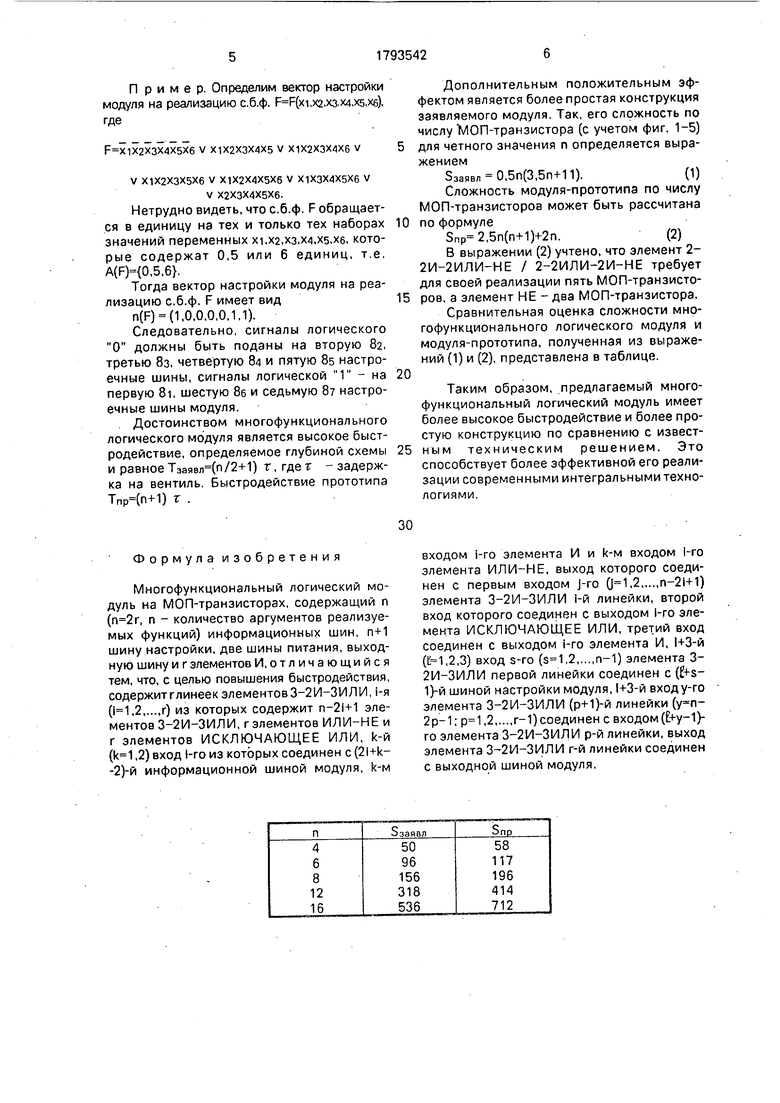

Дополнительным положительным эффектом является более простая конструкция заявляемого модуля. Так, его сложность по числу МОП-транзистора (с учетом фиг, 1-5) для четного значения п определяется выражением

5заявл 0,5п(3,5п + 11).(1)

Сложность модуля-прототипа по числу МОП-транзисторов может быть рассчитана по формуле

,5n(n+1)+2n.(2)

В выражении (2) учтено, что элемент 2- 2И-2ИЛИ-НЕ / 2-2ИЛИ-2И-НЕ требует для своей реализации пять МОП-транзисторов, а элемент НЕ -два МОП-транзистора,

Сравнительная оценка сложности многофункционального логического модуля и модуля-прототипа, полученная из выражений (1) и (2), представлена в таблице.

Таким образом, предлагаемый многофункциональный логический модуль имеет более высокое быстродействие и более простую конструкцию по сравнению с известным техническим решением. Это способствует более эффективной его реализации современными интегральными технологиями.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофункциональный логический модуль | 1990 |

|

SU1753589A1 |

| Многовходовый логический модуль | 1990 |

|

SU1793547A1 |

| Многофункциональный логический модуль | 1989 |

|

SU1676093A1 |

| Устройство для вычисления симметрических булевых функций | 1990 |

|

SU1748150A1 |

| Многофункциональный логический модуль | 1989 |

|

SU1637020A1 |

| Многофункциональный логический модуль | 1990 |

|

SU1732462A1 |

| Многофункциональный логический модуль | 1989 |

|

SU1598161A1 |

| Мультиплексор | 1990 |

|

SU1780185A1 |

| Мультиплексор | 1990 |

|

SU1774491A1 |

| Универсальный логический модуль | 1985 |

|

SU1264336A1 |

Изобретение относится к импульсной технике и микроэлектронике и предназначено для реализации симметрических булевых функций п переменных. Сущность изобретения: цель достигается тем, что много- функциональный логический модуль содержит r(, n - количество переменных реализуемых функций) элементов ИЛИ-НЕ, г элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, г элементов И, г линеек элементов 3-2И-ЗИЛИ, п информационных шин, л+1 шин настройки, две тины питания и выходную шину. Сложность модуля по числу МОП-транзисторов составляет 0,5п(3,5п+11), а быстродействие, определяемое глубиной схемы, равно п/2+1. 1 табл., 5 ил.

Формула изобретения

Многофункциональный логический модуль на МОП-транзисторах, содержащий п (, n - количество аргументов реализуемых функций) информационных шин, п+1 шину настройки, две шины питания, выходную шину и г элементов И, отличающийся тем, что, с целью повышения быстродействия, содержит г линеек элементов 3-2И-ЗИ Л И, i-я (,2,....г) из которых содержит n-2i+1 элементов 3-2И-ЗИЛИ, г элементов ИЛИ-НЕ и г элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, k-й (,2) вход 1-го из которых соединен с (2i+k- -2)-й информационной шиной модуля, k-м

входом 1-го элемента И и k-м входом 1-го элемента ИЛИ-НЕ, выход которого соединен с первым входом J-ro .2,...,n-2i+1) элемента 3-2И-ЗИЛИ i-й линейки, второй вход которого соединен с выходом 1-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, третий вход соединен с выходом i-ro элемента И. 1+3-й (Ы,2,3) вход s-го (,2,...,n-1) элемента 3- 2И-ЗИЛИ первой линейки соединен с (Ј+s- 1)-й шиной настройки модуля, l+3-й входу-го элемента 3-2И-ЗИЛИ (р+1)-й линейки ( 2р-1;р 1,2,...,г-1) соединен с входом (Е+у-1)- го элемента 3-2И-ЗИЛИ р-й линейки, выход элемента 3-2И-ЗИЛИ г-й линейки соединен с выходной шиной модуля.

C-J

tn

СП

« rtut. .4

7

Ijf

«

f1

&

41

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Многофункциональный логический модуль | 1989 |

|

SU1598161A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Многофункциональный логический модуль | 1990 |

|

SU1753589A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Способ приготовления консистентных мазей | 1919 |

|

SU1990A1 |

| МНОГОФУНКЦИОНАЛЬНЫЙ ЛОГИЧЕСКИЙ МОДУЛЬ | |||

Авторы

Даты

1993-02-07—Публикация

1991-03-07—Подача