fc

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь телевизионных стандартов | 1987 |

|

SU1506591A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1987 |

|

SU1494778A1 |

| СПОСОБ ДЛЯ ЦИФРОВОЙ СУБСТРАКЦИОННОЙ АНГИОГРАФИИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1992 |

|

RU2043073C1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ ВИДЕОСИГНАЛА | 1992 |

|

RU2027315C1 |

| Блок буферной памяти для терминального устройства | 1989 |

|

SU1633454A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1987 |

|

SU1522271A1 |

| Устройство для регистрации динамических процессов | 1989 |

|

SU1702358A1 |

| Устройство формирования сигнала для коррекции искажений телевизионного изображения | 1985 |

|

SU1317687A2 |

| Устройство для отображения информации на экране телевизионного приемника | 1986 |

|

SU1410717A1 |

| Устройство для воспроизведения изображения | 1980 |

|

SU1085014A1 |

Использование: техника телевидения, системы неразрушающего контроля, выполненных, в частности, на базе пировйдикона. Сущность изобретения: устройство содержит аналого-цифровой преобразователь 1, два коммутатора 2 и 3, блок памяти 4, арифметический блок 5, блок синхронизации 6. блок задания режимов 7 и два элемента ИЛИ 8 и 9. Видеосигнал преобразуется в дискретный код, запоминается в блоке памяти на время длительности кадра и вычитается из следующего кадра. При записи стоп-кадра в блок памяти вначале заносится первый кадр, затем результат вычитания, который хранится параллельно с записью - считывания текущей информации. 1-2-4-5- 3,5-3, 7-6-4, 7-2. 1-5, 7-8. 7-9, 6-7, &-1, 6-8-1, 6-9-4-3, 5-2. 1 .ф-лы, 2 ил.

СА

Изобретение относится к технике телевидения и может быть использовано в системах неразрушающего контроля, выполненных, в частности, на базе пирови- дикона, ; , :. ; , :.

Ближайшим к заявляемому устройству по своей jexHHHecKou сущности является ус- тройств8Г б;йё ржащее аналого-цифровой преобразователь (АЦП) арифметико-логический блок, п 0га%ре меннр выполняющий функции Bbt4HTaTeflj и входного коммутатора, выходной коммутатор и блок памяти, содержащий в себе узел синхронизации. В зави- си мости от того, какой кадр поступает на сигнальный вход устройства, в блок памяти поочередно заносится текущий либо ре- зультатирующий кадры, а считываются, соответственно, результэтирующий либо предыдущий кадры. Выходной коммутатор выдает результатирующий кадр, с блоков, соответственно, памяти либо арифметико- логического. ,Г--/Несмотря на наличие в устройстве избыточного объема памяти, связанного со схемной организацией его динамических узлов памяти, в устройстве отсутствуют средства хранения стоп-кадра (исходного либо эталонного) параллельно с обработкой текущего видеосигнала, что необходимо для оперативного контроля процесса изменения теплового изображения. Кроме тйго, работа осуществляется только в режиме обтюрации, в то время, как видеосигнал может пбступать и в режиме панорамирования . ..-.-,;.- .:.-.... . ... .:;

Целью изобретения является расширение функциональных возможностей устройства путем обеспечения преобразования сигнала в режиме хранения стоп-кадра.

Поставленная цель достигается тем, что в устройство для преобразования видеосигнала, содержащее последовательно соединенные АЦП, 2 входа которого - соответственно сигнальный и управляющий входы устройства, арифметический блок и первый коммутатор, второй вход которого соединен со вторым входом арифметического блока и выходом блока памяти, синх- ровход которого соединен с первым выходом блока синхронизации, а выход пер- його коммутатора - сигнальный выход устройства, введены второй коммутатор, первый сигнальный вход которого соединен с выходом АЦП, а выход - с информационным входом блока памяти, блок задания режимов, первые 4 входа которого - соответственно первый управляющий вход, входы записи и чтения, второй управляющий вход устройства, а первый выход соединен с управляющим входом второго

0

коммутатора, и 2 элемента ИЛИ, первые входы которых соединены со вторым выходом блока задания режимов, третий выход которого соединен с входом блока синхронизации, второй и третий выходы которого соединены соответственно с тактовым входом АЦП и синхровходом блока задания режимов, четвертый выход которого соединен с управляющим входом первого коммутатора, первый вход которого соединен со вторым сигнальным входом второго коммутатора, причем вторые входы элементов ИЛИ соединены с четвертым и пятым выходами блока синхронизации, а выходы - с первым и вто- 5 рым входами записи блока памяти.

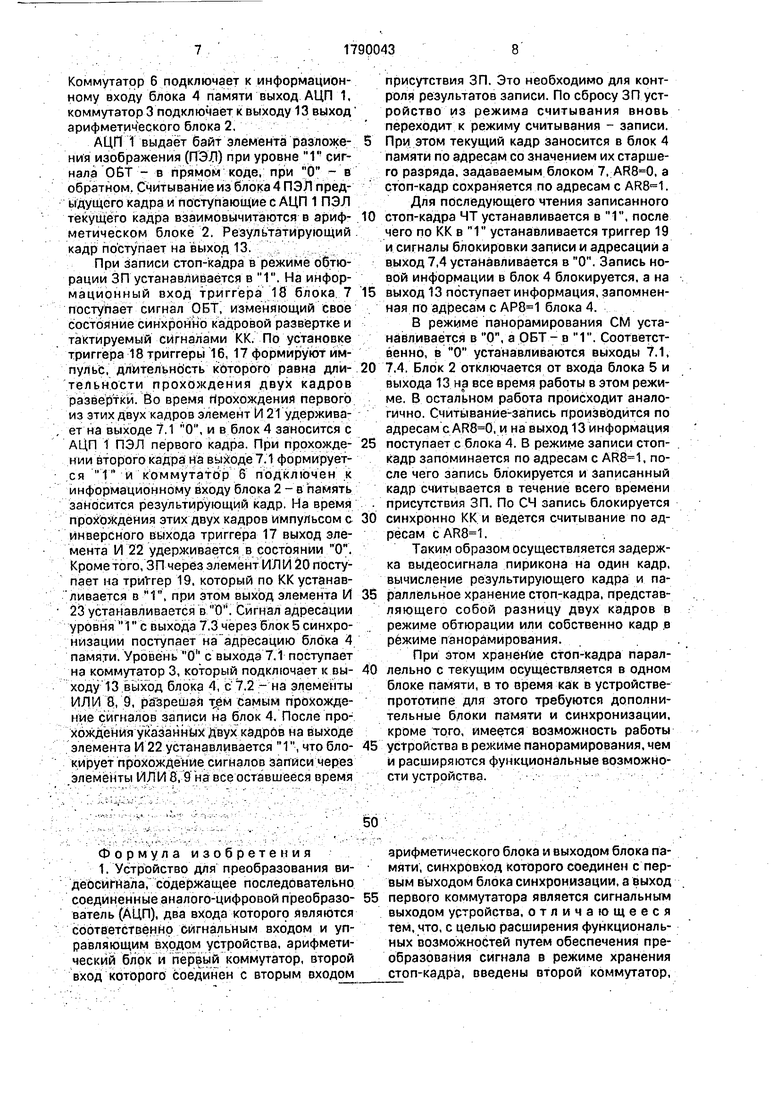

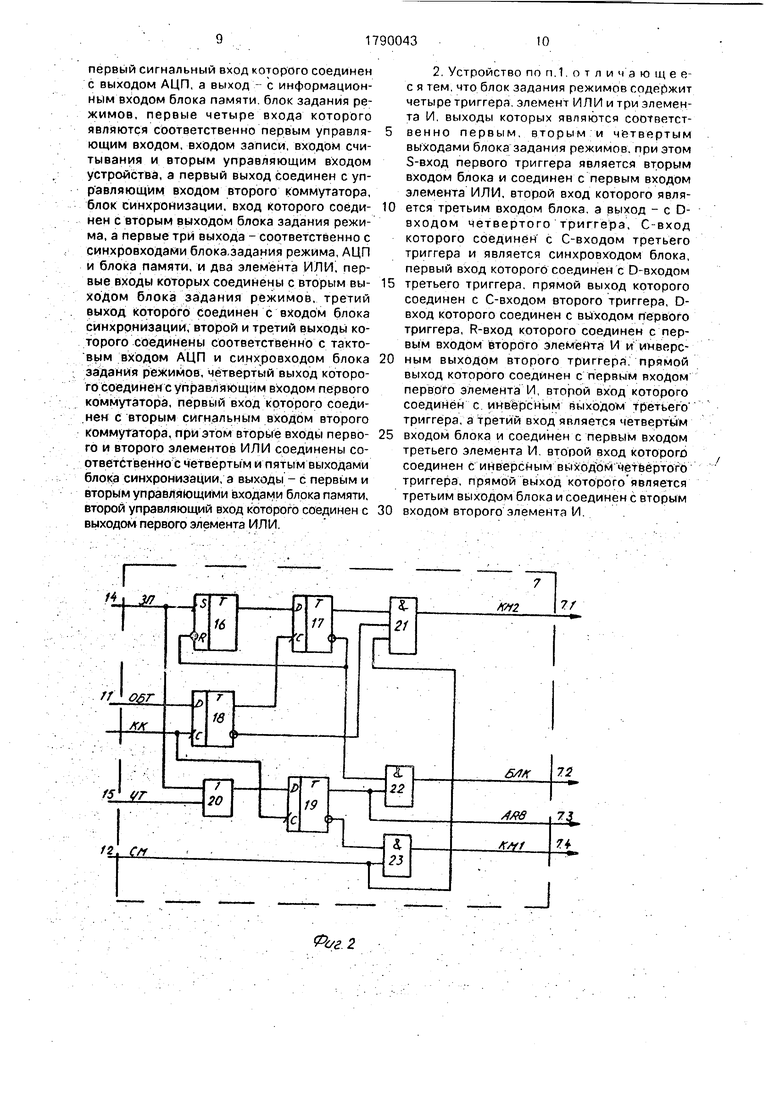

Блок задания режимов содержит 4 триггера, элемент ИЛИ и 3 элемента И, выходы которых - первый, второй и четвертый выходы блока, S-вход первого триггера - второй вход блока, соединенный с первым входом элемента ИЛИ, второй вход которого - третий вход блока, а выход соединен с D-вхо- дом четвёртого триггера; С-вход которого соединен с С-вхОдом третьего триггера и является синхровходом блока, D-вход третьего триггера - первый вход блока, а прямой выход соединен с С-входом второго триггера, D-вход которого соединен с выходом первого, которого соединен с первым входом второго элемента И и инверсным выходом второго триггера, прямой выход которого соединен с первым входом первого элемента И, второй вход которого соединен с инверсным .выходом третьего триггера, а третий - четвертый вход блока и соединён с пергвым входом третьего элемента И, второй вход которого соединен с инверсным выходом четвертого триггера, прямой выход которого - третий выход блока, соединенный со вторым входом второго элемента И. ; г

С учетом того, что устройства для цифровой обработки видеосигнала гшрикона отечественной промышленностью серийно не выпускаются, а известные решения не обеспечивают возможности хранения стоп- кадра параллельно с обработкой текущего кадра без существенного усложнения устройстве за счет увеличения конструктивного объема его блока памяти, а также не предусматривают переадресацию обрабатываемой информации в режиме считывание-модификация-запись, новая совокупность известных элементов позволяет расширить функциональные возможности оперативного контроля процесса изменения изображения и работы в режимах как обтюрации, так и панорамирования. Это достигается за счет введения таких новых существенных признаков, как второй коммутатор, блок зада0

5

0

5

0

5

0

5

ния режимов, 2 элемента ИЛИ и связей, отражающих новую организацию взаимодействия между элементами устройства. Новая совокупность известных элементов позволяет задействовать весь имеющийся объем памяти устройства и тем самым осуществлять хранение стоп-кадра параллельно с обработкой текущего кадра без существенного усложнения устройства за счет увеличения конструктивного объема его памяти.

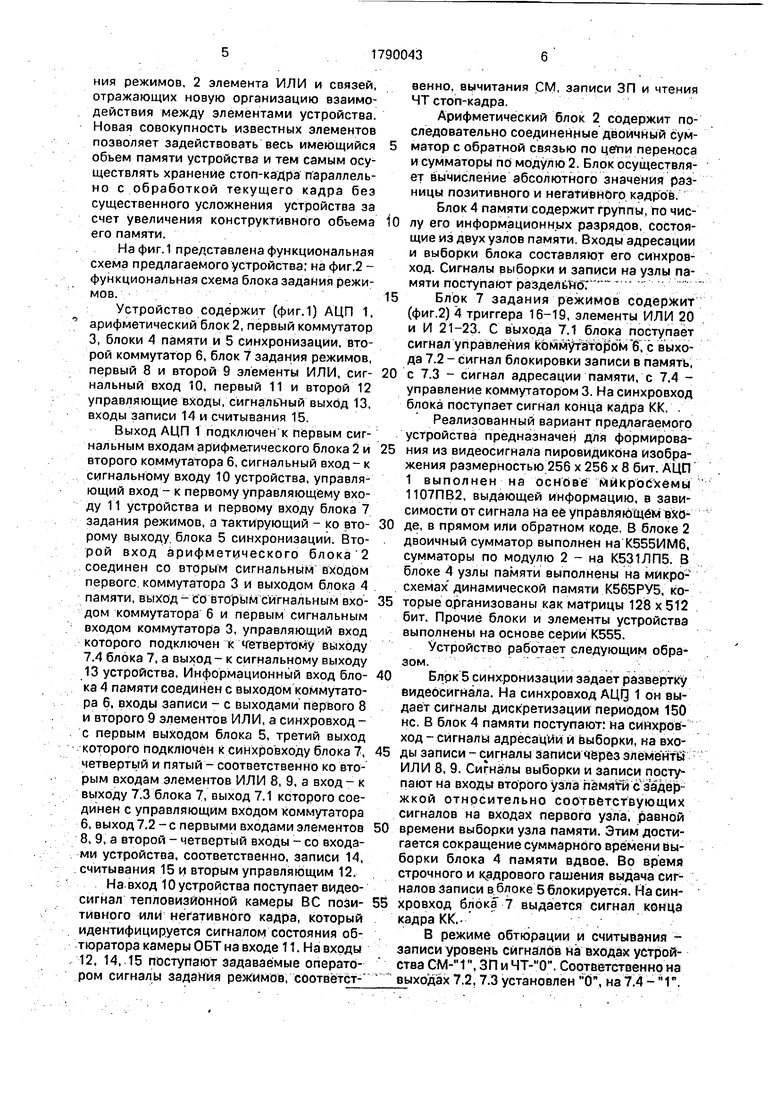

На фиг. 1 представлена функциональная схема предлагаемого устройства; на фиг.2 - функциональная схема блока задания режимов.

Устройство содержит (фиг.1) АЦП 1. арифметический блок 2, первый коммутатор 3, блоки А памяти и 5 синхронизации, Второй коммутатор 6, блок 7 задания режимов, первый 8 и второй 9 элементы ИЛИ, сигнальный вход 10, первый 11 и второй 12 управляющие входы, сигнальный выход 13, входы записи 14 и считывания 15.

Выход АЦП 1 подключен к первым сигнальным входам арифметического блока 2 и второго коммутатора 6, сигнальный вход - к сигнальному входу 10 устройства, управляющий вход - к первому управляющему входу 11 устройства и первому входу блока 7 задания режимов, а тактирующий - ко второму выходу; блока 5 синхронизации. Второй вход арифметического блока 2 соединен со вторым сигнальным входом первого, коммутатора 3 и выходом блока 4 памяти, выход-с О вторым сигнальным входом коммутатора б и первым сигнальным входом коммутатора 3, управляющий вход которого подключен к четвёртому выходу 7.4 блока 7, а выход- к сигнальному выходу 13 устройства. Информационный вход блокад памяти соединен с выходом коммутатора 6, входы записи - с выходами первого 8 и второго 9 элементов ИЛИ, а синхровход - с первым выходом блока 5, третий выход которого подключён к синхровходу блока 7, четвертый и пятый - соответственно ко вторым входам элементов ИЛИ 8, 9, а вход- к выходу 7.3 блока 7, выход 7.1 которого соединен с управляющим входом коммутатора 6, выход 7.2-с первыми входами элементов 8, 9, а второй - четвертый входы - со входами устройства, соответственно, записи 14, считывания 15 и вторым управляющим 12. -. На вход 10 устройства поступает видеосигнал тепловизйонной камеры ВС позитивного или негативного кадра, который идентифицируется сигналом состояния обтюратора камеры ОБТ на входе 11. На входы ,12, 14, 15 поступают задаваемые оператором сигналы задания режимов, соотвётст-

венно, вычитания СМ, записи ЗП и чтения ЧТ стоп-кадра.

Арифметический блок 2 содержит последовательно соединенные двоичный сум- 5 матор с обратной связью по цетш переноса и сумматоры по модулю 2. Блок осуществляет вычисление абсолютного значения разницы позитивного и негативного кадров. Блок 4 памяти содержит группы, по чис0 лу его информационных разрядов, состоящие из двух узлов памяти. Входы адресации и выборки блока составляют его сиххров- ход. Сигналы выборки и записи на узлы памяти поступают разделШбТ

5 Блок 7 задания режимов содержит (фиг.2) 4 триггера 16-19, элементы ИЛИ 20 и И 21-23. С выхода 7.1 блока поступает сигнал управления коммутаторомГ6, с выхода 7.2 - сигнал блокировки записи в память,

0 с 7.3 - сигнал адресации памяти, с 7.4 - управление коммутатором 3. На синхровход блока поступает сигнал конца кадра КК. .

Реализованный вариант предлагаемого устройства предназначен для формирова5 ния из видеосигнала пировидикОна изображения размерностью 256 х 256 х 8 бит. АЦП 1 выполнен на основе микросхемы 1107ПВ2, выдающей информацию, в зависимости от сигнала на её управляющем вхб0 де, в прямом или обратном коде. В блоке 2 двоичный сумматор выполнен на К555ИМ6. сумматоры по модулю 2 - на К531ЛП5. В блоке 4 узлы памяти выполнены на микросхемах динамической памяти К565РУ5, ко-.

5 торые организованы как матрицы 128 х 512 бит. Прочие блоки и элементы устройства выполнены на основе серии К555.

Устройство работает следующим обра зом. . : :/ ; .;

0 Блрк 5 синхронизации задает развертку видеосигнала. На синхровход АЦ(3 1 он выдает сигналы дискретизации периодом 150 не. В блок 4 памяти поступают: на синхровход - сигналы адресации и ёыборки, на вхо5 ды записи - сигналы записи через элемёнтьТ ИЛИ 8, 9. Сигналы выборки и записи поступают на входы второго узла памяти с зйдёр- жкой относительно соответствующих сигналов на входах первого узла, равной

0 времени выборки узла памяти. Этим достигается сокращение суммарного времени выборки блока 4 памяти вдвое. Во время строчного и кадрового гашения выдача сигналов записи в блоке 5 блокируется. На син5 хровход блока 7 выдается сигнал конца кадра КК..-

В режиме обтюрации и считывания - записи уровень сигналов на входах устройства , ЗП и . Соответственно на выходах 7.2.7.3 установлен О, на 7.4 - Г.

Коммутатор 6 подключает к информационному входу блока 4 памяти выход АЦП 1, коммутатор 3 подключает к выходу 13 выход арифметического блока 2,

АЦН 1 выдает байт элемента разложе- ния изображения (ПЭЛ) при уровне 1 сигнала 06Т - в прямом коде, при О -в обратном. Считывание из блока 4 ПЭ Л пред- ыДущого кадра и поступающие с АЦП 1 ПЭЛ текущего кадра взаимовычитаются в ариф- метическом блоке 2. Результатирующий кадр поступает на выход 13..

При записи стоп-кадра в режиме обтюрации ЗП устанавливается в 1. На информационный вход триггера 18 блока. 7 поступает сигнал ОБТ, изменяющий свое состояние синхронно кадровой развертке и тактируемый Сигналами КК. По установке триггера 18 триггеры 16, 17 формируют импульс, длйтельнбсть которого равна дли- тельности прохождения двух кадров развертки. Во время прохождения первого из этих Двух кадров элемент И 21 удерживает на выходе 7.1 О, и в блок 4 заносится с АЦП 1 ПЭЛ первого кадра. При прохржде- кии второго кадра на выходе 7.1 формируется 1 и Коммутатор б подключен к информационному входу блока 2-в память заносится результирующий кадр. На время прохождения этих двух кадров импульсом с инверсного выхода триггера 17 выход элемента 1/1 22 удерживается в состоянии О. Крометого/ЗП через элемент ИЛИ 20 поступает на триггер 19, который по КК устанав- ливается в 1, при этом выход элемента И 23 устанавливается в О. Сигнал адресации уровня 1 с выхода 7,3 через блок 5 синхронизации поступает на адрёсацию блока 4 памяти. Уровень О11 с выхода 7.1 поступает на коммутатор 3, который подключает к вы- ходу 13 выход блока 4, с 7.2: - на элементы ИЛИ 8, 9, разрешая тем самым прохождение сигналов записи на блок 4, После прохождения уйазаннУ на выходе элемента И 22 устанавливается 1, что бло- кирует прохождение сигналов записи через элементы ИЛИ8,9 на все оставшееся время

Формула изобретения 1. Устройство для преобразования видеосигнала, содержащее последовательно соединенные аналого-цифровой преобразователь (АЦП), два входа которого являются соответственно Сигнальным входом и управляющим входом устройства, арифметический блок и первый коммутатор, второй вход которого соединен с вторым входом

присутствия ЗП. Это необходимо для контроля результатов записи. По сбросу ЗП устройство из режима считывания вновь переходит к режиму считывания - записи. При этом текущий кадр заносится в блок 4 памяти по адресам со значением их старшего разряда, задаваемым блоком 7, , a стоп-кадр сохраняется по адресам с .

Для последующего чтения записанного стоп-кадра ЧТ устанавливается в 1, после чего по КК в 1 устанавливается триггер 19 и сигналы блокировки записи и адресации а выход 7,4 устанавливается в О. Запись новой информации в блок 4 блокируется, а на выход 13 поступает информация, запомненная по адресам с блока 4.

В режиме панорамирования СМ устанавливается в О, а ОБТ - в 1. Соответственно, в О устанавливаются выходы 7.1, 7.4. Блок 2 отключается от входа блока 5 и выхода 13 на все время работы в этом режиме. В остальном работа происходит аналогично. Считывание-запись производится по адресам с , и на выход 13 информация поступает с блока 4. В режиме записи стоп- кадр запоминается по адресам с , после чего запись блокируется и записанный кадр считывается в течение всего времени присутствия ЗП. По СЧ запись блокируется синхронно КК и ведется считывание по адресам с .

Таким образом осуществляется задержка выдеосигнала пирикона на один кадр, вычисление результирующего кадра и параллельное хранение стоп-кадра, представляющего собой разницу двух кадров в режиме обтюрации или собственно кадр .в режиме панорамирования.

При этом хранение стоп-кадра параллельно с текущим осуществляется в одном блоке памяти, в то время как в устройстве- прототипе для этого требуются дополнительные блоки памяти и синхронизации, кроме того, имеется возможность работы устройства в режиме панорамирования, чем и расширяются функциональные возможности устройства..

арифметического блока и выходом блока памяти, синхровход которого соединен с первым выходом блока синхронизации, а выход первого коммутатора является сигнальным выходом устройства, отличающееся тем, что, с целью расширения функциональных возможностей путем обеспечения преобразования сигнала в режиме хранения стоп-кадра, введены второй коммутатор,

первый сигнальный вход которого соединен с выходом АЦП, а выход - с информационным входом блока памяти, блок задания режимов, первые четыре входа которого являются соответственно первым управляющим входом, входом записи, входом считывания и вторым управляющим входом устройства, а первый выход соединен с управляющим входом второго коммутатора, блок синхронизации, вход которого соединен с вторым выходом блока задания режима, а первые три выхода - соответственно с синхровходами блока,задания режима, АЦП и блока памяти, и два элемента ИЛИ, первые входы которых соединены с вторым выходом блока задания режимов, третий выход которого соединен с входом блока синхронизации, второй и третий выходы которого соединены соответственно с тактовым входом АЦП и синхровходом блока задания режимов, четвертый выход которого соединен с управляющим входом первого коммутатора, первый вход которого соединен с вторым сигнальным входом второго коммутатора, при этом вторые входы первого и второго элементов ИЛИ соединены соответственное четвертым и пятым выходами блока синхронизации, а выходы - с первым и вторым управляющими входами блока памяти, второй управляющий вход которого соединен с выходом первого элемента ИЛИ.

третьего триггера, прямой выход которого соединен с С-входом второго триггера, D- вход которого соединен с выходом первого триггера, R-вход которого соединен с первым входом второго элемента И и инверсным выходом второго триггера, прямой выход которого соединен с первым входом первого элемента И, второй вход которого соединён с. инверсным выходом Третьего триггера, а третий вход является четвертым

входом блока и соединен с первым входом третьего элемента И. второй вход которого соединен с инверсным выходом четвёртогб триггера, прямой выход которого является третьим выходом блока и соединен с вторым

0 входом второго элемента И.

| Устройство для преобразования видеосигнала | 1986 |

|

SU1458977A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1993-01-23—Публикация

1990-10-31—Подача