Изобретение относится к вычислительной технике и может быть использовано при построении быстродействующих запоминающих устройств для обработки, ввода в ЭВМ и отображения графических изображений

Цель изобретения - повышение быстродействия устр )йства и расширение его области применения за счет возможности ска нирования как прогрессивной, так и телевизионной разверткой, а также хранения эта лонного кадра одновременно с осуществле нием операции «считывание -запись

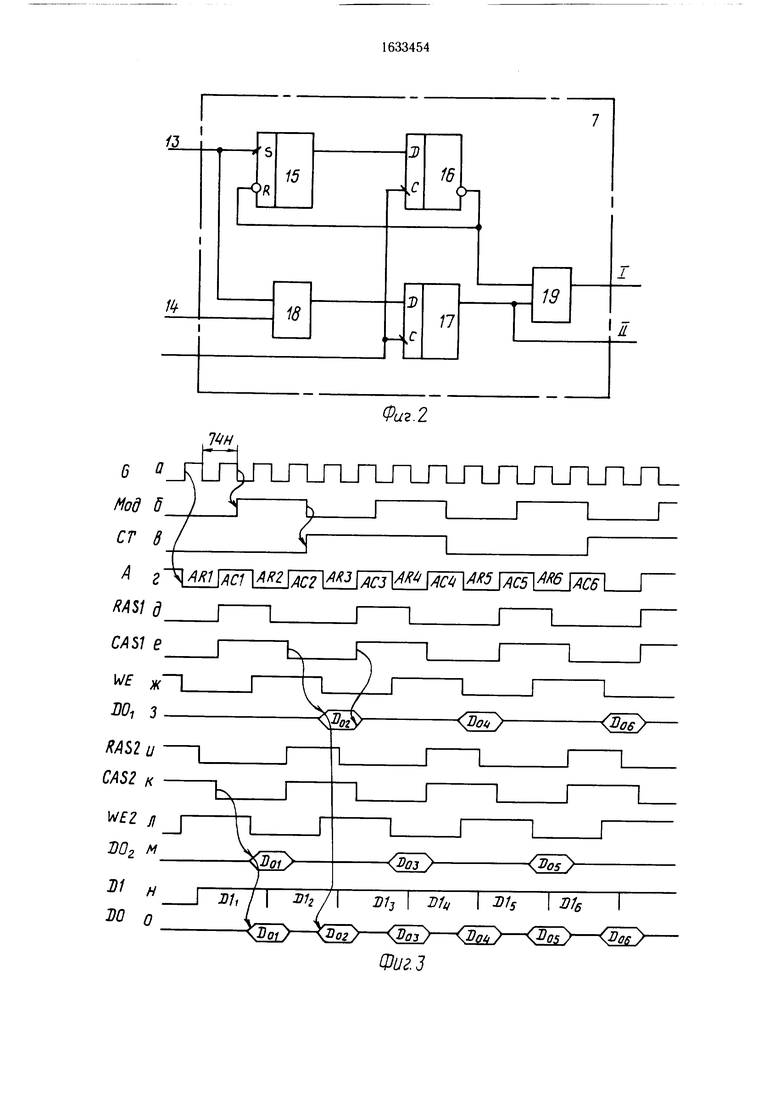

На фиг 1 представлена функциональ ная схема предлагаемого устройства, на фиг 2 - функциональная схема блока за дания режимов работы, на фиг 3 -- временные диаграммы работы устройства, на фиг 4 - временные диаграммы работы блока здания режимов работы

Устройство содержит (фиг 1) генератор 1 тактовых импульсов, первый 2 и второй 3 счетчики адресов, блок 4 управления записью- чтением, адресный коммутатор 5, первую группу матричных блоков 6 опера тивной памяти, блок 7 задания режимов работы, первый 8 и второй 9 элементы ИЛИ, вторую группу матричных блоков 10 опера тивной памяти, информационные входы 1 1 и выходы 12, входы 13 и 14 записи и чтения Количество блоков памяти в каждой из групп соответствует количеству информационных разрядов устройства

Выход генератора 1 тактовых импульсов соединен с входом первого счетчика 2 ад ресов, выходы которого подключены к адресным входам блока 4 управления записью чте нием, синхронизирующий выход которого соединен с входом второго счетчика 3 адресэсо

СО Јь СЛ 4

сов, выходы которого подключены к соответствующим информационным входам групп адресного коммутатора 5, вход управления которого соединен с выходом управления блока 4, а выход - с адресными входами блоков 6 и 10, информационные входы которых подключены к входам 11 устройства, выходы - к выходам 12 устройства, выходы выборки - к выходам выборки, соответственно, первому и второму блока 4 Входы записи блоков 6 подключены к выходу второго элемента ИЛИ 9, блоков 10 - к выходу первого элемента ИЛИ 8 Первые входы элементов 8 и 9 соответственно подключены к первому и второму выходам записи блока 4, вторые - к первому управляющему выходу блока 7 задания режимов, второй управляющий выход которо- ю соединен с информационным входом коммутатора 5, синхронизирующий вход - с выходом старшего разряда счетчика 3, а входы записи и чтения - соответственно к входам 13 и 14 устройства

Блок 7 задания режимов работы содер жит (фиг 2) триггеры 15 - 17, элементы ИЛИ 18 и И19 На вход установки триг- iepa 15 и первый вход элемента ИЛИ 18 с вхо ы 13 устройства поступает сигнал за- 11ти }п. на второй вход элемента 18 - с вхо id 14 сигнал чтения Чт На синхровхо- ды триггеров 16 и 17 поступает сигнал синхронизации блока Сигнал с выхода элемента И 19 через первый управляющий выход блока поступает на вторые входы эле ментов ИЛИ 8 и 9, с выхода триггера 17 чере второй управляющий выход блока - на информационный вход коммутатора 5

На фиг 3 обозначены а - выход младшею рафяда первого счетчика 2 адресов, бсигнал модификации второго счетчика 3 адресов, в - выход младшего разряда счетчика 3, г - управляющий сигнал на входе коммчтатора 5, д, е - первая группа сигналов выборки, соответственно, RAS1 и CAS1, ж - выход записи WE1 блока 4 управления записью-чтением, з - процесс поступления информации на выход матричных блоков в оперативной памяти, и -л - вторые сигналы выборки и записи, соответственно RAS2, CAS2, Wb.2, м - поступление информации на выход блоков 10 памяти, н - последовательность поступления информации на входы 11 устройства, и - считывание информации с выходов 12

На фиг 4 обозначены а - выход старшего разряда АС8 второго счетчика 3 адресов, б - выход ЗП на входе 13 устройства, в - сигнал ЧТ на входе 14 устройства, г - инверсный выход триггера 16 блока 7, д - выход триггера 17, подключенный ко второму выходу блока 7 и являющийся сигналом адреса AR8 для блоков 6, 10

0

памяти, е - выход элемента И19, подключенный к первому выходу блока 7 и являющийся сигналом блокировки записи в блоки 6 и 10

Устройство работает следующим образом

Выходным сигналом генератора 1 тактовых импульсов запускается первый счетчик 2 адресов (фиг. За) Выходные напряжения счетчика 2 поступают на адресные входы блока 4 управления записью-чтением К фронтам сигналов счетчика 2 привязаны генерируемые блоком 4 сигналы выборки и записи, поступающие с периодом 300 не, а также сигналы модификации второго счетчика 2 адресов и управления адресным коммутатором 5 Сигналы выборки и записи второй группы сдвинуты относительно соответствующих сигналов первой группы на 150 не Тем самым при длительности выборки матричных блоков 6, 10 оперативной памяти 300 не обеспечивается длительность обработки ПЭЛ в 150 не По переднему фронту сигнала с выхода синхронизации блока 4 (фиг 36) модифицируется второй счетчик 3 адресов (фиг Зв) По сосстоянию «О сигнала на

5 управляющем выходе блока 4 (фиг Зг) коммутатор 5 подключает к адресным входам блоков 6, 10, 7 младших разрядов счетчика 3 в качестве AR 1 - 7 и второй управляющий выход блока 7 в качестве AR8 По отрицательному фронту сигнала RAS1

0 (фиг 3d) строчный адрес заносится в адресные регистры блоков 6 По отрицатель ному фронту RAS2 (фиг Зи) этот адрес заносится в блоки 10 По состоянию «1 на управляющем входе коммутатора 5 к адресным входам блоков 6, 10 подключа5 ется 8 старших разрядов счетчика 3 в качестве АС1-8 По отрицательному фронту CAS1 (фиг Зе) адреса столбцов заносятся в блоки 6, по CAS2 (фиг Зк) - в блоки 10 и производится выборка этих блоков

0 (фиг Зз, м) По положительному фронту сигналов CAS выходы блоков 6, 10 переходят в третье состояние

При наличии сигнала ЗП на входе 13 (фиг 46) по сбросу сигнала АС8 (фиг. 4а) устанавливаются триггера 16 (фиг. 4г) и

5 17 (фиг 4д) В блоках 4 и 10 начинают выбираться ячейки с адресом По следующему сбросу сигнала АС8 триггер 16 сбрасывается, в результате чего на выходе элемента И19 устанавливается уровень «1 (фиг 4е), поступающий на элементы ИЛИ 8

0 и 9 и блокирующий дальнейшую запись в блоки 6 и 10 Тем самым в ячейки памяти блоков 6 и 10 по адресам ARSfl заносится последний, с момента появления ЗП, кадр После этого он начинает считывать5 ся на выходах 12 устройства вплоть до сброса ЗП. По сбросу же ЗП по адресам продолжается запись-считывание текущих кадров, а по адресам xpaнится стоп-кадр. По сигналу 4Т (фиг. 4в) синхронно окончанию кадра (сбросу АС8) элементы ИЛИ 8 и 9 блокируют прохождение сигналов записи на блоки 6 и 10, на шине AR8 устанавливается «I и информация о кадре, заполненном по предыдущему сигналу ЗП, начинает поступать на выходы 12. Так, блок 7 и элементы 8 и 9 обеспечивают запоминание и считывание стоп-кадра из ячеек блоков 6 и 10 по адресам

В режиме записи-считывания на входах 13 и 14 устройства установлен уровень «О Соответственно «О установлен на управляющих выходах блока 7. Элемент ИЛИ 8 передает сигнал WE2 (фиг Зл) на входы записи блоков 10, элемент ИЛИ 9 - сигнал WE1 (фиг Зж) на входы записи блоков 6 Поступающая на входы 11 устройства информация (фиг Зн) заносится согласно фиг 3 следующим образом - нечетные ПЭЛ в блоки 10, четные - в блоки 6 При этом на выходы 12 поступает информация о предыдущем кадре (фиг Зо) Ячейки блоков 6 и 10 с адресом AR8 1 не выбираются

При установке «1 на входе 13 состояние «I устанавливается на выходе триггера 15 и элемента ИЛИ 18 блока 7 По установке «О на выходе старшего разряда счетчика 3 на инверсном выходе триггера 16 устанавливается «О, на прямом выходе триггера 17 - «1, а триггер 15 сбрасывается На выходе триггера 16 формируется импульс, длительность которого соответствует длительности кадра С выхода триггера 17 уровень «1 поступает на информационный вход коммутатора 5 в качестве AR8 Тем самым в ячейки памяти блоков 6 и 10 по адресам заносится последний, с момента появления сигнала Зп кадр, после чего на выходе элемента И 19 устанавливается «1, которая передается на выход элементов ИЛИ 8 и 9 и поступление сигналов WE блокируется на все последующее время нахождения «1 на входе 13, что необходимо для отображения и контроля записанного кадра По сбросу сигнала Зп вновь устанавливается и снимается блокировка сигналов WE, устройство переходит в режим записи-считывания, а по адресам хранится запомненный кадр При необходимости его считывания на входе 14 устанавливается «I, после чего одновременно блокируется прохождение сигналов WE и на шине AR8 устанавливается «1 Информация о запомненном по сигналу Зп кадре начинает поступать на выходы 12

Требование регенерации информации в блоках 6 и 10 обеспечивается перебором адресов AR1-7 в течение строки кадра развертки за 64 мкс

Таким образом, в предлагаемом устройстве осуществляется задержка изображения на один кадр при периоде ввода ПЭЛ 150 не с длительностью выборки элементов памяти 300 не с одновременным хранением и, при необходимости, индикацией эталонного кадра

Если в прототипе осуществляется ввод ПЭЛ с периодом, вдвое меньшим, чем периП од выборки памяти за счет скани ования изображения в течение двух полукадров, то в предлагаемом устройстве за счет изменения организации памяти это сканирование осуществляется за один кадр, чем и достигается повышение быстродействия )ст5 ройства в 2 раза Одновременно этим достигается возможность сканирования как про грессивной, так и телевизионной разверт кой, а также хранения эталонного кадра одновременно с осуществлением операции «считывание-запись, чем достигается рас0 ширение области применения устройства

Формула изобретения

Блок буферной памяти для терминаль5 ного устройства, содержащий генератор тактовых импульсов, первый и второй счетчики адресов, блок управления записью- чтением, адресный коммутатор и первую гр п- пу матричных блоков оперативной памяти, информационные входы которых являются

0 информационными входами блока, информационные выходы матричных блоков оперативной памяти первой являются информационными выходами блока, адресные входы матричных блоков оперативной памя ти первой группы поразрядно обьединены и

5 подключены к выходам адресного коммутатора, управляющий вход которого соединен с первым выходом блока правления записью-чтением, выходы первой группы которого соединены с входами выборки мат

Q ричных блоков оперативной памяти первой группы, информационные входы первой и второй групп адресного коммутатора соединены соответственно с выходами младших и старших разрядов второго счетчика адресов, счетный вход которого соединен с вто

5 рым выходом блока управления записью- чтением, адресные входы которого соединены с выходами первого счетчика адресов, счетный вход которого соединен с выходом генератора тактовых импульсов, отличающийся тем, что, с целью повышения

0 быстродействия блока и расширения его области применения за счет возможности сканирования как прогрессивной, так и телевизионной развертки, а также хранения эталонного кадра одновременно с ос ществле5 нием операции «считывание-запись, в него введены блок задания режимов работы, первый и второй элементы ИЛИ и вторая группа матричных блоков оперативной памяти, информационные входы и выходы которых подключены к информационным входам и выходам матричных блоков оперативной памяти первой группы соответственно, входы выборки матричных блоков оперативной памяти второй группы соединены с выходами второй группы блока управления записью-чтением, адресные входы матричных блоков оперативной памяти второй группы подключены к соответствующим входам матричных блоков оперативной памяти первой группы, входы записи матричных блоков оперативной памяти второй группы объединены и подключены к выходу первого элемента ИЛИ, первый вход которого соединен с третьим выходом блока управления

0

записью-чтением, четвертый выход которого соединен с первым входом второго элемента ИЛИ, выход которого соединен со вхо дами записи матричных блокев оперативной памяти первой группы, второй вход второго элемента ИЛИ соединен со вторым входом первого элемента ИЛИ и подключен к первому выходу блока задания режимов работы, входы записи и чтения которого являются соответствующими входами блока, вход синхронизации блока задания режимов работы подключен к выходу старшего разряда второго счетчика адресов, второй выход блока задания режимов работы соединен с информационным входом адресного коммутатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО СОРТИРОВКИ СИМВОЛОВ | 1992 |

|

RU2067317C1 |

| Устройство для контроля блоков оперативной памяти | 1986 |

|

SU1358003A1 |

| Устройство для контроля многоразрядных блоков оперативной памяти | 1987 |

|

SU1495854A1 |

| Оперативное запоминающее устройство с самоконтролем | 1986 |

|

SU1325571A1 |

| Ассоциативно-адресное оперативное запоминающее устройство | 1987 |

|

SU1451773A1 |

| Устройство для преобразования видеосигналов | 1990 |

|

SU1790043A1 |

| Оперативное запоминающее устройство для растрового дисплейного терминала | 1988 |

|

SU1564692A1 |

| Многоканальное устройство ввода информации | 1985 |

|

SU1273936A2 |

| Устройство для обнаружения ошибок в блоках интегральной оперативной памяти | 1988 |

|

SU1605281A1 |

| Буферное устройство для передачи данных | 1987 |

|

SU1418725A1 |

Изобретение относится к вычислитель ной технике и может быть использовано при построении бйстродействующих запоминающих устройств для обработки, ввода в ЭВМ и отображения графических изображений Цель изобретенияповышение быстродействия и расширение области применения устройства за счет возможности сканирования как прогрессивной, так и телевизионной развертки, а также хранения эталонного кадра одновременно с осуществле нием операции «запись считывание Уст ройство содержит генератор тактовых импульсов, два счетчика адресов, блок управления записью-чтением, адресный коммутатор, две группы матричных блоков оперативной памяти, блок задания режимов работы и два элемента ИЛИ Считывание-запись изобра жения производится за один кадр прогрес сивной либо телевизионной развертки Чет ные элементы разложения изображения заносятся в блоки памяти одной из rpvnn, нечетные - в блоки другой Устройство мо жет дополнительно хранить эталонное изоб ражение На время его считывания запись в блоки памяти блокируется 4 ил lO С/)

Фиг.1

6и

Модб

СТ8

Ау AR1 АСЛАК2 Jfi

лтТИ/f j ДСБ

Фиг.2

Фиг.З

1

I

Ki Чсэ r fXJ (.

tr Ј «

Ј К ,§

Nt- л

Ј

| Авторское свидетельство СССР № 1231535, кл G 11 С 11/00, 1984 Авторское свидетельство СССР № 1418812, кл G 11 С 11/00, 1987 |

Авторы

Даты

1991-03-07—Публикация

1989-02-22—Подача