Изобре-тение относится к импульсной технике и может быть использовано в информационно-измерительных системах.

Известен управляемый делитель чатоты , управляемый программно и содержа1ций счетчики имупульсов, элеметы совпадения, регистровые блоки задания кода программы и блока упраления fl }.

Недостатком известного устройства является сложность, что связано со сложностью последовательно соединенных счетчиков с управляемым коэффициентом деления, количество котоЕжзх однозначно связано с точностью задания коэффициента деления программно управляемого дели.теля частоты..

Наиболее близким по технической сущности к предлагаемому является управляемый делитель частоты, содержащий N пересчетных блоков, каждый из которых, кроме последнего N-го пересчетного блока, состоит из . первого и второго элементов И, счетчика импульсов, выход которого подключен к первому входу второго элемента И, а вторые входы первого и второго логических элементов И в кадом, кроме последнего, пересчетном блоке соединены с соответствующими выходами блока управления, счетный вход счетчика первого пересчетного блока подключен к второй шине тактовых импульсов С2 J.

Недостатком известного устройства является сложность реализации.

В каждр.м из N пересчетных блоко используются счетчики с предварительной записью. Каждый счетчик с предварительной записью, например двоично-десятичный счетчик должен состоять, не учитывая четырех счетных триггеров, по меньшей мере из четырех логических элементов 2И и одного логического элемента 4И-НЕ Причем каждый триггер счетчика должен быть дополнен входом установки в 1. Подобный, минимально возможный, состав двоично-десятичного счетчика с предварительной записью реализуем при условии предварительного обнуления счетчика, так называемый режим синхронной записи. В режиме асинхронной записи на два установочных входа каждого триггера действуют парафазные сигналы установки. Кроме того, для программного управления счетчиками с предвар тел ной записью необходимо по четыре управляющих шины из блока задания кода или устройства управления на каждый счетчик.

Дель изобретения - упрощение и повыяение надежности работы устройства.

в устройстве используется только один счетчик с предварительной за писью, тогда как в остальных N-1 пересчетных блоках применены обычные счетчики или делители частоты. Дпя достижения поставленной цели в управляемый делитель-частоты, содержащий N пересчетных блоков, каждый из которых, кроме N -го, состоит из первого и второго элемен0 тов И, счетчика импульсов, выход которого подключен к первому входу второго элемента №, а вторые входы первого и второго элементов И в каждом, кроме последнего, пересчетном

5 блок. соединены с 2(N-1) -ми выходами блока управления, счетный вход счетчика импульсов первого пересчетного блока подключен к входной шине тактовых импульсов, введены шина .записи программ, триггер, фс мирователь импульсов, элемент задержки и в каждый пересчетный блок, креме последнего, - элемент ИЛИ, входы которого подключены к выходам первого и второго элементов И, а

выход соединен со счетным входом счетчика импульсов каждого последующего пересчетного блока, первые входы первого элемента И в каждом .{N-i)-M пересчетном блоке соединены с

0 шиной тактовых импульсов, а входы сброса счетчиков импульсов в каждом, кроме последнего, пересчетном блоке подключены к входу записи -кода счетчика импульсов последнего

5 N-ro пересчетного блока и к выходу элемента задержки, вход которого соединен с первым выходом формирователя импульсов, первый вход которого подключен к выходу счетчика

п импульсов N-ro пересчетного блока, информационные входы счетчика импульсов N-ro пересчетного блока соединены с соответствующими информационными выходами блока управления. первый вход которого подключен к вто

рому выходу формирователя импульсов , второй вход которого соединен С шиной запуска и с входом сброса триггера, первый выход которого подключен к выходной шине устройства,

0 а второй выход - к третьему входу блока управления, 2 N -и выход которого соединен со счетным входом триггера, а информационные входы блока управления подключены к шинам записи

5 программ.

Кроме того, в управляемом делителе частоты блок управления состоит из блока оперативного запоминающего устройства и регистра сдвига, 2N

0 выходов которого являются соответствующими выходами блока управления, причем 2 N, выходов регистра сдвига и третий вход блока управления подключен к соответствующим адресным

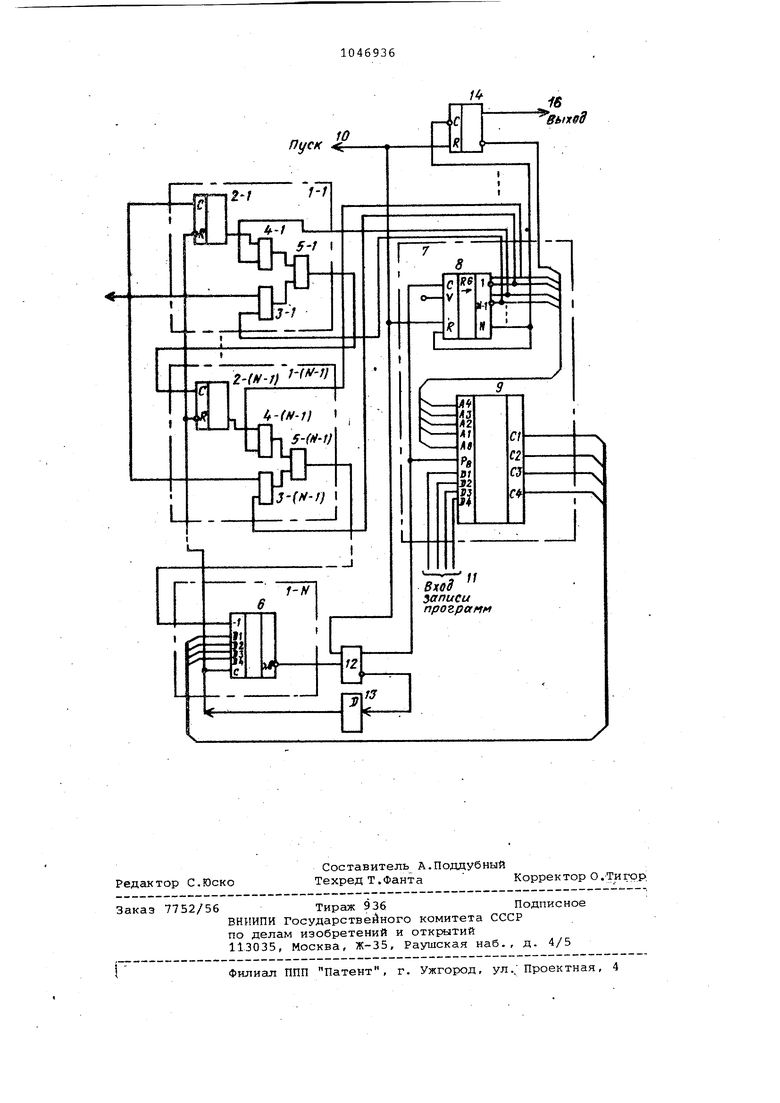

входам блока оперативного запоминяклцего устройства, информационные ;входы и ъыкоды которого являются со ответственно информационными входам блока управления, первый вход котор го соединен с входом разрешения вос произведения блока оперативного зап минающего устройства и входом син|Хронизации регистра сдвига, информа ционный вход которого подключен к шине единичного сигнала, первый и второй входы сбросарегистра сдвига соединены с 2 Nгм выходом регистра сдвига и вторым входом блока управления соответстве но. На чертеже представлена структур ная схема устройства.; Управляемый делитель частоты содержит пересчетные блоки 1-1 -1-N . каждый из которых, за исключением последнего N-ro, содержит счетчик 2-1-2-,(N-1)импульсов, элементы 3-1 - 3-(М-1) и 4-1 - 4-(N -1|Ы элемент, 5-1 -5- {N-1 ИЛИ, последний (1-N) -и блок содержит счетчик 6 импульсов; блок управления 7, состо щий из регистра сдвига 8 и блока 9 оперативного запоминающег.о устройства (ОЗУ), шину 10 запуска, шину 11 записи программ, формировател 12 импульсов, элемент 13 задержки, триггер 14, ошну 15 входных так товых импульсов, шину 16 выходную. При этом счетчик 6 импульсов являет ся счетчиком импульсов с предварительной установкой. Для пояснения работы предлагаемого программно-управляемого делите ля частоты рассмотрим пример форми рования импульсов, длительность которых составляет 871 Т , где Т,(, - п риод повторения входных тактовых си налов, а длительность паузы между импульсами 352 Т.д. Для реализации данного примера необходимо три пересчетных блока (N-3) и регистр сдвига с тремя разрядами. В исходном состояниии в блоке 9 по шинам 11 вводится информация в четырехразрядном двоично-десятичйом коде о коэффициенте деления час тоты входного сигнала, а также о скважности ВЕЛХОДНОГО импульса. Ад-. ресные шины записи (не показаны ) об диняются по схеме монтажное ИЛИ V. элементы с открытым коллекторе ) с соответствуюЕдами адресными шинами воспроизведения (входы А(,,...,А). После введения в блок 9 входной информации с пульта прибора или от вм него процессора поступает команда Пуск в виде короткого по длитель ности импульса. По этой команде про ходит обнуление триггера и регистра 8 сдвига. Команда Пуск, поступающая на вход формирователя 12, вы зывает появление на его выходах парафаэньох импульсов, длительность торых меньше периода повторения Тр входных тактовых импульсов. Импульс положительной полярности с прямого выхода формирователя 12, поступающий на вход разрешения воспроизведем дения Pj блока 9, инициирует считывание информации из блока 9. Код адреса считываемой информации оппеде лен состоянием разрядов регистра 8 сдвига и триггера 14, удерживаемых в нулевом состоянии действием сигнала на. шине 10 запуска на входах сброса регистра 8 и триггера 14. В соответствии с вышеприведенным римером на информационных выходахблока 9, и . следовательно, на входах предва ите л ьной записи счетчика .6 первым считывается код числа 1 (младшии разряд числа 871/). Импульс отрица тельной полярности с инверсионного выхода формирователя 12, задержанный с помощью элемента 13, поступает на вход записи счетчика 6, производя запись в счртчик информации с выхода блока 9. Орновременно с этим происходит сброс счетчиков 2-1 и 2-2 в нулевое состояние. Высокий уровень напряжения (сигнал 1)с инверсного выхода 1-го разряда регистра 8 сдвига открывает элемент 3-2 И. Элемент 4-2 И закрыт низким уровнем напряжения (сигнал О) с прямого выхода 1-го разряда регистра 8 сдвига. Импульсы с шины 15 поступают через элемент 3-2 И, и 5-2 ИЛИ на вычитающий вход счетчика 6. В момент обнуления счетчика на его, выходе формируется сигнал, вк/почающий формирователь 12. На выходах формирователя 12 формируются парафазные.импульсы. Импульс положительной полярности записывает 1 в первый разряд регистра 8 сдвига и разрешает считывание информации из е5Ло|са 9 по второму адресу, определяемого кодом на выходе регистра 8 сдвига. Задержанный импульс отрицательной полярности производит запись в счетчик 6 кода, соответствующего числу 7. Сигнал О с инверсного выхода 1-го разряда регистра 8 сдвига закрывает элемент 3-2 И. Элементы 3-1, 4-2 И открыты высокими уровнями нанапряжения с инверсного выхода 2-го разрзада и прямого выхода l-ro разряда соответственно. Импульсы с шины 15 проходят через элементы 3-1 И и 5-1 ИЛИ на счетный вход счетчика . Счетчик 2-2 производитделение частоты входного сигнала на 10. Импульсы с выхода счетчика 2-2 поступают через элементы 4-2 И и 5-2 ИЛИ на вычитающий вход счетчика 6. Обнуление счетчика 6 произойдет после прохождения 70 импульсов с входа предлагаемого устройства. Сигнал на Выходе счетчика б, возникающий в момент обнуления, включает формирователь 12, инициирующий запись 1 во второй разряд регистра 8 сдвига и считывание информации изблока 9 по третьему адресу. В счетчик 6 производится запись числа 8. Сигналы 1 на прямых выходах первого и второго разрядов регистра 8 сдвига обес печивают открытое состояние элементов 4-1, 4-2 И. Импульсы с шины 15 проводят последовательно через счетчики 2-1, 2-2 и элементы 4-1 И, 5-1ИЛИ, 4-2 И и 5-2 ИЛИ на вычитающий вход счетчика б. Обдий коэффициент деления счетчиков 2-1 и 2-2 равен 100. После прохождения 800 вхо ных импульсов на выходе счетчика 6 возникает сигнал обнуления. В резуль тате чего в регистре сдвига произойдет запись 1 в третий разряд, что в свою очередь, обеспечивает переклю чение триггера 14 в единичное состоя ние и сброс регистра сдвига в исходное, нулевое положение. Аналогично происходит формировани длительности паузы в выходной последовательности импульсов. С той разн цей, что сигнал О на внходе тригге г- . ра 14 определяют адресацию в новую зону памяти блока 9. С учетом показанных выше реализаций счетчиков с предварительной записью увеличение на один десятичный разряд коэффициента деления в известном устройстве приводит к .следующему аппаратному приращению; один счетчик с предварительной записью, состоящий из счетчика., 4-х элементов 2И, 1-го элемента 4И-НЕ, 2-х элементов 2И, 1-го элемента ЗИ, 4-х информационных шин/ ОЗУ на 2x4 бит. Всего; счетчик, восемь логических элементов, четыре шины, ОЗУ на 2-х 4 бит. В рассматриваемом устройстве увеличение коэффициента деления на один десятичный разряд приводит к добавлению одного счетчика или делителя частоты на 10, 2-х элементов 2И, 1-го элемента 2 ИЛИ, разряда регистра сдвига, реализуемого на 4-х элементах 2ИЛИ-НЕ,ОЗУ на 2x4 бит и 2-х управляющих шин.Итого: счетчик, семь логических элементов, две шины и ОЗУ 2x4 бит. Таким образом, устройство обладает простотой и надежностью.

| название | год | авторы | номер документа |

|---|---|---|---|

| АДАПТИВНЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ ИНТЕРВАЛОВ | 1991 |

|

RU2043648C1 |

| Измерительный двухфазный генератор | 1987 |

|

SU1442931A1 |

| Делитель частоты следования импульсов | 1980 |

|

SU875642A1 |

| Устройство для измерения частоты | 1983 |

|

SU1170373A1 |

| Устройство для деления чисел | 1981 |

|

SU1013948A1 |

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

| ПРЕОБРАЗОВАТЕЛЬ УГЛА ПОВОРОТА ВАЛА В КОД | 2013 |

|

RU2534971C1 |

| Устройство для измерения угла закручивания вращающегося вала | 1991 |

|

SU1795312A1 |

| Программируемая линия задержки | 1990 |

|

SU1723656A1 |

| УСТРОЙСТВО ДЛЯ ЗАДЕРЖКИ СИГНАЛОВ | 1992 |

|

RU2024186C1 |

1. УПРАВЛЯЕМЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ, содержащий / пересчетных блоков, каждый из КОТОЕЯЛХ, кроме N -го состоит из первого и второго элементов И, счетчика импульсов, выход которого подключен к первому входу второго элемента И, а вторые входы первого и второго элементов И в каждом, кроме, последнего, пересчетном блоке соединены с 2 {(Ч-1)-ми выходами блока управления, счетный вход счетчика импульсов первого пересчетного блока подключен к входной шине тактовых импульсов, о тличающийся тем, что, с целью упрощения и повышения надежности работы устройства, в него введены шина записи программ, триггер, формирователь импульсов, элемент задержки и в .каждый пересчет-. ный блок, кроме последнего - элемент ИЛИ, входы которого подключены к выходам первого и второго элементов И, а выход соединен со счетным входом счетчика импульсов каждого ;последующего пересчетиого блока, « I первые входы первого элемента И IB каждом (N-l)-M пересчетном соединены с шиной тактовых импульсов, а входы сброса счетчиков импульсов в каждом, кроме последнего, пересчетном блоке подключены к входу записи кода счетчика импульсов последнего N-ro пересчетного блока и к эыходу элемента задержки, вход которого соединен с первым выходом формирователя импульсов, первый вход которого подклк чен к выходу счетчика импульсов М -го пересчетного блока, информационные входы счетчика .импульсов fN-ro пересчетного блока соединены с сортветствуюидами информационными выходами блока управления, первый вход которого подключен к второму выходу Формирователя импульсов, второй вход которого соединен с шиной запуска и с входом сброса триггера, Лервый выход которого подключен к выходной шине устройства, а второй выход - к третьему входу блока управления, 2 N ,-й выход которого соединен со счетным (Л входом триггера, а информационные входы блока управления подключены к винам записи программ. .. 2, Делитель по п.1, отличающ и и с я тем, что блок управления 2 состоит из блока оперативного запоминающего устройства и регистра сдвига, 2 N выходов которого являют-i О 4i) ся соответствующими выходами блока . управления, причем 2N выходов регистра сдвига и третий вход блока 0) управления подключены к соответствуюСО 1ЧИМ адресным входг1М блока оперативного запоминающего устройства, ин00 формационные- входы и выходы которого № являются соответственно информационными входами и выходами блока управления, первый вход которого соединен с входом разрешения воспроизведения блока оперативного запоминающего устройства и входом синхронизации регистра сдвига, информационный вход которого подключен к шине единичного :Сигнала, первый и второй входы сброса регистра сдвига сое.цннены с 2N -м выходом регистра сдвига и вторым входом блока управления соответственно.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для формирования серий импульсов | 1976 |

|

SU632063A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Программируемый делитель частоты | 1975 |

|

SU621099A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1983-10-07—Публикация

1982-01-20—Подача