СО

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для защиты от импульсных помех | 1987 |

|

SU1483646A1 |

| Устройство демодуляции фазоманипулированных сигналов | 1987 |

|

SU1515387A1 |

| Двухканальное устройство подавления помех | 1989 |

|

SU1619415A1 |

| Дифференцирующее устройство | 1990 |

|

SU1829044A1 |

| Устройство для измерения отношения сигнал/помеха импульсных сигналов | 1987 |

|

SU1494232A1 |

| Устройство для автоматическойРЕгулиРОВКи уСилЕНия | 1979 |

|

SU801230A1 |

| Устройство для определения среднего значения | 1986 |

|

SU1319050A2 |

| ДЕМОДУЛЯТОР СИГНАЛОВ С ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МОДУЛЯЦИЕЙ | 2014 |

|

RU2549360C1 |

| Устройство автоматического регулирования температуры в секционированных картофелехранилищах | 1981 |

|

SU983665A1 |

| Устройство для решения систем линейных алгебраических уравнений | 1984 |

|

SU1187157A1 |

Использование: радиотехника, системы обработки аналоговых сигналов. Сущность изобретения: Устройство защиты от импульсных помех содержит вычитатель 1, двухсторонний ограничитель 2, электронный ключ 3, элемент интегрирования 4, сумматор 5 и элемент сравнения модуля сигнала с пороговым уровнем 6. В устройстве достигается увеличение помехозащищенности, т.к. в момент действия импульсной помехи выходной сигнал устройства остается на тбм же уровне, который был в устройстве до момента появления импульсной помехи. 2 ил.

Фиг. 1

-NJ Ю XI

О

О

Изобретение относится к радиотехнике и может быть использовано в системах обработки аналоговых сигналов.

Целью изобретения является увеличение помехозащищенности.

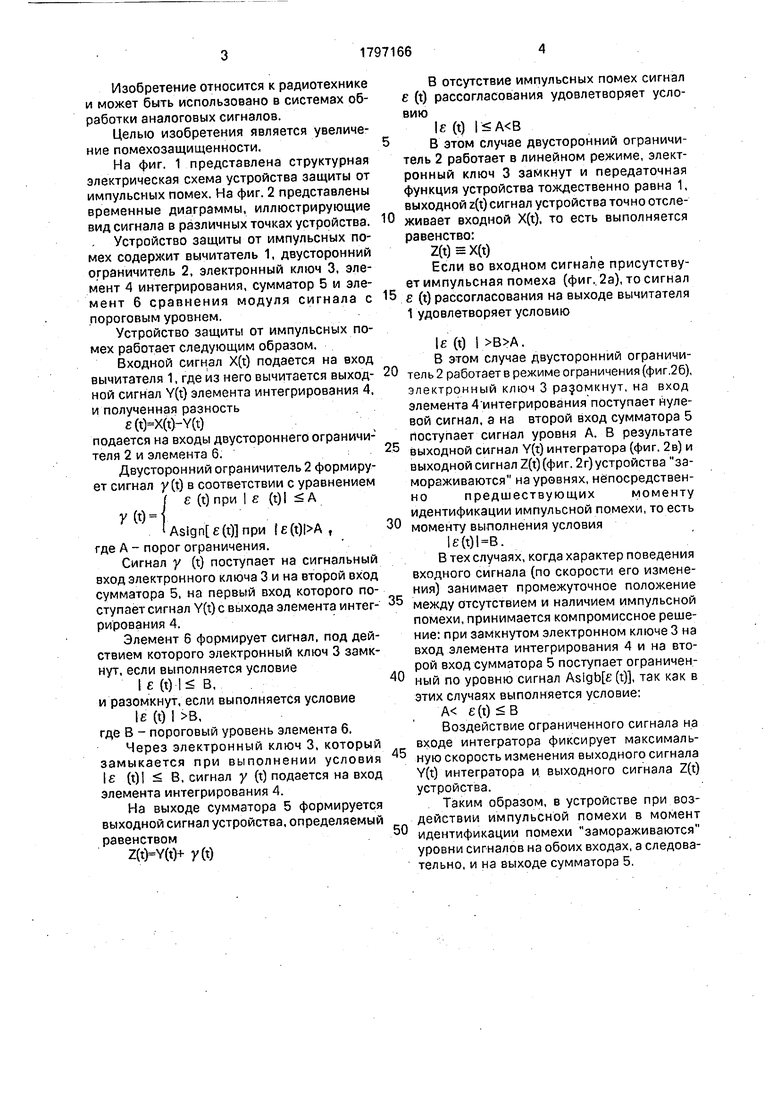

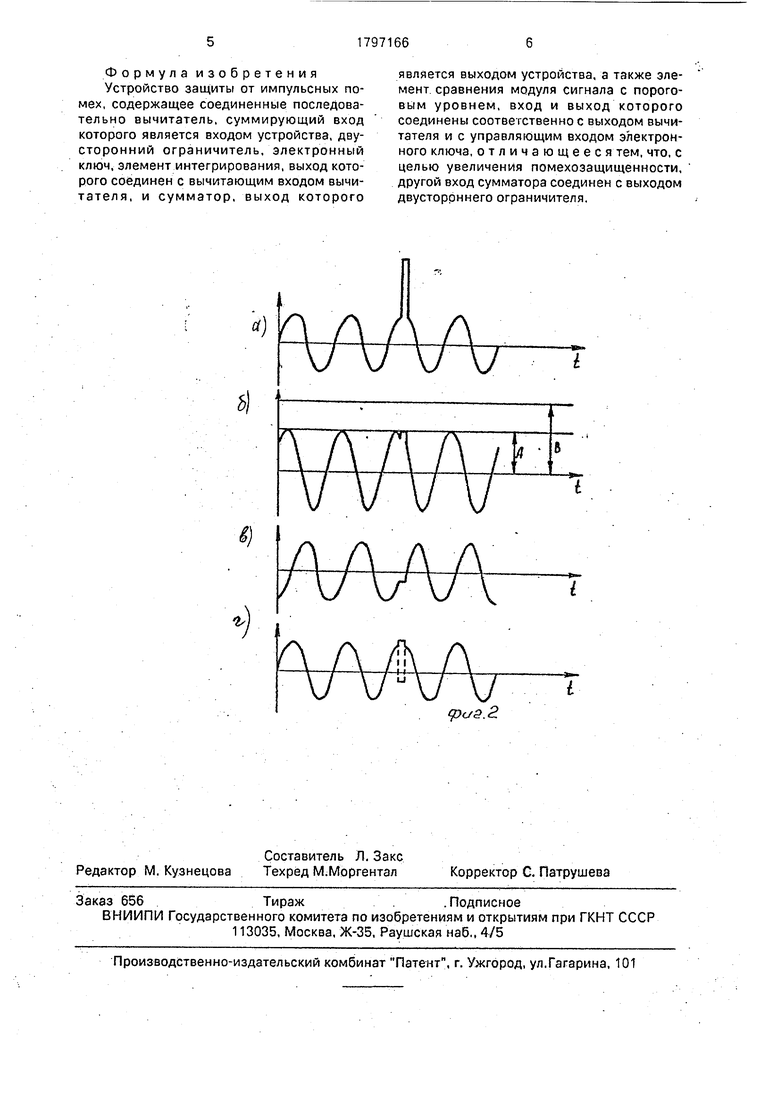

На фиг. 1 представлена структурная электрическая схема устройства защиты от импульсных помех. На фиг. 2 представлены временные диаграммы, иллюстрирующие вид сигнала в различных точках устройства.

Устройство защиты от импульсных помех содержит вычитатель 1, двусторонний ограничитель 2, электронный ключ 3, элемент 4 интегрирования, сумматор 5 и элемент 6 сравнения модуля сигнала с пороговым уровнем.

Устройство защиты от импульсных помех работает следующим образом.

Входной сигнал X(t) подается на вход вычитателя 1, где из него вычитается выходной сигнал Y(t) элемента интегрирования 4. и полученная разность

Ј(t)X(t)-Y(t)

подается на входы двустороннего ограничителя 2 и элемента 6.

Двусторонний ограничитель 2 формирует сигнал y(t) в соответствии с уравнением

( Ј (1)при I E (t)l A

y(t)

Asign Ј(t)npH |e(t) , где А - порог ограничения.

Сигнал у (t) поступает на сигнальный вход электронного ключа 3 и на второй вход сумматора 5, на первый вход которого поступает сигнал Y(t) с выхода элемента интегрирования 4.

Элемент 6 формирует сигнал, под действием которого электронный ключ 3 замкнут, если выполняется условие

IE (t)l В, . и разомкнут, если выполняется условие

IE (t) I B, где В - пороговый уровень элемента 6.

Через электронный ключ 3, который замыкается при выполнении условия |Ј (t)l В, сигнал у (t) подается на вход элемента интегрирования 4.

На выходе сумматора 5 формируется выходной сигнал устройства, определяемый равенством

Z(tH/(t)+ y(t)

В отсутствие импульсных помех сигнал е (t) рассогласования удовлетворяет условию

IE (t)

в этом случае двусторонний ограничитель 2 работает в линейном режиме, электронный ключ 3 замкнут и передаточная функция устройства тождественно равна 1, выходной z(t) сигнал устройства точно отеле- живает входной X(t), то есть выполняется равенство: Z(t)X(t)

Если во входном сигнале присутствует импульсная помеха (фиг., 2а), то сигнал Ј (t) рассогласования на выходе вычитателя 1 удовлетворяет условию

IE (t) I .

В этом случае двусторонний ограничитель 2 работает в режиме ограничения (фиг.2б), электронный ключ 3 разомкнут, на вход элемента 4 интегрирования поступает нулевой сигнал, а на второй вход сумматора 5 поступает сигнал уровня А. В результате

выходной сигнал Y(t) интегратора (фиг. 2в) и выходной сигнал Z(t) (фиг. 2г) устройства замораживаются на уровнях, непосредственно предшествующих моменту идентификации импульсной помехи, то есть

моменту выполнения условия

le(t)l-B.

В тех случаях, когда характер поведения входного сигнала (по скорости его изменения) занимает промежуточное положение

между отсутствием и наличием импульсной помехи, принимается компромиссное решение: при замкнутом электронном ключе 3 на вход элемента интегрирования 4 и на второй вход сумматора 5 поступает ограниченный по уровню сигнал AsigbJE (t), так как в этих случаях выполняется условие: А E(t) В

Воздействие ограниченного сигнала на входе интегратора фиксирует максимальную скорость изменения выходного сигнала Y(t) интегратора и. выходного сигнала Z(t) устройства.

Таким образом, в устройстве при воздействии импульсной помехи в момент

идентификации помехи замораживаются уровни сигналов на обоих входах, а следовательно, и на выходе сумматора 5.

Формула изобретения Устройство защиты от импульсных помех, содержащее соединенные последовательно вычитатель, суммирующий вход которого является входом устройства, двусторонний ограничитель, электронный ключ, элемент интегрирования, выход которого соединен с вычитающим входом вычи- тателя, и сумматор, выход которого

является выходом устройства, а также элемент, сравнения модуля сигнала с пороговым уровнем, вход и выход которого соединены соответственно с выходом вычи- тателя и с управляющим входом электронного ключа, отличающеес я тем, что, с целью увеличения помехозащищенности, другой вход сумматора соединен с выходом двустороннего ограничителя.

| Устройство для защиты от импульсных помех | 1987 |

|

SU1483646A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1993-02-23—Публикация

1990-05-03—Подача