Изобретение относится к импульсной технике и может быть использовано в устройствах автоматики, вычислительной и контрольно-измерительной техники.

Цель изобретения - расширение функциональных возможностей устройства за счет обеспечения диагностики нарушения последовательности чередования импульсов.

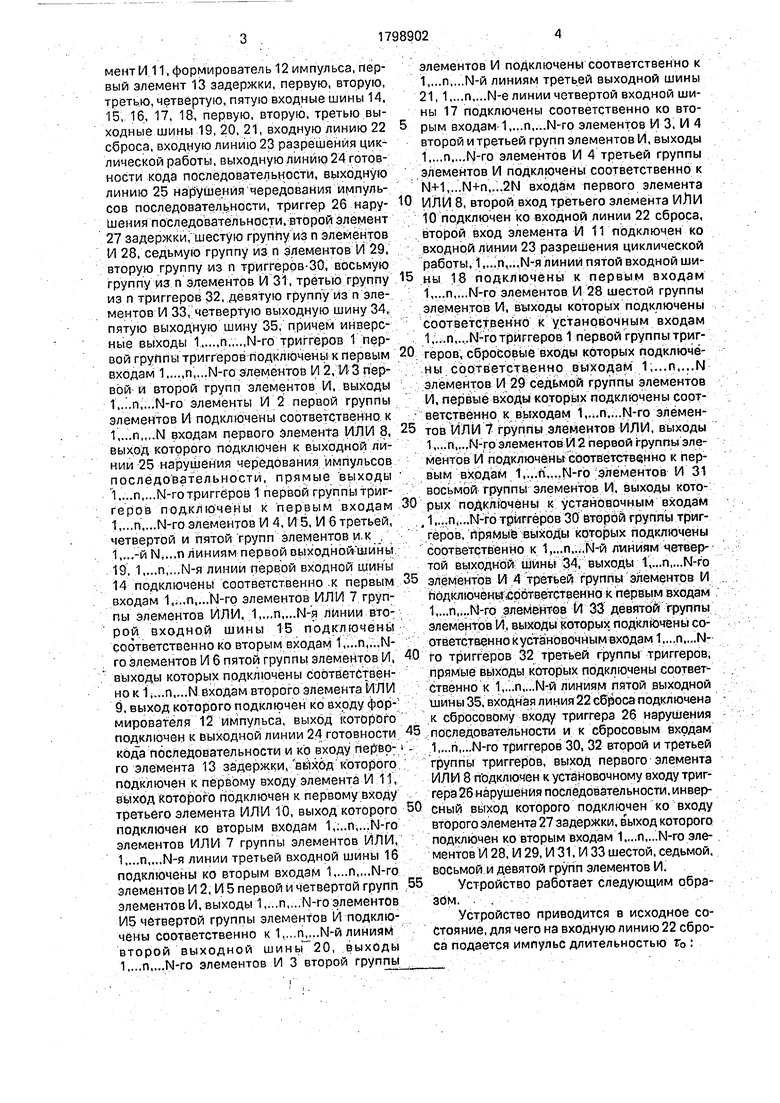

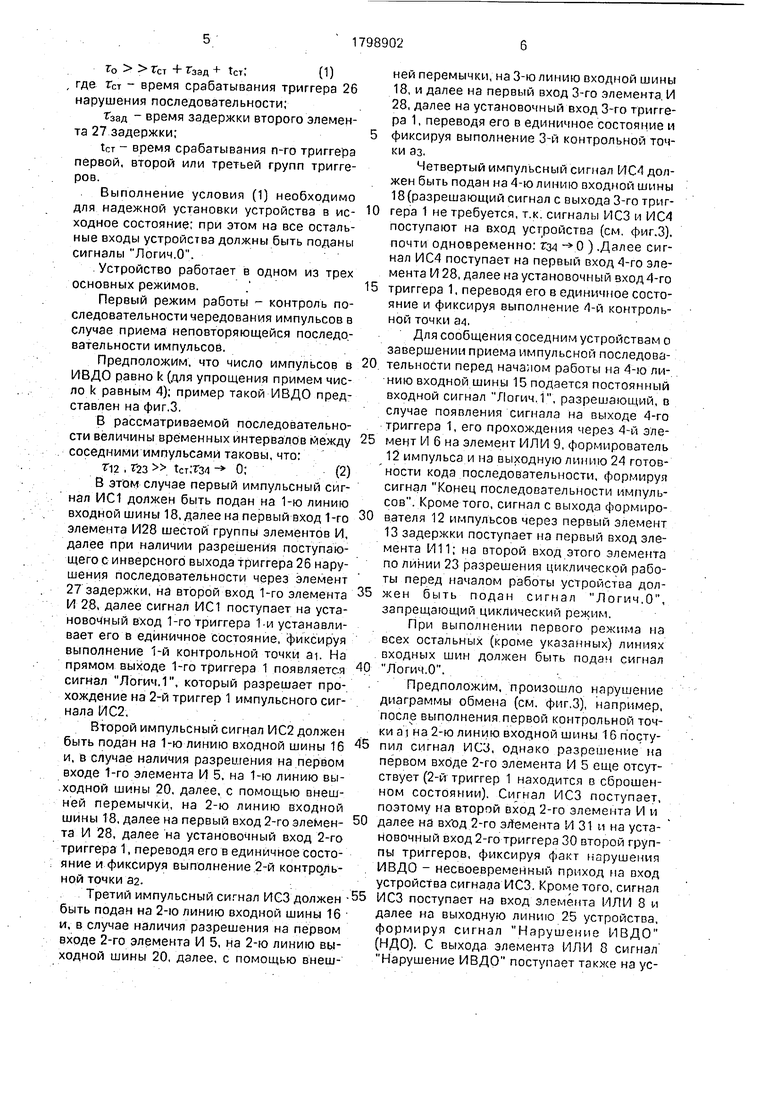

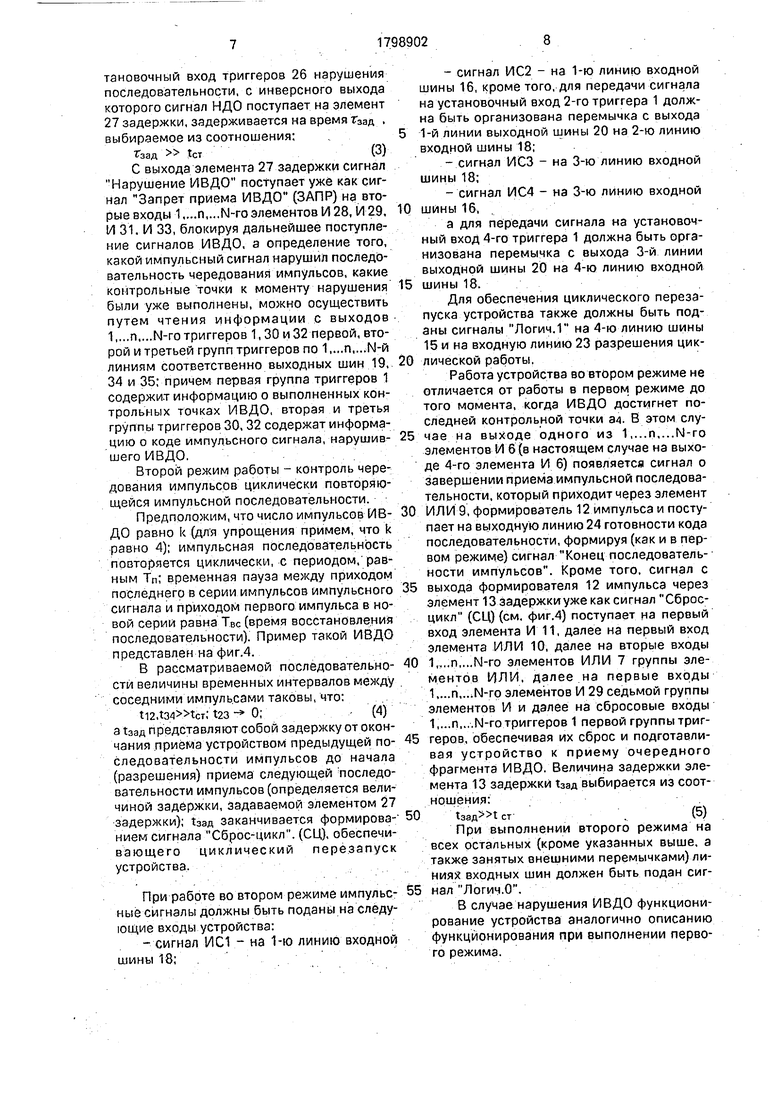

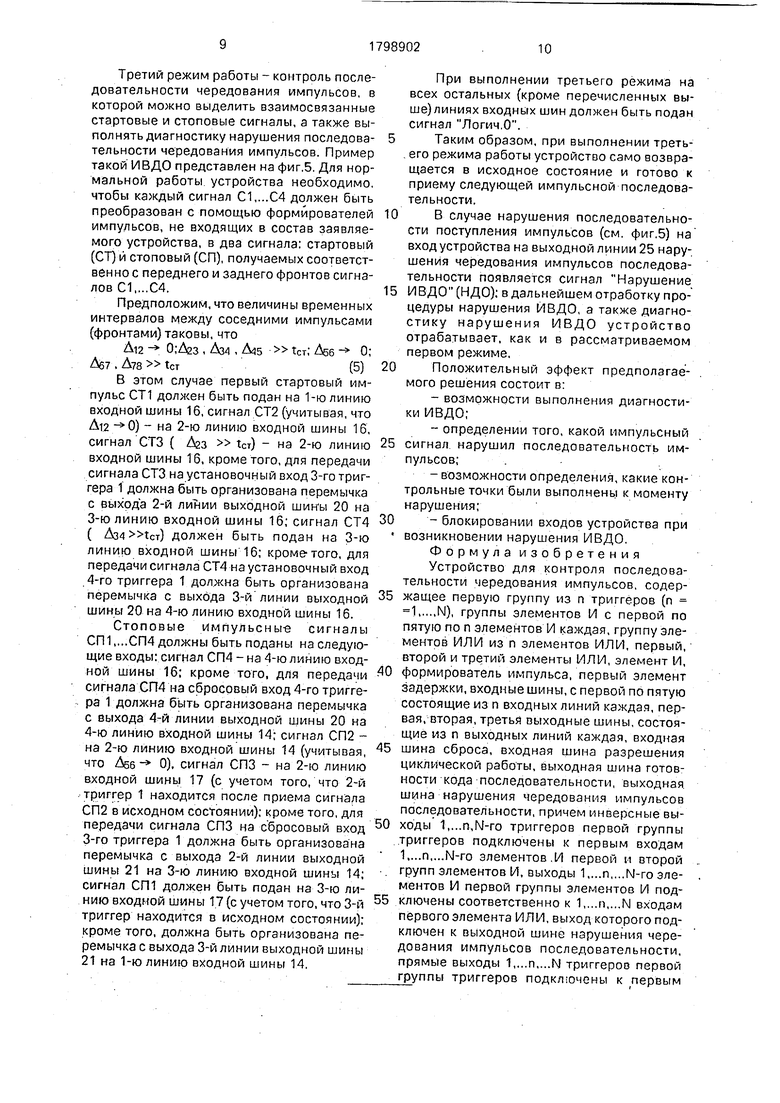

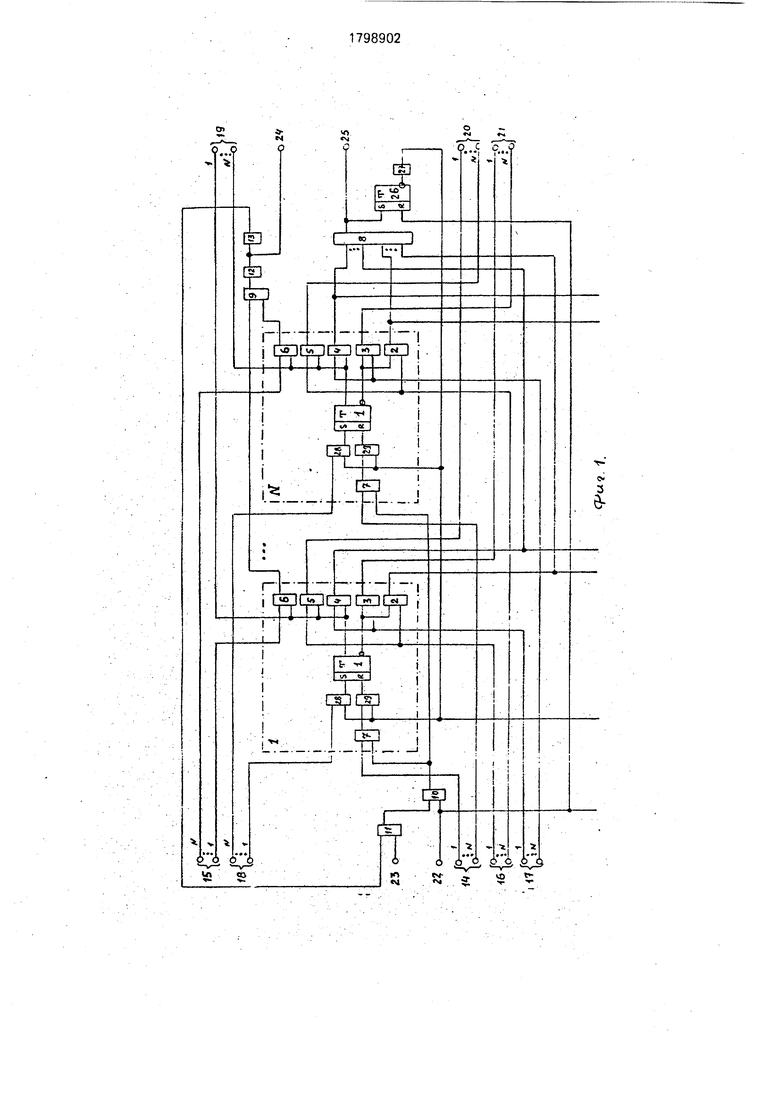

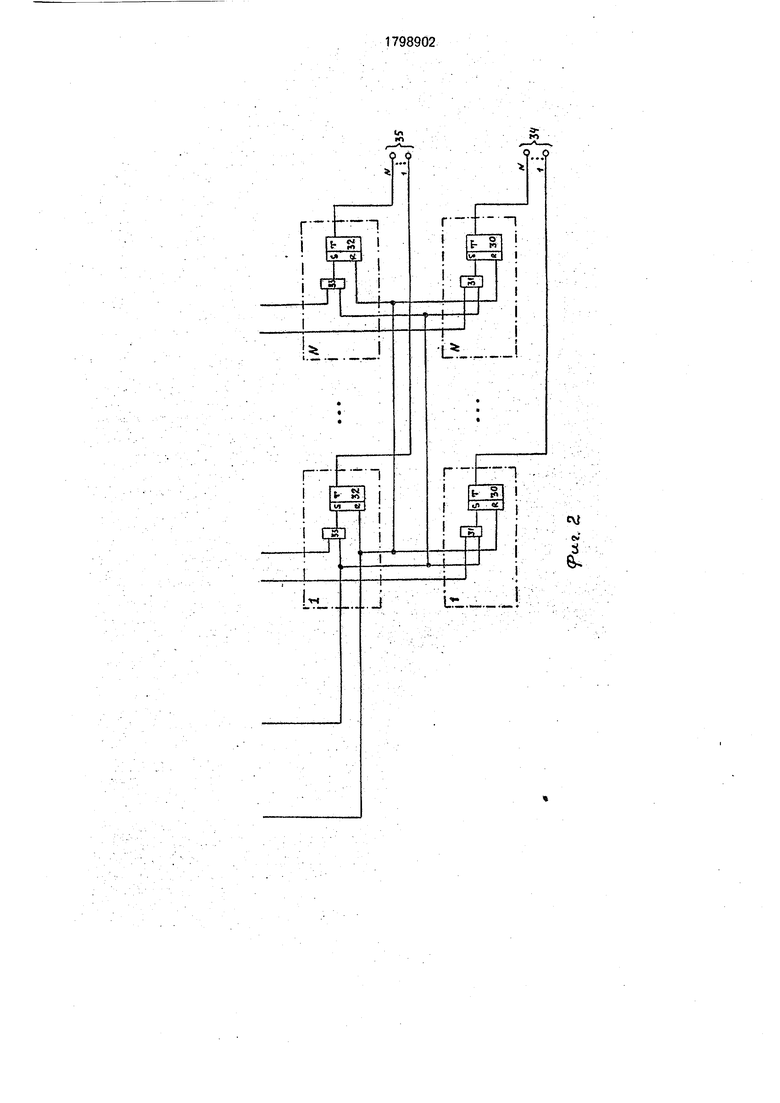

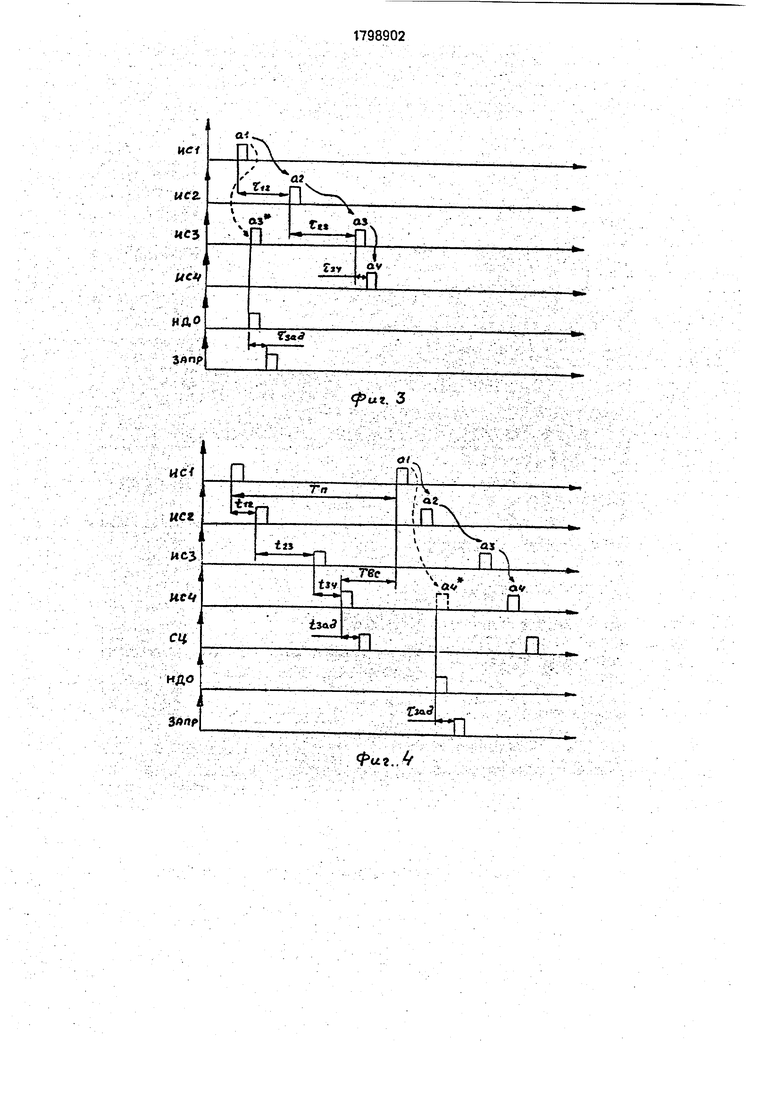

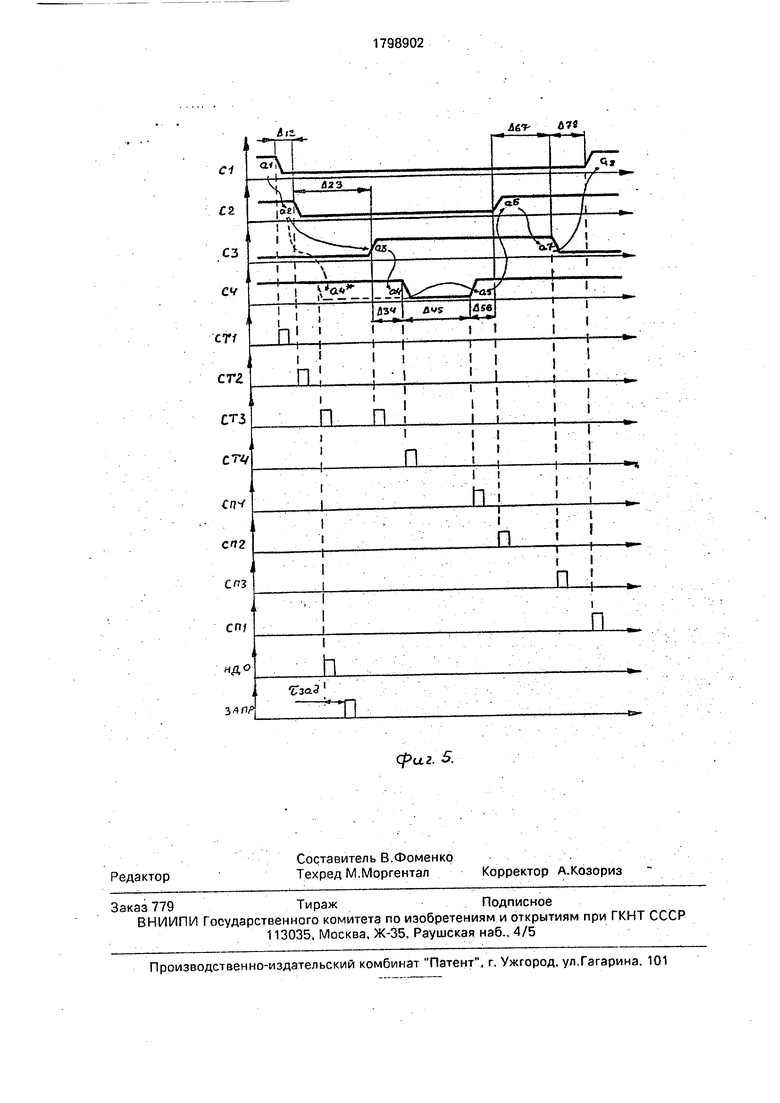

На фиг.1, 2 приведена структурная схема устройства для контроля последовательности чередования импульсов: на фиг.З - импульсная временная диаграмма обмена, представленная в виде циклически не повторяющейся последовательности импульсов, в которой возможно выполнение диагностики нарушения последовательности чередования импульсов; на фиг.4 - ИВДО, представленная в виде циклически по- . вторяющейся последовательности импульсов, в которой возможно выполнение диагностики нарушения последовательности чередования импульсов: на фиг.5 -. ИВ- ДО в виде последовательности импульсов, в которой можно выделить взаимосвязанные стартовые и стоповые сигналы и возможно выполнение диагностики нарушения последовательности чередования импульсов.

Устройство для контроля последовательности чередования импульсов содержит первую группу из n(n ) триггеров 1, первую группу из п элементов И 2, вторую группу из п элементов И 3,... пятую группу из п элементов И 6, группу из п элементов ИЛИ 7, первый элемент ИЛИ 8, второй элемент ИЛИ 9, третий элемент ИЛИ 10, элеXI Ю 00

ю о ю

мент И. 11, формирователь 12 импульса, первый элемент 13 задержки, первую, вторую, треть.ю, четвёртую, пятую входные шины 14, 15, 16, 17, 18, первую, вторую, третью выходные шины 19, 20, 21, входную линию 22 сброса, входную линию 23 разрешения циклической работы, выходную линию 24 готовности кода последовательности, выходную линию 25 нарушения чередования импульсов последовательности, триггер 26 нару- шения последовательности, второй элемент 27 задержки шестую группу из п элементов И 28. седьмую группу из п элементов И 29, вторую группу из п триггеррв-ЗО, восьмую группу из п элементов И 31, третью группу из п триггеров 32, девятую группу из пэпе- ментов И 33, четвертую выходную шину 34,: пятую выходную шину 35, причем инверсные выходы 1.,...,n,...,N-ro триггеров 1 пер- вой групгш триггеров подключены к первым входам 1,...,n,...N-ro элементов И 2, W3 первой и второй групп элементов И, выходы 1,..n,... N-ro элементы И 2 первой группы элементов 14 подключены соответственHQ.K 1,...n,,..N входам первого элемента ИЛИ 8, выход которого подключен к выходной линии 25 нарушения чередования импульсов последовательности, прямые выходы l....n....N-тотриггеров 1 первой группы триггеров подключены к первым входам 1,...n,...N-ro элементов И 4, И 5, И б третьей, четвертой и пятой групп элементов и.к. 1,...- и N .. .п л и н и я м п ер в о и вы х рд н ой ши н fat 19, 1,...п,,..М-я линии первой входной шины 14 подключены соответственно,к первым входам 1,.„п,„.М-го элементов ИЛИ 7. группы элементов ИЛИ, 1,.,.п,...М-я линии второй входной шины 15 подключены соответственно ко вторым входам 1,...n,,.,N- го элементов И б пятой группы элементов И, выходы которых подключены соответственно к ij..;.n,...N входам второго элемента |/ШVI 9, выход которого подключен ко входу формирователя 12 импульса, выход которого подключен к выходной линии 24 готовности кода последовательности и ко входу пер;врго элемента 13 задержки, вйхбд которого подключен к первому входу элемента И 11, выход которого подключен к первому входу третьего элемента ИЛИ 10, выход которого подключен ко вторым входам 1,...n,...N-ro элементов ИЛИ 7 группы элементов ИЛИ, 1,...п,.,.М-я линии третьей входной шины 16 подключены ко вторым входам 1,...n,...N-ro элементов И 2, И 5 первой и четвертой групп элементов И, выходы 1 ,..,n,,,.N-ro элементов И5 четвертой группы элементов И подключены соответственно к 1,,,,rv..N-u линиям второй выходной шины 20, выходы 1...n,...N-ro элементов И 3 второй группы

элементов И подключены соответственно к 1.,...п,„.М-й линиям третьей выходной шины 21,1,...n,...N-e линии четвертой входной шины 17 подключены соответственно ко вторым входам 1,...n,...N-ro элементов ИЗ, И 4 второй и третьей групп элементов И, выходы 1,...n,...N-rp элементов И 4 третьей группы элементов И подключены соответственно к M+1,...N+n,.;,2N входам первого элемента ИЛИ 8, второй вход третьего элемента ИЛИ 10 подключен ко входной линии 22 сброса, второй вход элемента И 11 пЬдключен ко входной линии 23 разрешения циклической работы, 1 ,.„п,„,1М-я линий пятой входной шины 18 подключены к первым входам 1,...n,...N-ro элементов И 28 шестой группы элементов И, выходы которых подключены соответственно к установочным входам 1,..,п,.,.М--го триггеров первой группы триггеров, сбросовые входы которых подключё- ны соответственно выходам 1 ;...n,...N элементов И 29 седьмой группы элементов И, первые входы которых подключены соответственно к выходам 1,.;.п,...N-ro элементов ИЛИ 7 группы элементов ИЛИ, выходы 1,..;n,,.,F4-ro элементов И 2 первой группы элементов И подключены соответственно к первым входам 1,..п .,,,М-го элементов Л 31 восьмой группы элементов И. выходы которых подкшочёны к установочным входам . 1 ,;.;П,.,. TpkrrepOB 30 вторбй группы триггеров, прямые выходы которых подключены соответртвенно к 1,.,.п,.;. линиям четвертой выходной шйньГ 34, выходы tt...n,..,N-ro элементбв И 4 третьей группы элементов И пбдключёни йрбтветственно к первым входам 1,...п,...№-го злеМентов И 33 девятой группы элементов И, выходы которых подключены соответственно установочным входам 1, ...п.,..N- го триггеров 32 третьей группы триггеров, прямые выходы которых подключены соответственно к 1,„.п,...М-й линиям пятой выходной шины 35, входная линия22 сброса подключена к сбросовому входу триггера 26 нарушения последовательности и к сбросовым входам 1,...n,...N-ro триггеров 30, 32 второй и третьей группы триггеров, выход первого элемента ИЛИ 8 подключен к установочному входу триггера 26 нарушения последовательности, инверсный выход которого подключен ко входу второго элемента 27 задержки, выход которого подключен ко вторым входам 1....n,...N-ro элементов VI 28, И 29, И 31. И 33 шестой, седьмой, восьмой:и девятой групп элементов И.

Устройство работает следующим образом. ..-

Устройство приводится в исходное состояние, для чего на входную линию 22 сброса подается импульс длительностью г0 :

То ГСТ +Гзад+ tCT;(1)

где гст - время срабатывания триггера 26 нарушения последовательности;

Тзад время задержки второго элемента 27 задержки;

tcr время срабатывания n-го триггера первой, второй или третьей групп триггеров.

Выполнение условия (1) необходимо для надежной установки устройства в исходное состояние; при этом на все остальные входы устройства должны быть поданы сигналы Логич.О.

.Устройство работает в одном из трех основных режимов.

Первый режим работы - контроль последовательности чередования импульсов в случае приема неповторяющейся последовательности импульсов..

Предположим, что число импульсов в ИВДО равно k (для упрощения примем число k равным 4); пример такой ИВДО представлен на фиг.З.

В рассматриваемой последовательности величины временных интервалов между соседними импульсами таковы, что;

Т12 , Г2з tCT;T34 - 0;(2)

В этом случае первый импульсный сигнал ИС1 должен быть подан на 1-ю линию входной шины 18, далее на первый вход 1-го элемента И28 шестой группы элементов И, далее при наличии разрешения поступающего с инверсного выхода триггера 26 нарушения последовательности через элемент 27 задержки, на второй вход 1-го элемента И 2.8, далее сигнал ИС1 поступает на установочный вход 1-го триггера 1-й устанавливает его в единичное состояние, фиксируя выполнение 1-й контрольной точки ai. На прямом выходе 1-го триггера 1 появляется сигнал Логич.1, который разрешает прохождение на 2-й триггер 1 импульсного сигнала ИС2.

Второй импульсный сигнал ИС2 должен быть подан на 1-ю линию входной шины 16 и, в случае наличия разрешения на первом входе 1-го элемента И 5, на 1-ю линию вы- .ходной шины 20, далее, с помощью внешней перемычки, на 2-ю линию входной шины 18, далее на первый вход 2-го элемента И 28, далее на установочный вход 2-го триггера 1, переводя его в единичное состояние и фиксируя выполнение 2-й контрольной ТОЧКИ 32.

Третий импульсный сигнал ИСЗ должен быть подан на 2-ю линию входной шины 16 и, в случае наличия разрешения на первом входе 2-го элемента И 5, на 2-ю линию выходной шины 20, далее, с помощью внешней перемычки, на 3-ю линию входной шины 18, и далее на первый вход 3-го элемента. И 28, далее на установочный вход 3-го триггера 1, переводя его в единичное состояние и

фиксируя выполнение 3-й контрольной точки аз.

Четвертый импульсный сигнал ИС4 должен быть подан на 4-ю линию входной шины 18 (разрешающий сигнал с выхода 3-го триггера 1 не требуется, т.к. сигналы ИСЗ и ИС4 поступают на вход устройства (см. фиг.З), почти одновременно: ТЗА 0 ) .Далее сигнал ИС4 поступает на первый вход 4-го элемента И 28, далее на установочный вход 4-го

триггера 1, переводя его в единичное состояние и фиксируя выполнение 4-й контрольной ТОЧКИ Э4.

Для сообщения соседним устройствам о завершении приема импульсной последовательности перед началом работы на 4-ю линию входной шины 15 подается постоянный входной сигнал Логич.1, разрешающий, в случае появления сигнала на выходе 4-го триггера 1, его прохождения через 4-й элемент И 6 на элемент ИЛИ 9, формирователь

12 импульса и на выходную линию 24 готовности кода последовательности, формируя сигнал Конец последовательности импульсов. Кроме того, сигнал с выхода формиро- вателя 12 импульсов через первый элемент

13 задержки поступает на первый вход элемента И11; на второй вход этого элемента по линии 23 разрешения циклической работы перед началом работы устройства должен быть подан сигнал Логич.О, запрещающий циклический режим.

При выполнении первого режима из всех остальных (кроме указанных) линиях входных шин должен быть подан сигнал

Логич.О.. -.. .

Предположим, произошло нарушение диаграммы обмена (см. фиг.З), например, после выполнения.первой контрольной точки а 1 на 2-ю линию входной шины 16 п оступил сигнал ИСЗ, однако разрешение на первом входе 2-го элемента И 5 еще отсутствует (2-й триггер 1 находится в сброшенном состоянии). Сигнал ИСЗ поступает, поэтому на второй вход 2-го элемента И и

далее на вх од 2-го элемента И 31 и на установочный вход 2-го триггера 30 второй группы триггеров, фиксируя факт нарушения ИВДО - несвоевременный приход на вход устройства сигнала ИСЗ. Кроме того, сигнал

ИСЗ поступает на вход элемента ИЛИ 8 и далее на выходную линию 25 устройства, формируя сигнал Нарушение ИВДО (НДО). С выхода элемента ИЛИ 8 сигнал Нарушение ИВДО поступает также на установочный вход триггеров 26 нарушения последовательности, с инверсного выхода которого сигнал НДО поступает на элемент 27 задержки, задерживается на время т3ад . выбираемое из соотношения;

Гзад tci(3)

С выхода элемента 27 задержки сигнал Нарушение ИВДО поступает уже как сигнал Запрет приема ИВДО (ЗАПР) на вторые входы 1 ,...n,...N-ro элементов И 28, И 29, И 31. И 33, блокируя дальнейшее поступление сигналов ИВДО, а определение того, какой импульсный сигнал нарушил последовательность чередования импульсов, какие контрольные точки к моменту нарушения были уже выполнены, можно осуществить путем чтения информации с выходов 1 ,...n,...N-ro триггеров 1,30 и 32 первой, второй и третьей групп триггеров по 1 ,...n,...N-ft линиям соответственно выходных шин 19, 34 и 35; причем первая группа триггеров 1 содержит информацию о выполненных контрольных точках ИВДО, вторая и третья группы триггеров 30,32 содержат информацию о коде импульсного сигнала, нарушившего ИВДО.

Второй режим работы - контроль чередования импульсов циклически повторяющейся импульсной последовательности.

Предположим, что число импульсов ИВДО равно к (дл я упрощения примем, что k равно 4); импульсная последовательность повторяется циклически, с периодом. равным Тп; временная пауза между приходом последнего в серии импульсов импульсного сигнала и приходом первого импульса в новой серии равна Твс (время восстановления последовательности). Пример такой ИВДО представлен на фиг.4.

В рассматриваемой последовательности величины временных интервалов между соседними импульсами таковы, что:

ti2, t23 - 0;.. .- (4) а Гзад представляют собой задержку от окончания .приёма устройством предыдущей последовательности импульсов до начала (разрешения) приема следующей последовательности импульсов (определяется величиной задержки, задаваемой элементом 27 задержки); т,3эд заканчивается формирова- нием сигнала Сброс-цикл. (СЦ), обеспечи- вающего циклический перезапуск устройства.

При работе во втором режиме импульсные сигналы должны быть поданы на следующие входы устройства:;

- сигнал ИС1 - на 1-ю линию входной шины 18;

- сигнал ИС2 - на 1-ю линию входной шины 16, кроме того, для передачи сигнала на установочный вход 2-го триггера 1 должна быть организована перемычка с выхода 1-й линии выходной шины 20 на 2-ю линию входной шины 18;

- сигнал ИСЗ - на 3-ю линию входной шины 18;

- сигнал ИС4 - на 3-ю линию входной

шины 16,

а для передачи сигнала на установочный вход 4-го триггера 1 должна быть организована перемычка с выхода 3-й линии выходной шины 20 на 4-ю линию входной

шины 18.

Для обеспечения циклического перезапуска устройства также должны быть поданы сигналы Логич.1 на 4-ю линию шины 15 и на входную линию 23 разрешения циклической работы.

Работа устройства во втором режиме не отличается от работы в первом режиме до того момента, когда ИВДО достигнет последней контрольной точки 34. В этом случае на выходе одного из 1,...n,...N-ro элементов И 6 (в настоящем случае на выходе 4-го элемента И 6) появляется сигнал о завершении приема импульсной последовательности, который приходит через элемент

ИЛИ 9, формирователь 12 импульса и поступает на выходную линию 24 готовности кода последовательности, формируя (как и в первом режиме) сигнал Конец последовательности импульсов. Кроме того, сигнал с

выхода формирователя 12 импульса через элемент 13 задержки уже как сигнал Сброс- цикл (СЦ) (см, фиг.4) поступает на первый вход элемента И 11, далее на первый вход элемента ИЛИ 10, далее на вторые входы

1,,..n,...N-ro элементов ИЛИ 7 группы элементов ИЛИ, далее на первые входы 1 ,...п,..,М-гр элементов И 29 седьмой группы элементов И и далее на сбросовые входы 1 ,...n,...N-ro триггеров 1 первой группы триггеров, обеспечивая их сброс и подготавливая устройство к приему очередного фрагмента ИВДО. Величина задержки элемента 13 задержки 13ад выбирается из соотношения:

ст. (5) При выполнении второго режима на всех остальных (кроме указанных выше, а также занятых внешними перемычками) линиях входных шин должен быть подан сигнал Логич.О.

В случае нарушения ИВДО функционирование устройства аналогично описанию функционирования при выполнении первого режима.

Третий режим работы - контроль последовательности чередования импульсов, в которой можно выделить взаимосвязанные стартовые и стоповые сигналы, а также выполнять диагностику нарушения последовательности чередования импульсов. Пример такой ИВДО представлен на фиг,5. Для нормальной работы устройства необходимо. чтобы каждый сигнал С1....С4 должен быть преобразован с помощью формирователей импульсов, не входящих в состав заявляемого устройства, в два сигнала: стартовый (СТ) и стоповый (СП), получаемых соответственно с переднего и заднего фронтов сигналов С1....С4.

Предположим, что величины временных интервалов между соседними импульсами (фронтами) таковы, что

Ai2 - 0;А2з, AM - Л« tcr; Ase - 0;

A57.(5)

В этом случае первый стартовый импульс СТ1 должен быть подан на 1-ю линию входной шины 16, сигнал СТ2 (учитывая, что Д|2 ) - на 2-ю линию входной шины 16, сигнал СТЗ ( А23 tcr) - на 2-ю линию входной шины Тб, кроме того, для передачи сигнала СТЗ на установочный вход 3-го триггера 1 должна быть организована перемычка с выхода 2-й лийии выходной шин ы 20 на

3-ю линию входной шины 16; сигнал СТ4 ( Дз4 tcr) должен быть подан на 3-ю линию входной шины 16; кроме-того, для передачи сигнала СТ4 на установочный вход

4-го триггера 1 должна быть организована перемычка с выхода 3-й линии выходной шины 20 на 4-ю линию входной шины 16.

Стоповые импульсны-е сигналы СП 1 ,,..СП4 должны быть поданы на следующие входы: сигнал СП4-на 4-ю линию входной шины 16; кроме того, для передачи сигнала СП4 на сбросовый вход 4-го триггера 1 должна быть организована перемычка с выхода 4-й линии выходной шины 20 на 4-ю линию входной шины 14; сигнал СП2 - на 2-ю линию входной шины 14 (учитывая, что Ase 0), сигнал СПЗ - на 2-ю линию входной шины 17 (с учетом того, что 2-й триггер 1 находится после приема сигнала СП2 в исходном состоянии); кроме того, для передачи сигнала СПЗ на сбросовый вход 3-го триггера 1 должна быть организована перемычка с выхода 2-й линии выходной шины 21 на 3-ю линию входной шины 14; сигнал СП1 должен быть подан на 3-ю линию входной шины 17 (с учетом того, что 3-й триггер находится в исходном состоянии); кроме того, должна быть организована перемычка с выхода 3-й линии выходной шины 21 на 1-ю линию входной шины 14.

При выполнении третьего режима на всех остальных (кроме перечисленных вы- ше)линиях входных шин должен быть подан сигнал Логич.О.

Таким образом, при выполнении треть- , его режима работы устройство само возвращается в исходное состояние и готово к приему следующей импульсной последовательности.

0 В случае нарушения последовательности поступления импульсов (см. фиг.5) на вход устройства на выходной линии 25 нарушения чередования импульсов последовательности появляется сигнал Нарушение

5 ИВДО(НДО): в дальнейшем отработку процедуры нарушения ЙВДО, а также диагностику нарушения ИВДО устройство отрабатывает, как и в рассматриваемом первом режиме.

0 Положительный эффект предполагаемого решения состоит в:

- возможности выполнения диагностики ИВДО;

- определении того, какой импульсный 5 сигнал нарушил последовательность импульсов;

-возможности определения, какие контрольные точки были выполнены к моменту нарушения; 0 - блокировании входов устройства при

возникновении нарушения ЙВДО. Формула изобретения Устройство для контроля последовательности чередования импульсов, содер5 жащее первую группу из п триггеров (п 1,...,N), группы элементов И с первой по пятую по п элементов И каждая, группу элементов ИЛИ из п элементов ИЛИ, первый, второй и третий элементы ИЛИ, элемент И,

0 формирователь импульса, первый элемент задержки, входные шины, с первой по пятую состоящие из п входных линий каждая, первая, вторая, третья выходные шины, состоящие из п выходных линий каждая, входная

5 шина сброса, входная шина разрешения циклической работы, выходная шина готовности кода последовательности, выходная, шина нарушения чередования импульсов последовательности, причем инверсные вы0 ходы 1,...п,М-го триггеров первой группы триггеров подключены к первым входам 1,...n,...N-ro элементов.И первой и второй

. групп элементов И, выходы 1,...n,...N-ro элементов И первой группы элементов И под- 5 ключены соответственно к 1,...n,...N входам первого элемента ИЛИ, выход которого подключен к выходной шине нарушения чередования импульсов последовательности, прямые выходы 1,...n,...N триггеров первой группы триггеров подключены к первым

входам 1,...n,...N элементов И третьей, четвертой и пятой групп элементов Пик 1,...n,.,.N линиям первой выходной шины, 1,...п,...М-я линии первой входной шины подключены соответственно к первым входам 1,...n,...N-ro элементов ИЛИ группы элементов ИЛИ, 1,..,п,-...М-я линий второй входной шины подключены соответственно к вторым входам 1,...n,...N-ro элементов И пятой группы элементов И, выходы которых подключены соответственно к 1,...n,...N входам второго элемента ИЛИ, выход которого подключен к входу формирователя импульсов, выход которого подключен к выходной шине готовности кода последовательности и к входу первого элемента задержки, выход которого подключен к первому входу элемента И, выход которого подключен к первому входу третьего элемента ИЛИ, выход которого подключен к вторым входам 1,...n,...N-ro элементов ИЛИ группы элементов ИЛИ, 1,...п,,..М-я линии третьей входной шины подключены к вторым входам 1,...n,.,.N-ro элементов И первой и четвертой групп элементов И, выходы 1....n,...N-ro элементов И четвертой группы элементов И подключены соответственно к (1,..,n,...N)-ft линиям второй выходной шины, выходы (1,...п,...1М)-го элементов И второй группы элементов И подключены соответственно к 1,...п,...М-й линиям третьей выходной шины, 1,,..n,...N-e линии четвертой входной шмны подключены соответственно ко вторым в ходам (1.,.n...N)-rq элементов И второй и третьей групп элементов И, выходы (1..,n...N)-ro элементов И третьей группы элементов И подключены соответственно к N+1...N+n...2N входам элемента ИЛИ, второй вход третьего элемента И подключен к входной шине сброса, второй вход элемента И подключен к входной шине разрешения циклической работы, отличающееся тем, что, с целью расширения функциональных возможностей устройства путем обеспечения диагностики нарушения последовательности чередования импульсов в режиме контроля последовательности с выделенными взаимосвязанными стартовыми и стоповыми сигналами, в него дополнительно введены шестая, седьмая, восьмая и девятая группы элементов И по n элементов И каждая, вторая и третья группы триггеров, состоящие из n триггеров каждая, второй элемент задержки, триггер нарушения последовательности, четвертая и пятая выходные шины из n выходных линий каждая, причем 1,...п,...М-я линии пятой входной шины подключены к первым входам 1,..,n,...N-ro элементов И шестой группы элементов И, выходы которых подключены соответственно к установочным входам 1,...n,...N-ro триггеров первой группы триггеров, сбросовые выходы которых подключены соответственно к выходам 1,,..n,...N элементов И седьмой группы элементов И, первые входы которых подключены соответственно к выходам 1,...n,...N-ro элементов ИЛИ группы элементов ИЛИ, выходы

1 ,...n,...N-ro элементов И первой группы элементов И подключены соответственно к первым входам 1,...n,...N-ro элементов И восьмой группы элементов И, выходы которых подключены к установочным входам

1,...п....N-ro триггеров второй группы триггеров, прямые выходы которых подключены соответственно к 1....п,...М-й линиям четвертой выходной шины, выходы 1,...n,...N-ro элементов Л третьей группы элементов И

подключены соответственно к первым вхо- дам 1,..,n,...N-ro элементов И девятой группы элементов -И, , выходы которых подключены соответственно к установочным входам 1,..,n,...N-ro триггеров третьей

группы триггеров, прямые выходы которых подключены соответственно к . 1,.-..п,... М-й линиям пятой выходной шины, входная шина сброса подключена к сбросовому входу триггера нарушения последовательности и

к сбросовым входам 1,...n,...N триггеров второй и третьей групп триггеров, выход первого элемента ИЛИ подключен к установочному входу триггера нарушения последовательности, инверсный выход которого подключен к входу второго элемента задержки, выход которого подключен к вторым входам 1,...n,.,.N-ro элементов И шестой., седьмой, восьмой и девятой групп элементов И..8

о

00 СП

гфиг. 3

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля последовательности чередования импульсов | 1990 |

|

SU1800602A1 |

| Устройство для контроля последовательности чередования импульсов | 1989 |

|

SU1651363A1 |

| Устройство для контроля последовательности чередования импульсов | 1986 |

|

SU1401587A1 |

| Устройство для вычисления характеристик сетевых графов | 1985 |

|

SU1290343A1 |

| Умножитель частоты | 1979 |

|

SU807281A1 |

| Устройство для контроля последовательности чередования импульсов | 1987 |

|

SU1497729A1 |

| Пороговое устройство (его варианты) | 1984 |

|

SU1352449A1 |

| Распределитель импульсов | 1980 |

|

SU919071A1 |

| Устройство для контроля последовательности чередования импульсов | 1986 |

|

SU1406757A1 |

| Устройство для обнаружения нарушений в чередовании импульсов | 1982 |

|

SU1042172A1 |

Изобретение относится к импульсной технике и может быть использовано в устройствах автоматики, вычислительной и контрольно-измерительной техники, для контроля очередности прохождения импульсных сигналов, причем в случае нарушения последовательности возможно выполнение диагностики: определение импульсного сигнала, нарушившего последовательность, а также блокировка входа устройства от поступления остальных сигналов последовательности. Устройство содержит три группы триггеров по п (г, 1.....N) триггеров в каждой, девять групп элементов И из п элементов И каждая, группу элементов ИЛИ из п элементов ИЛИ, три элемента ИЛИ, элемент И, формирователь импульса, первый и второй элементы задержки, триггер нарушения последовательности, пять входных шин, пять выходных шин, входную шину сброса, входную шину разрешения циклической работы, выходную шину готовности кода последовательности, выходную шину нарушения чередования импульсов последовательности. 5 ил. tn

Фиг.,1/

| Устройство для контроля последовательности чередования импульсов | 1986 |

|

SU1406757A1 |

| Устройство для контроля последовательности чередования импульсов | 1989 |

|

SU1651363A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1993-02-28—Публикация

1990-08-22—Подача