(54) УМНОЖИТЕЛЬ ЧАСТОТЫ

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты | 1983 |

|

SU1176439A1 |

| Умножитель частоты периодических импульсов | 1980 |

|

SU935956A1 |

| Умножитель частоты | 1980 |

|

SU868756A1 |

| Дискретный умножитель частоты | 1977 |

|

SU736099A1 |

| Устройство для определения первой разности частотно-импульсного сигнала | 1982 |

|

SU1043675A1 |

| Умножитель частоты следования импульсов | 1982 |

|

SU1038943A1 |

| Умножитель частоты | 1990 |

|

SU1797113A1 |

| Умножитель частоты | 1979 |

|

SU807322A1 |

| Устройство для дифференцирова-Ния чАСТОТы СлЕдОВАНия иМпульСОВ | 1978 |

|

SU798881A1 |

| Устройство для преобразования разности частотно-импульсных сигналов в код | 1976 |

|

SU750728A1 |

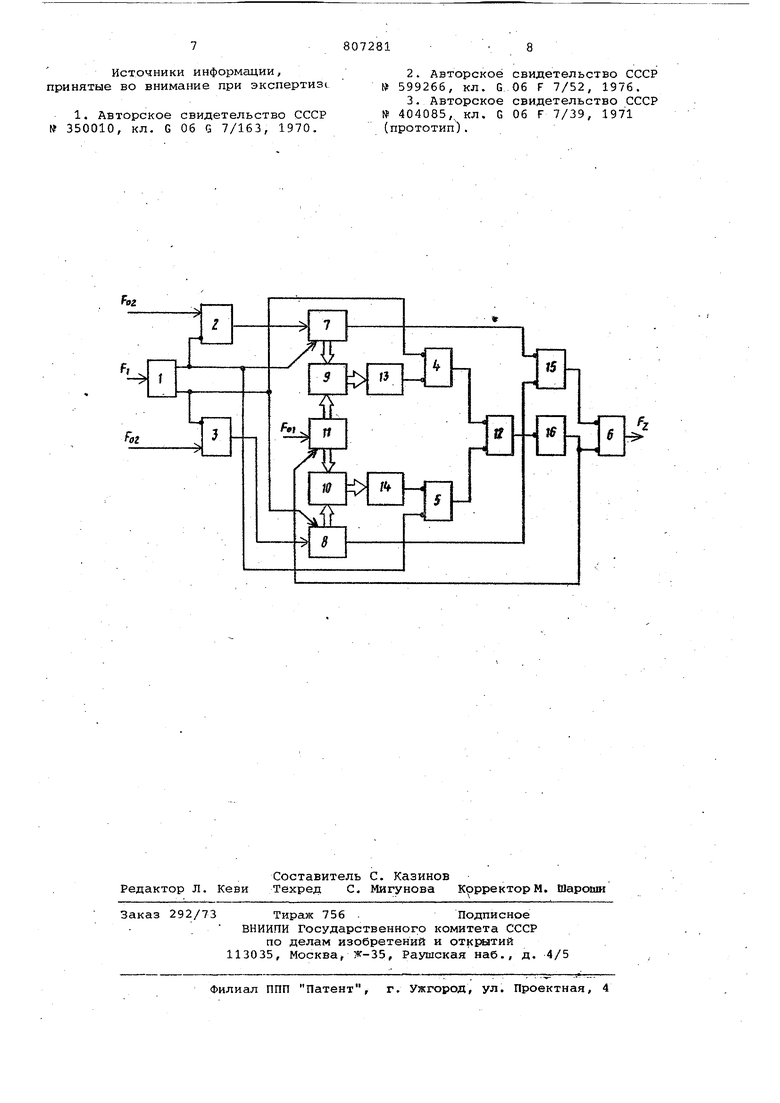

Изобретение относится к автоматй ке и вычи-слительной технике и может быть использовано в качестве вычислительного устройства, совершающего математические операции над сигнала ми, -представленными в частотно-импульсной форме. Известен умножитель частоты, содержащий генера тор опорных частот, реверсивный счетчик, преобразовател код-напряжение, генератор управляемой частоты, селектор периода, ключ счетчик, делитель частоты и двоичный умно хитель 1 . Недостатком устройства является пониженная динамическая точность умнокения частоты. Известен также умножитель частоты содержащий диФференцируюкото цепь, генераторы опорных частот, элементы и группы элементов И, суммирукщий и вычитающий счетчики, регистр памяти и блок фиксации нуля 2 . Недостатком данного устройства яв ляется зависимость выходной частоты от скважности входного частотно-импульсного сигнала. Наиболее близким к предлагаемому является умножитель, частоты, содер- Жсцций первый элемент ИЛИ, делитель частоты, подключенный счетным входом к входной шине первой опорной частоты, и первый и второй элементы И, соединенные выходами соответственно с счетньоми входами первого и второго п-разрядных счетчиков, причем первый счетчик подключен выходами (n-l)-ro разрядов к первым входам элементов И первой группы, а входом обнуления к первому выходу триггера, счетный вход которого соединен с входной шиной умножаемой частоты, а вт.орой выход - с входом обнуления второго счетчика, подключенного выходами (п- 1)-го разрядов к первым входам элементов И второй группы, причем выходы элементов И обеих групп соединены с входами разрядов третьего счетчика, подключенного счетным входом к входной шине первой опорной частоты, а выходом - к выходной Шине умножителя частоты и к вторым входам элементов И обеих групп, соединенных третьими входами соответственно q первым и вторым выходами второго триггера, счетный вход которого подключен к выходу первого элемента ИЛИ, соединенного входс1ми с выходами первого триггера, причем первый и второй выходы второго триггера соответственно подключены к первым входам второго и первого элементов И, соединенных вторыми вхо дами с выходом делителя частоты З. Недостатками устройства являются ограниченные функциональные возможности, обусловленные невозможностью плавного изменения коэффициента умно жения, а также конструктивная сложйость умножителя частоты. Цель изобретения - обеспечение плавного изменения коэффициента умножения и упрощение умножителя частоты. Эта цель достигается тем, что в умножитель частоты, содержащий первый элемент ИЛИ, делитель частоты, подключенный счётным входом к входной шине первой опорной частоты и пе вый и второй элементы И, соединенные выходами соответственно с счетными входами первого и второго п-разрядных счетчиков, причем первый счетчик подключен выходами (п-1)-го-разрядов к первым входам элементов И первой группы, а входом обнуления - к перво му выходу триггера, счетный вход которого соединен с входной шиной умно жаемой частоты, а второй выход - с входом обнуления второго счетчика, подключенного выходами (n-l)-ro разрядов к первым входам элементов И второй группы, дополнительного введены второй, третий и четвертый элементы ИЛИ, третий, четвертый и пятый элементы И и формирователь импульсов подключенный входом к выходу первого элемента ИЛИ, соединенного входами с выходами третьего и четвертого элементов И,причем третий элемент И подклю чей первым входом к второму выходу триггера и к первому входу второго элемента И, а вторым входом - к выхо ду второго элемента ИЛИ, входы которого соединены с выходами элементов И первой группы, а четвертый элемент И подключен первым входом к первому выходу триггера и к первому входу первого элемента И, а вторым входом к выходу третьего элемента ИЛИ, вхо ды которого соединены с выходами эле ментов И второй группы, причем вторые входы элементов И обеих групп подключены к выходам разрядов делителя частоты, соединенного установоч ным входом с выходом формирователя импульсов и с первым входом пятого элемента И, подключенного выходом к выходной шине умножителя частоты, а вторым входом - к выходу четверто го элемента ИЛИ, входы которого сое динены с выходом п-го разрядного пе вого и п-го разряда второго счетчиков , а вторые входы первого и второ го элементов И подключены к входным шинам второй опорной частоты. На чертеже изображена блок-схема умножителя частоты. Умножитель частоты содержит триг гер 1, элементы И 2-6, п-разрядные счетчики 7 и 8, группы элементов И и 10, делитель 11 частоты, элементы ИЛИ 12-15 и формирователь 16 импульсов . Триггер 1 соединен счетным входом с входной шиной умножаемой частоты F , первым выходом - с входом обнуления первого счетчика Тис первыми . входами первого 2 и четвертого 5 элементов И, а вторым выходом - с входом обнуления второго счетчика Вис первыми входами второго3 и таетьего 4 элементов И. Счетчик 7 подключен счетным входом к выходу элемента И 2, а выходами (n-l)-ro разрядов - к пер-вым входам элементов И 9 первой группы. Счетчик 8 соединен счетным входом с выходом элемента И 3, а выходами (n-l)-ro разрядов - с первыми входами элементов И 10 второй группы. Вторые входы элементов И 9 и 10 обеих групп, пoдкjIЮчeны к выходам разрядов делителя 11 частоты, соединенного счетным входом с входной шиной первой опорной частоты F. а установочным входом - с выходом формирователя 16 импульсов. Вход формирователя импульсов подключен к выходу первого элемента ИЛИ 12, соединенного входами с выходами элементов И 4 и 5, Вы- . ходы элементов И 9 перовой групгал подключены к входам второго элемента ИЛИ 13, соединенного выходом с вторым входом элемента И 4, а выходы элементов И 10 группы подключены к входам третьего элемента-ИЛИ 14, выход которого соединен с вторым входом элемента И 5, Вторые входа элементов И 2 и 3 подключены к входным шинам второй опорной частоты Выход п-го разряда счетчика 7 и выход п-го разряда счетчика 8 соединены с входами четвертого элемента ИЛИ 15. Пятый элемент И 6 подключен первым входом к выходу формирователя 16, вторым входом - к выходу элемента ИЛИ 15, а выходом - к выходной шине умножителя частоты. Умножитель частоты работает следующим образом. i Импульсами умножаемой частоты F,( возбуждается триггер 1, поочередно открывающий элементы И 2. и 3, которые, обеспечивают подачу в различные периоды времени импульсов опорной частоты F(j2 на входы счетчиков 7 и 8., причем перед записью этих импульсов в роответствующий счетчик 7 или 8 проиаводится его обнуление передним фронтом разрешающего сигнала, снимаемого с выходов триггера 1. Пусть в рассматриваемый момент времени на первом выходе триггера 1 сформировался разрешающий сигнал, а на .втором - запрещающий. Если умножитель до рассматриваемого момента времени находится во включенном состоя НИИ, то в счетчике 8 будет код-N, равный N Fo2/ v С поступлением,.им ульсовпервой опорной частоты ia счетный вход делителя 11 частоты (все разряды которого в исходном со стоянии установлены в 1) на выход разрядов делителя 11 формируется им пульсы длительность. 2 О ( , 2 TQ 2 to .... , TO , где перио частоты FO;( . В зависимости от значения кода чи ла, записанного в счетчик 8, через Группу элементов И 10 соответствующие импульсы, снимаемые с выходов со ответствующих разрядов делителя 11, проходят на входы элемента ИЛИ 14, причем длительность импульсов на вы ходе элемента ИЛИ 14 определяется ра венством Так как в рассматриваемый момент вре мени элемент и 5 открыт разреша пщим сигналом с первого выхода триггера 1, то импульс длительностью проходит через элементы И 5 и ИЛИ 12 на вход формирователя 16 импульсов., на выходе которого сформированы импульсы, соответствующие моментам переднего и заднего фронта импульса длительностью . Импульс с выхода формирователя 16 поступает через И б, открытый нулевым сигналом tio своему рторому (запрешающему) вхо ду, на выход умножителя частоты и одновременно на установочный вход де лителя 11, в результате чезго все ра ряды делителя 11 устанавливают в еди ничное состояние и процесс формирова ния выходных импульсов повторяется. Таким образом, на выходе умножителя имеет место последовательность импульсов с периодом следования Ту, равным ь , откуда получаем, что частота следования Fj, выходных иМпульсов равна f F приходом второго периода сигнала F в формировании выходной импуль сной последовательности задействованы счетчик 7, группа элементов И 9, делитель 11, элементы ИЛИ 12 и 13, И, 4 и б и формирователь 16. Дополнительные п-ые разряды счетчиков 7 и 8 совместно с элементами ИЛИ 15 и И б используются для прекращения подачи импульсов на выход умножителя при понижении входной частоты F ни,же расчетного предела изменения. Если частота F выходит за нижний.предел, то на одном из счетчиков (импульсов) 7 или 8 в его п-ом разряде формируется запрещающий сигнал, который через элемент ИЛИ 15 закрывает по второму (запрещающему) входу элемент И 6. Таким образом, предлагае1«алй умножитель частоты в отличие от известного позволяет обеспечить плавное из/менение коэффициента умножения (за счет возможности независимого изменения параметров Q и Р02 при более простой реализации, достигаемой за счет исключения третьего счетчика. Дополнительным преимуществом предлагаемого умножителя частоты явдяется возможность деления входной частоты при Рд2 QA Формула изобретения Умножитель частоты, содержащий первый элемент ИЛИ, делитель частоты, подключенный счетным входом к входной шине первой опорной частоты, и первый и второй элементы И, соединенные выходами, соответственно с счетными входами первого и второго п-разрядных счетчиков, причем первый счетчик подключен выходами (n-l)-ro разрядов к первым входам элементов И первой группы, а входом обнуления - к первому выхсЗду триггера, счетный вход которе го соединен с входной шиной умножаемой частоты, а второй выход - с входом обнуления второго счетчика, подключенного выходами (-n-D-ro разрядов к первым входам элементов И второй группы, отличающийся тем, что, с целью обеспечения плавного изменения коэффициента умножения и упрощения умножителя частоты, в умножитель частоты дополнительно введены второй, третий и четвертый элементы ИЛИ, третий, четвертый и пятый элементы И и формирователь импульсов , подключенный входом к выходу первого элемента ИЛИ, соединенного входами с выходами третьего и четвертого элементов И, причем третий элемен.т И подключен первым входом к второму выходу триггера и к первому входу второго элемента И, а вторым входом - к выходу второго элемента ИЛИ, входы которого соединены с выходами элементов И первой группы, а четвертый элемент И подключен первым входом к первому выходу триггера и к первому входу первого элемента И, а вторым входом - к выходу третьего элемента ИЛИ, входы которого соединены с выходами элементов И второй группы, причете вторые входы элементов И обеих групп подключены к выходам разрядов делителя частоты, соединенного установочным входом с выходом формирователя импульсов и с первым входом пятого элемента И, подключенного выходом к выходной шине умножителя частоты, а вторым входом - к . выходу четвертого элемента ИЛИ, вхоы которого соединены с выходом п-го азряда первого и п-го разряда второго счетчиков, а вторые входы первого и торого элементов И подключены к выходным шин.ам второй опорной частоты.

Источники информации, принятые во внимание при экспертиз

свидетельство СССР 06 F 7/52, 1976.

свидетельство СССР 06 F 7/39, 1971

Авторы

Даты

1981-02-23—Публикация

1979-03-06—Подача