Изобретение относится к вычислительной технике и может быть использовано при построении различных систем обработки дискретной информации, в том числе систем машинного голосования, кодирования и декодирования помехозащищенных кодов, распознавания образов и т.д.

Цель изобретения - расширение диа- ю фиг. 4 состоит из (2p+k) регистров

пазона входных сигналов и упрош;ение устройства.

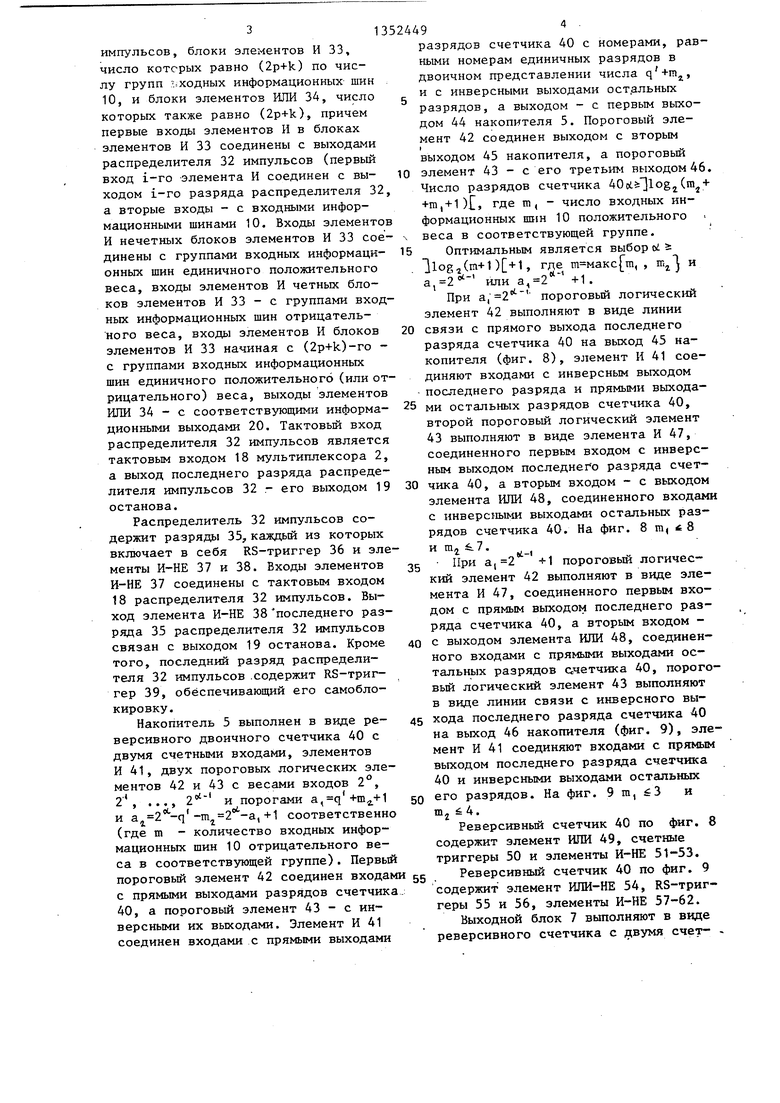

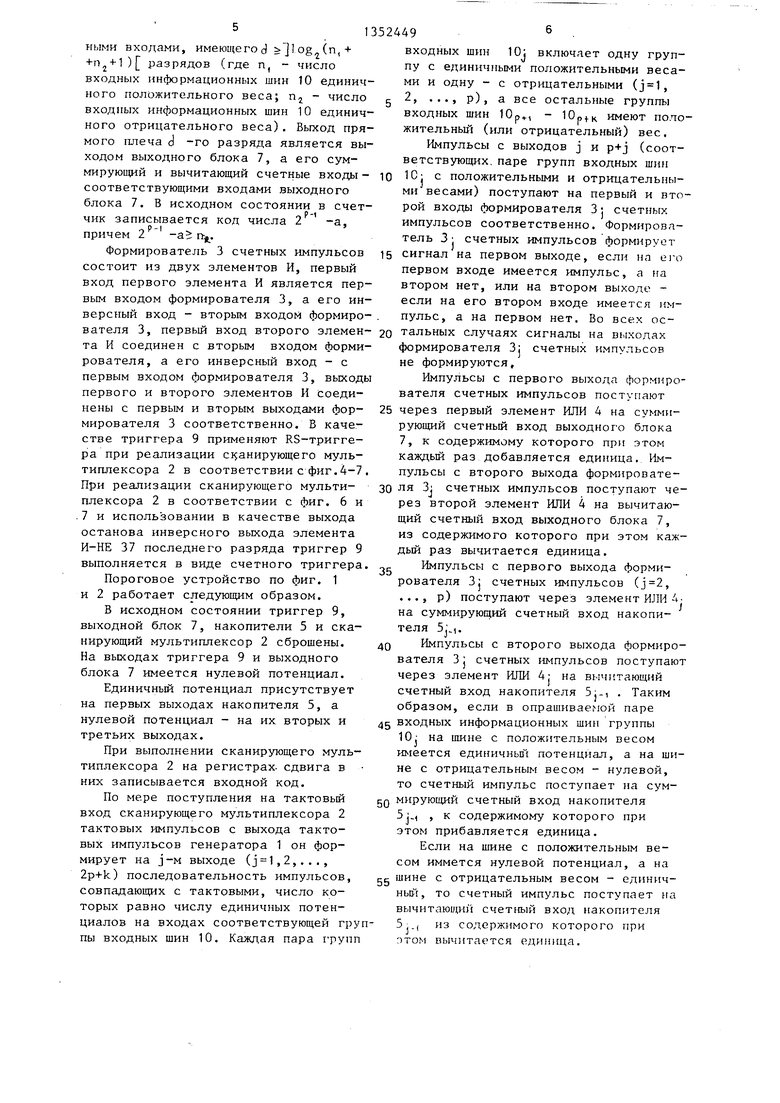

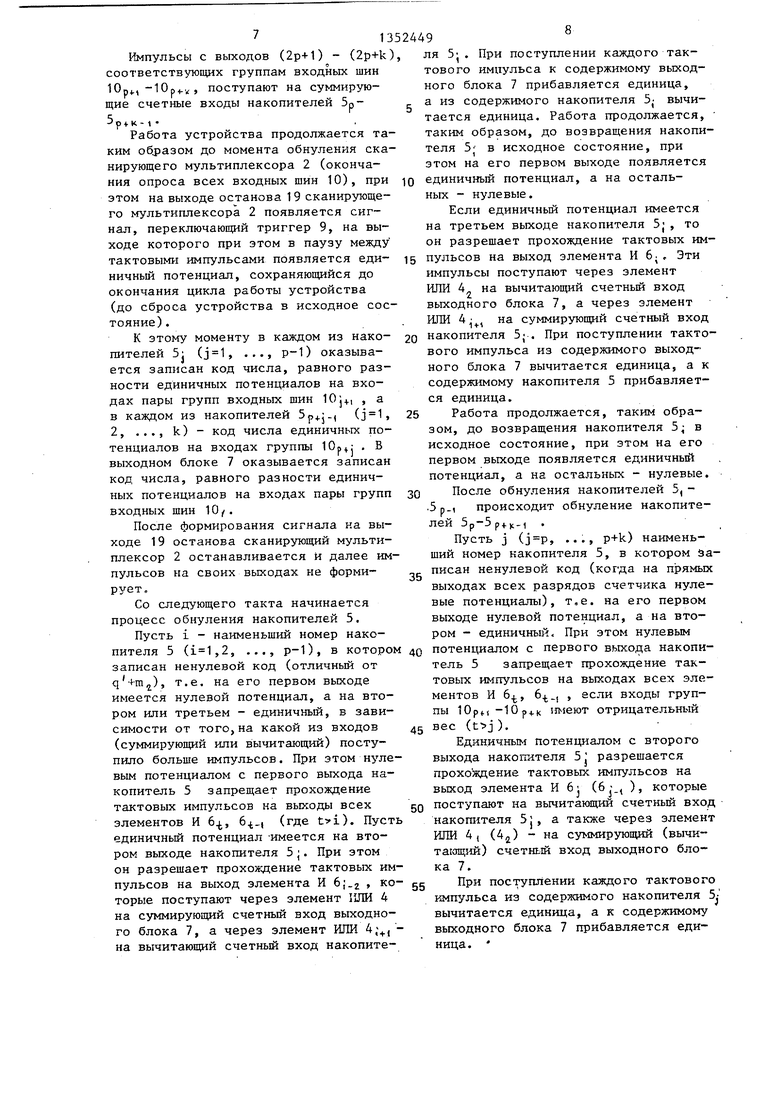

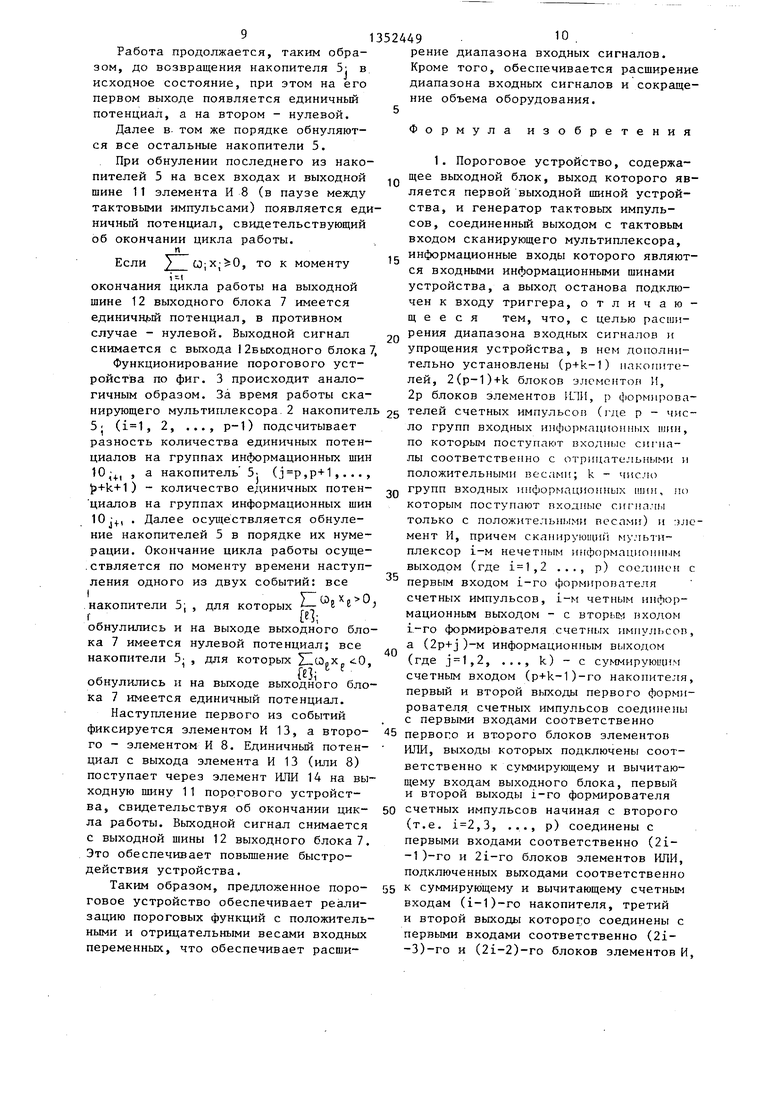

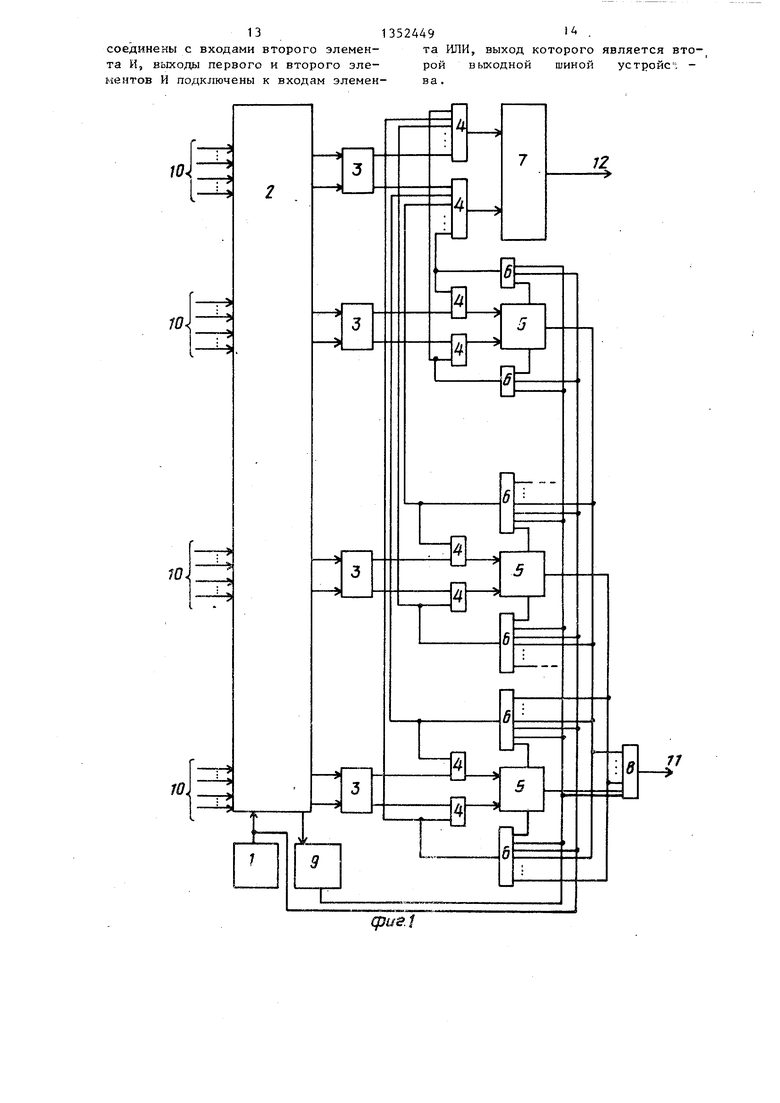

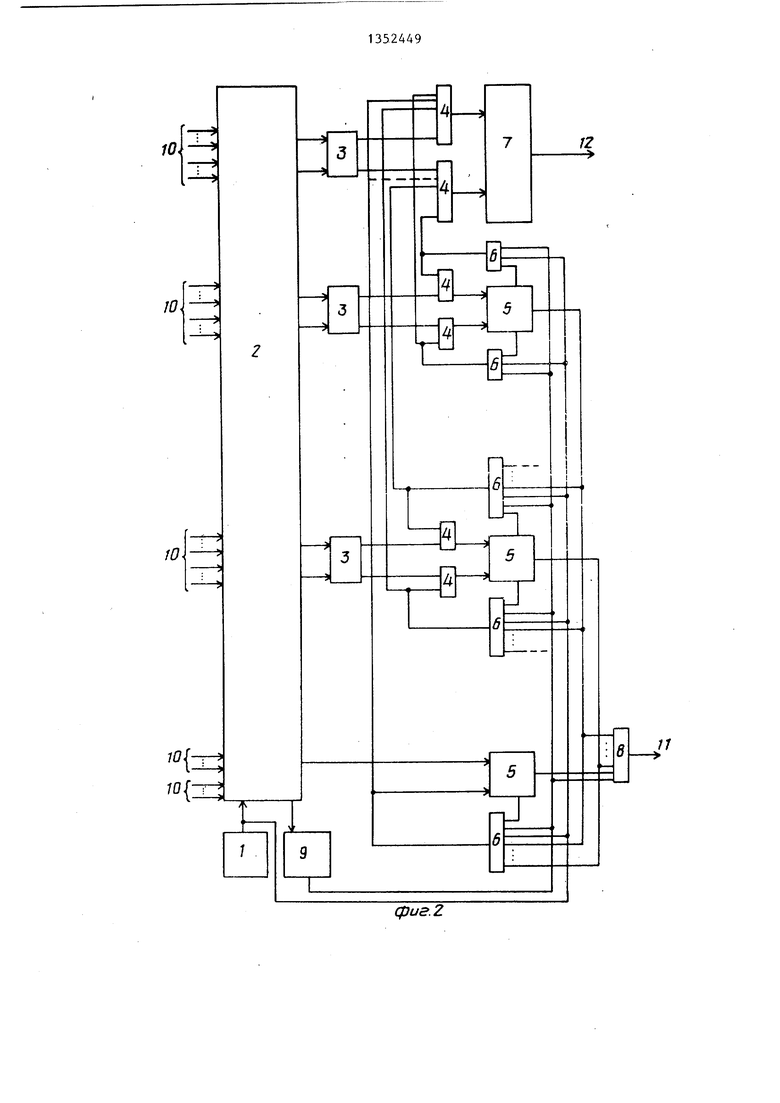

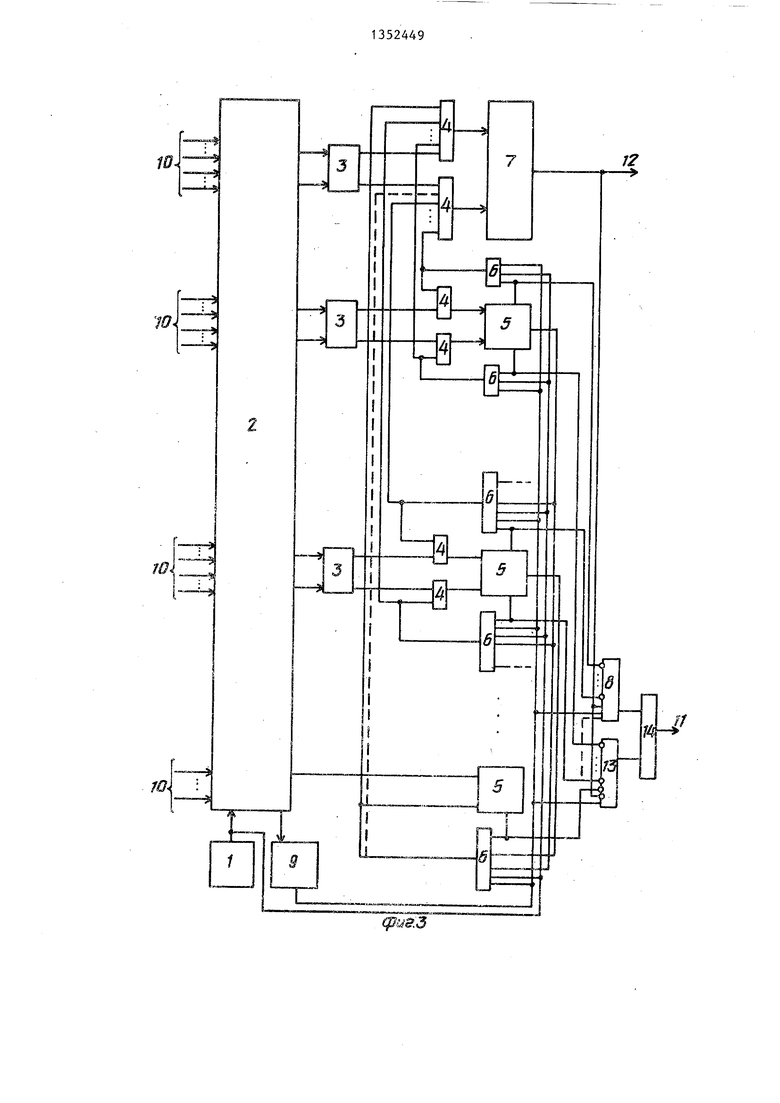

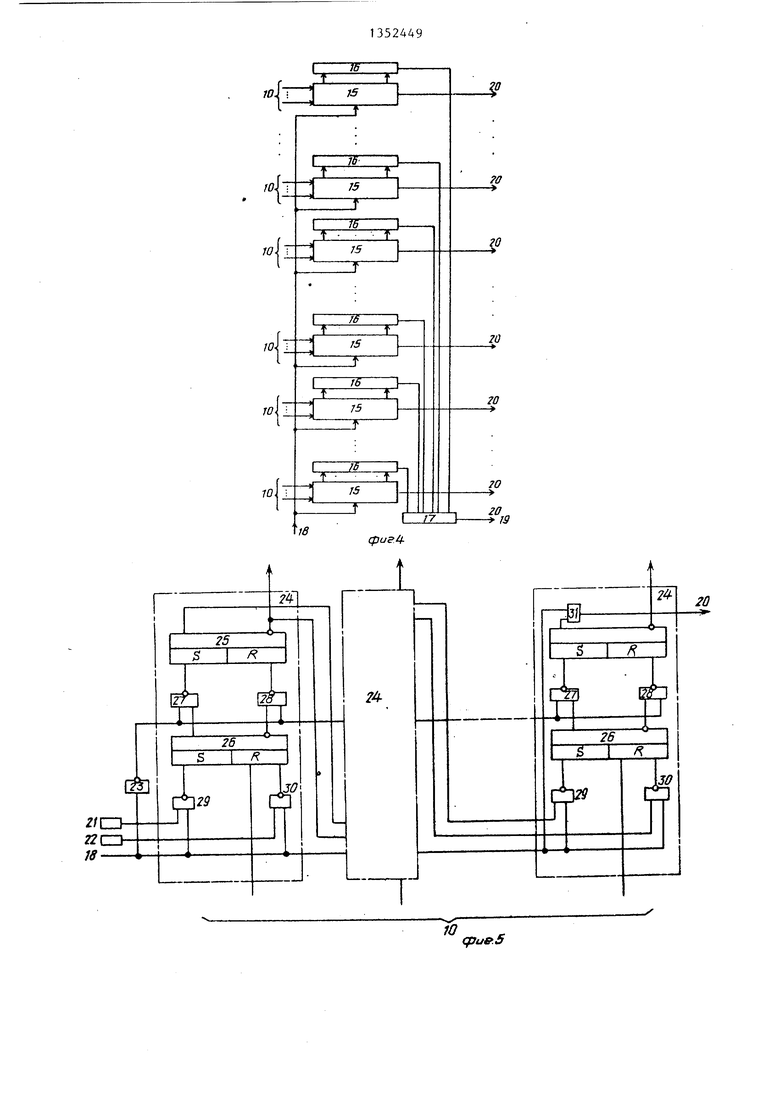

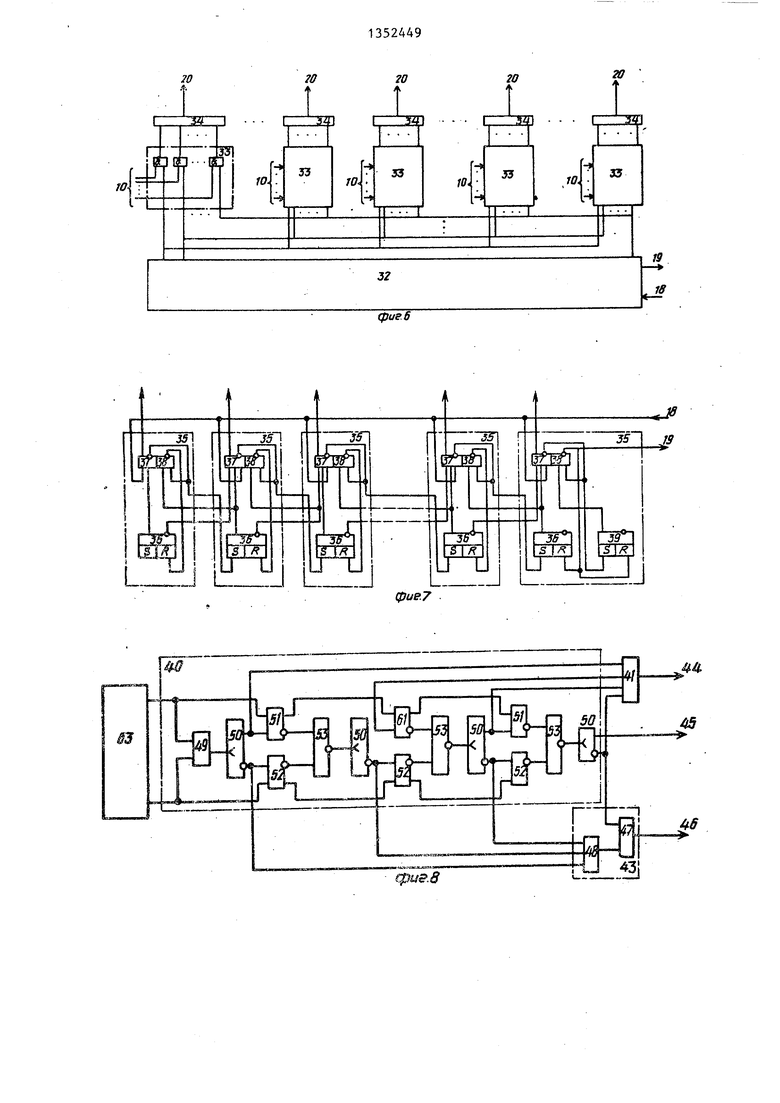

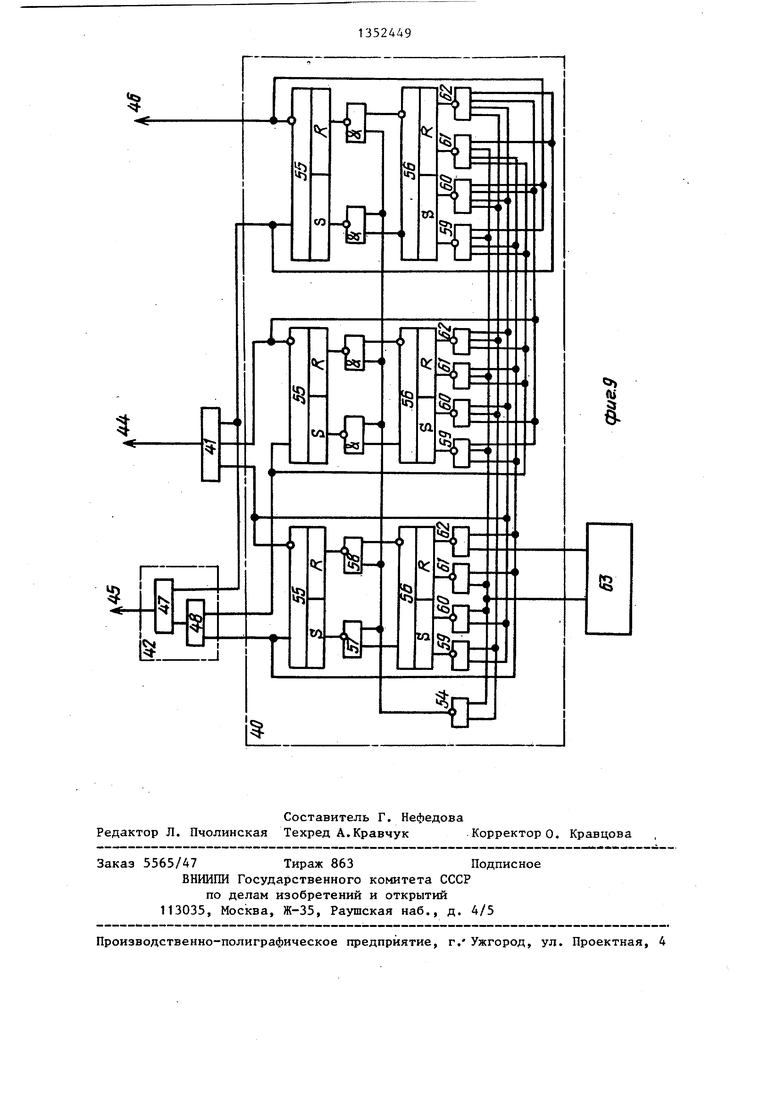

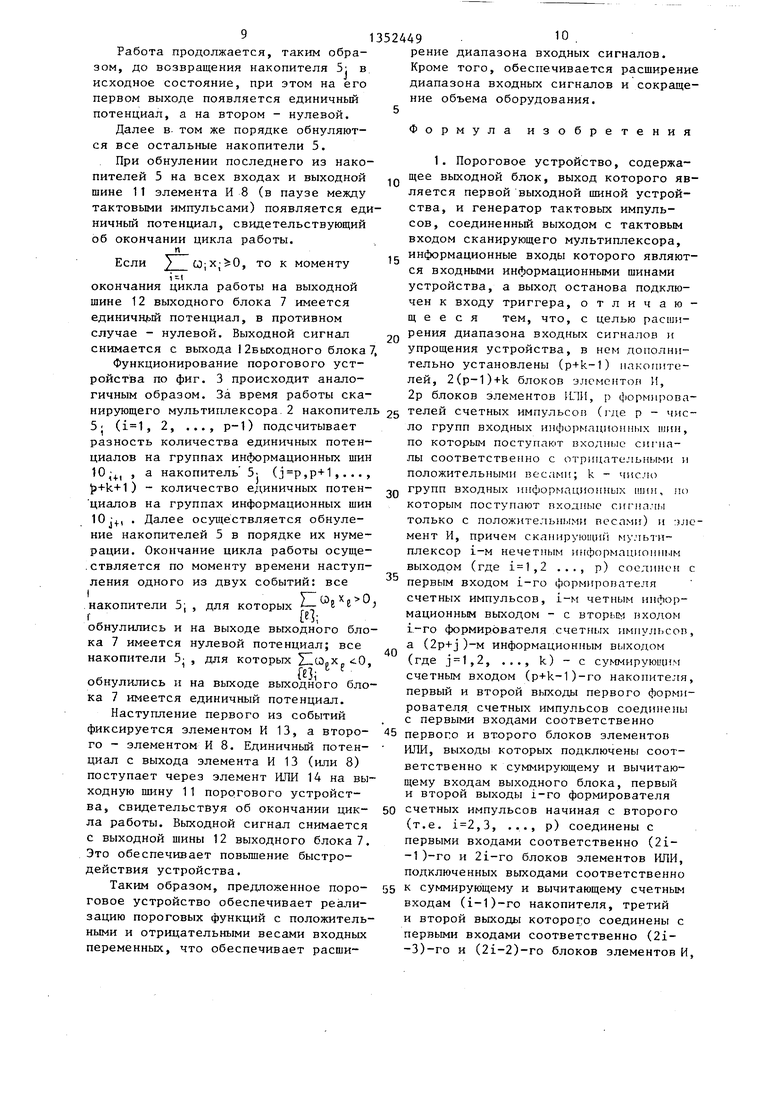

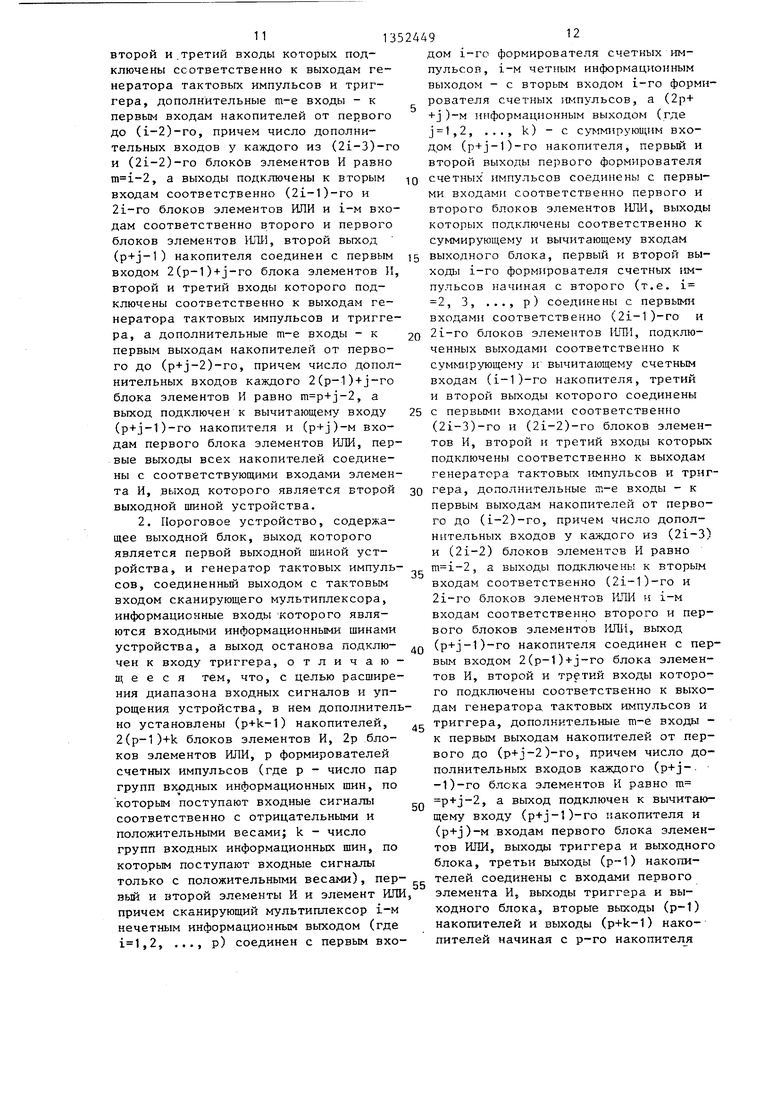

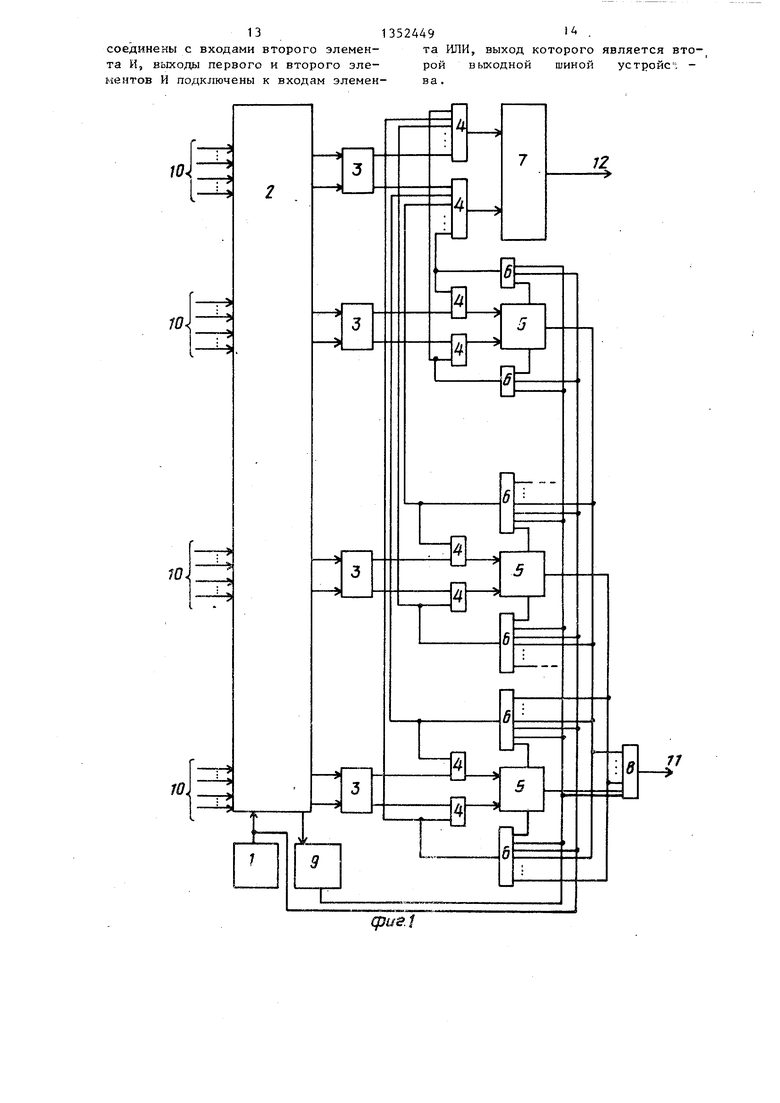

На фиг. 1 и 2 приведены принципиальные схемы устройства по первому варианту; на фиг. 3 - принципиальная схема устройства по второму варианту на фиг, 4 - принципиальная схема сканирующего мультиплексора по первому варианту-; на фиг. 5 - принципиальная схема регистра сдвига; на фиг, 6 - принципиальная схема сканирующего мультиплексора по второму варианту; на фиг, 7 - принципиальная схема распределителя импульсов; на фиг, 8и9- принципиальные схемы накопителей, варианты.

Пороговое устройство по фиг, 1 содержит генератор 1 тактовых импульсов, сканирующий мультиплексор 2, к вкодам которого подключены 2р групп входных информационных шин 10 (где .р - число групп входных информационных шин (р 1), по которым поступают сигналы с единичными положительными и отрицательными весами), р формирователей 3 счетных импульсов, 2р блоков элементов ИЖ 4, р-1 накопителей 5, 2(р-1) блоков элементов И 6 выходной блок 7, элемент И 8, триггер 9 и две выходные шины 11 и 12,

Пороговое устройство по фиг. 2 образуют генератор 1 тактовых импульсов, сканирующий мультиплексор 2, к входам которого подключены (2p+k) групп входных информационных шин 10 (где k - число групп входных информационных шин (), по которым поступают сигналы с единичными только положительными (или только отрицательными) весами), р формирователей 3 счетных импульсов, 2р блоков элементов ИЛИ 4, (p+k-1) накопителей 5, 2(p-1)+k блоков элементов И 6, выходной блок 7, элемент И 8, триггер 9 и две выходные шины 11 и 12.

Пороговое устройство по фиг, 3 содержит генератор 1 тактовых импульсов, сканируклций мультиплексор 2, к входам которого подключены (2p-t-k)

групп входных информационных шин 10, р формирователей 3 счетных имлульсов, 2р блоков элементов ИЛИ 4, (p+k-1) накопителей 5, 2(p-1)+k блоков элементов И 6, выходной блок 7, элемент И 8, триггер 9, две выходные шины 11 и 12, элемент И 13 и элемент ИЛИ 14. Сканирующий мультиплексор 2 по

5

5

0

15 сдвига по числу групп входных информационных шин (, ), (2p,+k) элементов И 16 по числу групп выходных информационных шин 10 и элемент И 17, Тактовые входы регистров 15 сдвига соединены с тактовым входом 18 мультиплексора 2, а инверсные выходы разрядов 15 сдвига - с входами элементов И 16, выходы которых соединены с входами элементов И 17, выход которого является выходом 19 останова мультиплексора 2, выходы переноса регистров 15 сдвига соединены с ин- формационньти выходами 20 мультиплексора 2, а их установочные входы - с входными информационными шинами 10, причем установочные входы нечетных регистров 15 сдвига соединены с группами входных информационных шин единичного положительного веса, установочные входы четных регистров 15 сдвига соединены с группами входных информационных шин единичного отрицательного веса соответственно, а установочные входы регистров 15 сдвига с порядковыми номерами, большими, чем 2р, связаны с группами входных информационных шин 10 единичного положительного (или отрицательного) веса.

Регистр 15 сдвига имеет источник

21постоянного напряжения, который формирует константы О, источник

22постоянного напряжения, который

g формирует константы 1, инвертор 23, разряды 24 регистра сдвига, казкдый из которых содержит RS-триггеры 25 и 26 и элементы И-НЕ 27-30, Входы элементов И-НЕ 29 и 30 разрядов 24 соединены с тактовым входом 18 регистра 15 сдвига, а входы инверсных плеч триггеров 26 - с входными информационными шинами 10, Последние разряды регистра 15 сдвига содержат элемент И 31, выход которого является информационным выходом 20 переноса регистра 15 сдвига.

Сканирующий мультиплексор 2 по фиг, 6 содержит распределитель 32 5

0

0

5

импульсов, блоки элементов И 33, число которых равно (2p+k) по числу групп л.ходных информационных шин 10, и блоки элементов ИЛИ 34, число которых также равно (2p+k), причем первые входы элементов И в блоках элементов И 33 соединены с выходами распределителя 32 импульсов (первый вход i-ro элемента И соединен с выходом i-ro разряда распределителя 32, а вторые входы - с входными информационными шинами 10. Входы элементов И нечетных блоков элементов И 33 соединены с группами входных информационных шин единичного положительного веса, входы элементов И четных блоков элементов И 33 - с группами входных информационных шин отрицательного веса, входы элементов И блоков элементов И 33 начиная с (2p+k)-ro - с группами входных информационных шин единичного положительного (или отрицательного) веса, выходы элементов

разрядов счетчика 40 с номерами, ра ными номерам единичных разрядов в

двоичном представлении числа q +ш, и с инверсными выходами остальных разрядов, а выходом - с первым выхо дом 44 накопителя 5. Пороговый элемент 42 соединен выходом с вторым

выходом 45 накопителя, а пороговый 10 элемент 43 - с его третьим выходом Число разрядов счетчика 40oi.5: 3logj(m +m,+1), где m, - число входных информационных шин 10 положительного веса в соответствующей группе. 15 Оптимальным является выборЫ ь log,(in+1 )+1, где т максГт, , и - - 2 +1.

а,2

или а.

20

При а, 2 пороговый логический элемент 42 выполняют в виде линии связи с прямого выхода последнего разряда счетчика 40 на выход 45 накопителя (фиг, 8), элемент И 41 сое диняют входами с инверсным выходом последнего разряда и прямыми выхода

ИЛИ 34 - с соответствующими информа- 25 ми остальных разрядов счетчика 40,

ционными выходами 20. Тактовый вход распределителя 32 импульсов является тактовым входом 18 мультиплексора 2, а выход последнего разряда распределителя импульсов 32 - его выходом 19 останова.

Распределитель 32 импульсов содержит разряды 35, каждый из которых включает в себя RS-триггер 36 и элементы И-НЕ 37 и 38. Входы элементов И-НЕ 37 соединены с тактовым входом 18 распределителя 32 импульсов. Выход элемента И-НЕ 38 последнего разряда 35 распределителя 32 импульсов связан с выходом 19 останова. Кроме того, последний разряд распределителя 32 импульсов .содержит RS-триггер 39, обеспечивающий его самоблокировку.

Накопитель 5 выполнен в виде реверсивного двоичного счетчика 40 с двумя счетными входами, элементов И 41, двух пороговых логических элементов 42 и 43 с весами входов 2°,

,ot-i

2 -4 -m,2 -a,+1

с весами входов и порогами a,q +m2 +1

соответственно

2. и а,

(где m - количество входных информационных шин 10 отрицательного веса в соответствующей группе). Первьй пороговый элемент 42 соединен входам с прямыми выходами разрядов счетчика 40, а noporoBbrft элемент 43 - с инверсными их выходами. Элемент И 41 соединен входами с прямыми выходами

дов счетчика 40 с номерами, равномерам единичных разрядов в

двоичном представлении числа q +ш, и с инверсными выходами остальных разрядов, а выходом - с первым выходом 44 накопителя 5. Пороговый элемент 42 соединен выходом с вторым

выходом 45 накопителя, а пороговый элемент 43 - с его третьим выходом 46. Число разрядов счетчика 40oi.5: 3logj(m + +m,+1), где m, - число входных информационных шин 10 положительного веса в соответствующей группе. Оптимальным является выборЫ ь log,(in+1 )+1, где т максГт, , и - - 2 +1.

а,2

или а.

При а, 2 пороговый логический элемент 42 выполняют в виде линии связи с прямого выхода последнего разряда счетчика 40 на выход 45 накопителя (фиг, 8), элемент И 41 соединяют входами с инверсным выходом последнего разряда и прямыми выхода

второй пороговый логический элемент 43 выполняют в виде элемента И 47, соединенного первым входом с инверсным выходом последнего разряда счетчика 40, а вторым входом - с выходом элемента ИЛИ 48, соединенного входами с инверсными выходами остальных разрядов счетчика 40. На фиг. 8 га 8

и т 7.

«oi-При а,2 +1 пороговый логический элемент 42 выполняют в виде элемента И 47, соединенного первым входом с прямым выходом последнего разряда счетчика 40, а вторым входом с выходом элемента ИЛИ 48, соединенного входами с прямыми выходами ос- тальнь1х разрядов счетчика 40, пороговый логический элемент 43 выполняют в виде линии связи с инверсного выхода последнего разряда счетчика 40 на выход 46 накопителя (фиг. 9), элемент И 41 соединяют входами с прямым выходом последнего разряда счетчика 40 и инверсными выходами остальных

его разрядов. На фиг. 9 т, 3 и fflj б4.

Реверсивный счетчик 40 по фиг. 8 содержит элемент ИЛИ 49, счетные триггеры 50 и элементы И-НЕ 51-53.

Реверсивный счетчик 40 по фиг. 9 содержит элемент ИЛИ-НЕ 54, RS-триг- геры 55 и 56, элементы И-НЕ 57-62.

Выходной блок 7 выполняют в виде реверсивного счетчика с счет- ными входами, имеющего J S-l og (п,+ ) разрядов (где п, - число входных информационных шин 10 единичного положительного веса; п - число входных информационных шин 10 единичного отрицательного веса), Выход прямого плеча с) -го разряда является выходом выходного блока 7, а его суммирующий и вычитающий счетные входы - соответствующими входами выходного

блока 7. В исходном состоянии в счет 0-1 чик

исходном состоянии в записывается код числа 2 -а причем 2 -а2; п-,.

Импульсы с выходов j и P+J (соответствующих, паре групп входных шин 10; с положительными и отрицательными весами) поступают на первый и второй входы формирователя 3; счетных импульсов соответственно. Формирователь 3j счетных импульсов формирует

сигнал на первом выходе, если на ej-o первом входе имеется импульс, а iia втором нет, или на втором выходе - если на его втором входе имеется импульс, а на первом нет. Во всех осФормирователь 3 счетных импульсов 15 состоит из двух элементов И, первый вход первого элемента И является первым входом формирователя 3, а его инверсный вход - вторым входом формиро- . вателя 3, первый вход второго элемен- 20 тальных случаях сигналы на выходах та И соединен с вторым входом форми- формирователя 3; счетных импульсов рователя, а его инверсный вход - с не формируются,

первым входом формирователя 3, выходы Импульсы с первого выхода формиро- первого и второго элементов И соеди- вателя счетных импульсов поступают нены с первым и вторым выходами фор- 25 через первый элемент ИЛИ 4 на сумми- мирователя 3 соответственно. В каче- рующий счетный вход выходного блока

7, к содержимому которого при этом каждый раз добавляется единица. Импульсы с второго выхода формироватестве триггера 9 применяют RS-тригге- ра при реализации С1 анирующего мультиплексора 2 в соответствии с фиг.4-7 При реализации сканирующего мультиплексора 2 в соответствии с фиг. 6 и .7 и использовании в качестве выхода останова инверсного выхода элемента И-НЕ 37 последнего разряда триггер 9 выполняется в виде счетного триггера

Пороговое устройство по фиг. 1 и 2 работает следующим образом.

В исходном состоянии триггер 9, выходной блок 7, накопители 5 и сканирующий мультиплексор 2 сброшены. На выходах триггера 9 и выходного блока 7 имеется нулевой потенциал.

Единичный потенциал присутствует на первых выходах накопителя 5, а нулевой потенциал - на их вторых и третьих выходах.

При выполнении сканирующего мультиплексора 2 на регистрах- сдвига в них записывается входной код.

По мере поступления на тактовый вход сканирующего мультиплексора 2 тактовых импульсов с выхода тактовых импульсов генератора 1 он формирует на J-M выходе (,2,..., 2p+k) последовательность импульсов, совпадающих с тактовыми, число которых равно числу единичных потенциалов на входах соответствующей группы входных шин 10. Каждая пара г рупп

30 ля 3; счетных импульсов поступают через второй элемент ИЛИ 4 на вычитающий счетный вход выходного блока 7, из содержимого которого при этом каждый раз вычитается единица.

Импульсы с первого выхода форми35

рователя 3; счетных импульсов (.

) ..., р) поступают через элемент ИЛИ Дна суммирующий счетный вход накопителя 5л,.

40 Импульсы с второго выхода формирователя 3 j счетных импульсов поступают через элемент ИЛИ 4; на вычитающий счетный вход накопителя 5;-, . Таким образом, если в опрашиваемой паре

45 входных информационных шин группы 10; на шине с положительным весом имеется единичньп потенциал, а на шине с отрицательным весом - нулевой, то счетный импульс поступает на сумgQ мирующий счетный вход накопителя 5;., , к содержимому которого при этом прибавляется единица.

Если на шине с положительным весом иммется нулевой потенциал, а на шине с отрицательным весом - единичный, то счетный импульс поступает на вычитающий счетный вход накопителя 5, , из содержимого которого при этом вычитается единица.

55

входных шин 10; включает одну группу с единичными положительными весами и одну - 2, ..., р),

входных шин Юо, - 10о4.к имеют поло0

с отрицательными (, а все остальные группы

р-и 10р,.к

жительный (или отрицательный) вес.

Импульсы с выходов j и P+J (соответствующих, паре групп входных шин 10; с положительными и отрицательными весами) поступают на первый и второй входы формирователя 3; счетных импульсов соответственно. Формирователь 3j счетных импульсов формирует

сигнал на первом выходе, если на ej-o первом входе имеется импульс, а iia втором нет, или на втором выходе - если на его втором входе имеется импульс, а на первом нет. Во всех ос50 тальных случаях сигналы на выходах формирователя 3; счетных импульсов не формируются,

30 ля 3; счетных импульсов поступают через второй элемент ИЛИ 4 на вычитающий счетный вход выходного блока 7, из содержимого которого при этом каждый раз вычитается единица.

Импульсы с первого выхода форми35

рователя 3; счетных импульсов (.

) ..., р) поступают через элемент ИЛИ Дна суммирующий счетный вход накопителя 5л,.

40 Импульсы с второго выхода формирователя 3 j счетных импульсов поступают через элемент ИЛИ 4; на вычитающий счетный вход накопителя 5;-, . Таким образом, если в опрашиваемой паре

45 входных информационных шин группы 10; на шине с положительным весом имеется единичньп потенциал, а на шине с отрицательным весом - нулевой, то счетный импульс поступает на сумgQ мирующий счетный вход накопителя 5;., , к содержимому которого при этом прибавляется единица.

Если на шине с положительным весом иммется нулевой потенциал, а на шине с отрицательным весом - единичный, то счетный импульс поступает на вычитающий счетный вход накопителя 5, , из содержимого которого при этом вычитается единица.

55

Импульсы с выходов (2р+1) - (2p+k) соответствующих группам входных шин Юр., -Юр.., поступают на суммирующие счетные входы накопителей 5р

к -1

Работа устройства продолжается таким образом до момента обнуления сканирующего мультиплексора 2 (окончания опроса всех входных шин 10), при этом на выходе останова 19 сканирующего мультиплексора 2 появляется сигнал, переключающий триггер 9, на выходе которого при этом в паузу между тактовыми импульсами появляется единичный потенциал, сохраняющийся до окончания цикла работы устройства (до сброса устройства в исходное состояние) .

К этому моменту в каждом из накопителей 5: (, ..., р-1) оказывается записан код числа, равного разности единичных потенциалов на вхо10;

)

дах пары групп входных шин в каждом из накопителей .- (j 1 2, ..., k) - код числа единичных потенциалов на входах группы 10в+; . В выходном блоке 7 оказывается записан код числа, равного разности единичных потенциалов на входах пары групп входных шин 10.

После формирования сигнала на выходе 19 останова сканирующий мультиплексор 2 останавливается и далее импульсов на своих выходах не формирует,

Со следующего такта начинается процесс обнуления накопителей 5.

Пусть i - наименьший номер накопителя 5 (,2,

записан ненулевой код (отличный от q +m), т.е. на его первом выходе имеется нулевой потенциал, а на втором или третьем - единичный, в зависимости от того,на какой из входов (суммирующий или вычитающий) поступило больше импульсов. При этом нулевым потенциалом с первого выхода накопитель 5 запрещает прохождение тактовых импульсов на выходы всех элементов И 6, 6, (где ). Пусть единичный потенциал -имеется на втором выходе накопителя 5 j. При этом он разрешает прохождение тактовых импульсов на выход элемента И б;. которые поступают через элемент ИЛИ 4 на суммирующий счетный вход выходного блока 7, а через элемент ИЛИ 4,, - на вычитающий счетный вход накопитер-1), в котором 40 потенциалом с первого выхода накопитель 5 запрещает прохождение тактовых импульсов на выходах всех элементов И 6, 6, , если входы группы 10рк-10р4.к имеют отрицательный

45 вес ( ).

Единичным Потенциалом с второго выхода накопителя 5 разрешается прохо ждение тактовых импульсов на выход элемента И 6 (б:, ), которые

50 поступают на вычитающий счетный вход нaкoшiтeля 5:, а также через элемент ИЛИ 4, (4,) - на суммирующий (вычи- та:ощ51й) счетный вход выходного блока 7.

55 При поступлении каждого тактового кмпульса из содержимого накопителя 5.- вычитается единица, а к содержимому выходного блока 7 прибавляется единица.

ля 5;. При поступлении каждого тактового имнульса к содержимому выходного блока 7 прибавляется единица, а из содержимого накопителя 5 вычитается единица. Работа продолжается, таким образом, до возвращения накопителя 5; в исходное состояние, при этом на его первом выходе появляется

единичный потенциал, а на остальных - нулевые.

Если единичный потенциал имеется на третьем выходе накопителя 5j, то он разрешает прохождение тактовых импульсов на выход элемента И 6, Эти импульсы поступают через элемент ИЛИ 4 на вычитающий счетный вход выходного блока 7, а через элемент

ИЛИ 4,

и- накопителя

на суммирующий счетный вход

5;. При поступлении такто5

0

5

вого импульса из содержимого выходного блока 7 вычитается единица, а к содержимому накопителя 5 прибавляется единица.

Работа продолжается, таким образом, до возвращения накопителя 5; в исходное состояние, при этом на его первом выходе появляется единичный потенциал, а на остальных - нулевые.

После обнуления накопителей 5, - .5 р., происходит обнуление накопителей 5р-5 р.., .

Пусть j (, ..., p+k) наименьший номер накопителя 5, в котором Записан ненулевой код (когда на прямых выходах всех разрядов счетчика нулевые потенциалы), т.е. на его первом выходе нулевой потенциал, а на втором - единичньй. При этом нулевым

тель 5 запрещает прохождение тактовых импульсов на выходах всех элементов И 6, 6, , если входы группы 10рк-10р4.к имеют отрицательный

вес ( ).

Единичным Потенциалом с второго выхода накопителя 5 разрешается прохо ждение тактовых импульсов на выход элемента И 6 (б:, ), которые

поступают на вычитающий счетный вход нaкoшiтeля 5:, а также через элемент ИЛИ 4, (4,) - на суммирующий (вычи- та:ощ51й) счетный вход выходного блока 7.

При поступлении каждого тактового кмпульса из содержимого накопителя 5.- вычитается единица, а к содержимому выходного блока 7 прибавляется единица.

Работа продолжается, таким образом, до возвращения накопителя 5: в исходное состояние, при этом на его первом выходе появляется единичный потенциал, а на втором - нулевой.

Далее в. том же порядке обнуляются все остальные накопители 5.

При обнулении последнего из накопителей 5 на всех входах и выходной шине 11 элемента И 8 (в паузе между тактовыми импульсами) появляется единичный потенциал, свидетельствующий

об окончании цикла работы. п

Если У , ТО К моменту

i-l

окончания цикла работы на выходной шине 12 выходного блока 7 имеется единичньй потенциал, в противном случае - нулевой. Выходной сигнал снимается с выхода 1 2выходного блока

Функционирование порогового устройства по фиг. 3 происходит аналогичным образом. За время работы сканирующего мультиплексора. 2 накопитель 25 телей счетных импульсов (где р - чисnwjXj o

5 (, 2, ..., р-1) подсчитывает разность количества единичных потенциалов на группах информационных шин 10,-, , а накопитель 5j (,p+1 ,. .. , ts+k+1) - количество единичных потен- циалов на группах информационных шин 10;., . Далее осуществляется обнуление накопителей 5 в порядке их нумерации. Окончание цикла работы осуще- .ствляется по моменту времени наступления одного из двух событий: все I накопители 5; , для которых

обнулились и на выходе выходного блока 7 имеется нулевой потенциал; все накопители 5; , для которых 511(0„х- 0,

fe,

обнулились и на выходе выходного блока 7 имеется единичный потенциал.

Наступление первого из событий фиксируется элементом И 13, а второго - элементом И 8. Единичный потенциал с выхода элемента И 13 (или 8) поступает через элемент ИЛИ 14 на выходную шину 11 порогового устройства, свидетельствуя об окончании цикла работы. Выходной сигнал снимается с выходной шины 12 выходного блока 7. Это обеспечивает повьш1ение быстродействия устройства.

Таким образом, предложенное пороговое устройство обеспечивает реализацию пороговых функций с положительными и отрицательными весами входных переменных, что обеспечивает расши35

40

ло групп входных инфо 1мациоиных шин, по которым поступают входные сигналы соответственно с отрицательными и положительными весами; k - число

30 групп входных информационных шин, пс) которым поступают входные .чы только с положительными весами) и :зле- мент И, причем сканирующш мультиплексор i-M нечетным информационн1.1м выходом (где ,2 ..., р) соединен с первым входом i-ro формирователя счетных импульсов, i-м четным информационным выходом - с вторым входом i-ro формирователя счетных имг1ул1)Сов, а (2p+j)-м информационным выходом (где j 1,2, ..., k) - с суммируюи(им счетным входом (p+k-1)-ro накопителя, первый и второй выходы первого формирователя, счетных импульсов соединены с первыми входами соответственно

5 первого и второго блоков элементов ИЛИ, выходы которых подключены соответственно к суммирующему и вычитающему входам выходного блока, первый и второй выходы i-ro формирователя

50 счетных импульсов начиная с второго (т.е. ,3, ..., р) соединены с первыми входами соответственно (2i- -1 )-го и 2i-ro блоков элементов ИЛИ, подключенных выходами соответственно

55 к суммирующему и вычитающему счетным входам (i-l)-ro накопителя, третий и второй выходы которого соединены с первыми входами соответственно (2i- -3)-го и (2i-2)-ro блоков элементов И,

рение диапазона входных сигналов. Кроме того, обеспечивается расширение диапазона входных сигналов и сокращение объема оборудования.

Формула изобретения

1. Пороговое устройство, содержащее выходной блок, выход которого является первой выходной шиной устройства, и генератор тактовых импульсов, соединенный выходом с тактовым входом сканирующего мультиплексора, информационные входы которого являются входными информационными шинами устройства, а выход останова подключен к входу триггера, отличающееся тем, что, с целью расширения диапазона входных сигналов и упрощения устройства, в нем дополнительно установлены (p+k-l) ипкопито- лей, 2(p-1)+k блоков элементов И, 2р блоков элементов 1ПИ, р формирова

ло групп входных инфо 1мациоиных шин, по которым поступают входные сигналы соответственно с отрицательными и положительными весами; k - число

групп входных информационных шин, пс) которым поступают входные .чы только с положительными весами) и :зле- мент И, причем сканирующш мультиплексор i-M нечетным информационн1.1м выходом (где ,2 ..., р) соединен с первым входом i-ro формирователя счетных импульсов, i-м четным информационным выходом - с вторым входом i-ro формирователя счетных имг1ул1)Сов, а (2p+j)-м информационным выходом (где j 1,2, ..., k) - с суммируюи(им счетным входом (p+k-1)-ro накопителя, первый и второй выходы первого формирователя, счетных импульсов соединены с первыми входами соответственно

первого и второго блоков элементов ИЛИ, выходы которых подключены соответственно к суммирующему и вычитающему входам выходного блока, первый и второй выходы i-ro формирователя

счетных импульсов начиная с второго (т.е. ,3, ..., р) соединены с первыми входами соответственно (2i- -1 )-го и 2i-ro блоков элементов ИЛИ, подключенных выходами соответственно

к суммирующему и вычитающему счетным входам (i-l)-ro накопителя, третий и второй выходы которого соединены с первыми входами соответственно (2i- -3)-го и (2i-2)-ro блоков элементов И,

второй и.третий входы которых подключены ссответственно к выходам генератора тактовых импульсов и триггера, дополнительные т-е входы - к первым входам накопителей от первого до (1-2)-го, причем число дополнительных входов у каждого из (2i-3)-ro и (2i-2)-ro блоков элементов И равно , а выходы подключены к вторым входам соответственно (21-1)-го и 2i-ro блоков элементов ИЛИ и i-м входам соответственно второго и первого блоков элементов ИЛИ, второй выход (p+j-1) накопителя соединен с первым входом 2(р-1 )-t-j-ro блока элементов И, второй и третий входы которого подключены соответственно к выходам генератора тактовых импульсов и триггера, а дополнительные т-е входы - к первым выходам накопителей от первого до (p+j-2)-ro, причем число дополнительных входов каждого 2(p-1)+j-ro блока элементов И равно m p+j-2, а выход подключен к вычитающему входу (p+j-1)-го накопителя и (p+j)-M входам первого блока элементов ИЛИ, первые выходы всех накопителей соединены с соответствующими входами элемента И, выход которого является второй выходной шиной устройства.

2. Пороговое устройство, содержащее выходной блок, выход которого является первой выходной шиной устройства, и генератор тактовых импульсов, соединенный выходом с тактовым входом сканирующего мультиплексора, информационные входы которого являются входными информационными шинами устройства, а выход останова подключен к входу триггера, отличающееся тем, что, с целью расширения диапазона входных сигналов и упрощения устройства, в нем дополнительно установлены (p+k-1) накопителей, 2(p-1)+k блоков элементов И, 2р блоков элементов ИЛИ, р формирователей счетных импульсов (где р - число пар групп вхрдных информационных шин, по которым поступают входные сигналы соответственно с отрицательными и положительными весами; k - число групп входных информационных шин, по которым поступают входные сигналы

с триггера, дополнительные т-е входы к первым выходам накопителей от пе вого до (p+j-2)-ro5 причем число д полнительных входов каждого (P+J-1)-го блока элементов И равно т p+j-2, а выход подключен к вычита щему входу (p+j-1)-го накопителя и ( ) входам первого блока элеме тов ИЛИ, выходы триггера и выходно блока, третьи выходы (р-1) накопителей соединены с входами первого

только с положительными весами), первьй и второй элементы И и элемент ИЛИ, элемента И, выходы триггера и выпричем сканирующий мультиплексор 1-м

нечетным информационным выходом (где

,2, ..., р) соединен с первым вхоходного блока, вторые выходы (р-1 накопителей и выходы (p+k-1) нако пителей начиная с р-го накопителя

0

5

дом i-ro формирователя счетных импульсов, i-M четным информационным выходом - с вторым входом i-ro формирователя счетных импульсов, а (2р+ +J)-м информационным выходом (где j 1,2, ..., k) - с суьгмирующим входом (p+j-1)-го накопителя, первый и второй выходы первого формирователя счетных импульсов соединены с первыми входами соответственно первого и второго блоков элементов ИЛИ, выходы которых подключены соответственно к cy миpyющeмy и вычитающему входам

5 выходного блока, первый и второй выходы i-ro формирователя счетных импульсов начиная с второго (т.е. i 2, 3, ..., р) соединены с первыми входами соответственно (2i-1)-ro и 2i-ro блоков элементов ИЛИ, подключенных выходами соответственно к сумм1рующему и вычитающему счетным входам (i-1)-ro накопителя, третий и BTopofi выходы которого соединены с первыми входами соответственно (2i-3)-ro и (2i-2)-ro блоков элементов И, второй и третий входы которых подключены соответственно к выходам генератора тактовых импульсов и триггера, дополнительные гг.-е входы - к первым выходам накопителей от первого до (i-2)-ro, причем число дополнительных входов у каждого из (2i-3) и (2i-2) блоков элементов И равно , а выходы подключень к вторым входам соответственно (2i-1)-ro и 2i-ro блоков элементов ИЛИ и i-м входам соответственно второго и первого блоков элементов ИЛИ, выход (p+j-1)-го накопителя соединен с первым входом 2(p-1)+j-ro блока элементов И, второй и третий входы которого подключены соответственно к выходам генератора, тактовых импульсов и

с триггера, дополнительные т-е входы - к первым выходам накопителей от первого до (p+j-2)-ro5 причем число дополнительных входов каждого (P+J- -1)-го блока элементов И равно т p+j-2, а выход подключен к вычитающему входу (p+j-1)-го накопителя и ( ) входам первого блока элементов ИЛИ, выходы триггера и выходного блока, третьи выходы (р-1) накопителей соединены с входами первого

0

5

0

0

элемента И, выходы триггера и выходного блока, вторые выходы (р-1) накопителей и выходы (p+k-1) накопителей начиная с р-го накопителя

131352449 .

соединены с входами второго элемен- та ИЛИ, выход которого является вто- та И, выходы первого и второго эле- рой выходной шиной устройс ; - ментов И подключены к входам элемен- ва.

Cpus.1

/0.

rz

| название | год | авторы | номер документа |

|---|---|---|---|

| Пороговый элемент | 1985 |

|

SU1297220A1 |

| Пороговый элемент | 1985 |

|

SU1297219A1 |

| ПОРОГОВЫЙ ЭЛЕМЕНТ | 1987 |

|

RU2034401C1 |

| Пороговый элемент | 1987 |

|

SU1584098A1 |

| Пороговое устройство | 1986 |

|

SU1368979A1 |

| Пороговый элемент | 1983 |

|

SU1126924A1 |

| Пороговый элемент | 1986 |

|

SU1387185A2 |

| Пороговый элемент | 1984 |

|

SU1277370A1 |

| Пороговый элемент | 1987 |

|

SU1647871A1 |

| Пороговый элемент | 1984 |

|

SU1261100A1 |

Изобретение относится к области вычислительной техники и может быть использовано при построении различных систем обработки дискретной информации, в том числе систем машинного голосования, кодирования и декодирования помехозащищенных кодов, распознавания образов и т.д. Целью изобретения является расширение диапазона входных сигналов устройства. Поставленная цель достигается за счет того, что входные щины устройства разбиты на p+k группы, где р - число пар групп входных шин, по которым подаются сигнал111 с положительными и отрицательными весами; k - число групп входных шин, по которым подаются сигналы только с положительными (или только отрицательными) весами. В каждой группе присутствуют сигналы только с одинаковыми весами и число сигналов в группах одинаково. Входные сигналы по входным шинам подаются на информационные входы сканирующего мультиплексора, который по сигналам генератора тактовых импульсов подключает к входным шинам формирователи счетных импульсов. Выходные сигналы формирователей через соответствующие им блоки элементов ШШ поступают на вычитающие и суммирующие входы накопителей, которые своими вторыми и третьими выходами самоблокируются по указанным входам через блоки элементов И. Выходные сигналы всех блоков элементов И поступают на соответствующие входы первого и второго блоков элементов ИЛИ, выходные сигналы которых подаются на суммирующий и вычитающий входы выходного блока, на выходе которого формируется результирующий сигнал. Первые выходы накопителей соединены с выходами элемента И, на выходе которого формируется признак окончания работы устройства. Второй вариант устройства отличается от первого принципом формирования признака окончания работы устройства. В нем выходные сигналы выходного блока генератора тактовых импульсов и вторые выходные сигналы накопителей подаются на входы первого элемента И, а выходные сигналы выходного блока генератора и третьи выходные сигналы накопителей - на входы второго элемента И, а с их выходов - на входы элемента ИЛИ, выход которого является вторым выходом устройства. 2 с.п.ф-лы, 9 ил.

ю

П 6

fOт

10

(и

70 {п:

6

11

фиг. 2

//

Г

Ж

25

S I /

f5

S I К

29

JO

z/o CZ}- 18

I

/

5 I /

5

та

л I

й

Cpu.S

20

2020

I I

20

20

фие.7

фаз: 8

| Патент США К 4027175, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Шеститрубный элемент пароперегревателя в жаровых трубках | 1918 |

|

SU1977A1 |

| Пороговый логический элемент | 1980 |

|

SU980064A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Пороговый элемент | 1982 |

|

SU1091344A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1987-11-15—Публикация

1984-06-14—Подача