ИзвесТ)1Ы устройства определения разности двух чисел, выполненные на сдвигающем регистре на ферритовых сердечниках.

Предложенное устройство отличается тем. что в нем выходы сдвигающего регистра, длина которого равна удвоенной константе минус единица, от участков сдвигающего регистра, длиною, равной половине константы, подсоединены через схемы «ИЛИ к первым входам первой, второй, третьей и четвертой схем С01зпадения, вторые входы которых подключены к источнику импульсов опроса результата операции; выходы первой и третьей схем совпадения соединены с единичными входами первого триггера, а выходы второй и четвертой схем - с единичными входами второго триггера, нулевые входы которых подсоединены к источнику импульсов установки нуля, а также к выходу схемы «ИЛИ съема минимальной разности; выходы триггеров через клапаны, п,одсоединенные также к источнику серии импульсов съема минимальной разности, и схемы задержки, подключенные к ключам прямого и обратного счета, выход нулевого разряда регистра и источник импульсов опроса результата операции подключены ко входам пятой схемы совпадения; выходы крайних старших разрядов и выходы первых разрядов подсоединены через схему «ИЛИ ко входу шестой схемы совпадения, второй вход которой через cxeAiy «ИЛИ подключен к выходам триггеров; а выходы пятой схемы совпадения 1 шестой схемы совпадения соединены со входами схемы «ИЛИ выделения минимальной разности.

Это позволяет определить разность двух чисел, меньших заданной константы, определить разность константы и разность этих чисел, определить минимальную разность из этих двух разностей, а также определить ее знак.

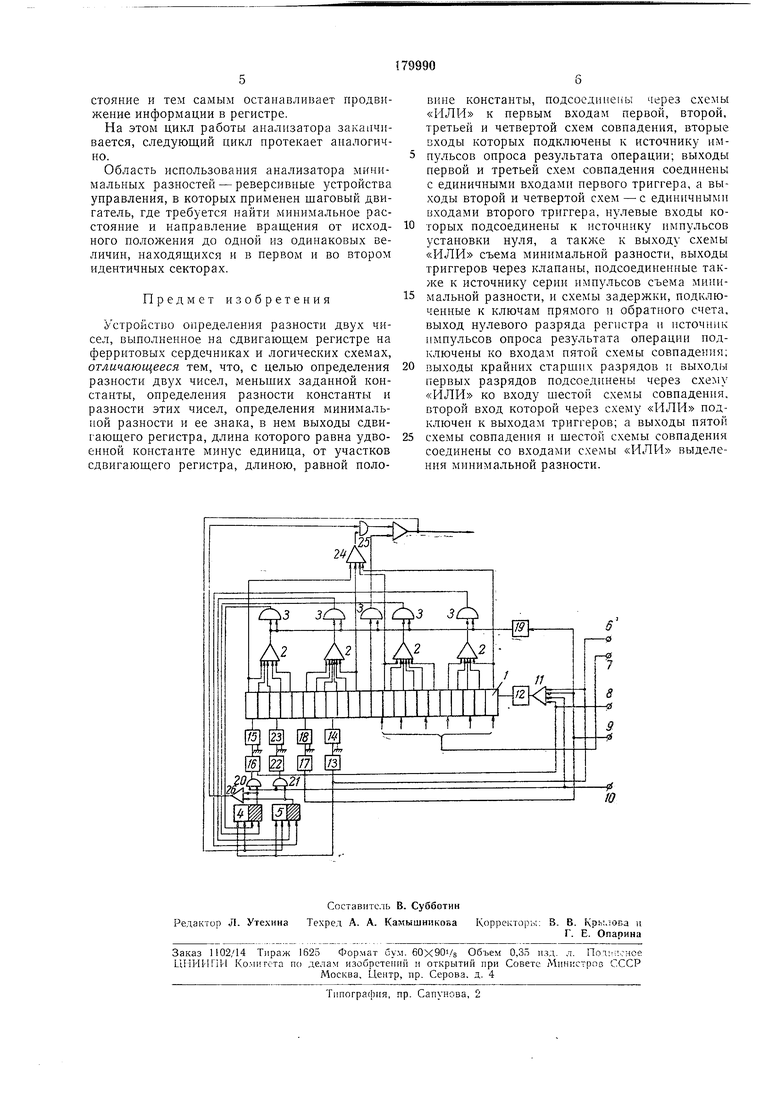

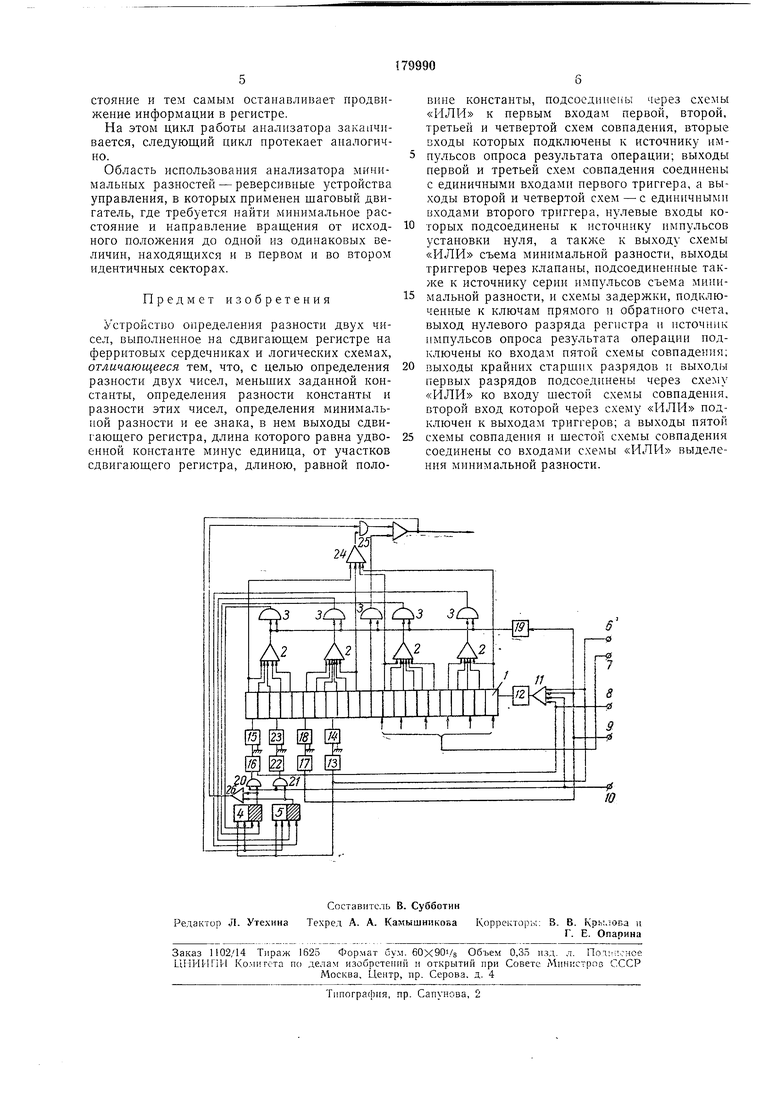

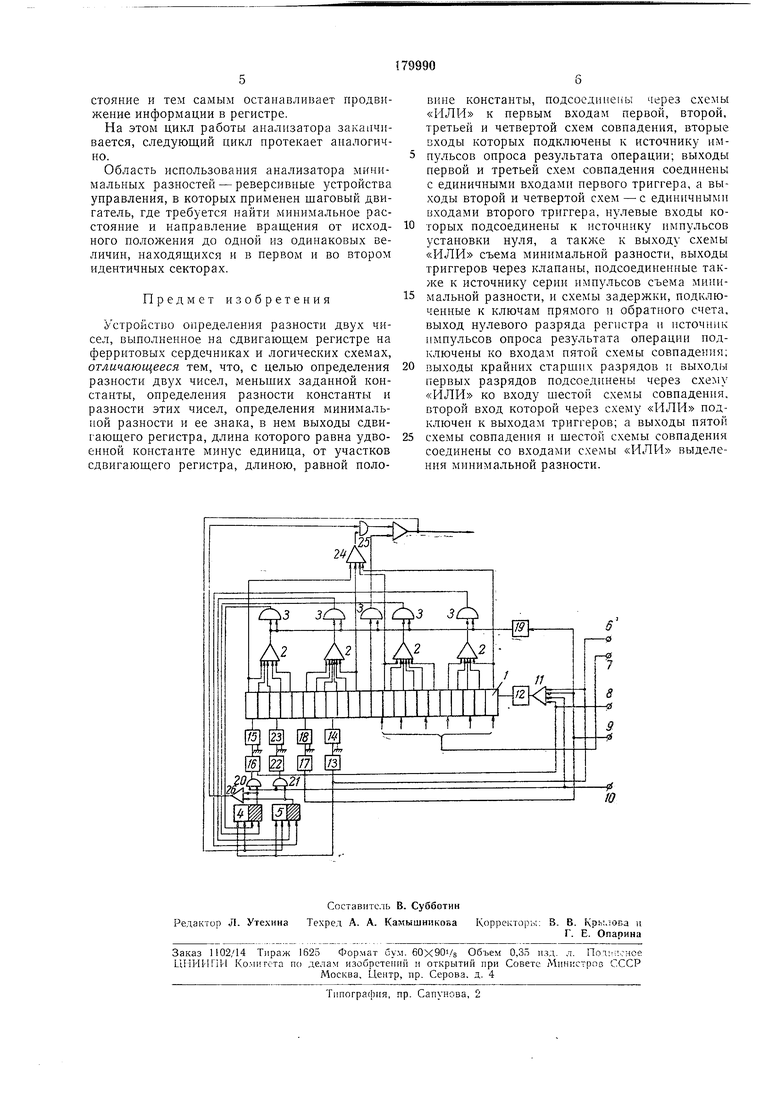

На чертеже представлена блок-схема предлагаемого устройства.

.Анализатор минимальной разности состоит из регистра / разности, схем 2 «ИЛИ и схем 3 совпадения, объединяющих выходы со всех сердечников регистра в группы минимальных разностей и триггеров 4, 5 управляющих направлением счета в регистре.

Анализатор работает от входных сигналов, подаваемых по раздельным цепям. По входу б подают импульс установки «О, по входу 7- импульс записи числа Ki в регистр 1 в позиционно десятичном коде, по входу 8 - серию импульсов записи числа К-2 в регистр / в унитарном коде; по входу 9 - импульс опроса результата операции, по входу W - серию импульсов съема минимальной разности.

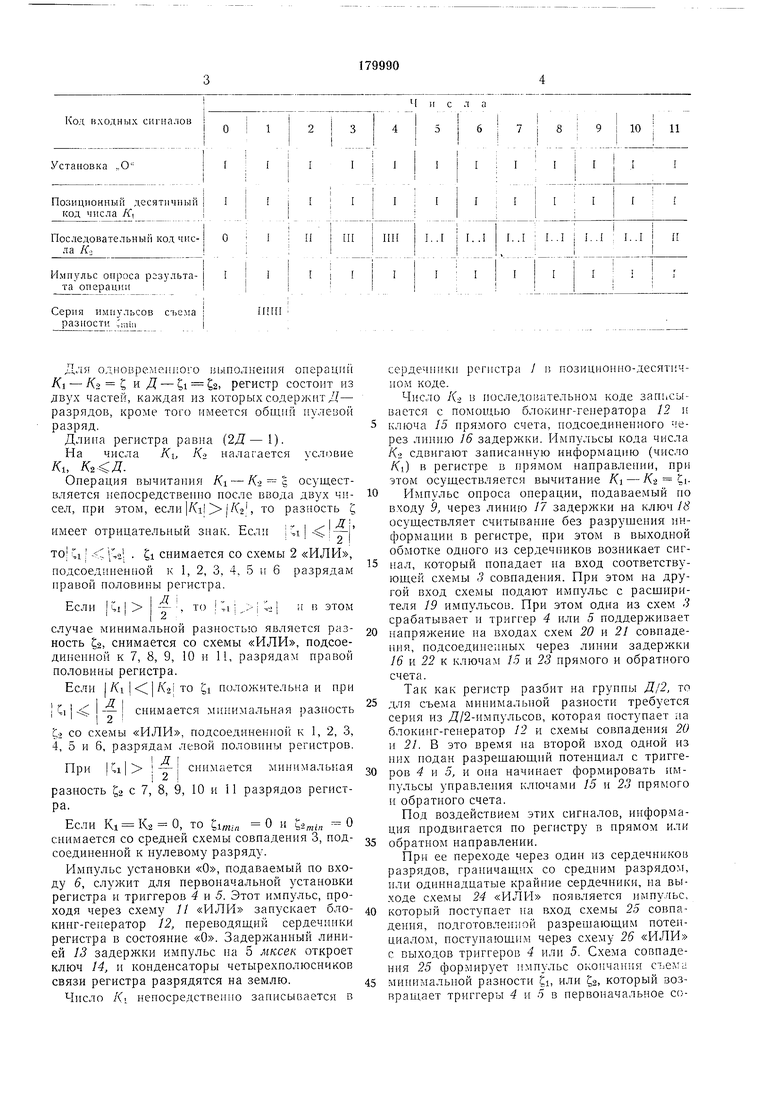

Код входных сигналов

Установка ,,ОI

О

И I III ПИ

Импульс опроса ргзульта jra onepamiii

Серия импульсов съема разности li-niiii

10 ; и

..I I I..I

I..I : I..I : 1..I : I..I i и

I I

| название | год | авторы | номер документа |

|---|---|---|---|

| АНАЛИЗИРУЮЩЕЕ УСТРОЙСТВО | 1969 |

|

SU246156A1 |

| ЗНАКОВЫЙ ЦИФРОВОЙ КОРРЕЛЯТОР"^ =-.»^»—~^ | 1971 |

|

SU310254A1 |

| УСТРОЙСТВО для ПРЕОБРАЗОВАНИЯ КОДОВ | 1967 |

|

SU201774A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО | 1972 |

|

SU429423A1 |

| Устройство программного управления с самоконтролем | 1981 |

|

SU999018A1 |

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1969 |

|

SU255993A1 |

| СПОСОБ ОБРАБОТКИ ГИДРОАКУСТИЧЕСКИХ СИГНАЛОВ СО СЛОЖНЫМ ЗАКОНОМ МОДУЛЯЦИИ | 2001 |

|

RU2293356C2 |

| Измеритель временных интервалов | 1983 |

|

SU1155990A1 |

| Ассоциативное запоминающее устройство | 1985 |

|

SU1274002A1 |

| ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ АНАЛОГ - КОД | 1991 |

|

RU2027303C1 |

л1,ля одновремеллого выполнения onepaunii /Ci - K.z t, и Д - 1 2, регистр состоит из двух частей, каждая из которых содержит Д- разрядов, кроме того имеется общий нулевой разряд.

Длина регистра равна (2Д-1).

На числа Кь .- налагается условие /Сь .

Операция вычитания /d - /(2 g осуществляется непосредственно после ввода двух чнсел, при этом, если j/Cj, то разность С,

А

нак. Если I

имеет отрицательный 2

то| Ci I - i,2l . 1 снимается со схемы 2 «ИЛИ,

подсоединенной к 1, 2, 3,

-, 5 и 6 разрядам нравой ноловины регистра. Д

Если I Ci I

il 15 этом

T(J

случае минимальной разность 0 является разность ga, снимается со схемы «ИЛИ, подсоединенной к 7, 8, 9, 10 н 11, разрядам правой половины регистра. Если | С|Д2| то 1 ноложнтельна и нрн

I - I /Д i

j С I - снимается минимальная разность

1

Г,. со схемы «ИЛИ, нодсоелТ,нненной к 1,2, 3, 4, 5 и 6, разрядам левой половины регистров. Д

При

;у

снимается минимальная

разность 2 с 7, 8, 9, 10 и 11 разрядов регистра.

Если 0, то 1„г;„ 0 и ,, 0 снимается со средней схемы совпадения 3, подсоединенной к нулевому разряду.

Импульс установки «О, подаваемый но входу 6, служит для первоначальной установки регистра и триггеров 4 и 5. Этот имнульс, проходя через схему // «ИЛИ запускает блокинг-генератор 12, переводящий сердечники регистра в состояние «О. Задержанный линией 13 задерл ки импульс на 5 мксек откроет ключ 14, н конденсаторы четырехполюсников связи регистра разрядятся на землю.

сердечники регистра / г, нознционио-десятнчиом коде.

К- в иоследовательном коде заньсь вается с номоилью блокниг-генератора 12 и ключа 15 ирямого счета, нодсоединеиного через линию 16 задержки. Импульсы кода числа К.-, сдвигают записанную информацию (число Ki) в регистре в ирямом направлении, при этом осуществляется вычитание /Cj - K-i tiИмпульс опроса операции, подаваемый по входу 9, через линию 17 задержки на ключ 18 осуществляет считывание без разрущения информации в регистре, при этом в выходиой обмотке одного из сердечников возникает снгнал, который попадает на вход соответствующей схемы 3 совпадения. При этом на другой вход схемы подают импульс с расширителя 19 импульсов. При этом одиа из схем 3 срабатывает н триггер 4 или 5 поддерживает

напряжение на входах схем 20 и 21 совиадеиия, нодсоединеиных через линии задержки

16 и 22 к ключам 15 и 23 нрямого и обратного

счета.

Так как регистр разбит на груипы Д/2, то

для съема мииимальной разности требуется серия из Д/2-импульсов, которая поступает на блокинг-генератор 12 и схемы совпадения 20 и 21. В это время иа второй вход одной из них нодан разрещающнй потенциал с триггеров 4 и 5, н оиа начинает формировать импульсы управления ключами 15 и 23 нрямого и обратного счета.

Под воздействием этих сигналов, информация продвигается по регистру в нрямом или

обратном направлении.

При ее переходе через один из сердечников разрядов, граничащих со средиим разрядом, или одиннадцатые крайние сердечники, иа выходе схемы 24 «ИЛИ появляется импульс,

который поступает на вход схемы 25 совпадения, подготовленной разрешающим потенциалом, поступающим через схему 26 «ИЛИ с выходов триггеров 4 или 5. Схема совпадения 25 формирует импульс окончания

Даты

1966-01-01—Публикация