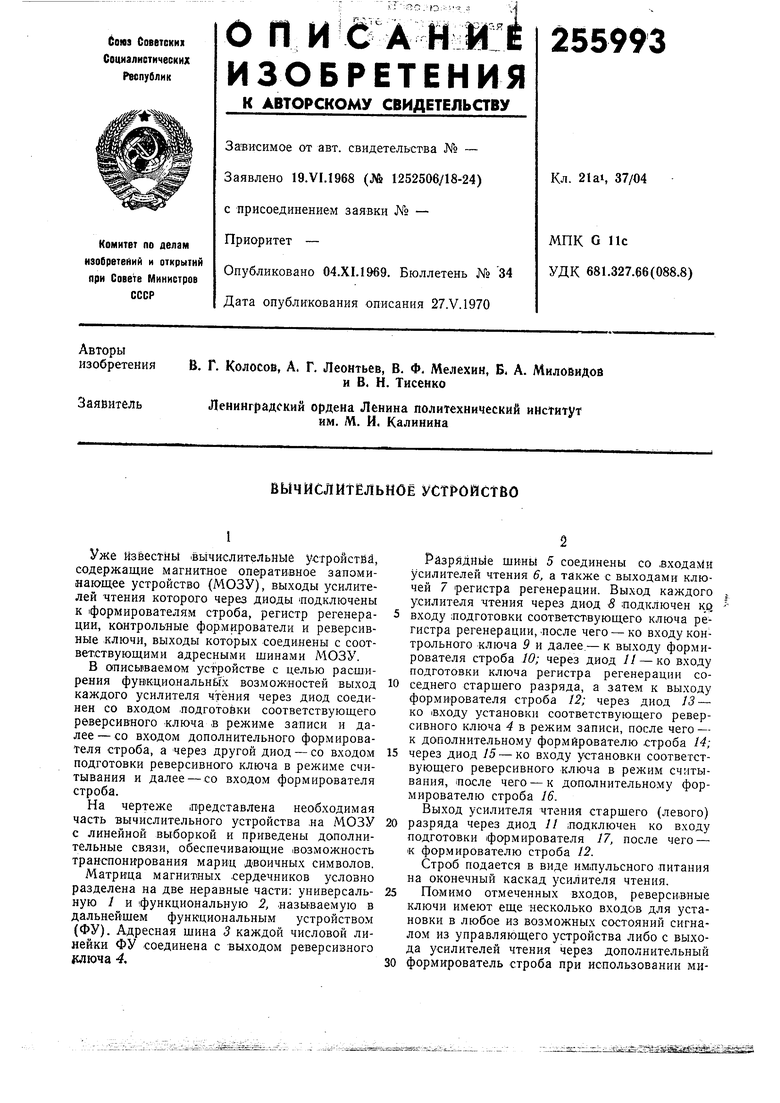

Уже Известны вычислительные устройстйй, содержащие магнитное оперативное запомииающее устройство (МОЗУ), выходы усилителей чтения которого через диоды подключены к формирователям строба, регистр регенерации, контрольные формирователи и реверсивные ключи, выходы которых соединены с соответствующими адресными шинами МОЗУ.

В описываемом устройстве с целью расширения функциональных возможностей выход каждого усилителя чтения через диод соединен со входом лодготойки соответствующего реверсивного ключа в режиме записи и далее- со входом дополнительного формирователя строба, а через другой диод - со входом подготовки реверсивного ключа в режиме считывания и далее - со входом формирователя строба.

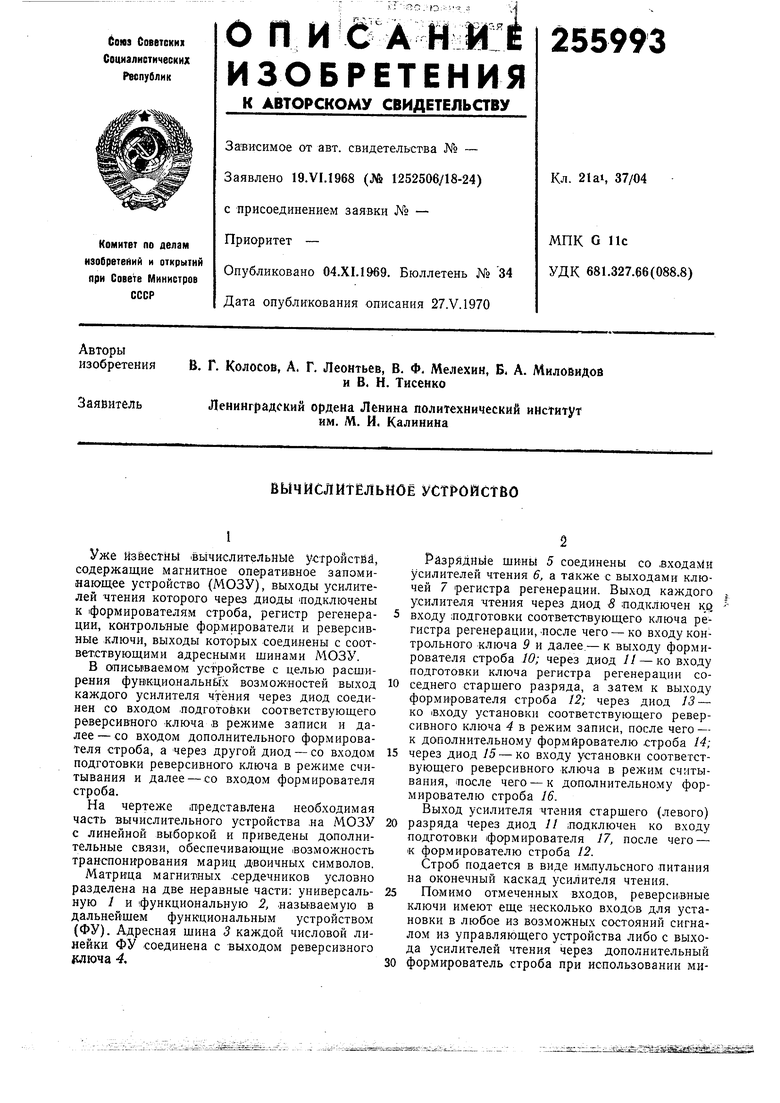

На чертеже представлена необходимая часть вычислительного устройства .на МОЗУ с линейной выборкой и приведены дополнительные связи, обеспечивающие возможность транспонирования мариц двоичных символов.

Матрица магнитных сердечников условно разделена на две неравные части: универсальную / и функциональную 2, называемую в дальнейшем функциональным устройством (ФУ). Адресная шина 3 каждой числовой линейки ФУ соединена с выходом реверсивного |слюча 4,

РазряДнУе щинЫ 5 соединены со .входами усилителей чтения 6, а также с выходами ключей 7 регистра регенерации. Выход каждого усилителя чтения через диод S подключен KQ

входу подготовки соответствующего ключа регистра регенерации, .после чего - ко входу контрольного ключа 9 и далее.- к выходу формирователя строба 10; через диод // - ко входу подготовки ключа регистра регенерации соседнего старшего разряда, а затем к выходу формирователя строба 12; через диод 13 - ко входу установки соответствующего реверсивного ключа 4 в режим записи, после чего - к дополнительному формирователю строба 14;

через диод 15 - ко входу установки соответствующего реверсивного ключа в режим считывания, (после чего - к дополнительному формирователю строба 16.

Выход усилителя чтения старшего (левого)

разряда через диод 11 .подключен ко входу подготовки формирователя 17, после чего - к формирователю строба 12.

Строб подается в виде имлульсного питания на оконечный каскад усилителя чтения.

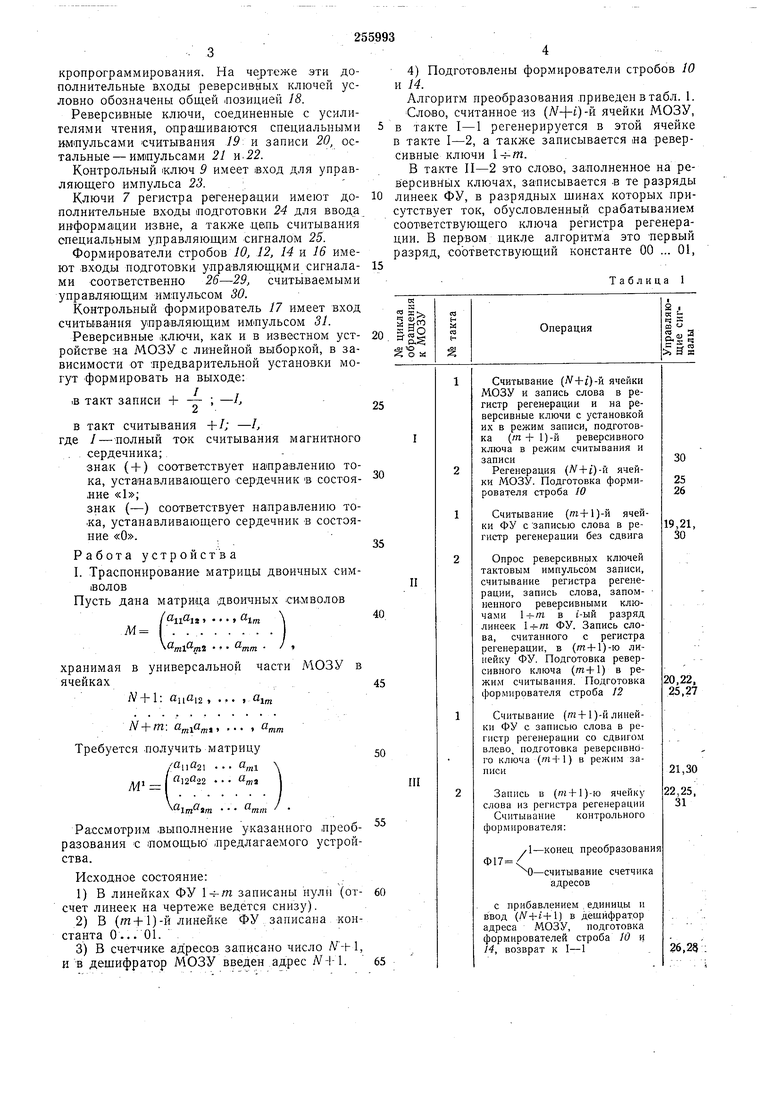

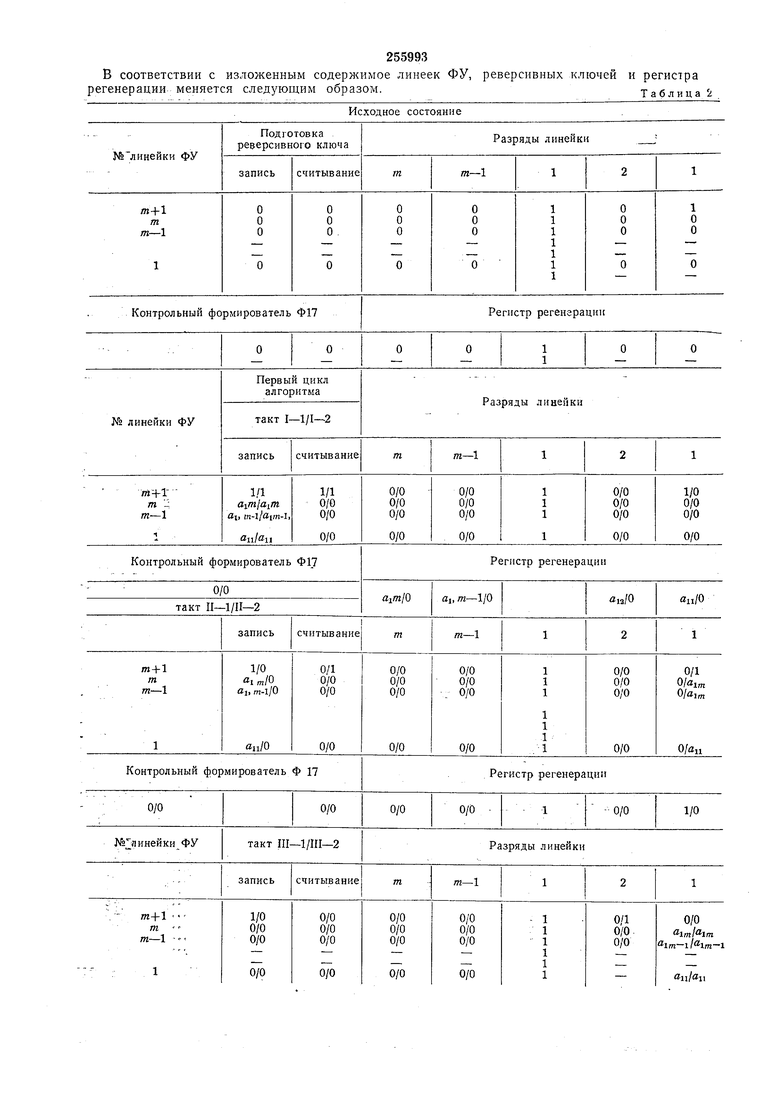

Помимо отмеченных входов, реверсивные ключи имеют еще несколько входов для установки в любое из возможных состояний сигналом из управляющего устройства либо с выхода усилителей чтения через дополнительный кропрограммирования. На чертеже эти дополнительные входы реверсивных ключей условно обозначены общей позицией 18. Реверсивные ключи, соединенные с усилителями чтения, опрашиваются специальными шшпульсами считывания 19 и записи 20, остальные- импульсами 21 и.22. Контрольный 1КЛЮЧ 9 имеет вход для управляющего импульса 23. Ключи 7 регистра регенерации имеют дополнительные входы подготовки 24 для ввода информации извне, а также цепь считывания специальным управляющим сигналом 25. Формирователи стробов lOj 12, 14 и 16 имеют .входы подготовки управляю щими сигналами соответственно 26-29, считываемыми управляющим имяульсом 30. Контрольный формирователь 17 имеет вход считывания управляющим импульсом 31. Реверсивные .ключи, как и в известном устройстве на МОЗУ с линейной выборкой, в зависимости от предварительной установки могут формировать на выходе: iB такт записи + - ; -I, в такт считывания +1; -/, где / - полный ток считывания магнитного . , сердечника;. знак (-f) соответствует направлению тока, устанавливающего сердечник в состояниезнак (-) соответствует направлению тока, устанавливающего сердечник в состояние «О. Работа устройства I. Траспонирование матрицы двоичных симПусть дана матрица двоичных символов , .,., части МОЗУ в Хранимая в универсальной ячейках V + 1: aii«i2 , ... , а - N + m: ,, ...,«„„ Требуется получить матрицу , ... а„ Рассмотрим .выполнение указанного преобразо-вания с помощью предлагаемого устройства. Исходное состояние: 1)В линейках ФУ записаны нули (отсчет линеек на чертеже ведется снизу). 2)В (т+1)-и линейке ФУ записана константа О... 01. влены формирователи стробов 10 реобразования приведен в табл. 1. танноеИЗ (N-}-i)-fi ячейки МОЗУ, 1 регенерируется в этой ячейке а также записывается на ревери . -2 это слово, заполненное на реючах, записывается -в те разряды в разрядных шинах которых прик, обусловленный срабатыванием щего ключа регистра регенерам цикле алгоритма это первый ветствующий константе 00 ... 01, Таблица 1 Операция Считывание (N+i)-ii ячейки МОЗУ и запись слова в регистр регенерации и на реверсивные ключи с установкой их в режим записи, подготовка (т -f 1)-й реверсивного ключа в режим считывания и записи Регенерация ()-й ячейки МОЗУ. Подготовка формирователя строба W Считывание (т-Ы)-й ячейки ФУ с записью слова в регистр регенерации без сдвига Опрос реверсивных ключей тактовым импульсом записи, считывание регистра регенерации, запись слова, запомненного реверсивными ключами в i-ый разряд линеек ФУ. Запись слова, считанного с регистра регенерации, в (т + 1)-к лииейку ФУ. Подготовка реверсивного ключа (т+1) в режим считывания. Подготовка формирователя строба 12 Считывание (т-1-1)-й линейки ФУ с записью слова в регистр регенерации со сдвигом влево, подготовка реверсивного ключа (тН-1) в режим записиЗапись в (т + 1)-ю ячейку слова из регистра регенерации Считывание контрольного формирователя: 1-конец преобразования О-считывание счетчика адресов с прибавлением .единицы и ввод (M+i+l) в дешифратор адреса МОЗУ, подготовка формирователей строба 10 и 14, возврат к I-1 В соответствии с изложенным содержимое регенерации меняется следующим образом. линеек ФУ, реверсивных ключей и регистра Таблица/

Продолжение табл. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО для ПАРАЛЛЕЛЬНОГО СУММИРОВАНИЯДВУХ ЧИСЕЛ | 1970 |

|

SU268498A1 |

| ЦИФРОВОЕ ВЫЧИСЛИТЕЛЬНО-ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1970 |

|

SU273523A1 |

| ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU428450A1 |

| ЛОГИЧЕСКОЕ ЗАПОЛНИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU432598A1 |

| ЬИЬЛИО', ЕКА | 1973 |

|

SU365707A1 |

| ЦИФРОВОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО НА ПОЛНОТОЧНОМНАКОПИТЕЛЕ | 1971 |

|

SU289514A1 |

| Логическое запоминающее устройство | 1972 |

|

SU474847A2 |

| Логическое запоминающее устройство | 1971 |

|

SU443411A1 |

| УСТРОЙСТВО для ВЫБОРКИ ИНФОРМАЦИИ из постоянного ТРАНСФОРМАТОРНОГО ЗАПОМИНАЮЩЕГО | 1973 |

|

SU377868A1 |

| ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1970 |

|

SU258388A1 |

записанной в (т+1)-й линейке ФУ. В тактах III-1, III-2 в результате сдвига единица в (т+1)-и ячейке лередвигается на один разряд (Влево. Поэтому во втором цикле алгоритма слово записывается во второй {зазряд линеек ФУ и так далее.

В такте II1-2 контролируется ко-нец преобразования матрицы. Если имцульс на выходе контрольного формирователя 17 отсутствует (условно Ф17 0), это значит, что еще не во в;се разряды линеек ФУ за-писаны слова-столбцы, т. е. что матрица М затисана еще не полностью.

Если в такте HI-1 сдвигаемая единица выходит за разрядную сетку и подготавливает контрольный формирователь, это значит, что матри1ца М записана полностью. Поэтому срабатывание формирователя 17 (условно ) фиксирует конец преобразования.

Преобразование может быть вьшолнено ПО следующему алгоритму (см. табл. ).

В соответствии с изложенным содержимое линеек ФУ, реверсивных ключей и регистра регенерации (меняется следующим образом (см. табл. 2).

Для транспонирования матрицы mxtn потребуется 3/п циклов обращения к ЗУ.

7 О О О О О 1 1 О

О О О О

о о

о о

О О

о о о о о 1

о о о

о о

Возможно преобразование неквадратной матрицы тих при . В этом случае в ячейку т+1 записывается константа Л , ... , а

д I 1 при t

I О при i m-fe+il

В рассмотренном выще алгоритм-е в качестве счетчика адресов предполагалось использование специального счетчика.

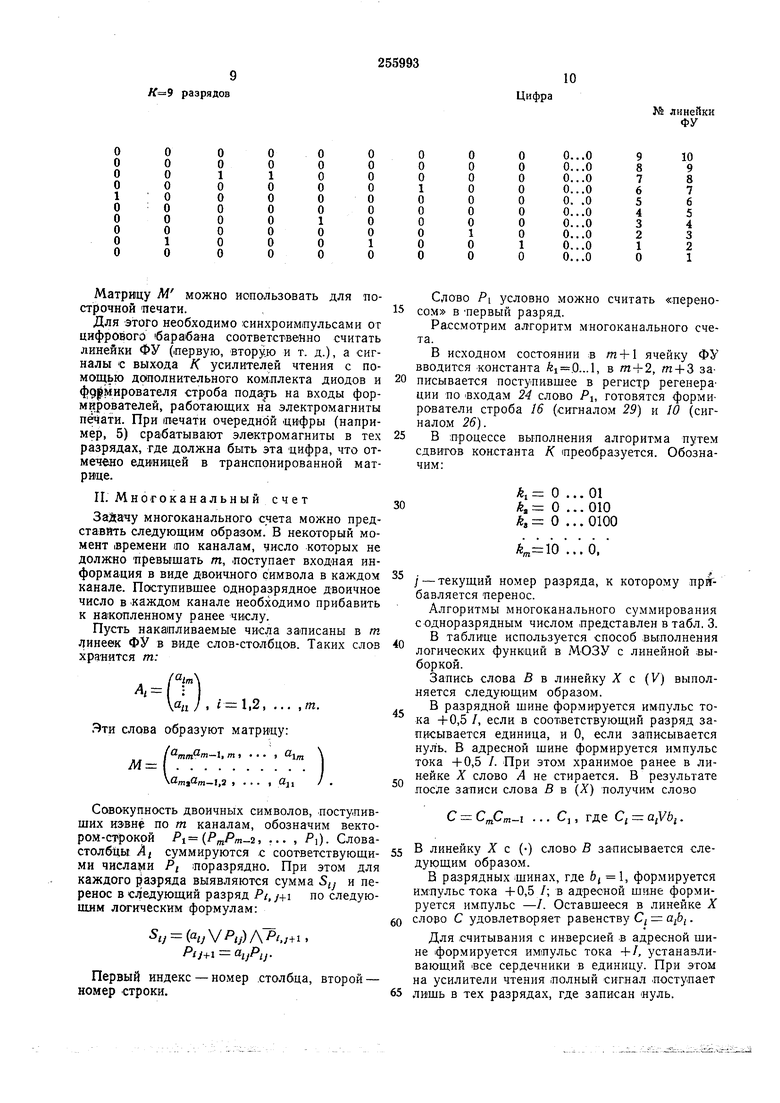

Транспонирование матрицы может быть использовано, например, для преобразования информации при выводе на построчную печать. Рассмотрим подробнее вывод на построчную печать К-разрядных десятичных чисел в коде 1 из 10. Код 1 из 10 получается в процессе преобразования двоичных чисел в десятичные. Это преобразование может выполняться вычислительным устройством на МОЗУ (см. упомянутую заявку) программным путем. Для простоты рассмотрим случай, когда каждый десятичный разряд в коде 1 из 10 залисаи В отдельную линейку МОЗУ. Все слово хранится iB К. линейках. Например, при число Л 517731421 представлено матрицей М:

Адрес

о о о о о о о о о о

о, ЛГ+1

.0

о 1 о о о о о о о Л/Ч-2 .0

0. 0. 0. 0. 0. 0. 0. 0.

о 1 о о о о о о

о о 1 о о о 1 о .0 .0 ЛГ+5 .0 ЛГ+6 .0 ЛГ-1-7 .0 ЛГ-Ь8 .0 .0

разрядов

Матрицу М можно использовать для построчной печати.

Для этого необходимо синхроимпульсами от цифрового бара1бана соответственно считать линейки ФУ (.первую, втору.ю и т. д.), а сигналы с выхода К усилителей чтения с помоц|;ью дополнительного комплекта диодов и ф9|миравателя строба подать на входы форм рователей, работающих на электромагниты печати. При течати очередной цифры (например, 5) срабатывают электромагниты в тех разрядах, где должна быть эта цифра, что отмечено единицей в транспонированной матрице.

II. Многоканальный счет

Зайачу многоканального счета можно представить следующим образом. В некоторый момент (Времени ino каналам, число которых не должно превыщать т, .поступает входная информация в виде двоичного символа в каждом канале. Паступивщее одноразрядное двоичное число в .каждом канале необходимо прибавить к накопленному ранее числу.

Пусть нака1пливаемые числа записаны в т линеек ФУ в виде слов-столбцов. Таких слов хранится т:

4 I % / . f - Ii2т.

Эти слова образуют матри цу:

, m ... , GI

М QmiQm-I,2 ... I Oji

Совокупность ДВОИЧНЫХ СИМВОЛОВ, поступивших ИЗВН по т каналам, обозначим вектором-строкой Pi(, ... , Р}). Словастолбцы AI суммируются с соответствующими числами PI поразрядно. При этом для каждого разряда выявляются сумма и перенос в следующий разряд Pt.j+i по следующим логическим формулам:

Sij ().,i, Pii+i ai}PiiЦифра

Слово Р условно можно считать «переносом в Первый разряд.

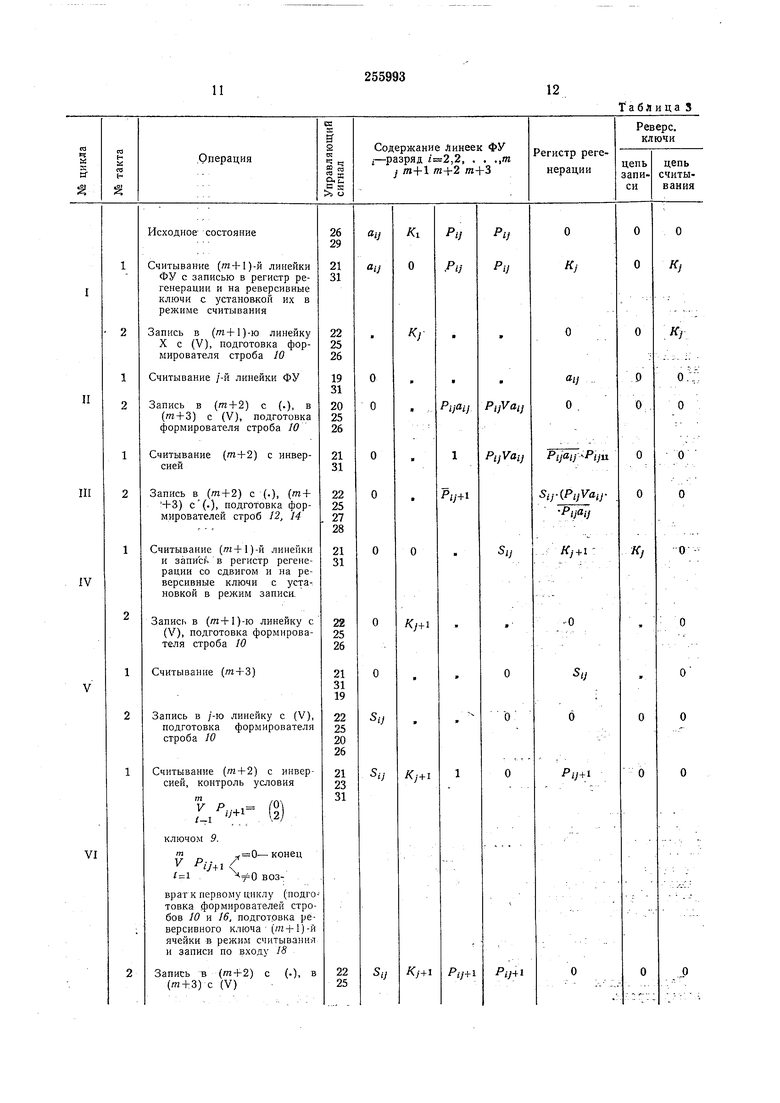

Рассмотрим алгоритм многоканального счета.

В исходном состоянии в т-Ы ячейку ФУ вводится константа i.0...1, в от+ 2, т + 3 записывается поступившее в регистр регенерации по .входам 24 слово Р, готовятся формирователи строба 16 (сигналом 25) и 10 (сигналом 26}.

В процессе выполнения алгоритма путем сдвигов константа К преобразуется. Обозначим:

k О ... 01 fe, О ... 010 А;, о ... 0100

... 6/

/ - текущий номер разряда, к которому прибавляется перенос.

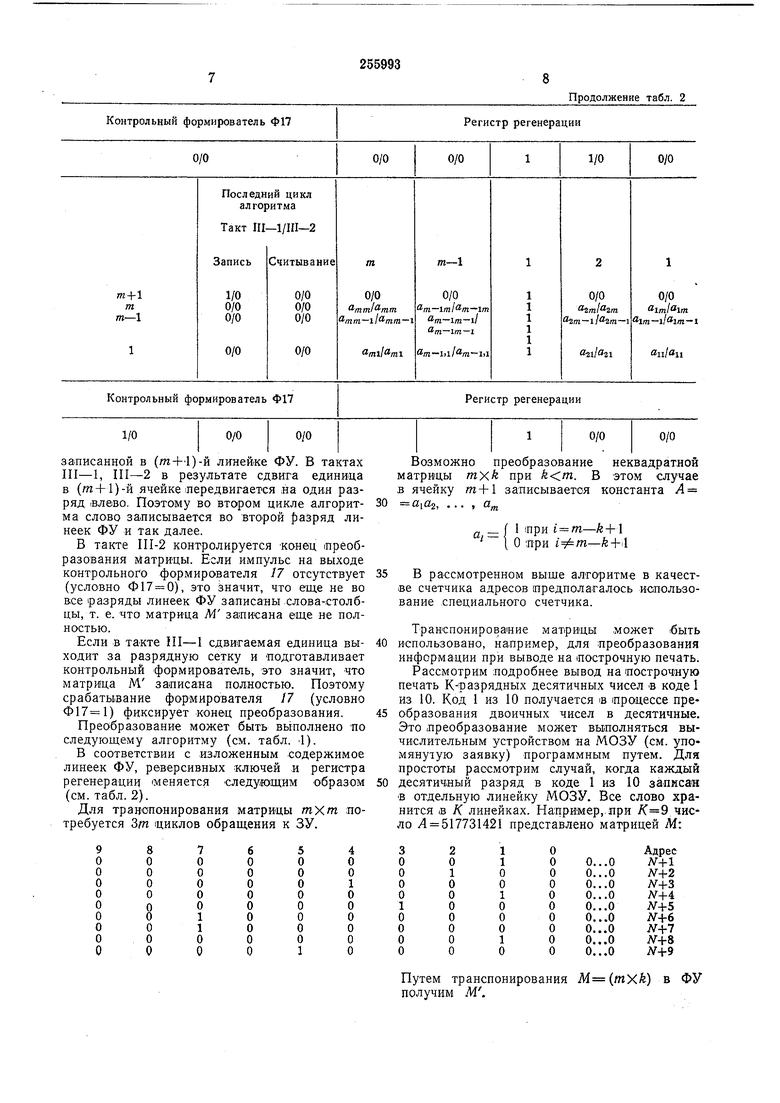

Алгоритмы многоканального суммирования с одноразрядным числом представлен в табл. 3.

В таблице используется способ выполнения логических функций в МОЗУ с линейной выборкой.

Запись слова В в линейку Л с (V) выполняется следующим образом.

В разрядной шине формируется импульс тока + 0,5 /, если в соот.ветствующий разряд записывается единица, и О, если записывается нуль. В адресной шине формируется импульс тока +0,5 /. При этом хранимое ранее в линейке X слово А не стирается. В результате после записи слова В в (К} получим слово

С ... С,, где GI - .

В линейку X с () слово В записывается следующим образом.

В разрядных шинах, где ft, 1, формируется импульс тока +0,5 /; в адресной шине формируется импульс -/. Оставшееся в линейке X

слоео С удовлетворяет равенству Q : аД .

Для считывания с инверсией в адресной шине формируется импульс тока +/, устанавливающий .все сердечники в единицу. При этом на усилители чтения .полный сигнал поступает лишь в тех разрядах, где записан пуль.

Таблица S

Необходимые импульсы тока в адресных шинах формируются реверсивными ключами 4.

Из приведенной таблицы видно, что для многоканального суммирования с одноразрядными числами требуется от 6 до 6/и обращений к МОЗУ.

После цикла суммирования в матрице ФУ записаны числа

тт.т-1,т, .... S

т,т--1 m-l,m-lt -Jl, ш-1

,1 ... t 11

Если счет ведется не -с нуля, а с некоторых значений, которые хранятся в N+1, N+2, ..., линейках МОЗУ, предварительно следует транопонирОВать матри-цу, образованную этими чи.слами, а затем перейти к многоканальному счету.

Аналогично может быть разработан алгоритм параллельного суммирования двух групп слов (|по m чисел в каждой группе). Матрицы, соответствующие «аждой груопе, должны быть

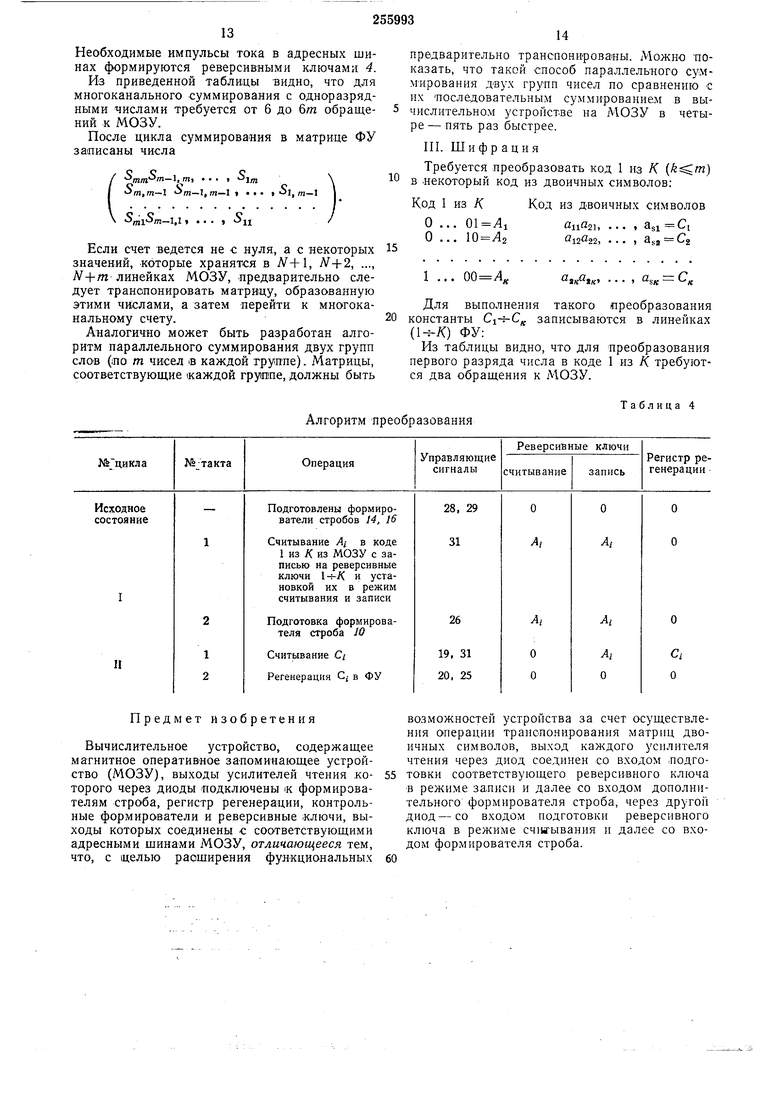

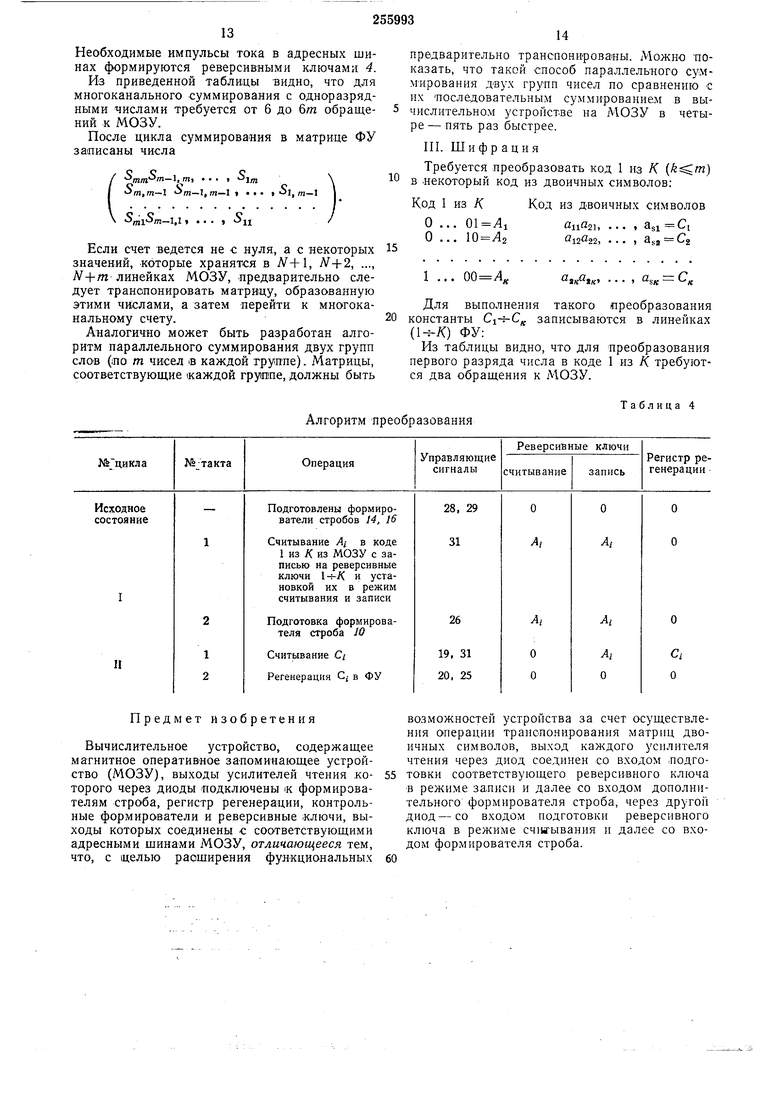

Алгоритм преобразования Предмет изобретения Вычислительное устройство, содержащее магнитное оперативное запоминающее устройство (МОЗУ), выходы усилителей чтения ко- 55 торого через диоды подключены « формирователям строба, регистр регенерации, контрольные формирователи и реверсивные .ключи, выходы которых соединены с соответствующими адресными шинами МОЗУ, отличающееся тем, что, с щелью расширения функциональных 60

предварительно транспонироваеы. Можно -показать, что такой способ параллельного сумМирования Двух групп чисел по сравнению с их последовательным суммированием в вычислительно.м устройстве на МОЗУ в четыре - пять раз быстрее.

III. Шифрация

Требуется преобразовать код 1 из /С () в .некоторый код из двоичных символов:

Код 1 из К Код из двоичных символов О ... 01 Л1 110213 1 Ci

О ... 10 Лг012022, ... ,

OSK - я

Для выполнения такого преобразования константы Cj-f-C записываются в линейках (1-V-/C) ФУ:

Из таблицы видно, что для преобразования первого разряда числа в коде 1 из К требуются два обращения к МОЗУ.

Таблица 4 возможностей устройства за счет осуществления операции транспонирования матриц двоичных символов, выход каждого усилителя чтения через диод соединен со входом .подготовки соответствующего реверсивного ключа в режиме записи и далее со входом дополнительного формирователя строба, через другой диод-со входом подготовки реверсивного ключа в режиме счиа-ывания и далее со входом формирователя строба.

tl 12

и 2(

Г8

o

-w

4

23

30

Vtfi

/2

16 It

гттт «

29 28 27 26 31 2Ч

«

; .-;Г

iH

«r $1

,5

.J

IZZHCZD

+4

25

-f

Даты

1969-01-01—Публикация