Изобретение относится к контрольно- измерительной технике и может быть использовано для контроля монтажа многослойных печатных плат.

Целью изобретения является расширение функциональных возможностей за счет осуществления контроля сопротивлений изоляции цепей многослойных печатных плат.

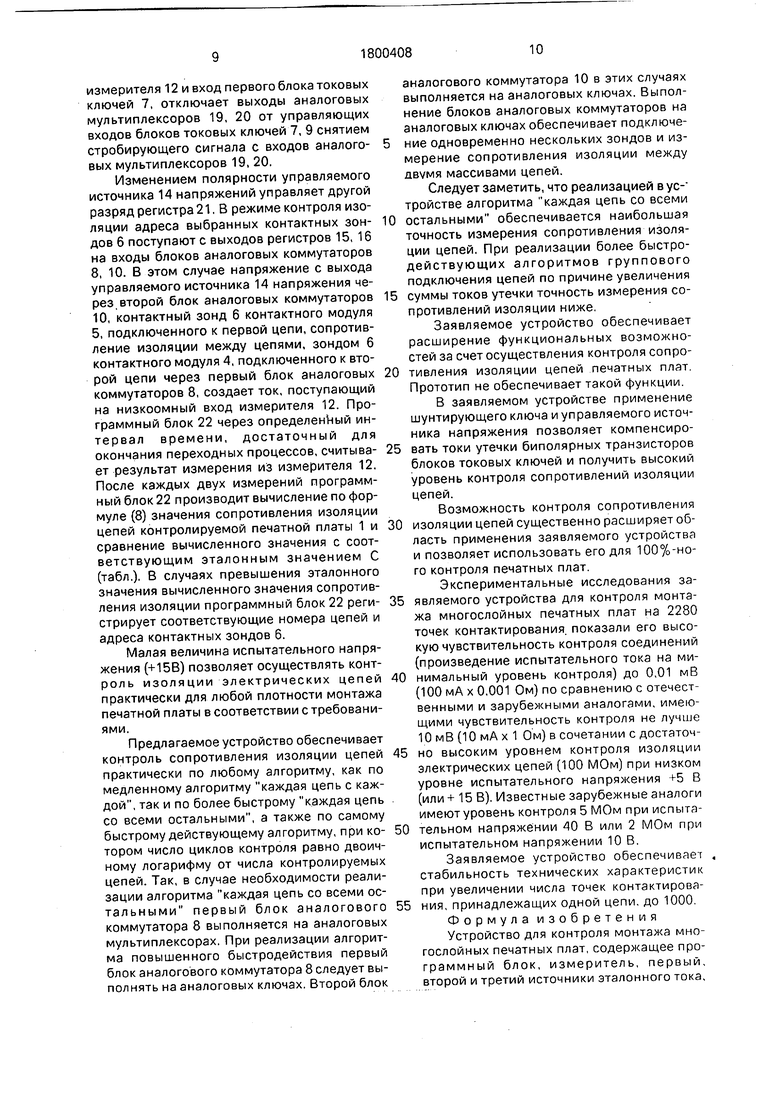

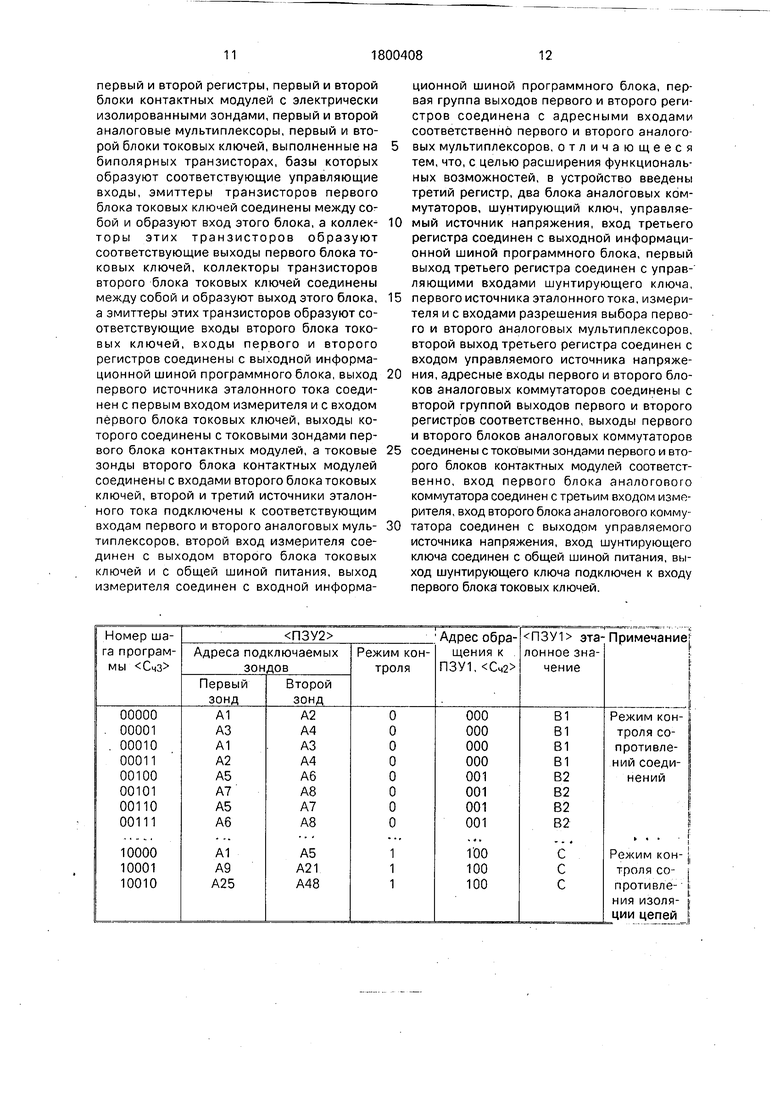

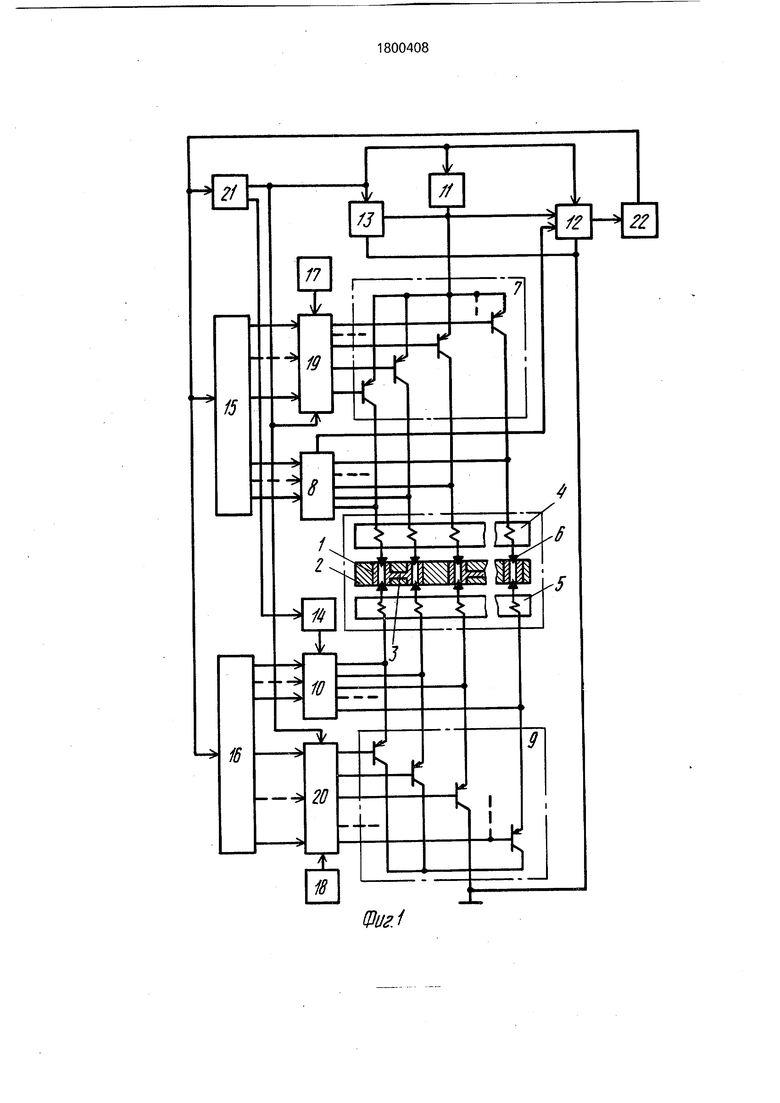

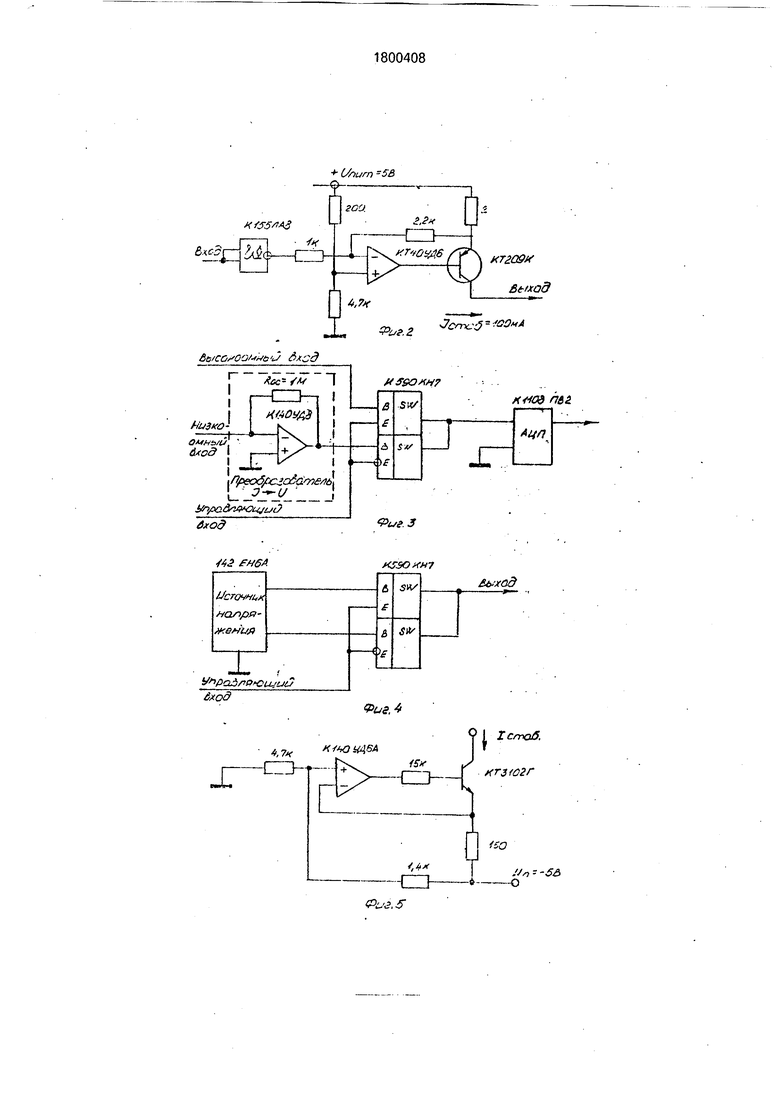

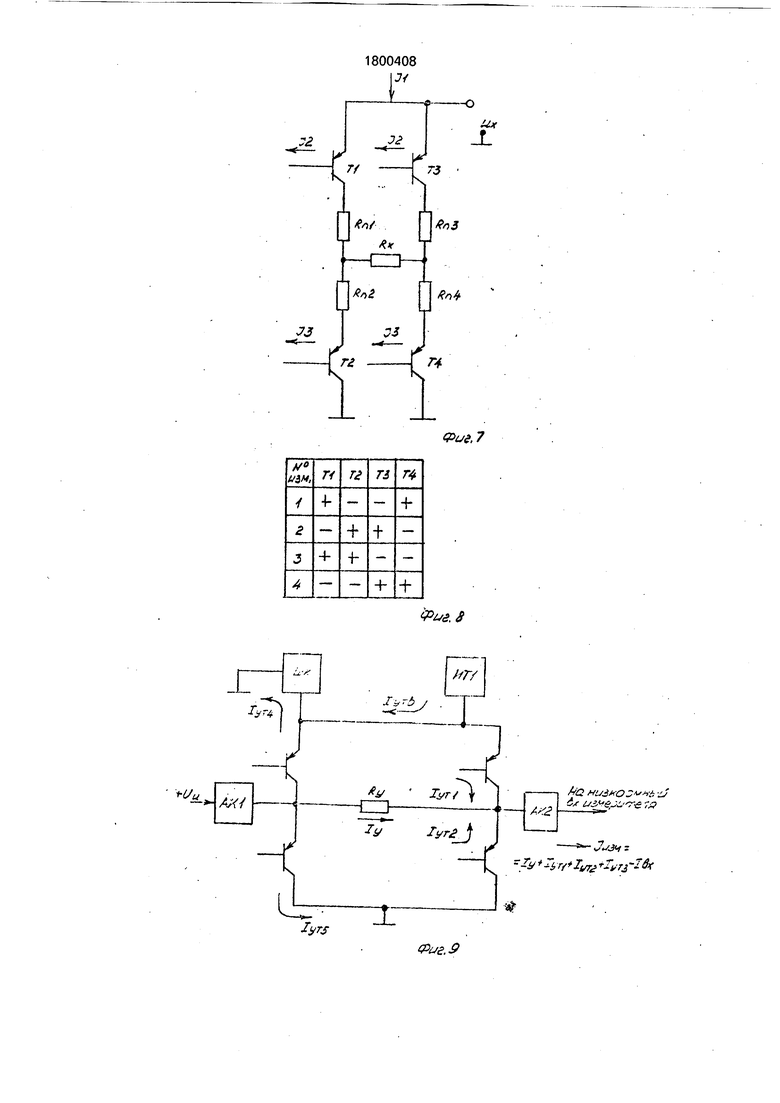

-На фиг.1 изображена блок-схема заявляемого устройства; на фиг.2,3,4,5,6 приведены примеры выполнения первого источника эталонного тока, измерителя, управляемого источника напряжения, второго и третьего источников эталонного тока, программного блока соответственно; на фиг.7 - эквивалентная схема измерения при контроле сопротивления соединения печатной платы; на фиг.8 - состояния транзисторов при измерениях; на фиг.9, 10 - эквивалентная схема устройства при положительном и

отрицательном испытательном напряжении.

Устройство для контроля монтажа многослойных печатных плат 1, приведенное на фиг.1, содержит межслойные и внутрисловные соединения, выполненные в виде металлизированных отверстий 2 и соединяющих их токопроводящих дорожек 3, первого 4 и второго 5 (верхний и нижний) контактных модулей, выполненных в виде матриц отдельных подпружиненных контактных зондов 6, расположенных с шагом. кратным шагу координатной сетки печатной платы 1. Контактные зонды 6 первого (верхнего) контактного модуля 4 подключены к коллекторам биполярных транзисторов первого блока токовых ключей 7 и к выходам первого блока аналогового коммутатора 8. Контактные зонды 6 второго (нижнего) контактного модуля 5 подключены к эмиттерам биполярных транзисторов второго блока токовых ключей 9 и к выходам второго блока

СО

с

00

о о

р

ioo

аналогового коммутатора 10. Блоки токовых ключей 7 и 9 выполнены на транзисторах типа КТ209Г, аАО. 336. 065ТУ. Блоки аналоговых коммутаторов 8, 10 могут быть выполнены на аналоговых мультиплексорах К590КН6 6К0.348.209-05ТУ или на аналоговых ключах К590КН5 6К0.348.209-06ТУ. Входная токовая шина первого блока токовых ключей 7, представляющая собой соединенные эмиттеры транзисторов, подключена к первому источнику 11 эталонного тока, выполненного, например, по схеме, представленной на фиг.2, к первому (высокоомному) входу измерителя 12, выполненного по схеме, представленной на фиг.З, и к выходу шунтирующего ключа 13, выполненного на аналоговых ключах К590КН5 6К0.348.209-06ТУ. Выходная токовая шина второго блока токовых ключей 9, представляющая собой соединенные коллекторы транзисторов, подключена к общей шине питания, к второму (общему) входу измерителя 12, к входу шунтирующего ключа 13. Аналоговый вход первого блока аналогового коммутатора 8 соединен с третьим (низкоомным) входом измерителя 12. Аналоговый вход второго блока аналогового коммутатора 10 соединен с выходом управляемого источника 14 напряжения, выполненного по схеме, представленной на фиг.4. Управляющие входы первого и второго блоков аналоговых коммутаторов 8, 10 соединены с первой группой выходов регистров 15, 16 соответственно.

Управляющим сигналом, поступающим на базу одного из транзисторов каждого блока токовых ключей 7, 9, является стабилизированный ток, формируемый соответствующими вторым и третьим источниками 17, 18 эталонного тока, выполненными, например, по схеме, представленной на фиг.5. Выбор транзисторов блоков токовых ключей 7, 9 осуществляется аналоговыми мультиплексорами 19, 20, выполненными, например, на микросхемах К590КН6 6К0.348.209-05ТУ в соответствии с адресными кодами, поступающими на соответствующие управляющие входы аналоговых мультиплексоров 19, 20 с первой группы выходов регистров 15, 16. Управление разрешением выбора на аналоговые мультиплексоры 19, 20 поступает с третьего регистра 21. Этот сигнал также поступает на управляющие входы шунтирующего ключа 13, первого источника 11 эталонного тока, измерителя 12. Регистры 15, 16, 21 могут быть выполнены, например, на микросхемах типа К555ТМ8 6К0.346.289-29ТУ. Управляемый источник 14 напряжения соединен также с третьим регистром 21 шиной, задающей полярность напряжения на выходе источника 14 напряжения. Значение адресов в регистры 15, 16 и управляющая информация в регистр 21 заносятся программным блоком 22, входная информационная шина которого соединена с выходом измерителя 12. Программный блок 22 может быть выполнен на базе микроЭВМ Электроника МС 0507.02.УВ.030.313

0 6К0.305.181ТУ (ДВК-3) и интерфейсного уз- ла,выполненного, например, по схеме с же- сткой логикой функционирования, например, как приведено на фиг.6. В последнем случае программный блок 22 вклю5 чает в себя узел управления, узел записи результатов измерений, арифметический узел, два постоянных запоминающих устройства (ПЗУ1, ПЗУ2), схему сравнения (СС), триггер брака (ТГ2). Узел управления пред0 назначен для синхронизации работы узлов программного блока и включает в свой состав синхронизирующий генератор (Г), триг- гер с организацией счетного входа, служащий для деления синхронизирующей

5 частоты на 2 (TYi), два элемента И (И1, 1/12), два элемента НЕ (НЕ1, НЕ2), элемент ИЛИ (ИЛИ1). Синхронизирующий генератор состоит из резистора R, конденсатора С, трех элементов НЕ (НЕ4,5,6). Узел записи резуль0 татов измерений предназначен для организации записи результатов измерений измерителем 12 и включает в свой состав двухразрядный двоичный счетчик (Сч1), дешифратор на четыре направления (Дш) со

5 стробирующим входом и четыре регистра (Рг1, Рг2, РгЗ, Рм). Арифметический узел предназначен для формирования значения - и включает в свой состав три сумматора (1, 2, 3) и инверторы

0 (НЕЗ).

ПЗУ1 предназначено для хранения эталонных значений сопротивлений соединений и сопротивления изоляции цепей контролируемой многослойной печатной

5 платы; эти значения заносятся в ПЗУ1 в порядке, соответствующем программе контро- ля, и вк ючает в свой состав непосредственно ПЗУ, счетчик адреса обращения (Сч2) и схему управления записью ад0 реса, включающую элемент И (ИЗ) и элемент задержки сигнала записи (I-).

ПЗУ2 предназначено для хранения программы контроля сопротивлений соединений и сопротивлений изоляции цепей

5 печатной платы. Программа контроля представляет собой массив адресов подключаемых пар контактных зондов. ПЗУ2 включает в свой состав непосредственно ПЗУ, счетчик адреса обращения (Счз) и схему управле- ния записью адреса, включающую два

элемента И (И4, И5), элемент ИЛИ (ИЛИ2) и элемент НЕ (НЕ7). Пример организации ПЗУ1 и ПЗУ2 приведен в таблице.

Схема сравнения (СС) предназначена для реализации функции

х 0 а b

где х - выход схемы; а,Ь - входы схемы.

Триггер брака предназначен для фиксации брака (превышения вычисленного значения по результатам измерений соответствующего эталонного значения).

Пример элементной базы для реализации программного блока:

ИЛ И1,2- микросхема 13ЗЛ И1,

И1, 2- микросхема 133ЛА4.

ИЗ...5-микросхема 133ЛАЗ,

НЕ1...8-микросхема 133ЛН1,

Тг1,Тг2,Рг1...4 -микросхема 133ТМ2,

Сч1...з- микросхема 133ИЕ5, 2)1...3, СС -микросхема 133ИМЗ,

М -микросхема 133ЛА8,

Дш- микросхема 133ИД4,

ПЗУ1,2- микросхема 5ЭЗРФ2.

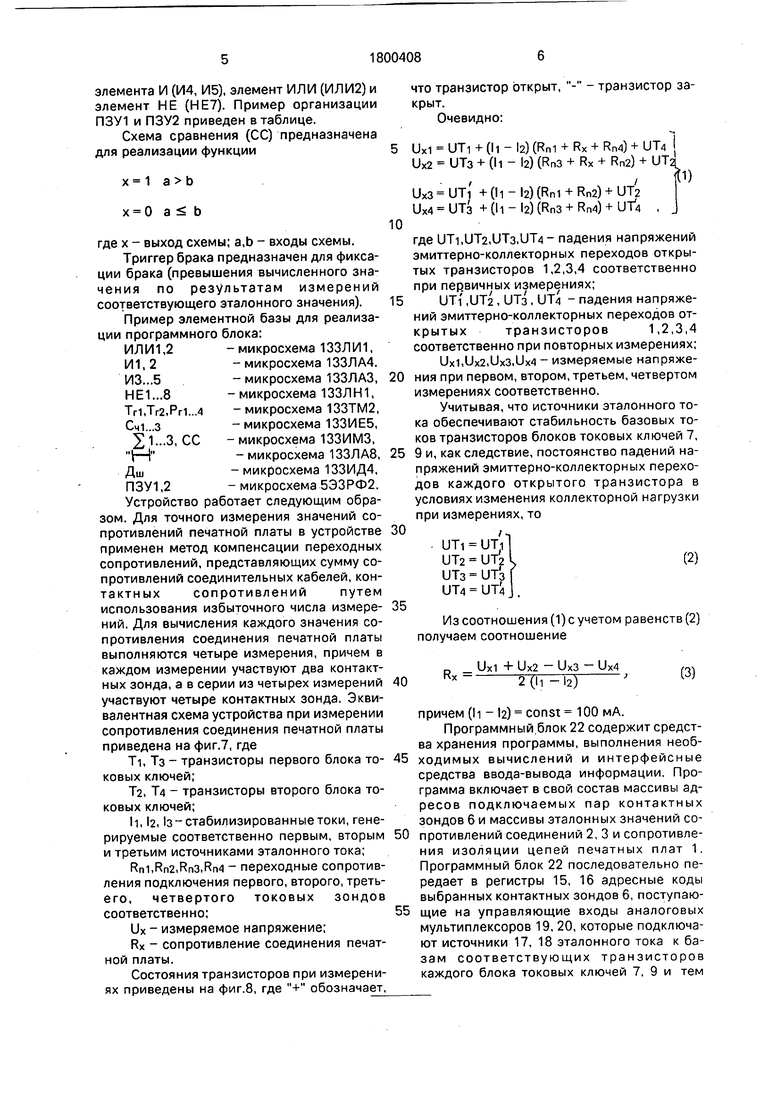

Устройство работает следующим образом. Для точного измерения значений сопротивлений печатной платы в устройстве применен метод компенсации переходных сопротивлений, представляющих сумму сопротивлений соединительных кабелей, кон- тактных сопротивлений путем использования избыточного числа измерений. Для вычисления каждого значения сопротивления соединения печатной платы выполняются четыре измерения, причем в каждом измерении участвуют два контактных зонда, а в серии из четырех измерений участвуют четыре контактных зонда. Эквивалентная схема устройства при измерении сопротивления соединения печатной платы приведена на фиг.7, где

Ti, Тз - транзисторы первого блока токовых ключей;

Та, Тд - транзисторы второго блока токовых ключей;

И, 2, з-стабилизированныетоки, генерируемые соответственно первым, вторым и третьим источниками эталонного тока;

Rni,Rn2,Rn3,Rn4 - переходные сопротивления подключения первого, второго, третьего, четвертого токовых зондов соответственно;

DX - измеряемое напряжение;

Rx - сопротивление соединения печатной платы.

Состояния транзисторов при измерениях приведены на фиг.8, где + обозначает,

что транзистор открыт, - - транзистор закрыт.

Очевидно:

Uxi UTi + (И - I2) (Rni + Rx + Rn4) + UT4 I

Ux2 UT3 + (И - l2) (Rn3 + Rx + Rn2) + UT2

,/ fl1)

Ux3 UTi + (11 - l2) (Rni + Rn2) + UT2 Ux4 - UT3 + (11 - l2) (Rn3 + Rn4) + UT4 ,

где UTi,UT2,UT3,UT4- падения напряжений эмиттерно-коллекторных переходов открытых транзисторов 1,2,3,4 соответственно при первичных измерениях;

UTi ,UT2, UTs , UT4 - падения напряжений эмиттерно-коллекторных переходов открытыхтранзисторов 1,2,3,4 соответственно при повторных измерениях;

Uxl,UX2,Ux3,Ux4 - измеряемые напряжения при первом, втором, третьем, четвертом измерениях соответственно.

Учитывая, что источники эталонного тока обеспечивают стабильность базовых токов транзисторов блоков токовых ключей 7, 9 и, как следствие, постоянство падений напряжений эмиттерно-коллекторных переходов каждого открытого транзистора в условиях изменения коллекторной нагрузки при измерениях, то

(2)

35

Из соотношения (1) с учетом равенств (2) получаем соотношение

40

D Uxi + UX2 - Ux3 - UX4n. Rx-----2 (И - I2)--- (3)

причем (li - I2) const 100 мА.

Программный.блок 22 содержит средства хранения программы, выполнения необходимых вычислений и интерфейсные средства ввода-вывода информации. Программа включает в свой состав массивы адресов подключаемых пар контактных зондов 6 и массивы эталонных значений сопротивлении соединений 2, 3 и сопротивления изоляции цепей печатных плат 1. Программный блок 22 последовательно передает в регистры 15, 16 адресные коды выбранных контактных зондов 6, поступающие на управляющие входы аналоговых мультиплексоров 19, 20, которые подключают источники 17, 18 эталонного тока к базам соответствующих транзисторов каждого блока токовых ключей 7, 9 и тем

самым открывают их. В этом случае ток источника 11 эталонного тока, протекая через открытый транзистор блока токовых ключей 7, контактный зонд 6 контактного модуля 4, печатную плату 1, контактный зонд 6 кон- тактного модуля 5, открытый транзистор блока токовых ключей 9 на общую шину питания и в источники 17, 18 эталонного тока через базы открытых транзисторов блоков токовых ключей 7, 9 и мультиплексо- ры 19, 20 соответственно создает падение напряжения, которое поступает на высоко- омный вход измерителя 12. Программный блок 22 через определенный интервал времени, достаточный для окончания переход- ных процессов, считывает результат измерения из измерителя 12. После каждых четырех измерений программный блок 22 проводит вычисление по формуле (3) значения сопротивления контролируемого соеди- нения 2, 3 печатной платы 1 и сравнение значения вычисленного сопротивления с соответствующим эталонным значением В (табл.). В случае превышения значения сопротивления соответствующего эталонного значения программный блок 22 регистрирует соответствующие номера цепей и адреса контактных зондов 6. При контроле сопротивлений изоляции электрических цепей печатной платы в устройстве применен метод, основанный на измерении тока, протекающего через контролируемое сопротивление. Для исключения влияния паразитных токов на результаты измерения в устройстве применен метод компенсации, для чего измере- ния сопротивлений изоляции электрических цепей проводятся при перемене полярности испытательного напряжения. Для вычисления каждого значения сопротивления изоляции электрической цепи печатной пла- ты выполняются два измерения.

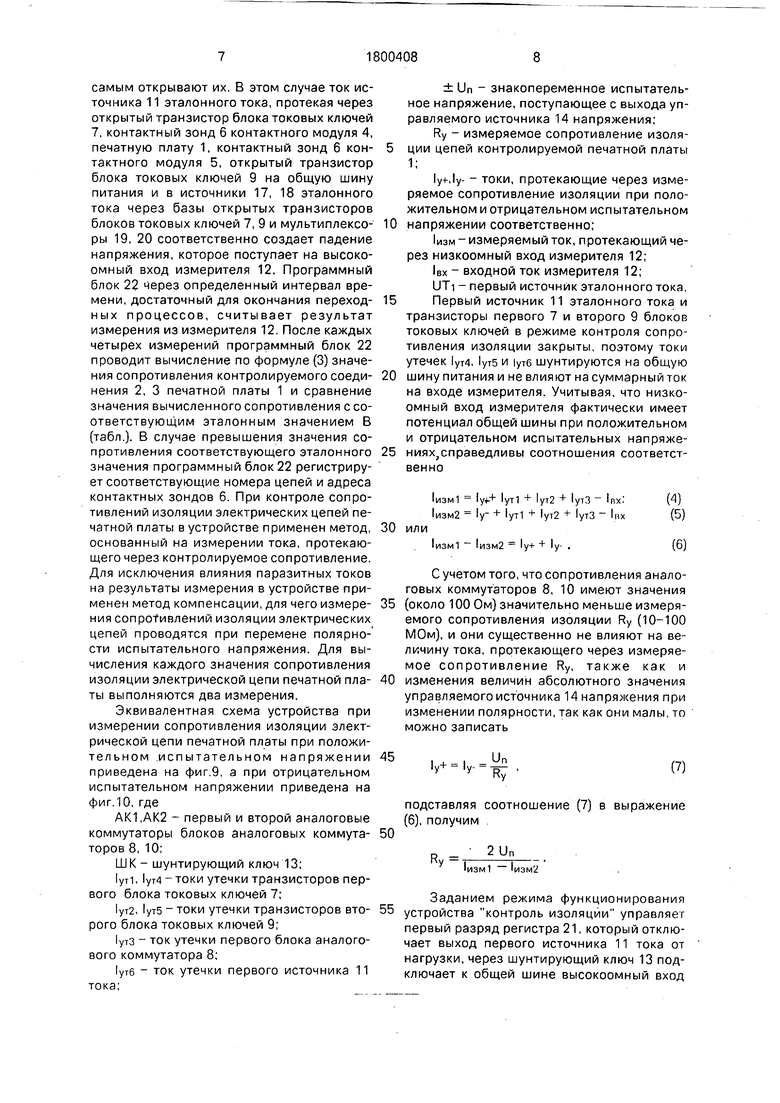

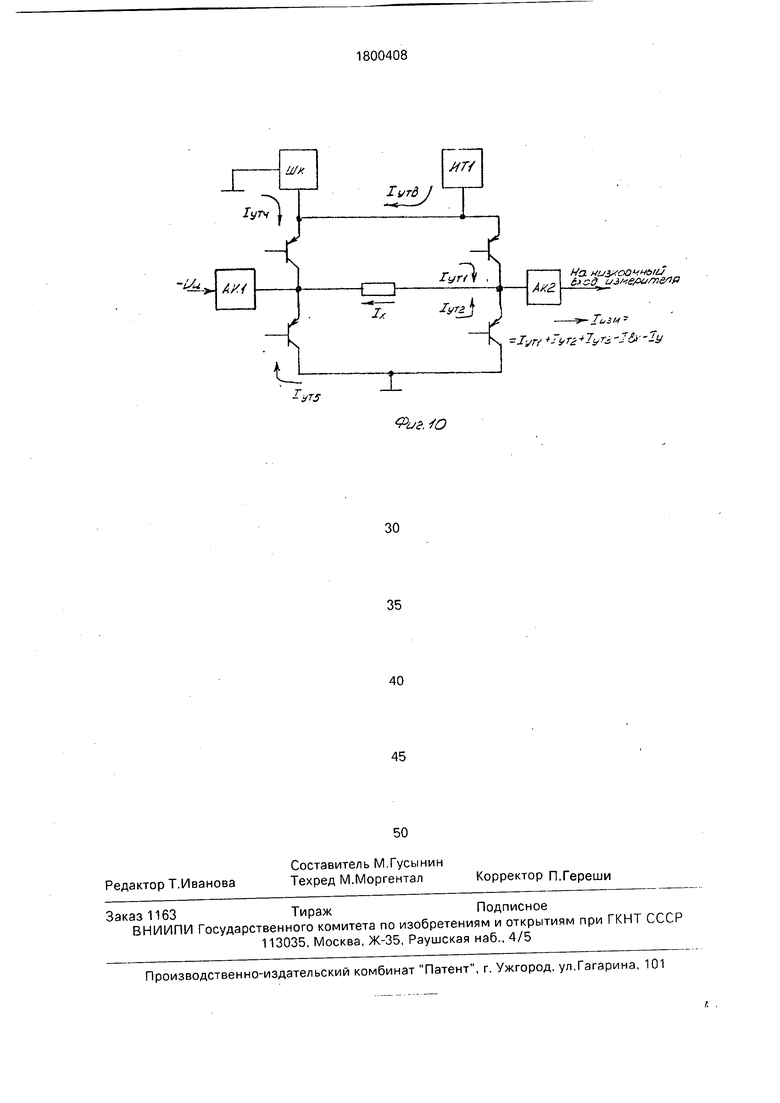

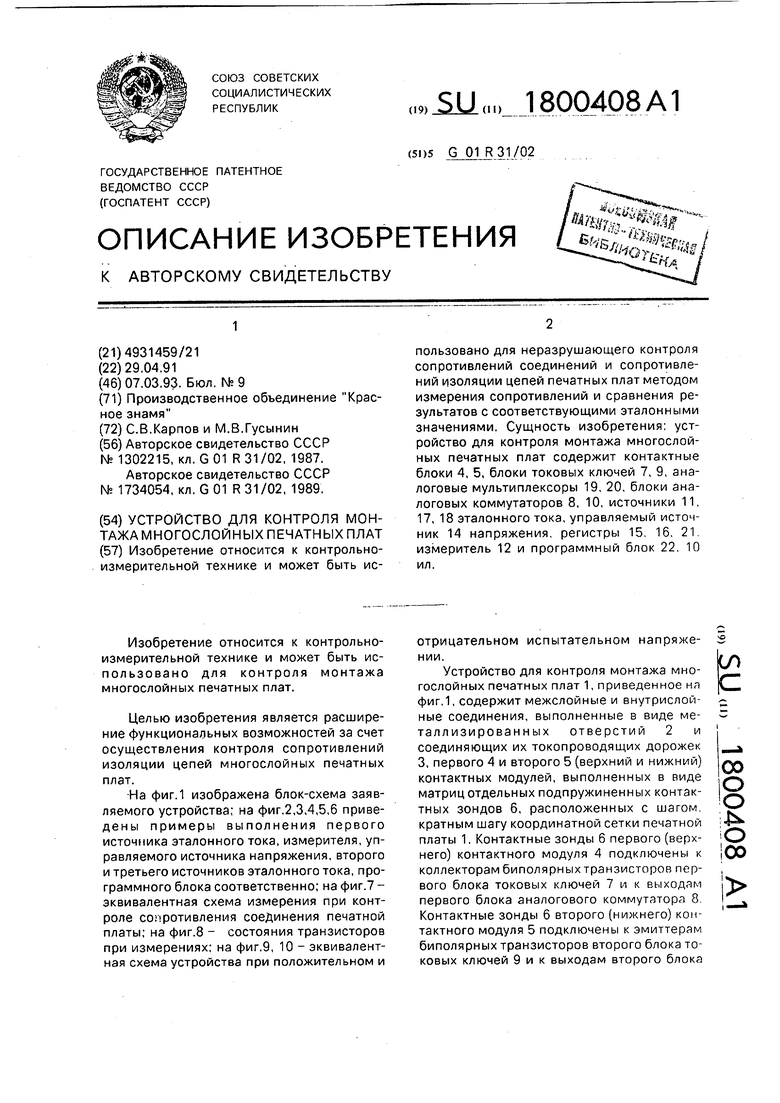

Эквивалентная схема устройства при измерении сопротивления изоляции электрической цепи печатной платы при положительном .испытательном напряжении приведена на фиг.9, а при отрицательном испытательном напряжении приведена на фиг. 10, где

АК1.АК2 - первый и второй аналоговые коммутаторы блоков аналоговых коммута- торов 8, 10;

Ш К - шунтирующий ключ 13;

1ут1, 1ут4 - токи утечки транзисторов первого блока токовых ключей 7;

1ут2, 1ут5 - токи утечки транзисторов вто- рого блока токовых ключей 9;

1Утз - ток утечки первого блока аналогового коммутатора 8;

1Утб - ток утечки первого источника 11 тока;

± Un - знакопеременное испытательное напряжение, поступающее с выхода управляемого источника 14 напряжения;

Ry - измеряемое сопротивление изоляции цепей контролируемой печатной платы 1;

ly+,ly- - токи, протекающие через измеряемое сопротивление изоляции при положительном и отрицательном испытательном напряжении соответственно;

изм - измеряемый ток, протекающий через низкоомный вход измерителя 12;

1Вх - входной ток измерителя 12;

UTi - первый источник эталонного тока.

Первый источник 11 эталонного тока и транзисторы первого 7 и второго 9 блоков токовых ключей в режиме контроля сопротивления изоляции закрыты, поэтому токи утечек 1уТ4, 1ут5 и |утб шунтируются на общую шину питания и не влияют на суммарный ток на входе измерителя. Учитывая, что низкоомный вход измерителя фактически имеет потенциал общей шины при положительном и отрицательном испытательных напряже- ниях справедливы соотношения соответственно

1изм1 lyf.+ 1уТ1 + Ут2 + 1утЗ - Inx:(4)

1изм2 ly- + 1ут1 + 1ут2 + 1утЗ Inx(5)

1изм1 1изм2 ly+ + ly- .(6)

ИЛИ

С учетом того, что сопротивления аналоговых коммутаторов 8, 10 имеют значения (около 100 Ом) значительно меньше измеряемого сопротивления изоляции Ry (10-100 МОм), и они существенно не влияют на величину тока, протекающего через измеряемое сопротивление Ry, также как и изменения величин абсолютного значения управляемого источника 14 напряжения при изменении полярности, так как они малы, то можно записать

Un

Rv

(7)

подставляя соотношение (7) в выражение (6), получим

Rv

2Un

1изм1 - 1изм2

Заданием режима функционирования устройства контроль изоляции управляет первый разряд регистра 21, который отключает выход первого источника 11 тока от нагрузки, через шунтирующий ключ 13 подключает к общей шине высокоомный вход

измерителя 12 и вход первого блока токовых ключей 7, отключает выходы аналоговых мультиплексоров 19, 20 от управляющих входов блоков токовых ключей 7, 9 снятием стробирующего сигнала с входов аналоговых мультиплексоров 19, 20.

Изменением полярности управляемого источника 14 напряжений управляет другой разряд регистра 21. В режиме контроля изоляции адреса выбранных контактных зондов 6 поступают с выходов регистров 15, 16 на входы блоков аналоговых коммутаторов 8, 10. В этом случае напряжение с выхода управляемого источника 14 напряжения через, второй блок аналоговых коммутаторов 10, контактный зонд 6 контактного модуля 5, подключенного к первой цепи, сопротивление изоляции между цепями, зондом б контактного модуля 4, подключенного к второй цепи через первый блок аналоговых коммутаторов 8, создает ток, поступающий на низкоомный вход измерителя 12. Программный блок 22 через определенный интервал времени, достаточный для окончания переходных процессов, считывает результат измерения из измерителя 12, После каждых двух измерений программный блок 22 производит вычисление по формуле (8) значения сопротивления изоляции цепей контролируемой печатной платы 1 и сравнение вычисленного значения с соответствующим эталонным значением С (табл.). В случаях превышения эталонного значения вычисленного значения сопротивления изоляции программный блок 22 регистрирует соответствующие номера цепей и адреса контактных зондов 6.

Малая величина испытательного напряжения (+15В) позволяет осуществлять конт- роль изоляции электрических цепей практически для любой плотности монтажа печатной платы в соответствии с требованиями.

Предлагаемое устройство обеспечивает контроль сопротивления изоляции цепей практически по любому алгоритму, как по медленному алгоритму каждая цепь с каждой, так и по более быстрому каждая цепь со всеми остальными, а также по самому быстрому действующему алгоритму, при котором число циклов контроля равно двоичному логарифму от числа контролируемых цепей. Так, в случае необходимости реализации алгоритма каждая цепь со всеми остальными первый блок аналогового коммутатора 8 выполняется на аналоговых мультиплексорах. При реализации алгоритма повышенного быстродействия первый блок аналогового коммутатора 8 следует выполнять на аналоговых ключах. Второй блок

аналогового коммутатора 10 в этих случаях выполняется на аналоговых ключах. Выполнение блоков аналоговых коммутаторов на аналоговых ключах обеспечивает подключение одновременно нескольких зондов и измерение сопротивления изоляции между двумя массивами цепей.

Следует заметить, что реализацией вус- тройстве алгоритма каждая цепь со всеми

0 остальными обеспечивается наибольшая точность измерения сопротивления изоляции цепей, При реализации более быстродействующих алгоритмов группового подключения цепей по причине увеличения

5 суммы токов утечки точность измерения сопротивлений изоляции ниже.

Заявляемое устройство обеспечивает расширение функциональных возможностей за счет осуществления контроля сопро0 тивления изоляции цепей печатных плат. Прототип не обеспечивает такой функции.

В заявляемом устройстве применение шунтирующего ключа и управляемого источника напряжения позволяет компенсиро5 вать токи утечки биполярных транзисторов блоков токовых ключей и получить высокий уровень контроля сопротивлений изоляции цепей.

Возможность контроля сопротивления

0 изоляции цепей существенно расширяет область применения заявляемого устройства и позволяет использовать его для 100%-но- го контроля печатных плат.

Экспериментальные исследования за5 являемого устройства для контроля монтажа многослойных печатных плат на 2280 точек контактирования, показали его высокую чувствительность контроля соединений (произведение испытательного тока на ми0 нимальный уровень контроля) до 0,01 мВ (100 мА х 0,001 Ом) по сравнению с отечественными и зарубежными аналогами, имеющими чувствительность контроля не лучше 10 мВ (10 мА х 1 Ом) в сочетании с достаточ5 но высоким уровнем контроля изоляции электрических цепей (100 МОм) при низком уровне испытательного напряжения +5 В (или + 15 В). Известные зарубежные аналоги имеют уровень контроля 5 МОм при испыта0 тельном напряжении 40 В или 2 МОм при испытательном напряжении 10 В.

Заявляемое устройство обеспечивает , стабильность технических характеристик при увеличении числа точек контактирова5 ния, принадлежащих одной цепи, до 1000, Формула изобретения Устройство для контроля монтажа многослойных печатных плат, содержащее программный блок, измеритель, первый, второй и третий источники эталонного тока.

первый и второй регистры, первый и второй блоки контактных модулей с электрически изолированными зондами, первый и второй аналоговые мультиплексоры, первый и второй блоки токовых ключей, выполненные на биполярных транзисторах, базы которых образуют соответствующие управляющие входы, эмиттеры транзисторов первого блока токовых ключей соединены между собой и образуют вход этого блока, а коллег торы этих транзисторов образуют соответствующие выходы первого блока токовых ключей, коллекторы транзисторов второго блока токовых ключей соединены между собой и образуют выход этого блока, а эмиттеры этих транзисторов образуют соответствующие входы второго блока токовых ключей, входы первого и второго регистров соединены с выходной информационной шиной программного блока, выход первого источника эталонного тока соединен с первым входом измерителя и с входом первого блока токовых ключей, выходы которого соединены с токовыми зондами первого блока контактных модулей, а токовые зонды второго блока контактных модулей соединены с входами второго блока токовых ключей, второй и третий источники эталонного тока подключены к соответствующим входам первого и второго аналоговых муль- типлексоров, второй вход измерителя соединен с выходом второго блока токовых ключей и с общей шиной питания, выход измерителя соединен с входной информационной шиной программного блока, первая группа выходов первого и второго регистров соединена с адресными входами соответственно первого и второго аналоговых мультиплексоров, отличающееся тем, что, с целью расширения функциональных возможностей, в устройство введены третий регистр, два блока аналоговых коммутаторов, шунтирующий ключ, управляемый источник напряжения, вход третьего регистра соединен с выходной информационной шиной программного блока, первый выход третьего регистра соединен с управляющими входами шунтирующего ключа, первого источника эталонного тока, измерителя и с входами разрешения выбора первого и второго аналоговых мультиплексоров, второй выход третьего регистра соединен с входом управляемого источника напряжения, адресные входы первого и второго блоков аналоговых коммутаторов соединены с второй группой выходов первого и второго регистров соответственно, выходы первого и второго блоков аналоговых коммутаторов соединены с токовыми зондами первого и второго блоков контактных модулей соответственно, вход первого блока аналогового коммутатора соединен с третьим входом измерителя, вход второго блока аналогового коммутатора соединен с выходом управляемого источника напряжения, вход шунтирующего ключа соединен с общей шиной питания, выход шунтирующего ключа подключен к входу первого блока токовых ключей.

to/

со о «т о о

00

Фиг.$

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля соединений многослойных печатных плат | 1989 |

|

SU1734054A1 |

| Устройство для контроля межслойных соединений печатных плат | 1986 |

|

SU1323987A1 |

| Устройство для контроля металлизированных переходов печатной платы | 1985 |

|

SU1308955A1 |

| УСТРОЙСТВО ДЛЯ ПАРАМЕТРИЧЕСКОГО КОНТРОЛЯ МНОГОСЛОЙНЫХ ПЕЧАТНЫХ ПЛАТ | 2003 |

|

RU2256187C1 |

| Автоматическое устройство для проверки качества металлизации отверстий печатных плат | 1977 |

|

SU729498A1 |

| Устройство для контроля печатных плат | 1987 |

|

SU1510112A1 |

| Устройство для проверки качества металлизации отверстий печатных плат | 1986 |

|

SU1413557A1 |

| Устройство для контроля межслойных переходов печатной платы | 1980 |

|

SU947793A1 |

| Устройство для контроля металлизации отверстий в печатных платах | 1975 |

|

SU634290A1 |

| Устройство для контроля монтажа | 1986 |

|

SU1449942A1 |

Изобретение относится к контрольно- измерительной технике и может быть использовано для неразрушающего контроля сопротивлений соединений и сопротивлений изоляции цепей печатных плат методом измерения сопротивлений и сравнения результатов с соответствующими эталонными значениями, Сущность изобретения: устройство для контроля монтажа многослойных печатных плат содержит контактные блоки 4, 5, блоки токовых ключей 7, 9, аналоговые мультиплексоры 19, 20, блоки аналоговых коммутаторов 8, 10, источники 11, 17, 18 эталонного тока, управляемый источник 14 напряжения, регистры 15, 16, 21. измеритель 12 и программный блок 22. 10 ил.

U-

1

.rl .Г

АТУ

Фиг.$

Фиг. to

| Коммутационная система для испытательного оборудования | 1981 |

|

SU1302215A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля соединений многослойных печатных плат | 1989 |

|

SU1734054A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1993-03-07—Публикация

1991-04-29—Подача