СО

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения абонентов с каналом связи | 1987 |

|

SU1432537A1 |

| Многоканальное устройство для подключения абонентов к общей магистрали | 1986 |

|

SU1383352A1 |

| Многоканальное устройство для подключения абонентов к общей магистрали | 1990 |

|

SU1815637A1 |

| Устройство для сопряжения абонента с линией связи локальной сети ЭВМ | 1989 |

|

SU1645962A1 |

| Многоканальное устройство приоритета | 1984 |

|

SU1226459A1 |

| Многоканальное устройство для подключения абонентов к общему ресурсу | 1990 |

|

SU1837307A1 |

| Многоканальное устройство приоритета | 1988 |

|

SU1501057A1 |

| Устройство для подключения источников информации к общей магистрали | 1986 |

|

SU1444797A1 |

| Устройство для подключения абонентов к общей магистрали | 1987 |

|

SU1416986A1 |

| Система обмена данными в вычислительной сети | 1991 |

|

SU1807493A1 |

Изобретение относится к вычислительной технике и может быть использовано для управления доступом к локальному каналу микропроцессора абонента, процедура захвата (освобождения) .канала передачи у которого отличается от соответствующей процедуры микропроцессора. Целью изобретения является упрощение устройства. Устройство содержит элемент ИСКЛЮЧАЮЩЕЕ ИЛИ. элемент задержки, элемент И с тремя состояниями, два элемента НЕ и четыре триггера. Упрощение устройства по сравнению с прототипом обеспечивается за счет сокращения числа используемых элементов и количества соединений между ними. 2 ил.

Изобретение относится к вычислительной технике и может быть использовано для управления доступом ,к локальному каналу микропроцессора.

Целью изобретения является упрощение устройства управления доступом к локальному каналу микропроцессора. выполняющего процедуру захвата активного абонента для безусловного отключения этого абонента от общего (с источником запрос) канала передачи (например, от локального канала микропроцессора).

Поставленная цель достигается тем. что в известное устройство, содержащее три триггера, элемент НЕ и элемент И г, тремя состояниями, выход которого соединен с входом-выходом захвата устройства, выход первого триггера является выходом подтверждения захвата устройства, вход сброса устройства соединен с. входом сброса второго триггера, допплмш ш.но введены

четвертый триггер, второй элемент НЕ, элемент задержки и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ. выход которого через второй элемент НЕ соединен с единичным входом второго триггера, выход которого соединен с нулевым входом третьего триггера, инверсный выход которого соединен с информационным входом третьего триггера, синхровхо- дом второго триггера, входами элемента И с тремя состояниями и входом сброса четвертого триггера, выход которого соединен с входом сброса первого триггера, синхров- ход и информационный вход которого соединены соответственно с выходом элемента И с тремя состояниями и шиной логической единицы устройства, вход синхронизации устройства соединен с синхровходом четвертого триггера и через первый элемент НЕ - с синхровходом третьего триггера, вход запроса устройства соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и с

00

о

VI

4 Ю

входом элемента задержки, выход которого соединен со вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, вход сброса устройства соединен с информационным входом четвертого триггера, информационный вход второго триггера соединен с шиной логического нуля устройства.

Существенные отличия предлагаемого технического решения заключаются в уменьшении числа элементов и связей меж- ду ними, что дает новый положительный эффект. Устройства, идентичные предлагаемому, в патентной и научно-технической литературе не .обнаружены, что позволяет сделать вывод о том, что оно об- ладает новизной и существенными отличиями.

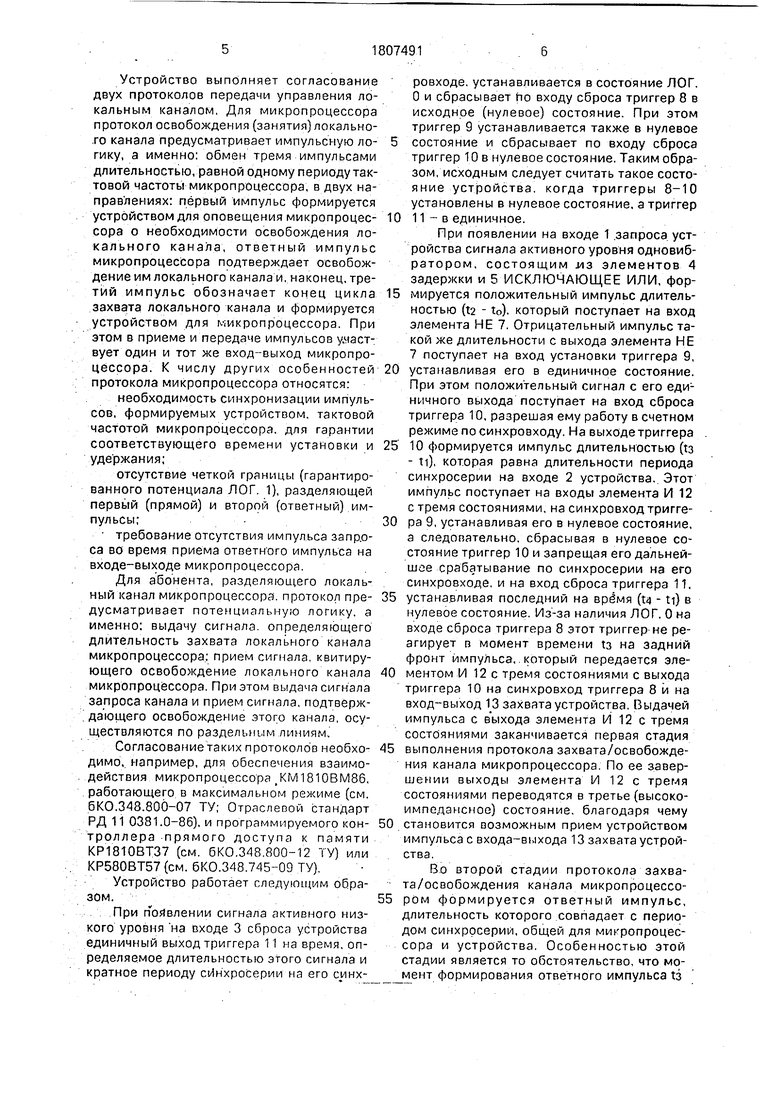

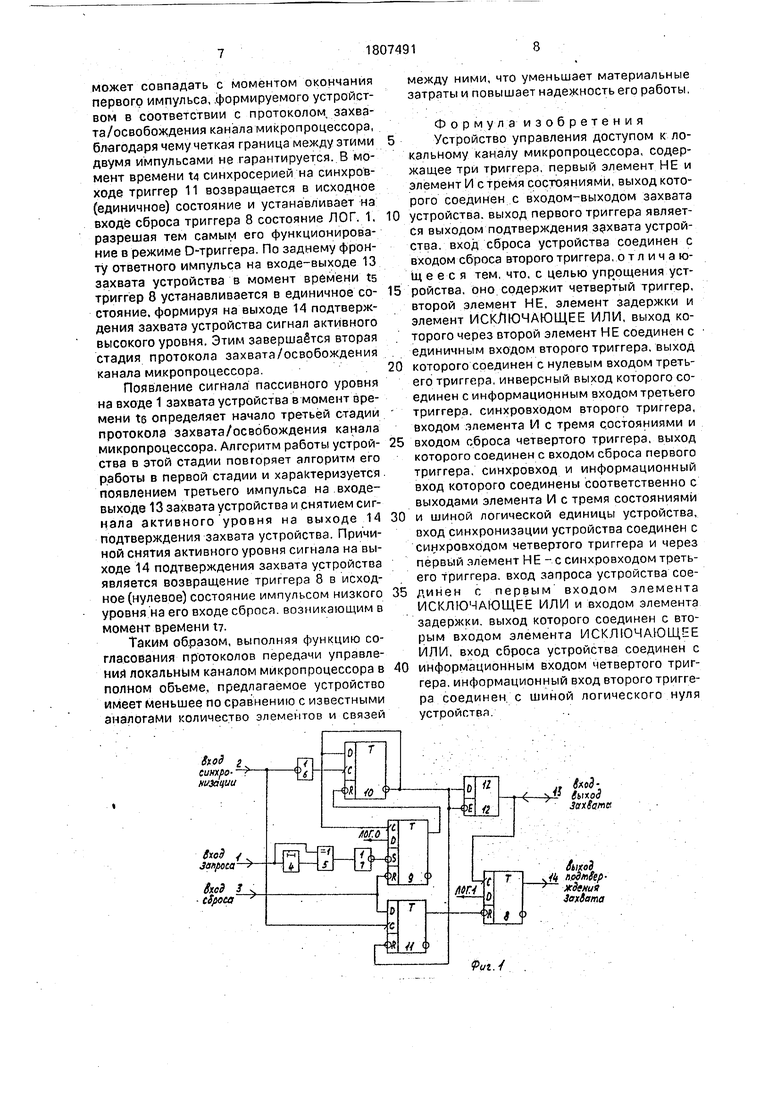

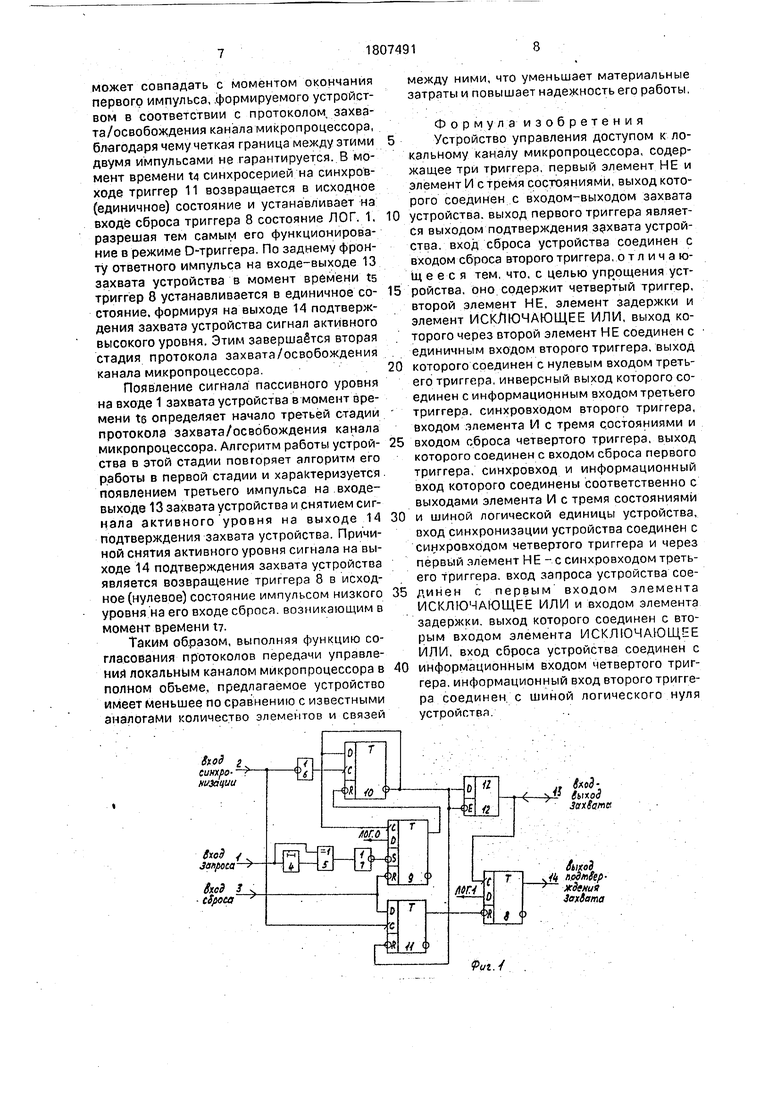

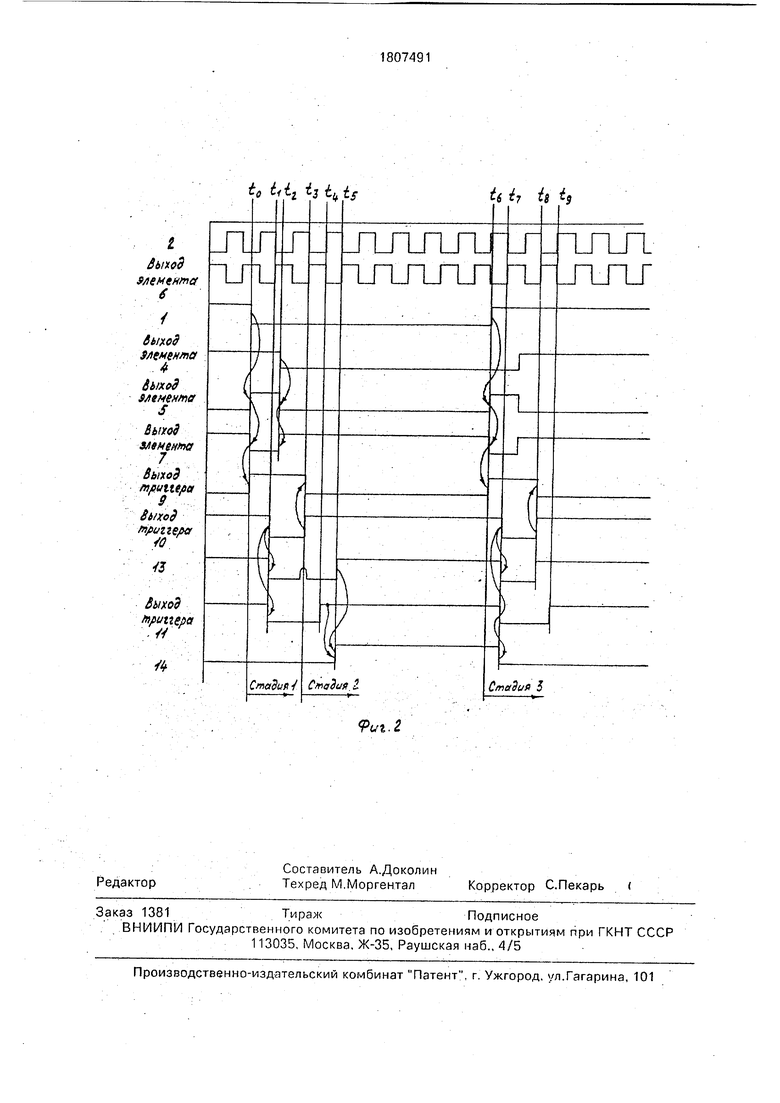

На фиг. 1 представлена электрическая принципиальная схема устройства; на фиг. 2 - временная диаграмма работы устройст-

ва.....

Устройство управления доступом к локальному каналу микропроцессора содержит вход 1 запроса, вход 2 синхронизации, вход 3 сброса, элемент 4 задержки, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 5, элементы НЕ 6 и 7, триггеры 8-11, элемент И 12 с тремя состояниями, выход которого подключен к входу-выходу 13 захвата устройства и син- хровходу триггера 8, выход которого являет- ся выходом 14 подтверждения захвата устройства, .

Вход 1 запроса устройства предназначен для приема сигнала запроса локального канала микропроцессора от абонента, тре- бугощего доступа к этому каналу. Длительность этого сигнала определяет длительность захвата канала абонентом. Вход 1 запроса устройства подключен к входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 5 и че- рез элемент 4 задержки - к второму входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 5, выход которого через элемент НЕ 7 соединен с единичным входом триггера 9.

Вход 2 Синхронизации устройства, предназначенный для приема серии синхронизирующих импульсов от общего с захватываемым . микропроцессором источника, синхросерии (например, от генератора тактовых импульсов КР1810ГФ84), со- единен с Синхровходом триггера 1 и через элемент НЕ 6 с синхровходом триггера 10.

Вход 3 сброса устройства предназначен для установки триггеров в исходное состояние и соединен с входом сброса триггера 9 и информационным входом триггера 11. Сигнал сброса может поступать от общего с захватываемом микропроцессором источника (например, От генератора КР181ОГФ84,

формирующего синхронизируемый тактовой частотой импульс сброса).

Выход триггера 9 подключен к входу сброса триггера 10, инверсный выход которого подключен к информационному входу триггера 10, синхровходу триггера 9, входам элемента И 12 с тремя состояниями и входу сброса триггера 11. Выход триггера 11 соединен с входом сброса триггера 8, информационный вход которого соединен с шиной логической единицы, а информационный вход триггера 9 соединен с шиной логического нуля.

Элементы задержки и ИСКЛЮЧАЮЩЕЕ ИЛИ устройства в совокупности образуют одновибратор, который формирует импульсы по переднему и заднему фронтам сигнала, поступающего на вход 1 запроса (фиг. 1) устройства. Формирование этих импульсов необходимо для разрешения срабатывания триггеров 9 и 10 (фиг. 1), предназначенных для формирования соответствующих импульсов протокола микропроцессора требуемой длительности и фазы. Длительность импульсов на выходе одновибратора определяется соотношением . . . . .

(D

где т.и длительность импульса, формируемая на выходе элемента 5 (фиг. 1) устройства: : .. . ..:. . . т -длительность периода последовательности синхронизирующих импульсов на синхровходе триггера 10 (фиг. 1).

Вход-выход 13 захвата устройства предназначен для передачи и приема импульсной последовательности, прёдусмот- реннойпротоколом захвата микропроцессора. :

Выход 1.4 подтверждения захвата устройства предназначен для выдачи сигнала, подтверждающего освобождение, локального канала микропроцессором и, следовательно, возможность занятия этого канала абонентом, сформировавшим сигнал запроса на входе 1 (фиг. 1) устройства.

Устройство управления доступом к локальному каналу микропроцессора предназначено дняпереключения микропроцессора в пассивное состояние (состояние захвата) с целью безусловного освобождения его локального канала для другого абонента, использующего этот канал передачи, на время, определяемое длительностью сигнала запроса на Одноименном входе устройства.

Устройство выполняет согласование двух протоколов передачи управления локальным каналом. Для микропроцессора протокол освобождения (занятия) локального канала предусматривает импульсную логику, а именно: обмен тремя импульсами длительностью, равной одному периоду тактовой частоты микропроцессора, в двух направлениях: первый импульс формируется устройством для оповещения микропроцессора о необходимости освобождения локального канала, ответный импульс микропроцессора подтверждает освобождение им локального канала и,наконец,третий импульс обозначает конец цикла захвата локального канала и формируется устройством для микропроцессора. При этом в приеме и передаче импульсов участвует один и тот же вход-выход микропроцессора. К числу других особенностей протокола микропроцессора относятся:

необходимость синхронизации импульсов, формируемых устройством, тактовой частотой микропроцессора, для гарантии соответствующего времени установки и удержания;

отсутствие четкой границы (гарантированного потенциала ЛОГ. 1), разделяющей первый (прямой) и второй (ответный) импульсы;

требование отсутствия импульса запр.о- са во время приема ответного импульса на входе-выходе микропроцессора.

Для абонента, разделяющего локальный канал микропроцессора, протокол предусматривает потенциальную логику, а именно: выдачу сигнала, определяющего длительность захвата локального канала микропроцессора: прием сигнала, квитирующего освобождение локального канала микропроцессора. При этом выдача сигнала запроса канала и прием сигнала, подтверж- . дающего освобождение этого канала, осуществляются по раздельным линиям,

Согласование таких протоколов необходимо,, например, для обеспечения взаимодействия микропроцессора МШОВМЗб, работающего в максимальном режиме (см. 6К0.348.800-07 ТУ; Отраслевой стандарт РД 11 0381.0-86), и программируемого контроллера прямого доступа к памяти КР1810ВТ37 (см. 6К0.348.800-12 ТУ) или КР580ВТ57 (см. 6К0.348.745-09 ТУ).

Устройство работает следующим образом,

При появлении сигнала активного низкого уровня на входе 3 сброса устройства единичный выход триггера 11 на время, определяемое длительностью этого сигнала и кратное периоду сйн хросерии на его синхровходе. устанавливается в состояние ЛОГ. О и сбрасывает по входу сброса триггер 8 в исходное (нулевое) состояние. При этом триггер 9 устанавливается также в нулевое 5 состояние и сбрасывает по входу сброса триггер 10 в нулевое состояние. Таким образом/исходным следует считать такое состояние устройства, когда триггеры 8-10 установлены в нулевое состояние, а триггер

0 11 - в единичное.

При появлении на входе 1 .запроса устройства сигнала активного уровня одновиб- ратором, состоящим .из элементов 4 задержки и 5 ИСКЛЮЧАЮЩЕЕ ИЛИ, фор5 мируется положительный импульс длительностью (т.2 - to), который поступает на вход элемента НЕ 7. Отрицательный импульс такой же длительности с выхода элемента НЕ 7 поступает на вход установки триггера 9,

0 устанавливая его в единичное состояние. При этом положительный сигнал с его единичного выхода поступает на вход сброса триггера 10, разрешая ему работу в счетном режиме по синхровходу. На выходе триггера

5 10 формируется импульс длительностью (ta - ti), которая равна длительности периода синхросерии на входе 2 устройства.. Этот импульс поступает на входы элемента И 12 с тремя состояниями, на синхровход тригге0 ра 9, устанавливая его в нулевое состояние, а следовательно, сбрасывая в нулевое состояние триггер 10 и запрещая его дальнейшее срабатывание по синхросерии на его синхровходе. и на вход сброса триггера 11,

5 устанавливая последний на время ( - ti) в нулевое состояние. Из-за наличия ЛОГ. О на входе сброса триггера 8 этот триггер не реагирует в момент времени t3 на задний фронт импульса,. который передается эле0 ментом И 12 с тремя состояниями с выхода триггера 10 на синхровход триггера 8 и на вход-выход 13 захвата устройства. Выдачей импульса с выхода элемента И 12 с тремя состояниями заканчивается первая стадия

5 выполнения протокола захвата/освобождения канала микропроцессора. По ее завершении выходы элемента И 12 с тремя состояниями переводятся в третье (высоко- импедаысное) состояние, благодаря чему

0 становится возможным прием устройством импульса с входа-выхода 13 захвата устройства.

Во второй стадии протокола захвата/освобождения канала микропроцессо5 ром формируется ответный импульс, длительность которого совпадает с периодом синхросерии, общей для микропроцессора и устройства. Особенностью этой стадии является то обстоятельство, что момент формирования ответного импульса Тз

может совпадать с моментом окончания первого импульса, .формируемого устройством в соответствии с протоколом, захвата/освобождения канала микропроцессора, благодаря чему четкая граница между этими двумя импульсами не гарантируется. В момент времени t4 синхросерией на синхров- ходе триггер 11 возвращается в исходное (единичное) состояние и устанавливает на входе сброса триггера 8 состояние ЛОГ. 1. разрешая тем самым его функционирование в режиме D-триггера. По заднему фронту ответного импульса на входе-выходе 13 захвата устройства в момент времени ts триггер 8 устанавливается в единичное состояние, формируя на выходе 14 подтверждения захвата устройства сигнал активного высокого уровня. Этим завершается вторая стадия протокола захвата/освобождения канала микропроцессора.

Появление сигнала пассивного уровня на входе 1 захвата устройства в момент времени ts определяет начало третьей стадии протокола захвата/освобождения канала микропроцессора. Алгоритм работы устройства в этой стадии повторяет алгоритм его работы в первой стадии и характеризуется появлением третьего импульса на .входе- выходе 13 захвата устройства и снятием сигнала активного уровня на выходе 14 подтверждения захвата устройства. Причиной снятия активного уровня сигнала на выходе 14 подтверждения захвата устройства является возвращение триггера 8 в исходное (нулевое)состояние импульсом низкого уровня на его входе сброса, возникающим в момент времени t.

Таким образом, выполняя функцию согласования протоколов передачи управления локальным каналом микропроцессора в полном объеме, предлагаемое устройство имеет меньшее по сравнению с известными аналогами количество элементов и связей

между ними, что уменьшает материальные затраты и повышает надежность его работы,

Фор мула изобретения

Устройство управления доступом к локальному каналу микропроцессора, содержащее три триггера, первый элемент НЕ и элемент И с тремя состояниями, выход которого соединен с входом-выходом захвата

устройства, выход первого триггера является выходом подтверждения захвата устройства, вход сброса устройства соединен с входом сброса второго триггера, о тли ч a rain e ее я тем, что, с целью упрощения устройства, оно содержит четвертый триггер, второй элемент НЕ, элемент задержки и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого через второй элемент НЕ соединен с

единичным входом второго триггера, выход

которого соединен с нулевым входом третьего триггера, инверсный выход которого соединен с информационным входом третьего

триггера, синхровходом второго триггера, входом элемента И с тремя состояниями и

входом сброса четвертого триггера, выход которого соединен с входом сброса первого триггера, синхровход и информационный вход которого соединены соответственно с выходами элемента И с тремя состояниями

и шиной логической единицы устройства, вход синхронизации устройства соединен с синхровходом четвертого триггера и через первый элемент НЕ-с синхровходом третьего триггера, вход запроса устройства соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и входом элемента задержки, выход которого соединен с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, вход сброса устройства соединен с

информационным входом четвертого триггера, информационный вход второго триггера соединен, с шиной логического нуля устройства...

г

Јыход элемента Ј

St/ito9 ЗМмента

4

9лгмеша

5

Выход злеменьм

Выход трипе fa 3

Выход триггера SO.

Я

ВыхоЪ триггера .«

Фиг. 2

| Ю.Чжен Лю, Г | |||

| Гибсон | |||

| Вальцевой станок для смазки клеем фанер | 1927 |

|

SU8086A1 |

| М.: Радио и связь, 1987, с | |||

| Передвижная комнатная печь | 1922 |

|

SU383A1 |

| Коммутатор без переговорно-вызывных ключей с применением автоматических искателей | 1924 |

|

SU1810A1 |

| Ректификационная тарелка | 1957 |

|

SU110381A1 |

Авторы

Даты

1993-04-07—Публикация

1991-03-19—Подача