4ib СО N9

Сл

СО

Nl

Изобретение относится к вычисли- ельной технике и может быть исполь- Ьовано в локальных вычислительных сетях в качестве устройства для обме- на данными между локальными станциями сети и абонентами (процессорами) высшего уровня каждой локальной станции через канал связи.

Цель изобретения - повьапение на- |цежности за счет оперативного перераспределения функции ведущего абонента.

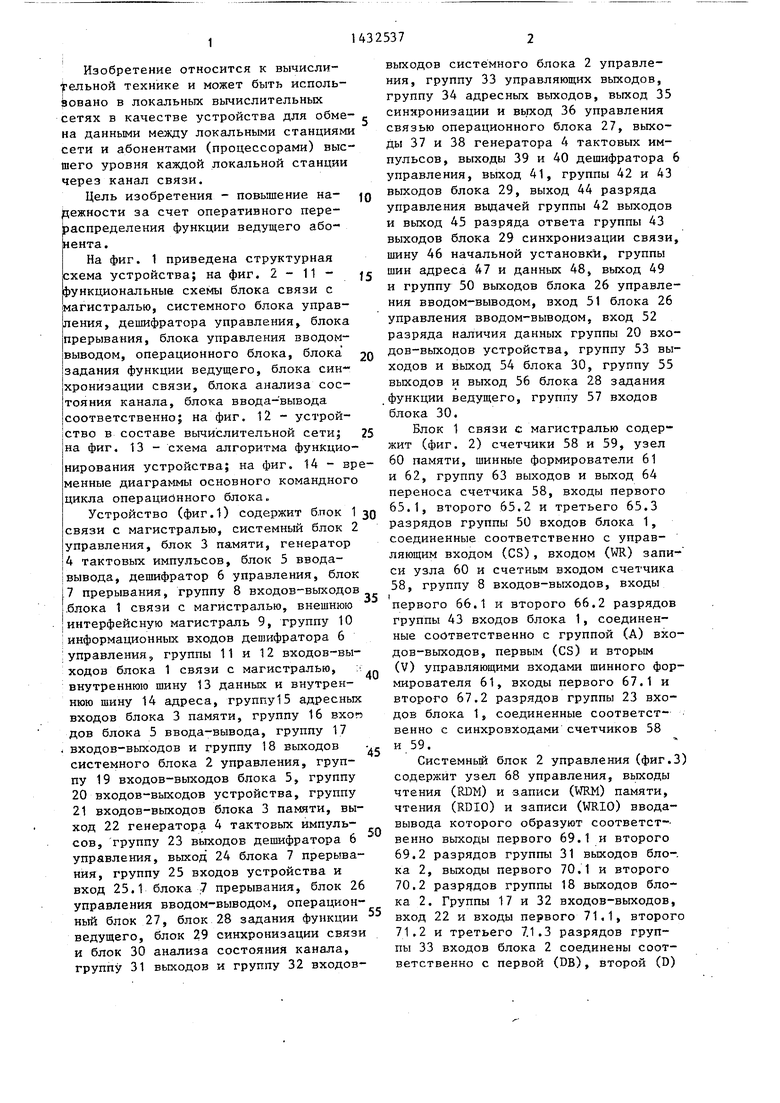

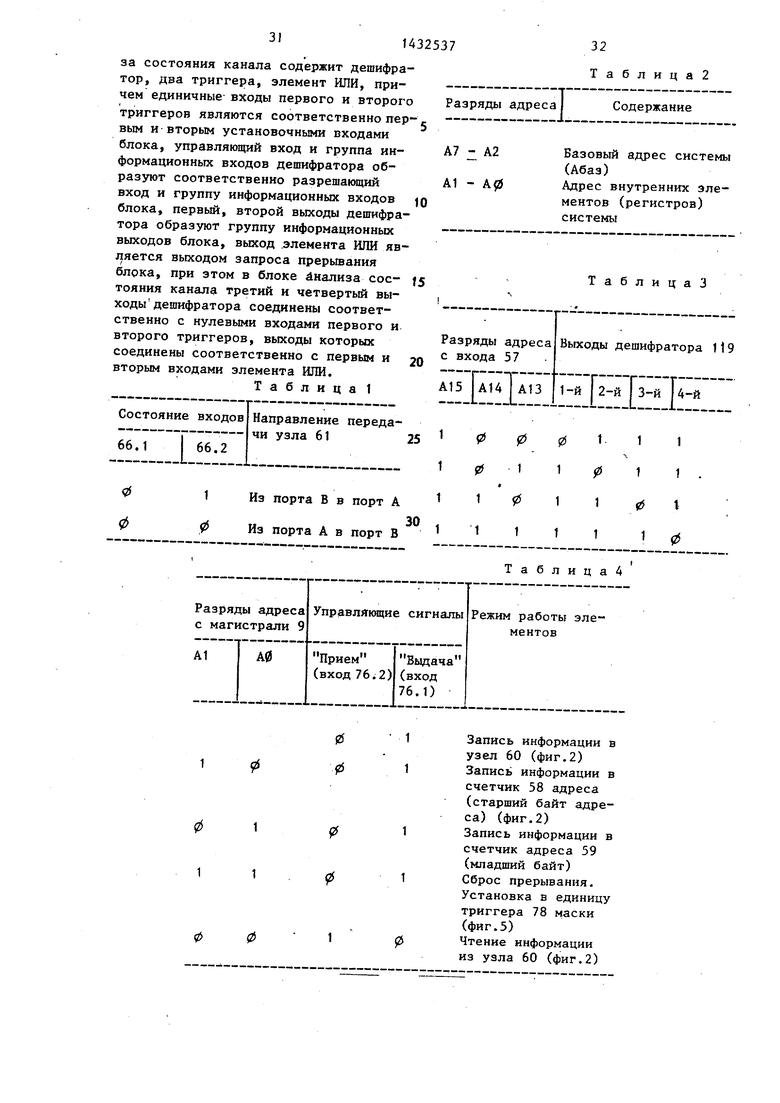

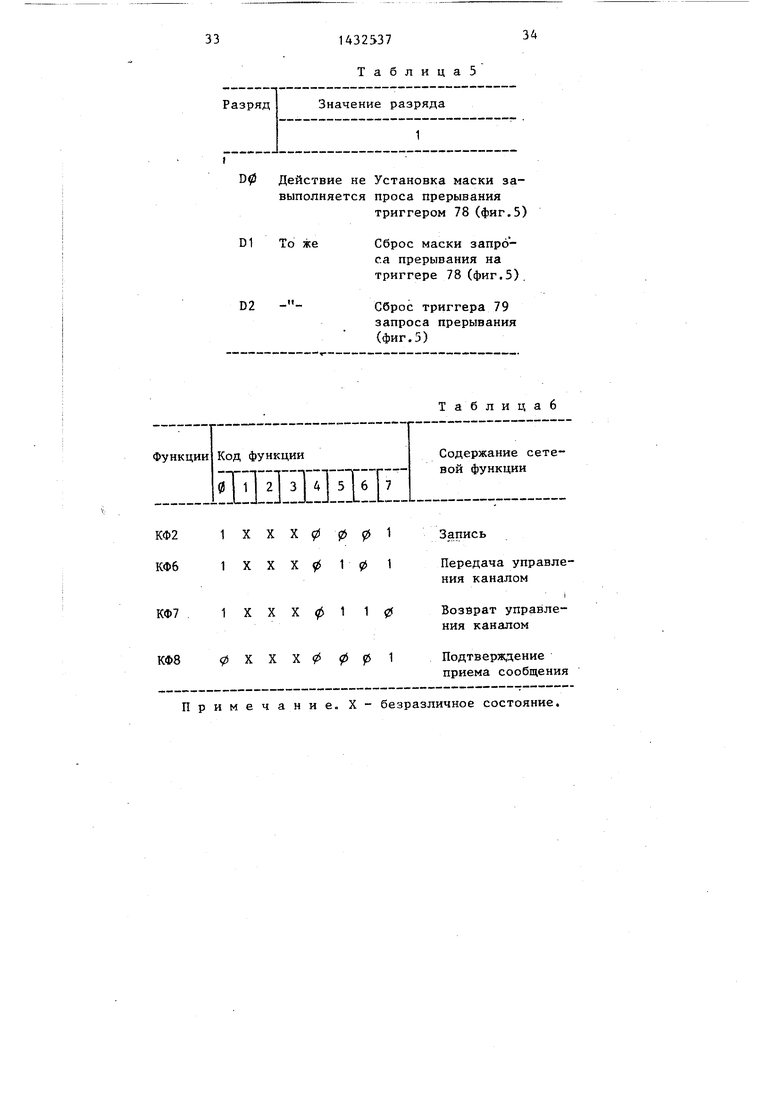

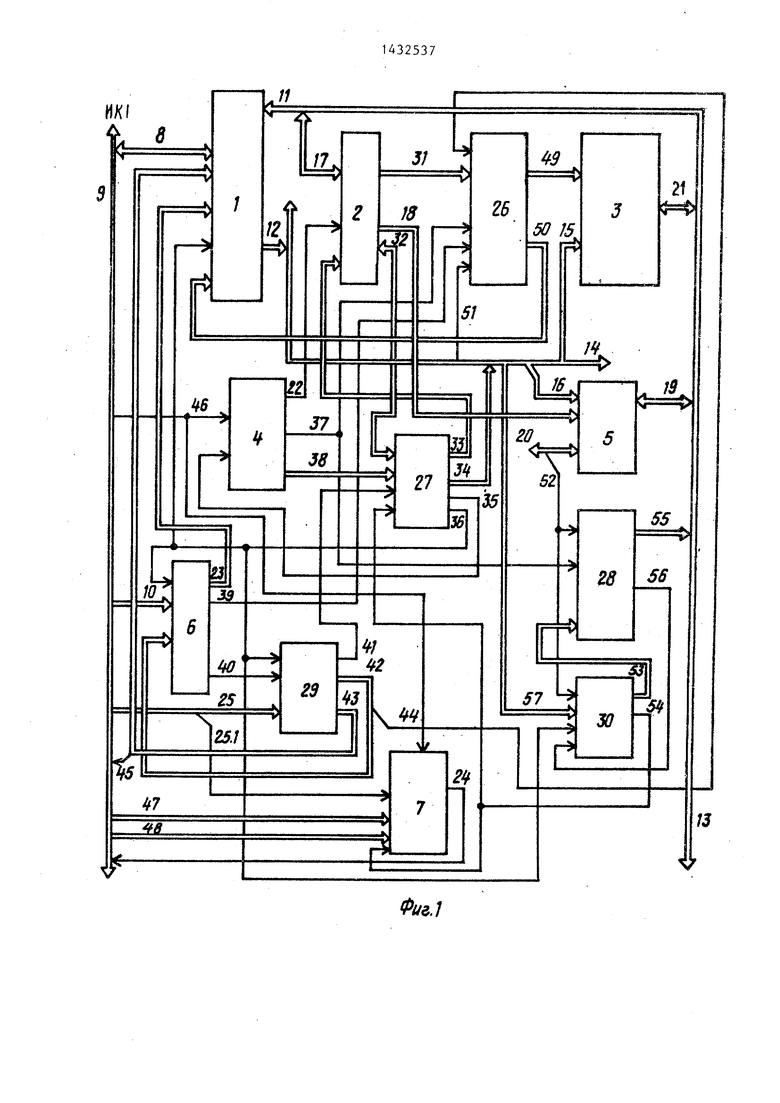

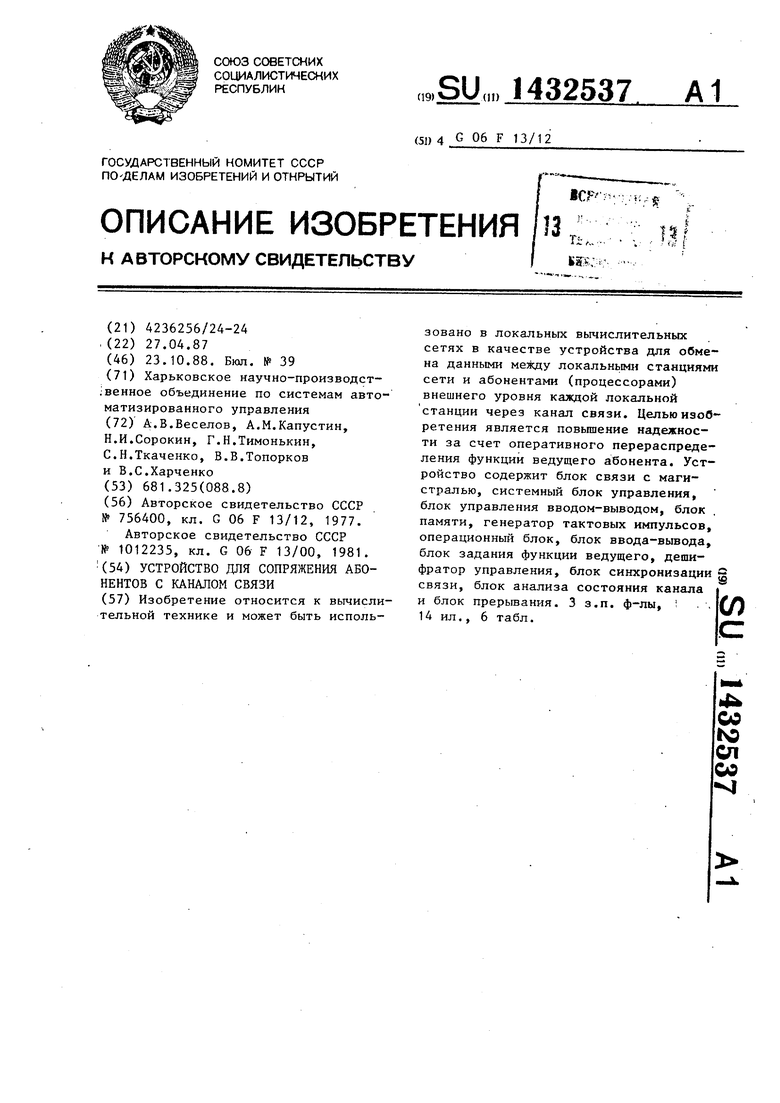

На фиг. 1 приведена структурная схема устройства; на фиг. 2 - 11 - функциональные схемы блока связи с магистралью, системного блока управления, дешифратора управления блока прерывания, блока управления вводом- выводом, операционного блока, блока |задания функции ведущего, блока син- |хронизации связи, блока анализа состояния канала, блока ввода- вывода соответственно; на фиг. 12 - устрой- JCTBO в составе вычислительной сети; |на фиг. 13 - схема алгоритма функцио

нирования устройства; на фиг. 14 - врменные диаграммы основного командного цикла операцибнного блока

Устройства (фиг.1) содержит блок 1 |связи с магистралью, системный блок 2 1управления, блок 3 памяти, генератор 14 тактовых импульсов, блок 5 ввода- 1 вывода, дешифратор 6 управления, блок 17 прерывания, группу 8 входов-выходов .блока 1 связи с магистралью, внешнюю :интерфейсную магистраль 9, группу 10 ;информационных входов дешифратора 6 :управления, группы 11 и 12 входов-выходов блока 1 связи с магистралью, : внутреннюю шину 13 данных и внутреннюю шину 14 адреса, группу15 адресных входов блока 3 памяти, группу 16 дов блока 5 ввода-вывода, группу 17 i входов-выходов и группу 18 выходов системного блока 2 управления, группу 19 входов-выходов блока 5, группу

20входов-выходов устройства, группу

21входов-выходов блока 3 памяти, выход 22 генератора 4 тактовых импульсов, группу 23 выходов дешифратора 6 управления, выход 24 блока 7 прерывания, группу 25 входов устройства и вход 25.1 блока 7 прерывания, блок 26 управления вводом-выводом, операционный блок 27, блок 28 задания функции ведущего, блок 29 синхронизации связи

и блок 30 анализа состояния канала, группу 31 вькодов и группу 32 входов

,

0

выходов системного блока 2 управления, группу 33 управляющих выходов, группу 34 адресных выходов, выход 35 синхронизации и выход 36 управления связью операционного блока 27, выходы 37 и 38 генератора 4 тактовых импульсов, выходы 39 и 40 дешифратора 6 управления, выход 41, группы 42 и 43 выходов блока 29, выход 44 разряда управления выдачей группы 42 выходов и выход 45 разряда ответа группы 43 выходов блока 29 синхронизации связи, шину 46 начальной установки, группы шин адреса 47 и данных 48, выход 49 и группу 50 выходов блока 26 управления вводом-выводом, вход 51 блока 26 управления вводом-выводом, вход 52 разряда наличия данных группы 20 входов-выходов устройства, группу 53 выходов и выход 54 блока 30, группу 55 выходов и выход 56 блока 28 задания .функции ведущего, группу 57 входов блока 30.

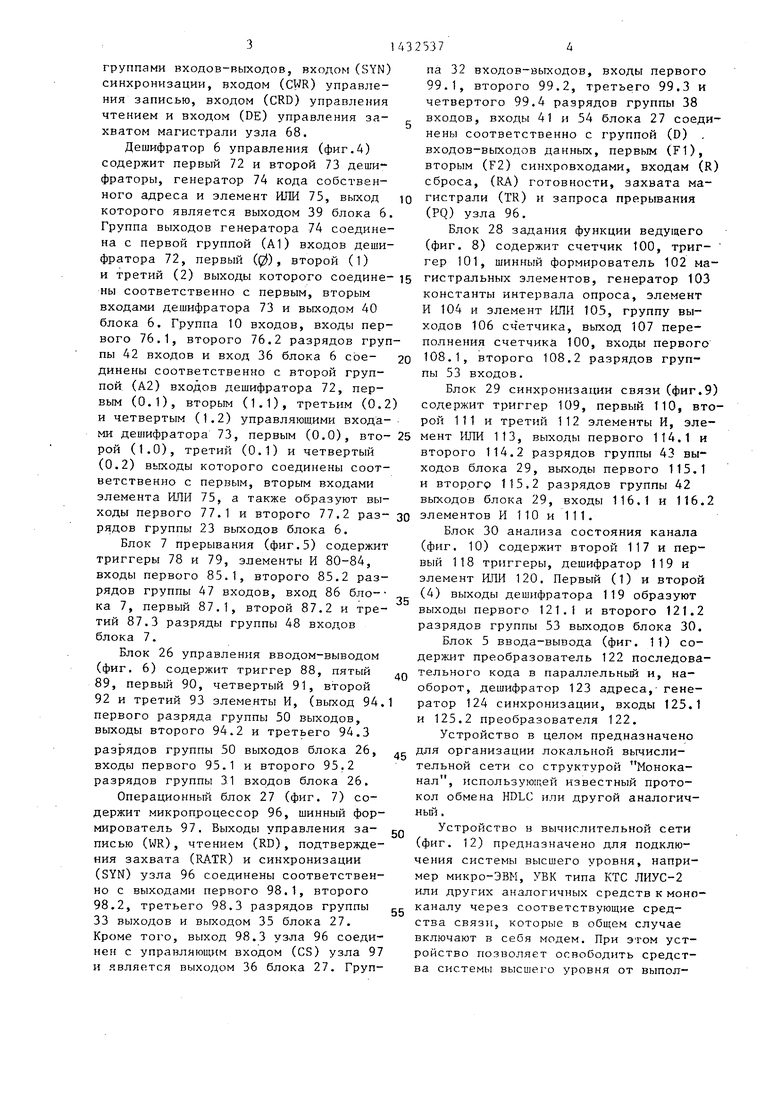

Блок 1 связи с магистралью содержит (фиг. 2) счетчики 58 и 59, узел 60 памяти, шинные формирователи 61 и 62, группу 63 выходов и выход 64 переноса счетчика 58, входы первого 65.1, второго 65.2 и третьего 65.3 разрядов группы 50 входов блока 1, соединенные соответственно с управляющим входом (CS), входом (WR) запи- си узла 60 и счетным входом счетчика 58, группу 8 входов-выходов, входы

первого 66.1 и второго 66.2 разрядов группы 43 входов блока 1, соединенные соответственно с группой (А) входов-выходов, первым (CS) и вторым (V) управляющими входами шинного формирователя 61, входы первого 67.1 и второго 67.2 разрядов группы 23 входов блока 1, соединенные соответственно с синхровходами счетчиков 58 и 59.

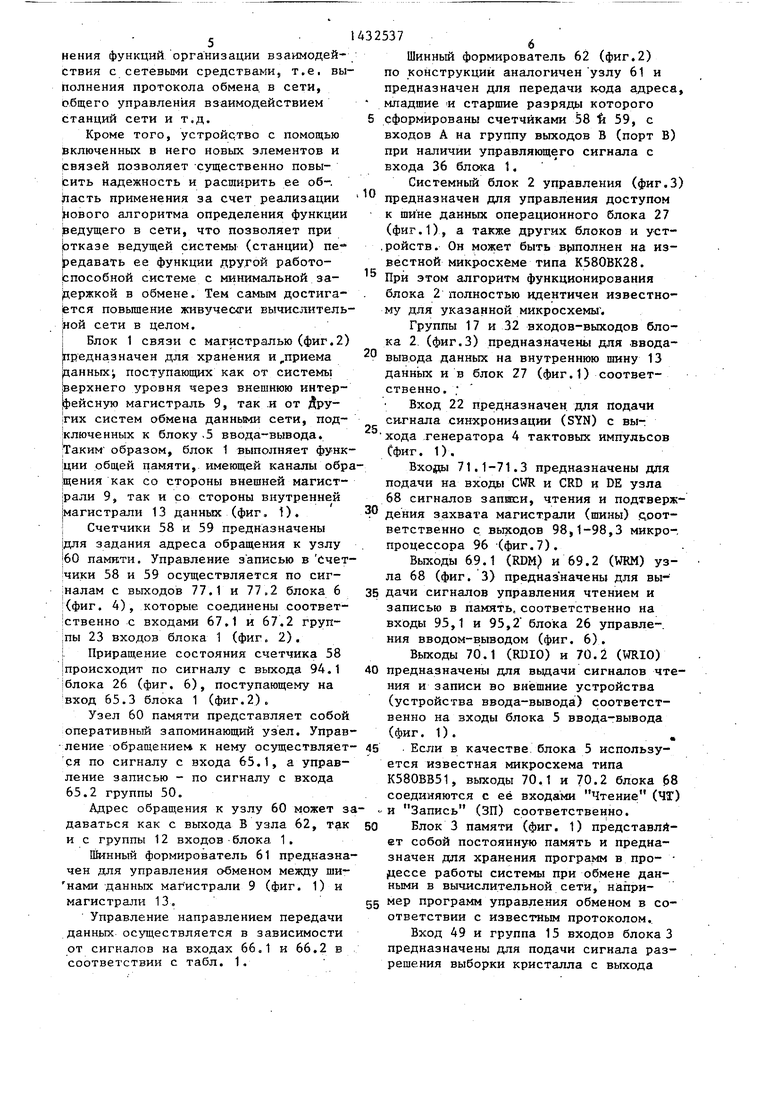

Системньй блок 2 управления (фиг.З) содержит узел 68 управления, выходы чтения (RDM) и записи (WRM) памяти, чтения (RDIO) и записи (WR10) ввода- вывода которого образуют соответст- венно выходы первого 69.1 и второго 69.2 разрядов группы 31 выходов бло-. ка 2, выходы первого 70.1 и второго 70.2 разр5|дов группы 18 выходов блока 2. Группы 17 и 32 входов-выходов, вход 22 и входы первого 71,1, второго 71.2 и третьего 7.1.3 разрядов группы 33 входов блока 2 соединены соответственно с первой (DB), второй (D)

группами входов-выходов, входом (SYN) синхронизации, входом (CWR) управления записью, входом (CRD) управления чтением и входом (DE) управления захватом магистрали узла 68.

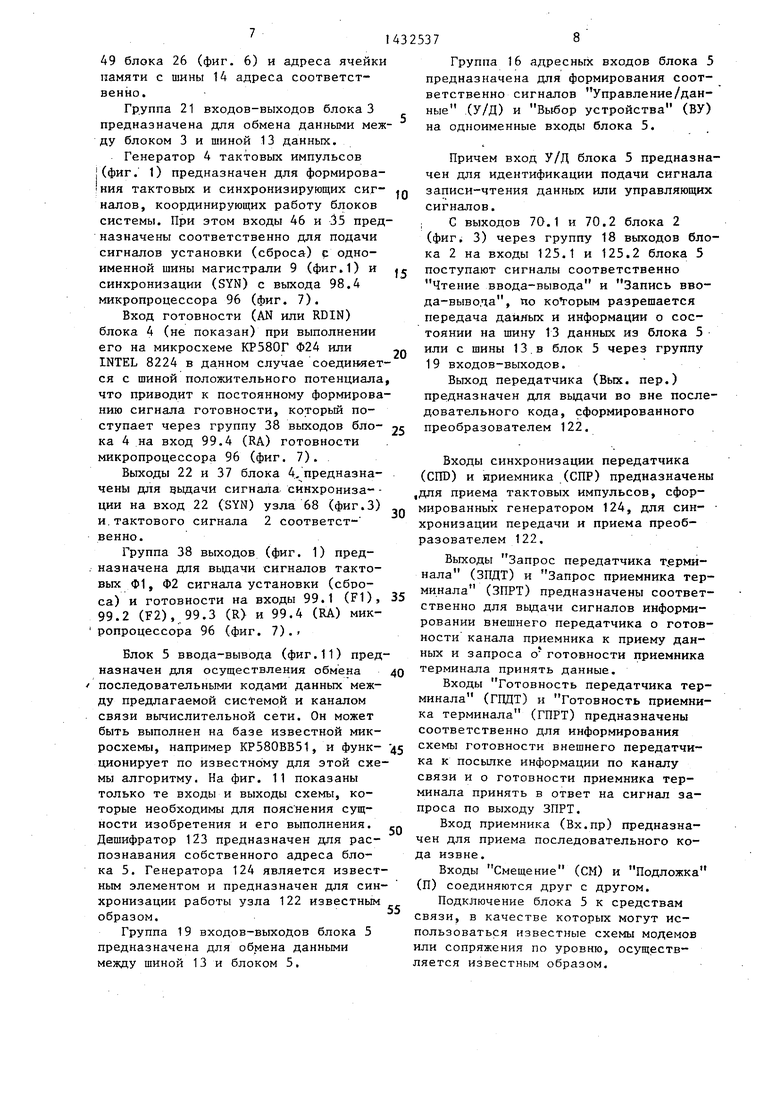

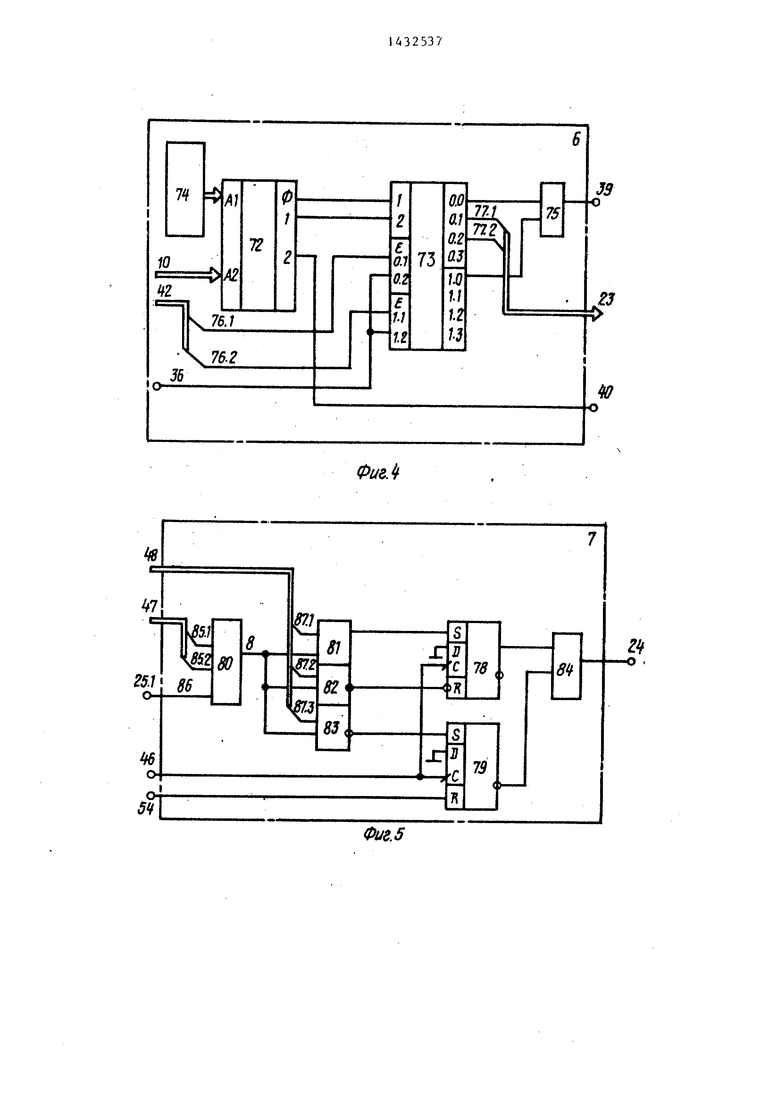

Дeu ифpaтop 6 управления (фиг.4) содержит первый 72 и второй 73 дешифраторы, генератор 74 кода собственного адреса и элемент ИЛИ 75, выход которого является выходом 39 блока 6 Группа выходов генератора 74 соединена с первой группой (А1) входов дешифратора 72, первый (0), второй (1) и третий (2) выходы которого соедине- ны соответственно с первым, вторым входами дешифратора 73 и выходом 40 блока 6, Группа 10 входов, входы первого 76.1, второго 76.2 разрядов группы 42 входов и вход 36 блока 6 сое- динены соответственно с второй группой (А2) входов дешифратора 72, пер- вьм (0.1), вторым (1.1), третьим (0.2 и четвертым (1.2) управляющими входами дешифратора 73, первым (0.0), вто- рой (1.0), третий (0.1) и четвертый (0.2) выходы которого соединены соответственно с первым, вторым входами элемента ИЛИ 75, а также образуют выходы первого 77.1 и второго 77.2 раз- рягдов группы 23 выходов блока 6.

Блок 7 прерывания (фиг.5) содержит триггеры 78 и 79, элементы И 80-84, входы первого 85.1, второго 85.2 разрядов группы 47 входов, вход 86 бло- ка 7, первый 87.1, второй 87.2 и третий 87.3 разряды группы 48 входов блока 7.

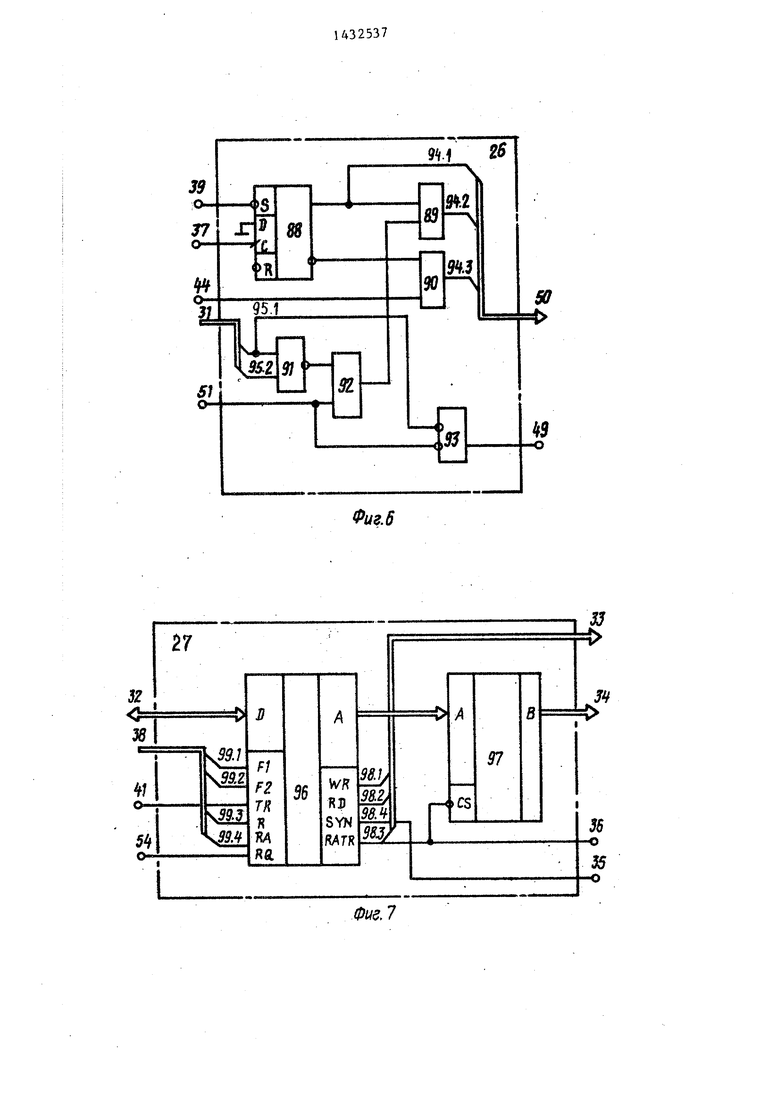

Блок 26 управления вводом-выводом (фиг. 6) содержит триггер 88, пятый 89, первый 90, четвертый 91, второй 92 и третий 93 элементы И, (выход 94. первого разряда группы 50 выходов, выходы второго 94.2 и третьего 94.3

разрядов группы 50 выходов блока 26, входы первого 95.1 и второго 95.2 разрядов группы 31 входов блока 26.

Операционньм блок 27 (фиг. 7) содержит микропроцессор 96, шинный формирователь 97. Выходы управления за- писью (WR), чтением (RD), подтверждения захвата (RATR) и синхронизации (SYN) узла 96 соединены соответственно с выходами первого 98.1, второго 98.2, третьего 98.3 разрядов группы 33 выходов и выходом 35 блока 27. Кроме того, выход 98.3 узла 96 соединен с управляющим входом (CS) узла 97 и является выходом 36 блока 27. Группа 32 входов-выходов, входы первого 99.1, второго 99.2, третьего 99.3 и четвертого 99.4 разрядов группы 38 входов, входы 41 и 54 блока 27 соединены соответственно с группой (D) . входов-выходов данных, первым (F1), вторым (F2) синхровходами, входам (R сброса, (RA) готовности, захвата магистрали (TR) и запроса прерывания (PQ) узла 96.

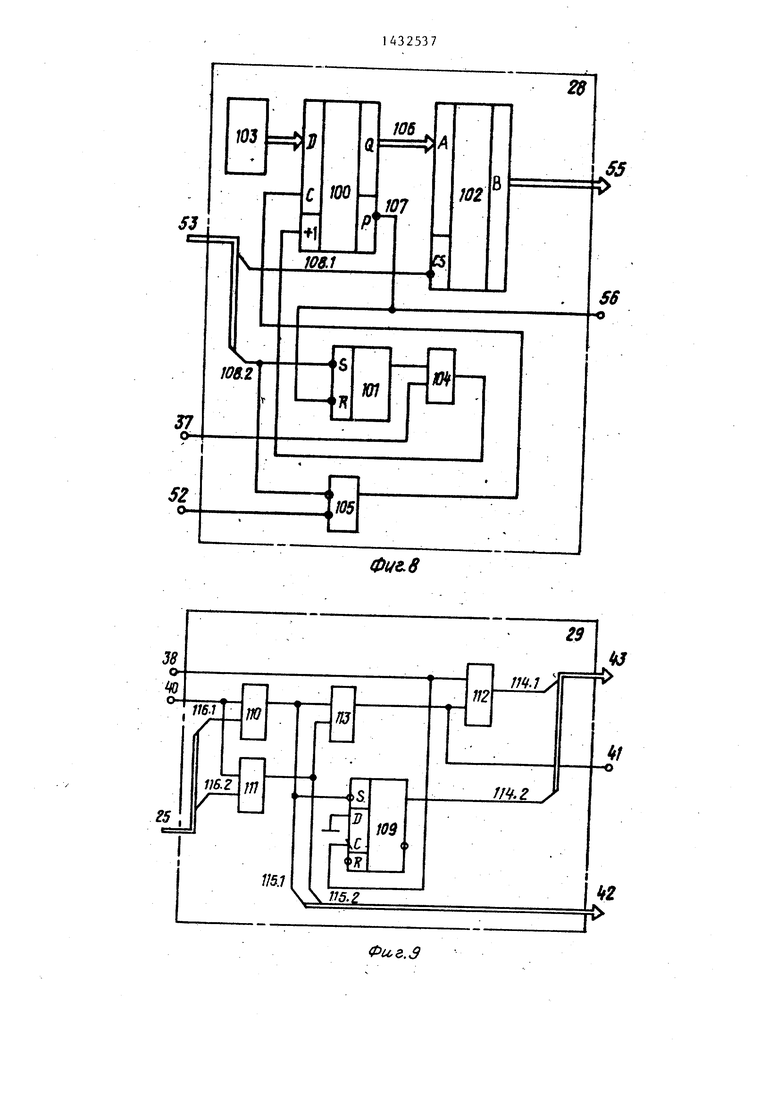

Блок 28 задания функции ведущего (фиг. 8) содержит счетчик 100, триггер Ш1, шинный формирователь 102 магистральных элементов, генератор 103 константы интервала опроса, элемент И 104 и элемент ИЛИ 105, группу выходов 106 счетчика, выход 107 переполнения счетчика 100, входы первого 108.1, второго 108.2 разрядов группы 53 входов.

Блок 29 синхронизации связи (фиг.9 содержит триггер 109, первый 110, втрой 111 и третий 112 элементы И, элемент ИЛИ 113, выходы первого 114.1 и второго 114.2 разрядов группы 43 выходов блока 29, выходы первого 115.1 и второго 115,2 разрядов группы 42 выходов блока 29, входы 116.1 и 116. элементов И 110 и 111.

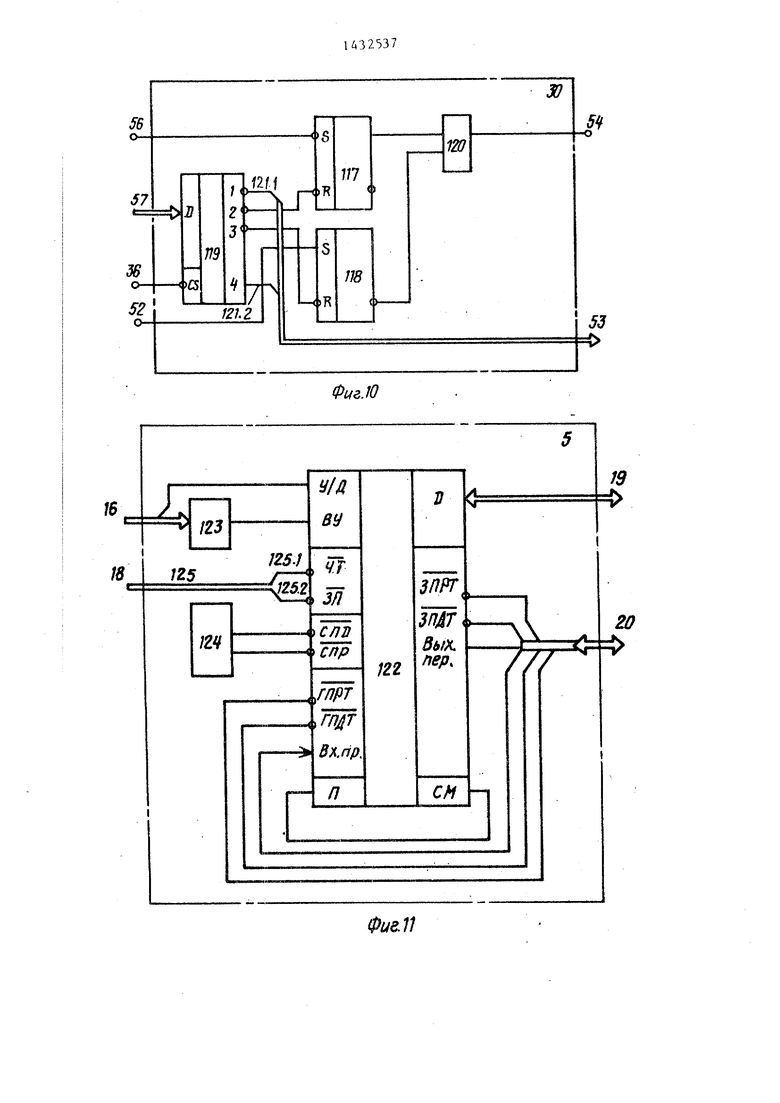

Блок 30 анализа состояния канала (фиг. 10) содержит второй 117 и первый 118 триггеры, дешифратор 119 и элемент ИЛИ 120. Первый (1) и второй (4) выходы дешифратора 119 образуют выходы первого 121.1 и второго 121.2 разрядов группы 53 выходов блока 30. Блок 5 ввода-вывода (фиг. 11) содержит преобразователь 122 последовательного кода в параллельный и, наоборот, дешифратор 123 адреса,- генератор 124 синхронизации, входы 125.1 и 125.2 преобразователя 122.

Устройство в целом предназначено для организации локальной вычислительной сети со структурой Моноканал, использую1цей известный протокол обмена HDLC или другой аналогичный .

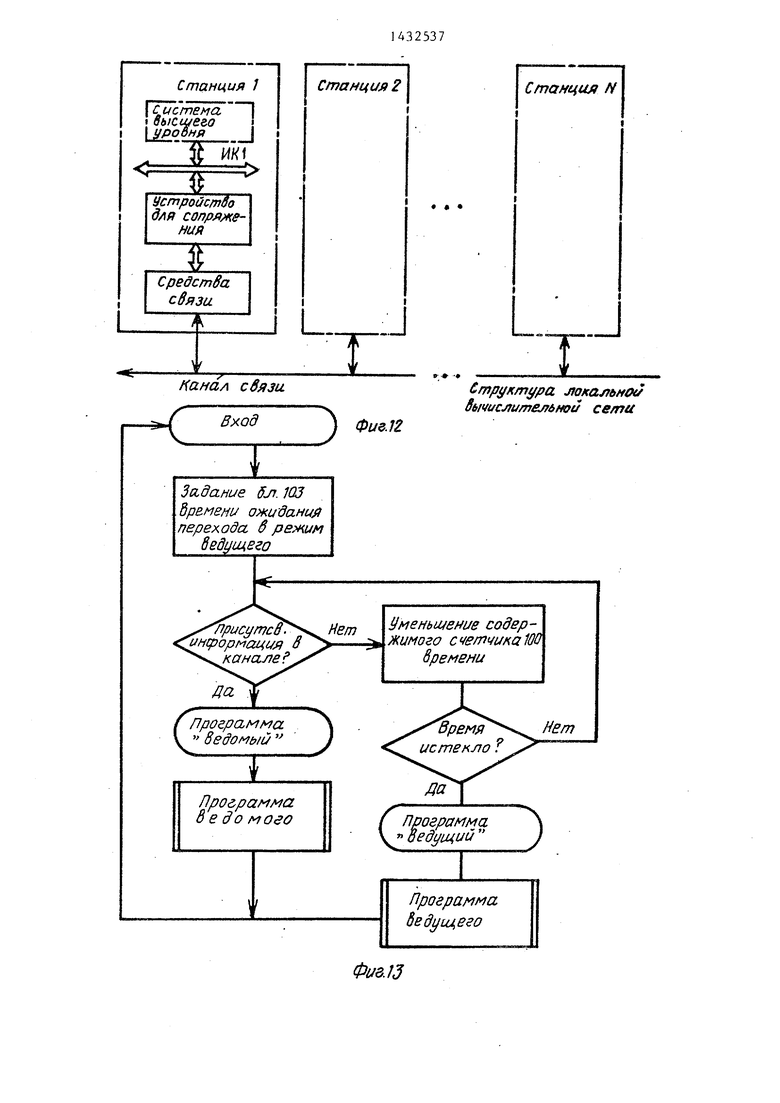

Устройство в вычислительной сети (фиг. 12) предназначено для подключения системы высшего уровня, например микро-ЭВМ, УВК типа КТС ЛИУС-2 или других аналогичных средств к моноканалу через соответствующие средства связи, которые в общем случае включают в себя модем. При этом устройство позволяет освободить средства системы высшего уровня от выпол

нения функций организации взаимодей- ствия с сетевыми средствами, т.е. выполнения протокола обмена, в сети, общего управления взаимодействием станций сети и т.д.

Кроме того, устройство с помощью включенных в него новых элементов и связей позволяет -существенно повысить надежность и расширить ее об-, {пасть применения за счет реализации Нового алгоритма определения функции едущего в сети, что позволяет при тказе ведущей системы (станции) передавать ее функции другой работо- Ьпособной системе с минимальной за- |цержкой в обмене. Тем самым достигается повышение живучесаги вычислитель йой сети в целом.

I Блок 1 связи с магистралью (фиг.2) Предназначен для хранения и,приема данных; поступающих как от системь верхнего уровня через внешнюю интерфейсную магистраль 9, так .и от Дру- гих систем обмена данными сети, под- ключенных к блоку .5 ввода-вывода. |Таким образом, блок 1 выполняет функ |ции общей памяти, имеющей каналы обр ения как со стороны внешней магист- |рали 9, так и со стороны внутренней магистрали 13 данных (фиг. 1). i Счетчики 58 и 59 предназначены |для задания адреса обращения к узлу |60 памяти. Управление записью в счет |чики 58 и 59 осуществляется по сиг- |налам с выходов 77.1 и 77.2 блока 6 г(фиг. 4), которые соединены соответ- |ственно с входами 67.1 и 67.2 груп- ;пы 23 входов блока 1 (фиг„ 2). ;. Приращение состояния счетчика 58 происходит по сигналу с выхода 94.1 |блока 26 (фиг. 6), поступающему на вход 65.3 блока 1 (фиг.2).

Узел 60 памяти представляет собой оперативный запоминающий узел. Управ ление обращением к нему осуществляется по сигналу с входа 65.1, а управление записью - по сигналу с входа 65.2 группы 50.

Адрес обращения к узлу 60 может з даваться как с выхода В узла 62, так и с группы 12 входов блока 1.

Шинный формирователь 61 предназначен для управления обменом меяоду ши- нами данных маг истрали 9 (фиг. 1) и магистрали 13,

Управление направлением передачи данньгх осуществляется в зависимости от сигналов на входах 66.1 и 66.2 в соответствии с табл. 1.

10

15

20

25

-

- , 50

6

Шинный формирователь 62 (фиг.2) по конструкции аналогичен узлу 61 и предназначен для передачи кода адреса, младшие -и старшие разряды которого 5 сформированы счетчиками 58 6 59, с входов А на группу выходов В (порт В) при наличии управляющего сигнала с входа 36 блока 1,

Системньй блок 2 управления (фиг.З) предназначен для управления доступом к шине данных операционного блока 27 (фиг.1), а также других блоков и устройств. Он может быть вдаолнен на известной микросхеме типа К580ВК28. При этом алгоритм функционирования блока 2 полностью идентичен известному для указанной микросхемы .

Группы 17 и 32 входов-выходов блока 2 (фиг.З) предназначены для ввода- вывода данных на внутреннюю шину 13 данньпс ив блок 27 (фиг.1) соответственно . ,

Вход 22 предназначен для подачи сигнала синхронизации (SYN) с вы-: хода генератора 4 тактовых импульсов Сфиг. 1).

Входы 71.1-71.3 предназначены для подачи на входы CWR и CRD и DE узла 68 сигналов записи, чтения и подтверждения захвата магистрали (шины) t;ooT- ветственно с выходов 98,1-98,3 микро-, процессора 96 (фиг.7).

Выходы 69.1 (RDM) и 69.2 (WRM) узла 68 (фиг. 3) предяаз начены для вы- 35 дачи сигналов управления чтением и записью в память, соответственно на входы 95,1 и 95,2 блока 26 управле-. ния вводом-выводом (фиг. 6).

Выходы 70.1 (RDIO) и 70.2 (WRIO) предназначены для выдачи сигналов чтения и записи во внешние устройства (устройства ввода-вывода) соответственно на входы блока 5 ввода-вывода (фиг. 1).,

. Если в качестве, блока 5 используется известная микросхема типа К580ВВ51, выходы 70.1 и 70.2 блока 68 соединяются с её входами Чтение (ЧТ) и Запись (ЗП) соответственно.

Блок 3 памяти (фиг. 1) представлА- ет собой постоянную память и предназначен для хранения программ в про- (цессе работы системы при обмене данными в вычислительной сети, напри- 55 мер программ управления обменом в соответствии с известным протоколом.

Вход 49 и группа 15 входов блока 3 предназначены для подачи сигнала разрешения выборки кристалла с выхода

30

40

45

49 блока 26 (фиг. 6) и адреса ячейк памяти с шины 14 адреса соответственно.

Группа 21 входов-выходов блока 3 предназначена для обмена данными меду блоком 3 и шиной 13 данных.

Генератор 4 тактовых импульсов |(фиг. 1) предназначен для формирова |ния тактовых и синхронизирующих сигналов, координирующих работу блоков системы. При этом входы 46 и 35 преназначены соответственно для подачи сигналов установки (сброса) р одноименной шины магистрали 9 (фиг.1) и синхронизации (SYN) с выхода 98.4 микропроцессора 96 (фиг. 7).

Вход готовности (AN или RDIN) блока 4 (не показан) при выполнении его на микросхеме КР580Г Ф24 или INTEL 8224 в данном случае соедикяет ся с шиной положительного потенциала что приводит к постоянному формированию сигнала готовности, который поступает через группу 38 выходов бло- ка 4 на вход 99.4 (RA) готовности микропроцессора 96 (фиг. 7).

Выходы 22 и 37 блока 4, предназначены для дьщачи сигнала синхрониза- ции на вход 22 (SYN) узла 68 (фиг.З) и.тактового сигнала 2 соответст- венно.

Группа 38 выходов (фиг. 1) предназначена для выдачи сигналов тактовых Ф1, Ф2 сигнала установки (сброса) и готовности на входы 99.1 (F1), 99.2 (F2), 99.3 (R и 99.4 (RA) микропроцессора 96 (фиг. ).

Блок 5 ввода-вывода (фиг.11) предназначен для осуществления обмена последовательными кодами данных между предлагаемой системой и каналом связи вычислительной сети. Он может быть выполнен на базе известной мик

10

f5

20

432537

5

5

0

0

8

Группа 16 адресных входов блока 5 предназначена для формирования соответственно сигналов Управление/данные (У/Д) и Выбор устройства (ВУ) на одноименные входы блока 5.

Причем вход У/Д блока 5 предназначен для идентификации подачи сигнала записи-чтения данных или управляющих сигналов.

; С выходов 70.1 и 70.2 блока 2 (фиг. 3) через группу 18 выходов блока 2 на входы 125.1 и 125.2 блока 5 поступают сигналы соответственно Чтение ввода-вывода и Запись ввода-вывода, по ко горым разрешается передача дайлых и информации о состоянии на шину 13 данных из блока 5 или с шины 13.в блок 5 через группу 19 входов-выходов.

Вьтод передатчика (Вых. пер.) предназначен для выдачи во вне последовательного кода, сформированного преобразователем 122.

Входы синхронизации передатчика (сив) и приемника (СПР) предназначены ,для приема тактовых импульсов, сформированных генератором 124, для син- хронизации передачи и приема преобразователем 122.

Выходы Запрос передатчика т,ерми- нала (ЗПДТ) и Запрос приемника терминала (ЗПРТ) предназначены соответственно для выдачи сигналов информировании внешнего передатчика о готовности канала приемника к приему данных и запроса о готовности приемника терминала принять данные.

Входы Готовность передатчика терминала (ГПДТ) и Готовность приемника терминала (ГПРТ) предназначены соответственно для информирования

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена данными в вычислительной сети | 1988 |

|

SU1599864A1 |

| Система обмена данными в вычислительной сети | 1991 |

|

SU1807493A1 |

| Устройство для сопряжения микропроцессорных внешних устройств с каналом ввода-вывода ЭВМ | 1985 |

|

SU1278871A1 |

| СИСТЕМА КОНТРОЛЯ И УПРАВЛЕНИЯ ВЫСОКОВОЛЬТНЫМИ ЯЧЕЙКАМИ РАСПРЕДЕЛИТЕЛЬНОЙ СЕТИ ШАХТЫ | 1990 |

|

RU2037205C1 |

| Мультиплексное устройство для обмена информацией | 1983 |

|

SU1157546A1 |

| Устройство для сопряжения магистрали эвм с магистралью внешних устройств | 1984 |

|

SU1229765A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С ВНЕШНИМИ ОБЪЕКТАМИ | 1993 |

|

RU2018944C1 |

| Устройство для сопряжения ЭВМ с периферийной системой | 1989 |

|

SU1635188A1 |

| Устройство для обмена данными | 1988 |

|

SU1599863A1 |

| Устройство для сопряжения ЭВМ с каналом связи | 1988 |

|

SU1656544A1 |

Изобретение относится к вычислительной технике и может быть использовано в локальных вычислительных сетях в качестве устройства для обмена данными между локальньми станциями сети и абонентами (процессорами) внешнего уровня каждой локальной станции через канал связи. Целью иэоб ретения является повьппение надежности за счет оперативного перераспределения функции ведущего абонента. Устройство содержит блок связи с магистралью, системный блок управления, блок управления вводом-выводом, блок памяти, генератор тактовых импульсов, операционный блок, блок ввода-вывода, блок задания функции ведущего, депш- фратор управления, блок синхронизации g связи, блок анализа состояния канала и блок прерьтания. 3 з.п. ф-лы, 14 ил., 6 табл. (Л

росхемы, например КР580ВВ51, и функ- 45 схемы готовности внешнего передатчиционирует по известному для этой схемы алгоритму. На фиг. 11 показаны только те входы и выходы схемы, которые необходимы для пояс нения сущности изобретения и его выполнения. Дешифратор 123 предназначен для распознавания собственного адреса блока 5. Генератора 124 является известным элементом и предназначен для синхронизации работы узла 122 известньм образом.

Группа 19 входов-выходов блока 5 предназначена для обмена данными между шиной 13 и блоком 5.

0

5

ка к посьшке информации по каналу связи и о готовности приемника терминала принять в ответ на сигнал запроса по выходу ЗПРТ.

Вход приемника (Вх.пр) предназначен для приема последовательного кода извне.

Входы Смещение (СМ) и Подложка (П) соединяются друг с другом.

Подключение блока 5 к средствам связи, в качестве которых могут использоваться известные схемы модемов или сопряжения по уровню, осуществляется известным образом.

Управление узлом 122 осуществляется программно сразу после начальной установки (вход начальной установки не показан), в узел 122 с входов 19

записываются команды начальной уста

:НОВКИ.

I Посредством управляющих слов узлу 1.122 сообщаются скорость приема-пере- 1дачи данных, количество разрядов в каждом блоке данных, число разрядов останова, режим работы, наличие или отсутствие разряда четности каждого Iблока данных.

Управляющие слова подразделяются на два типа: инструкции режима и инструкции команды.

При передаче данных блоком 5 осуществляется преобразование данных, поступающих с группы 19 входов-выходов в параллельном коде в последовательность символов со служебной информаци ей и выдача ее в канал связи с различной программно-задаваемой-скоростью.

При приеме информации блок 5 получает последовательность символов со I служебной информацией из канала связи осуществляет выделение данных в ней, преобразование их в параллельный вось миразрядньй код и передачу его на группу 19 выходов.

Дешифратор 6, управления (фиг, 4) предназначен для формирования управляющих си,гнапов на основе кода адреса, поступающего с шины 9 на группу 10 входов, управляющих сигналов с выходов 42 блока 29 (фиг. 1) синхронизации связи и сигнала подтверждения захвата магистрали с выхода 36 блока 27 (фиг, 1).

Генератор 74 адреса (фиг. 4) предназначен для формирования кода собственного адреса системы при подключении к интерфейсной магистрали 9 (фиг. 1).

Входы разрядов 76.1 и 76.2 группы 42 входов соединены соответственно с выходами 115.1 и 115,2 блока 29 (фиг, 9),

Выходы разрядов 77.1 и 77.2 груп- пы 23 выходов соединены соответственно с входами 67.1 и 67,2 блока 1 (фиг. 2) и предназначены для записи кода адреса ячейки ОЗУ в счетчики 59 и 59,

Выход 40 предназначен для передачи сигналов разрешения срабатыв ания элементов И 110 и 111 блока 29 (фиг, 9)

0

5

5

,

5

0

5

0

Блок 7 прерываний (фиг. 5) предназначен для формирования интерфейсного сигнала запроса прерывания на выходе 24, который поступает на соответствующую шину интерфейсной магистрали 9 (фиг, 1),

Основными элементами блока 7 являются триггеры маски 78 и запроса пре- .рывания 79 (фиг, 5),

Элементы И 80-83 предназначены для управления состоянием триггеров 78 и 79,

На группу 48 входов с магистрали 9 на входы 87,1 - 87,3 поступают сигналы значений данных (разряды ДЙ, Д1 Ц2), код которых предназначен для уп- равления триггерами 78 и 79, В частности, сигналом с входа 87,1 устанавливается маска прерывания, а сигналом со входа 87.2 осуществляется сброс мaQки. Сигналом с входа 87,3 производится сброс запроса прерывания.

Управление элементом И 80 осуществляется на основании значений сигналов разрядов (А0И А1 адреса, поступающих на входы 85,1 и 85.2 соответственно, и интерфейсного сигнала Выдача, поступающего на вход 86 с соответствующей шины интерфейсной магистрали 9 (фиг, 1).

На вход 54 поступает сигнал запроса прерывания блока 27 (фиг. 1),

На вход 46 поступает сигнал установки в исходное состояние с соответствующей шины интерфейсной магистрали 9,

Интерфейсная магистраль 9 предназначена для организации обмена данными, а также адресными и управляющими сигналами между предлагаемой системой и системой высшего уровня, подключаемой к вычислительной сети (фиг.12), Она может быть построена в соответствии с известным интерфейсньм протоколом ИК1 и содержит три группы шин: данных, адреса и управляющие,

Шины 13 и 14 (фиг, 1) предназначены для обмена данными и адресной информацией внутри устройства.

Блок 26 управления вводом-выводом (фиг, 6) предназначен для формирования сигналов управления блоком 1 связи с магистралью и блока 3 памяти (фиг. 1).

На входы 95.1 и 95,2 разрядов группы 31 входов поступают сигналы чтения памяти (RDM) и записи в память

(WRM) с выходов 69.1 и 69.2 системного блока 2 управления (фиг. 3).

Выходы 9А.1 - 94.3 разрядов группы 50 выходов предназначены соответ- стненно для выдачи сигналов на счетный вход (+1) 65.3 счетчика 58 блока 1 (фиг. 2), вход 65,1 выбора кристалла (CS) и вход 65.2 управления записью (WR) узла 60 памяти. Q

Выход 49 блока 26 (фиг. 6) предназначен для выдачи сигнала выбора кристалла (CS) на одноименный вход блока 3 памяти (фиг. 1).

Операционный блок 27 (фиг, 7) пред- 5 назначен для управления обменом данными и управляющей информацией в системе в соответствии с заданным сетевым протоколом, например известным протоколом HDLC.20

Микропроцессор 96 может быть выполнен на известной микросхеме, на- - пример, типа КР580ИК80, INTEL8080 или другой аналогичной.

Назначение входов-выходов и алго- 25 ритмы реализации команд узла 96 полностью аналогичны известным для микропроцессора указанной марки.

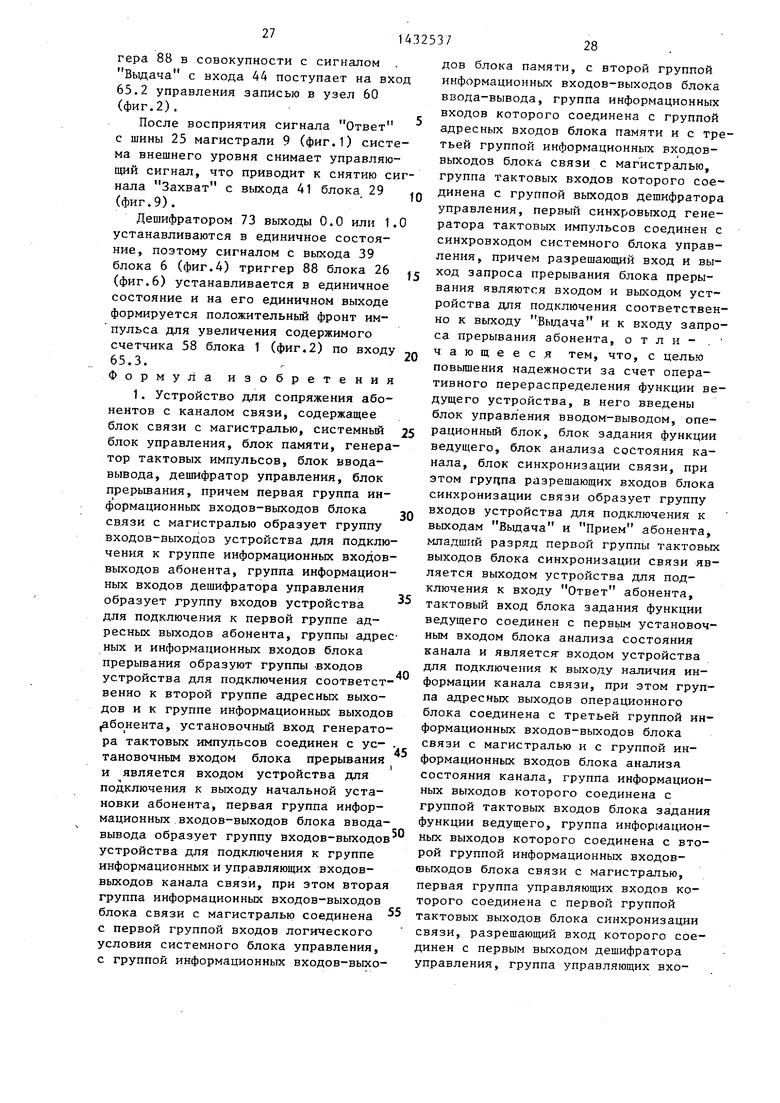

Основной командньй цикл микропроцессора 96 приведен на фиГ, 14. ЗО

. Шинный формирователь 97 (фиг.7) предназначен для управления передачей кода адреса с группы адресных выходов (А) микропроцессора 96 на группу 34 выходов блока 27 и дашее на шину 14 адреса системы. Узел 97 срабатывает при наличии сигнала низкого потенциала на входе CS, поступающего с выхода 98.3 (RATR) узла 96.

Группа 32 входов-выходов предна- 0 значена для реализации обмена данными между узлом 96 и боком 2 (фиг.1).

На входы 99.1 (F1), 99.2 (F2), 99.3 (R) и 99.4 (RA) группы 38 входов блока 27 поступают соответствен- но известные сигналы первой синхро- серии, второй синхросерии, установки в исходное (сброса) и готовности с соответствующей группы выходов генеатора 4 тактовых импульсов (фиг. .1).сп Входы 41 (TR) и 54 (RQ) блока 27 (96) предназначены соответственно для подачи на соответствующие входы узла 96 известных сигналов Захват (HOLD) и Запрос прерывания с выхо- цов блока 29 (фиг. 9) и блока 30 (фиг. 10).

Выходы разрядов 98.1 (WR), 98.2 (RD) и 98.3 (RATR) группы 33 выходов

35

Q

5 0

5

О

0

5

блока 27 (96) предназначены для выдачи соответственно сигналов Запись, Прием (Чтение) и Подтверждение захвата, поступающих на входы 71.1 (CWR), 71.2 (CRD) и 71.3 (DE) узла 68 (фиг. 3).

Выход 35 (SYN) узла 96 (фиг. 7) предназначен для формирования сигнала синхронизации, формируемого микропроцессором в начале каждого машинного цикла.

Выход 36 используется для выдачи сигнала подтверждения захвата на блоки 6,29 и 30 системы (фиг. 1).

Блок 28 задания функции ведущего (фиг. 8) предназначен для инициирования переходи устройства к реализации функции ведущего в вычислительной сети.

Счетчик 100 предназначен для отсчета времени слушания канала связи устройством на предмет обнаружения наличия информации в канале свяаи.

Триггер 101 предназначен для формирования сигнала управления счетом на счетчик 100.

Шинньи| формирователь 102 предназначен для передачи на шину 13 данных с группы 106 выходов счетчика 100 его содержимого.

Подключение входов порта А к выхо рам порта В осуществляется по управляющему сигналу с входа 108.1 блока

28, который поступает с выхода 121.1 блока 30 (фиг. 10).

Генератор 103 кода предназначен для задания кода временногЪ интерва-. ла, в течение которого устройство осуществляет слушание линии связи и по истечении которого происходит переход к реализации режима ведущего в соответствии с алгоритмом, приведенным на фиг. 13.

Каждое из устройств, входящих в состав вычислительной сети (фиг,12), характеризуется собственным интервалом времени ожидания перехода в режим ведущего. Поэтому одновременно в сети в режим ведущего может перейти только одна станция. Кроме того, этим обеспечивается повышение отказоустойчивости устройства и сети в целом за счет того, что при отказе ведущей в данный момент станции по истечении конечного интервала времени функции ведущего возьмет на себя другая станция.

Элемент И 104 предназначен для уп- 1 авления подачей счетных импульсов rta соответствующий вход (+1) счетчика 100 с входа 37 блока 28 (фиг,8). Элемент ИЛИ 105 предназначен для формирования сигнала Запись в счет- мнк 100 значения кода .временного интервала ожидания перехода в режим ведущего. При этом сигнал Запись фор- мируется либо при возбуждении йыхода 21.2 (входа 108.2 блока 28 (фиг.8) дешифратора 119 блока 30 (фиг.10) по 1:оманде микропроцессора, либо по сигналу Низкий потенциал с входа 52 ()лока 28, являющегося признаком нали- 1ИЯ информации в канале связи.

Вход 52 предназначен для сообщения системе признака наличия информации I) канале связи (фиг. 12). Он может формироваться, например, модемом, 11ХОДЯЩИМ в состав средств связи в качестве сигнала-детектора линейного сигнала. Входы 52 всех устройств, объ ( диняемых в вычислительную сеть фиг.12), подключены к одной и той же Jrинии канала связи. Поэтому до тех пор, пока в канале связи присутствует информация, генерируется сигнал, который поступает на входы 52 всех осталь 11ЫХ станций сети и обеспечивает запис 1 их счетчики 100 соответствующих ко- дов интервалов времени ожидания перевода в режим ведущего. Тем самым обеспечивается блокировка перехода в резким ведущей какого-либо другого уст- )ойства до момента завершения выполнения своих функций или отказе, опре- |1еленном по отсутствии сигнала на входе 52 ведущего в данный момент устройства.

Выход 56-преднааначен для выдачи сигнала Переполнение счетчика 100 На вход блока 30 (фиг.10), что свидетельствует об истечении времени ожидания перехода в режим ведущего для данного устройства.

Блок 29 синхронизации связи (фиг.9 предназначен для преобразования сигналов управления интерфейсной магистрали во внутренние управляющие сигна- лы евязи ycтpoйcfвa.

Триггер 109 предназначен для управления связью между шинами данных 8 магистрали 9 и внутренней шиной 13 данных через шинный формирователь 61 блока 1 (фиг. 2)о

Элементы И 110 и 111 предназначены для стробирования приема блоком 29

0

5

(фиг. 9) интерфейсных сигналов Выдача и прием соответственно, поступающих с входов 116.1 и 116.2 группы 25 входов блока 29.

Элемент И 112 предназначен для формирования сигнала Ответ (в соответствии с протоколом интерфейса ИК1), который с выхода 114.1 блока 29 по- :ступает через разряд 45 группы 43 выходов блока 29 на шину сигнала Ответ магистрали 9 (фиг.1).

Элемент ИЛИ 113 предназначен для формирования сигнала Захват на выходе 41 блока 29, который поступает на вход TR микропроцессора 96 (фиг.7). ,Сигналы с выходов 114.1 и 114.2 группы 43 выходов поступают соответственно на входы 66.1 и 66.2 блока 1 (фиг. 2). Выходы разрядов 115.1 и 115.2 группы 42 выходов блока 29 соединены соответственно с входами 76.1 .и 76.2 блока 6 (фиг.4).

Блок 30 анализа состояния канала (фиг.10) предназначен для формирования управляющих сигналов на основе анализа состояния канала связи (наличия информации в нем) и анализа признака завершения интервала времени ожидания перехода в режим ведущего.

Триггер 117 предназначен для фиксации сигнала завершения интервала времени ожидания перехода в режим ведущего.

Триггер 118 предназначен для фик- садии сигнала отсутствия информации в канале связи.

Дешифратор 119 предназначен для формирования следующих управлякяцих сигналов: с выходов 1 (121.1) и 4 (121.2) сигналов управления шинным формирователем 102 блока 28 (фиг.8) и триггера 101 (элемента ИЛИ 105) соответственно, с выходов 2 и 3 - сигналов установки в нулевое состояние триггеров 117 и 118 блока 30 (фиг. 10) соответственно.

Элемент ИЛИ 120 предназначен для формирования сигнала запроса прерывания на выходе 54 блока 30, который по- dTynaeT (фиг.1) на одноименные входы блока 7 (фиг. 5) и блока 27 (фиг.7).

Входы 56,57,36 и 52 блока 30 (фиг.10) предназначены соответственно для приема сигналов окончания интервала времени ожидания перехода в режим ведущего, крда адреса для формирования управляющих сигналов дешифратором -19, сигнала Подтверждение

захвата с выхода 98.3 (36) блока 27 (фиг. 7) и сигнала Признак наличия информации в канале связи.

Обращение к устройству при обмене данными с ним со стороны системы высшего уровня, например вычислительной машины (фиг.12), осуществляется через интерфейсную магистраль 9 (фиг. 1) в соответствии с известным протоколом JQ ИК1.

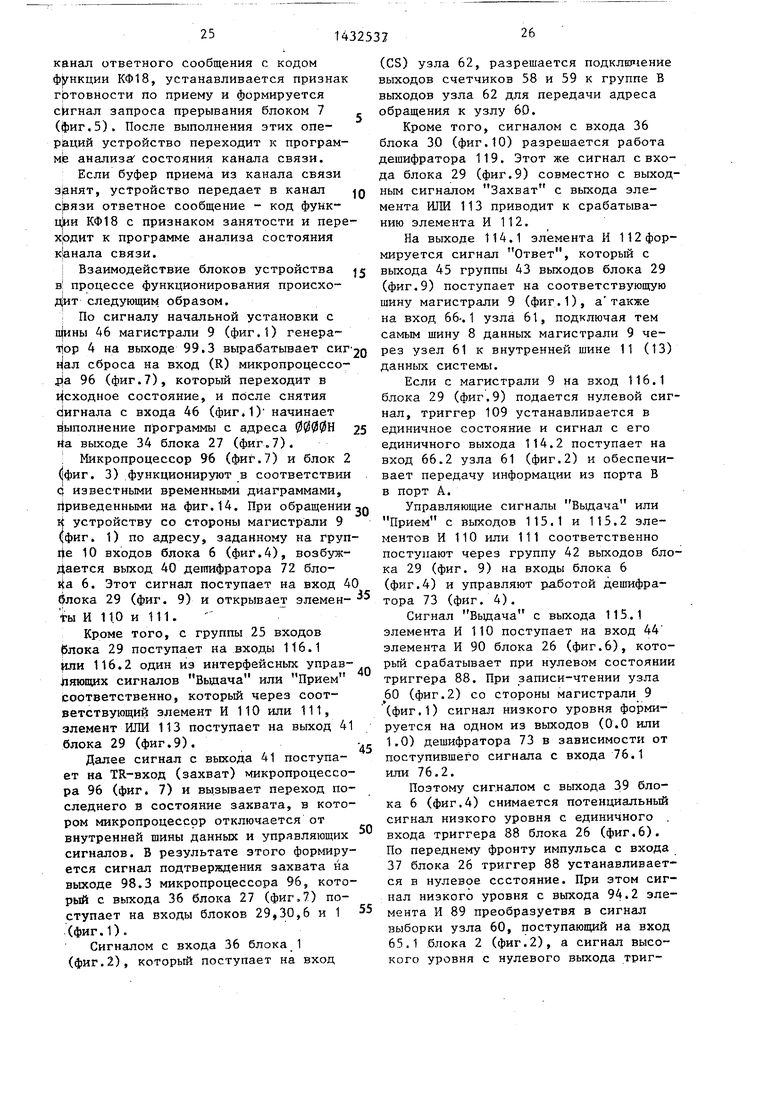

Формат адреса при обращении к системе со стороны магистрали 9 приве ден в табл. 2.

Комбинация значений разрядов ад- 5 реса А1 и А0 и управляющих сигналов, поступающих на входы 25, определяет режимы работы элементов системы, например дешифратора 73 блока 6 (фиг.4).

Алгоритм работы дешифратора 119 0 (фиг.10) описывается табл.3 соответствия.

Алгоритм работы дешифратора 73 (фиг.4) блока 6 описывается в табл.4. 25

Адрес, формируемый на основании одержимого счетчиков 58 и 59 (фиг.2), редставляет собой десятиразрядный од, условно подразделяемый на старшую (разряды А9 и А8) и младшую часть ,Q (разряды А7 - A0J

При записи Б счетчики 58 и 59 информация представляется в виде двух байтов, которые поступают поочередно с шин данных 8 интерфейсной магистра- ли через узел 61 (фиг. 2) на входы счетчиков 58 и 59 соответственно. При этом первый байт задает младший байт адреса, а второй байт разрядами D1 и DO - значения разрядов А9 и А8 адреса соответственно. Разряды D7 - D2 второго байта в этом случае не используются.

Запись и чтение информации в (из) узел 60 памяти (фиг. 2) осуществляется следующим образом.

Для чтения содержимого узла 60 по адресу (Абаз+1), поступающему на вход 10 блока 6 (фиг.4) в счетчик 58 записывается с шин 8 данных магистрали 9 через узел 61 младший байт адреса. После этого по адресу (Абаз+2) в устройство выдается старший байт адреса и, наконец, по адресу (Абаз+ф) производится прием информации из устройства через группу D-выходов узла 60, шину 11 блока 1, порти В и А уз- ла 61 на шины 8 данных магистрали 9 (фиГ.1), с которой данные могут по40

45

50

JQ

5

0

5

Q

0

5

0

ступать в систему высшего уровня (фиг.12),

. При записи информации в узел 60 памяти (фиг.2) по адресу (Абаз+1) в устройство вьщается младший байт адреса с шин 8 данных магистрали 9 (фиг.1). Далее аналогично по адресу (Абаз+2) в устройство выдается старший байт адреса, после чего по адресу (Абаз+) в устройство поступает информация для записи в узел 60 (фиг. 2).

При обмене массивами данных указанным образом определяется только начальный адрес ячейки узла 60 памяти. Приращение же адреса в процессе передачи (приема) массива данных осуществляется по сигналам с выхода 94.1 триггера 88 (фиг.6, блок 6) блока 26. Это позволяет освободить процессор (систему) верхнего уровня управления от формирования адресов всех ячеек массива обмена и тем самым повысить его полезную нагрузку для решения задач, не связанных с обменом.

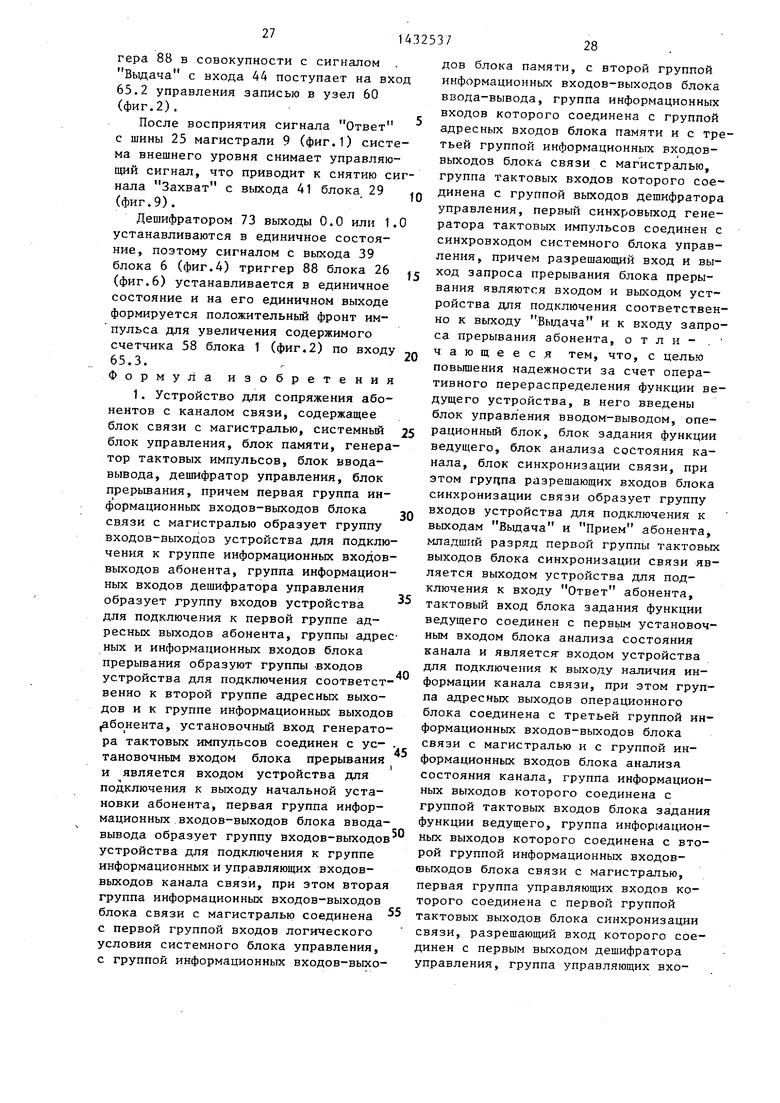

Для управления элементами И 81 - 83 блока 7 прерываний (фиг. 5) используется информация, поступающая с шин 48 данных магистрали 9 (фиг.1). При этом используется значение сигналов разрядов в соответствии со следующей табл.5.

Узел 60 памяти (фиг.2) условно подразделяется на несколько зон, содержащих помимо программ, реализуемых устройством, специальную управляющую информацию.

Распределение указанной информации по зонам узла 60 может быть, например, следующим:

а)зона конфигурации вычислительной сети, включающая список собственных адресов устройств, аналогичных данному, которые подключаются к локальной вычислительной сети;

б)байт состояния канала, содержащий информацию о коде выполняемой сетевой функции (биты D0-D3), признак занятости канала (D4), признак того, что канал не отвечает (D5), признак изменения конфигурации (D6), признак- невыполнения сетевых функций (D7).

Разряды D0-D3 определяют код сетевой функции и устанавливаются системой высшего уровня через магистраль 9 (фиг. 1). Разряд D4 определяет наличие непрерывной информации в канале связи. Установка разряда D4 осуществляется на основе анализа .содержимого счетчика 100 блока 28 (фиг.8). Установка разряда D5 в единицу производится, если после опроса устройством других станций, входящих в сеть, ни от одной из них не был получен ответ. Установка разряда D6 в единицу производится, в отличие от разряда D5, если не все, а только некоторые, стан- ции не выдали ответ. Установка в нулевое состояние разрядов D4-D6 осуществляется по коду, принимаемому от системы высшего уровня через магист- раль 9. Установка (сброс) разряда D7 осуществляется системой высшего уровня после записи информации о конфигурации сети в узел 60 (фиг,2) (самим устройством при переходе на выполне- ние рабочей программы);

в) байт состояния передачи, содержащий информацию о коде выполняемой функции (биты D0-D3), признак не- I ответа канала связи (D4), признак занятости канала связи (D5), признак сбоя в канале (D6), признак невыполнения функции (D7). Разряды D0-D3 ис- : пользуются ДЛЯ задания функции За- i пись (код 1000), остальные коды не I задействованы. Установка кода функции I осуществляется с магистрали 9. Уста- I новка в единицу (нуль) разряда D4 осу I ществляется устройством в случае от- : сутствия ответа от адресуемой станции, после трехкратного повторения обращения к ней (системой высшего : уровня через магистраль 9). Разряд ;D5 устанавливается устройством в слу- :чае занятости буфера приема у абонен . Сброс D5 производится через маги- страль D9. Разряд D6 устанавливается устройством при получении от адресуемой станции признака занятости буфера приема. Сброс D6 осуществляется через магистраль D 9. Разряд D7 устанавливается через магистраль D9 после записи массива данных в буфере передачи узла 60 (фиг. 2). Сброс D7 осуществляется после выполнения функции Запись, При этом в зависимости от результата выполнения функции Запись разряд D7 может быть сброшен, а разряды () не установлены (если функция Запись выполнена правильно в противном случае разряд D7 сброшен а установлен в единичное состояние один из разрядов D4-D6 в зависимости от причины невыполнения функции Запись }

Q с

5

0

г)байт состояния приема, содержащий информацию о коде выполняемой функции (биты ) и признак завершения приема информации из канала связи (бит D7). Остальные биты не используются. Функция Запись имеет код 1000. Разряд D7 устанавливается устройством после приема сообщения

из канала связи. Сброс бита D7 осуществляется со стороны магистрали 9 после освобождения приемного буфера;

д)байт состояния завершения приема, содержащий информацию о признаке молчания канала (бит D0), признаке неправильного приема (D1) и признаке приема информации в дополнительный буфер (D2). Биты D3-D7 не используются. Установка битов D0-D2 осуществляется при выполнении устройством подпрограммы приема;

е)признак ведущей станции устанавливается устройством после того, как оно принимает на себя функции ведущего. При этом установленному (сброшенному) признаку соответствует код FFH (00И);

ж)зона рабочих ячеек памяти используется устройством для выполнения основных функций, определения статуса ведущего и других операций;

з)собственный адрес элемента записывается устройством в узел 60 (фиг.2) в начале выполнения программы в соответствии с кодом, генерируемым узлом 74 (фиг.4);

и) признак готовности по передаче (код FFH) формируется устройством после выполнения функции Запись. Если маска прерывания не установлена, то программно выз| шается формирование запроса прерывания;

к) признак готовности по приему (код FFH) формируется устройством после завершения приема;

л) буфер сообщения для передачи в канал связи, используемый для записи в узел 60 (фиг.2) со стороны магистрали 9 сообщения, предназначенного для передачи в другую станцию. В буфер писывается адрес станции назначения, длина сообщения и текст сообщения;

м) основной и дополнительный буферы приема из канала связи, предназначенный для приема сообщения от других станций.

При обмене данными между локальными станциями (фиг.12) в системе реализуется интерфейс ИРМ, Вит-последонательный обмен данными по линиям связи. При этом передача сообщений между локальными станциями осуществляется посредством ограниченного набора байтов, порядок следования которых устанавливается форматом сообщения. Интерфейсом ИРМ устанавливается два типа форматов сообщений, известных для протокола HDLC, как форма- ты 1 и 2. В целом алгоритм организации обмена данными между устройством и другими элементами вычислительной сети определяется программой, которая хранится в блоке 3 памяти (фиг.1). При этом характеристики алгоритма обмена, определяемые протоколом обмена форматами сообщений, способами формирования служебной информации (синхро- байтов, контрольных битов и т.д.) и другими атрибутами могут варьировать- ся программно без изменения структуры технических средств устройства.

Устройство может выполнять несколько сетевых функций, код которых задается в формате сообщений байтом, содержащим информацию о виде сообщения (бит 0, вызов-ответ), признаке занятости локальной станции (бит 1), типе формата сообщения (бит 2, форматы 1/2), признаке повторения передачи (бит 3, принимает значение 1 при по вторных посыпках), коде сетевой функции (биты 4 - 7).

Коды сетевых функций могут задаваться табл. 6.

Остальные 28 кодов (из 32 возможных) функций являются резервными и в рассматриваемом примере не исполь- зуются.

Обмен сообщениями между локальными станциями в сети организован в виде циклов, под которыми понимается процедура передачи в канал связи од- ного сообщения. Несколько взаимосвязанных циклов образуют процесс передачи, который организуется по асинхронному принципу, поэтому на посылаемые в канал связи вызовы устройство должно получать ответы.

В соответствии с интерфейсом ИРМ локальной станцией могут выполняться следующие функции, которые определяют ее место на соответствую щем уровне передачи управления в сети: прием - ответ; централизованное управление.

,

jg, 20 25„ .Q

-дг50

55

При выполнении соответствующей функции локальная станция считается активной относительно этой функции. В зависимости от функции, выполняемой устройстом в данный момент времени, различают следующие три типа состояний локальных станций: управляемая подсистема; инициативная управляющая подсистема; ведущая подсистема.

Переходы между состояниями локальных станций осуществляются в соответствии с принятым алгоритмом обмена данными в сети.

В состоянии управляемая подсистема осуществляется прием адресованных устройству сообщений и формирование ответных сообщений в соответствии с кодом реализуемой сетевой функции.

В состоянии инициативная управляющая подсистема устройство может принимать управление обменом по каналу связи, формировать и передавать сообщения, принимать и анализировать ответные сообщения, а также возвращать управление по окончании процесса пе редачи. .

В состоянии Ведущая подсистема устройство осуществляет координацию работы всех устройств, подключенных к каналу связи (фиг.12). При этом ведущее устройство может осуществлять передачу управления другому устройству и контролировать работу активного управляющего устройства. В соответствии с принятым алгоритмом обмена в каждый момент времени в сети может быть только одно ведущее устройство.

Координация взаимодействия локальных станций сети осуществляется ведущим устройством сети путем выполнения функций передачи и возврата управления следующим образом.

При передаче управления ведущее устройство назначает одно из других устройств, входящих в сеть, активной управляющей подсистемой для передачи сообщения. Для этого ведущее устройство направляет выбранной управляющей локальной станции сообщение формата 1 с кодом функции КФ6 (передача управления каналом).

После приема сообщения с кодом функции КФ6 управляющая станция ста новится активной и может выполнять один цикл обмена в одном процессе передачи. По окончании процесса передачи активная управляющая станция выполняет функцию возврата управления, для чего она направляет ведущему устройству сообщение с кодом функции КФ7 (возврат управления каналом), при чем передача управления может осуществляться только по инициативе ведущего устройства. Причем последовательность процедур управления каналом связи при передаче управления по инициативе ведущего устройства мо- : жет определяться только этим устройством.

Процедура передачи данных осуще- :ствляется при выполнении сетевой функ Iции с кодом КФ2 (Запись), При этом i ведущее устройство или активная уп- Iравляющая подсистема формирует посыл- :ку в канал связи сообщения с кодом ;функции КФ2, которое адресуется для ;приема конкретной управляемой станци- ;ей. После вьщачи сообщения активная :управляющая станция осуществляет про- граммный отсчет контрольного интер- :вала времени в ожидании ответного со:общения.

; Все устройства, подключенные к ка iналу связи (фиг.12), осуществляют при iем посылаемого сообщения. Адресуемое устройство производит опознание соб- |ственного адреса в сообщении и выдает В канал связи сообщение с кодом функ- ;ции КФ18 (подтверждение приема сооб- ;щения).

При отсутствии ответа в течение контрольного интервала времени активная управляющая станция осуществляет : трехкратную повторную передачу того |же сообщения. В случае отсутствия от- |вета на трехкратную повторную переда|чу адресуемое устройство считается отказавшим.

Во время обмена с адресуемым устройством ведущее устройство выполняет функцию пассивного приема сообще-

НИИ.

Основными режимами работы устройства являются режимы: начального запуска; передача - прием данных.

Режим начального запуска осуществляют следующим образом.

В.этом режиме устройство переходит при поступлении сигнала установки с шины 46 магистрали 9 (фиг,Т) от системы высшего уровня управления.

При поступлении сигнала с входа 4 генератор 4 вырабатывает сигнал на- чальной установки на выходе 99.3 (фиг.7), который поступает на вход

-

5 0 5

О

ж

.

5

0

55

сброса микропроцессора 96. После этого последний переходит к реализации программы начального запуска.

В процессе выполнения программы начального запуска в узле 60 (фиг.2) происходит очистка списка адресов локальных станций, байтов состояния, сброс байтов готовности и установка признака готовности устройства к выполнению рабочей программы.

К выполнению рабочей программы устройство переходит после приема в узел 60 (фиг.2) таблицы конфигурации сети в виде списка адресов подключенных локальных станций от системы верхнего уровня.

Признаком окончания занесения таб лицы конфигурации в узел 60 является установка соответствующего признака в байте состояния.

В процессе начального запуска про- .изводится начальная установка счетчика 100 0лока 28 (фиг.8) либо цирку- лярно всех устройств, подключенных к сети, по сигналу с входа 52 (фиг.1 и 8), либо сигналом с выхода 121.2 дешифратора 119 (фиг.10), который поступает на вход 108.2 блока 28 задания функции ведущего (фиг.8). В последнем случае управление дешифратором 119 (фиг.10) осуществляется кодом, с группы 34 адресных выходов блока 27 (фиг. 1) который через шину 14 адреса поступает на группу 57 входов блока 30 (фиг.10).

Далее устройство переходит к реализации алгоритма, изображенного на фиг. 13.. .

Поскольку каждому устройству, входящему в сеть, задается собственный код времени ожидания перехода в режим ведущего устройства, то при отсутствии информации в канале связи .(единичном сигнале на входе 52) по истечении интервала ожидания С. (i - номер -устройства в сети) появится сигнал на выходе 107 счетчика 100. По.этому сигналу устанавливается в нулевое состояние триггер 101 блока 28 (фиг.8), прещая через элемент И 104 тем самым приращение содержимого счетчика 100, а также по сигналу с входа 56 (фиг.10) триггер 117, блока 30 устанавливается в единичное состояние, формируя через элемент ИЛИ 120 на выходе 54 сигнал запроса прерывания, на соответствующий вход микропроцессора 96 (фиг.7). Микропроцессор при этом осуществляет

переход в программу ведущего устройства.

Кроме того, сигнал с выхода 54 блка 30 (фиг.10) поступает на нулевой вход триггера 79, который устанавливается в нулевое состояние, и сигналом с одноименного выхода через элемент И 84 (фиг. 5) может сформироват сигнал прерывания на выходе 24 для устройства высшего уровня управления при неустановленной маске прерывания на триггере 78 блока 7,

Аналогично переход в состояние ведущего устройства осуществляется при отсутствии информации в канале связи по причине отказа ведущего в данный момент устройства. Этим обеспечивается повышение отказоустойчивости и живучести устройства, а также расшире-

ние области ее применения. I

При выполнении программы ведущего

устройства организуется передача управления с функций КФ6 каждой локальной станции, входящей в список, хра- нящийся в узле 60 (фиг.2), и контролируется информация из канала связи с функцией возврата управления (КФ7)

Если в канале связи информации отсутствует, т.е. ни одна из локальных станций сети не отвечает на передачу управления, ведущее устройство снимает с себя функции ведущего и переходит в программу анализа состояния канала связи аналогично описанному выше. При этом программа анализа состояния канала связи выполняется до тех пор, пока в канале не появится . информация, либо не истечет интервал времени ожидания перехода к функции ведущего.

Если в канале связи присутствует информации с кодом функции передачи управления, устройство формирует в ответ код функции возврата управле- ния и переходит на выполнение программы инициативного управляющего устройства или управляемого устройства.

Режим приема-передачи данных осуществляют следующим образом.

Перед передачей данных в канал связи осуществляется проверка готовности устройства к передаче. При этом устройство считается готовым к передаче, если в байте состояния передачи в узле 60 (фиг, 2) разряд , а признак готовности по передаче установлен в нулевое состояние.

, «

c 0

5

о Q

с

0

Если передача данных в канал связи осуществляется с магистрали 9 (фиг.1), в узел 60 записываются адрес абонента назначения, длина сообщения и его текст. После этого в байт состояния передачи записывается код, который является признаком задания устройству выполнения функции Запись. Устройство начинает передачу сообщения в канал связи после приема из него сообщения с кодом функции передачи управления.

После передачи сообщения -в канал связи устройство переходит в режим ожидания ответа. При отсутствии ответа от абонента осуществляется повторная передача сообщения с последующим переходом в режим ожидания ответа. Повтор передачи может быть повторен трехкратно.

Если в режиме ожидания принимается информация с кодом функции КФ18 (подтверждение приема), устройство осуществляет сброс бита D7 в байте состояния передачи.

Окончание процедуры передачи сообщения в канал связи характеризуется установкой признака готовности по пе- , редаче и формированием сигнала запроса прерывания при снятой маске на выходе 24 блока 7 (фиг.5).

В локальной вычислительной сети только одно устройство может быть ведущим и осуществлять управление каналом связи. Все остальные устройства, включенные в сеть, являются пассивными и активизируются после передачи им управления.

При отказе ведущего устройства функции ведущего может взять на себя одно из описанных других устройств.

Любое устройство, входящее в сеть, осуществляет анализ информации, циркулирующей в канале связи с целью обнаружения адрессованного ему сообщения. После выбора адресованного сообщения устройство контролирует правильность приема сообщения и кода функции. При неправильном приеме информации устройство переходит к выполнению программы анализа состояния канала связи.

Если же информация принята правильно и получено сообщение с кодом функции Запись, устройство производит анализ занятости буфера приема из канала связи. Если буфер свободен, устройство осуществляет передачу в

канал ответного сообщения с кодом функции КФ18, устанавливается признак готовности по приему и формируется сигнал запроса прерывания блоком 7 (фиг.5). После выполнения этих операций устройство переходит к програм- м1е анализа состояния канала связи.

Если буфер приема из канала связи , устройство передает в канал ответное сообщение - код функ- КФ18 с признаком занятости и пере хЬдит к программе анализа состояния к анала связи.

Взаимодействие блоков устройства В: процессе функционирования происхо- д|ит следующим образом. I По сигналу начальной установки с фны 46 магистрали 9 (фиг.О генера Tlop 4 на выходе 99.3 вырабатывает сиг сброса на вход (R) микропроцессо- jja 96 (фиг.7), который переходит в исходное состояние, и пбсле снятия с игнала с входа 46 (фиг.1) начинает выполнение программы с адреса rta выходе 34 блока 27 (фиг.7). : Микропроцессор 96 (фиг.7) и блок 2 (|фиг. 3) функционируют в соответствии 4 известными временными диаграммами, Приведенными на фиг.14. При обращении k устройству со стороны магистрали 9 (фиг. 1) по адресу, заданному на группе 10 входов блока 6 (фиг.4), возбуж- 4ается выход 40 дешифратора 72 бло- ka 6. Этот сигнал поступает на вход 4 0лока 29 (фиг. 9) и открывает элемен- 1гы И ПО и 111.

Кроме того, с группы 25 входов Рлока 29 поступает на входы 116.1 рли 116.2 один из интерфейсных управляющих сигналов Вьщача или Прием соответственно, который через соответствующий элемент И 110 или 111, элемент ИЛИ 113 поступает на выход 41 блока 29 (фиг.9).

Далее сигнал с выхода 41 поступает на TR-вход (захват) микропроцессора 96 (фиг. 7) и вызывает переход последнего в состояние захвата, в котором микропроцессор отключается от внутренней шины данных и управляющих сигналов. В результате этого формируется сигнал подтверждения захвата на выходе 98.3 микропроцессора 96, который с выхода 36 блока 27 (фиг.7) поступает на входы блоков 29,30,6 и 1 (фиг.1).

Сигналом с входа 36 блока 1 (фиг.2), который поступает на вход

. Q

0

5

0

(CS) узла 62, разрешается подклю 1ение выходов счетчиков 58 и 59 к группе В выходов узла 62 для передачи адреса обращения к узлу 6D.

Кроме того, сигналом с входа 36 блока 30 (фиг.10) разрешается работа дешифратора 119. Этот же сигнал с входа блока 29 (фиг.9) совместно с выходным сигналом Захват с выхода элемента ИЖ 113 приводит к срабатыванию элемента И 112.

На выходе 114.1 элемента И 112 формируется сигнал Ответ, который с выхода 45 группы 43 выходов блока 29 (фиг.9) поступает на соответствующую шину магистрали 9 (фиг.1), а также на вход 66. 1 узла 61, подключая тем самым шину 8 данных магистрали 9 через узел 61 к внутренней шине 11 (13) данных системы.

Если с магистрали 9 на вход 116.1 блока 29 (фиг.9) подается нулевой сигнал, триггер 109 устанавливается в единичное состояние и сигнал с его единичного выхода 114.2 поступает на вход 66.2 узла 61 (фиг.2) и обеспечивает передачу информации из порта В в порт А.

Управляющие сигналы Выдача или Прием с выходов 115.1 и 115.2 элементов И 110 или 111 соответственно поступают через группу 42 выходов блока 29 (фиг. 9) на входы блока 6 (фиг.4) и управляют ра-ботой дешифратора 73 (фиг. 4).

Сигнал Вьщача с выхода 115.1 элемента И 110 поступает на вход 44 элемента И 90 блока 26 (фиг.6), который срабатывает при нулевом состоянии триггера 88. При записи-чтении узла 60 (фиг.2) со стороны магистрали 9 (фиг.1) сигнал низкого уровня формируется на одном из выходов (0.0 или 1.0) дешифратора 73 в зависимости от поступившего сигнала с входа 76.1 или 76.2.

Поэтому сигналом с выхода 39 блока 6 (фиг.4) снимается потенциальный сигнал низкого уровня с единичного , входа триггера 88 блока 26 (фиг.6). По переднему фронту импульса с входа 37 блока 26 триггер 88 устанавливается в нулевое состояние. При этом сигнал низкого уровня с выхода 94.2 элемента И 89 преобразуетвя в сигнал выборки узла 60, поступающий на вход 65.1 блока 2 (фиг.2), а сигнал высокого уровня с нулевого выхода триг

гера 88 в совокупности с сигналом . Вьщача с входа 44 поступает на вхо 65.2 управления записью в узел 60 (фиг.2).

После восприятия сигнала Ответ с шины 25 магистрали 9 (фиг.1) система внешнего уровня снимает управляю- щий сигнал, что приводит к снятию синала Захват с выхода 41 блока 29 (фиг.9).

Дешифратором 73 выходы 0.0 или 1. устанавливаются в единичное состояние, поэтому сигналом с выхода 39 блока 6 (фиг.4) триггер 88 блока 26 (фиг.6) устанавливается в единичное состояние и на его единичном выходе формируется положительный фронт им- пульса для увеличения содержимого счетчика 58 блока 1 (фиг.2) по входу 65.3. Формула изобретения

ts

20

5

JQ

0

5

0

0

5

дов блока памяти, с второй группой информационных входов-выходов блока ввода-вывода, группа информационных входов которого соединена с группой адресных входов блока памяти и с третьей группой информационных входов- выходов блока связи с магистралью, группа тактовых входов которого соединена с группой выходов дешифратора управления, первый синхровыход генератора тактовых импульсов соединен с синхровходом системного блока управления, причем разрешающий вход и выход запроса прерывания блока прерывания являются входом и выходом устройства для подключения соответственно к выходу Выдача и к входу запроса прерывания абонента, о т л и - . чающееся тем, что, с целью повышения надежности за счет оперативного перераспределения функции ведущего устройства, в него введены блок управления вводом-выводом, опе- рационньЕЙ блок, блок задания функции ведущего, блок анализа состояния канала, блок синхронизации связи, при этом rpyrtna разрешающих входов блока синхронизации связи образует группу входов устройства для подключения к выходам Выдача и Прием абонента, младший разряд первой группы тактовых выходов блока синхронизации связи является выходом устройства для подключения к входу Ответ абонента, тактовый вход блока задания функции ведущего соединен с первь1м установочным входом блока анализа состояния канала и является- входом устройства для подключения к выходу наличия информации канала связи, при этом группа адресных выходов операционного блока соединена с третьей группой информационных входов-выходов блока связи с магистралью и с группой информационных входов блока анализа состояния канала, группа информационных выходов которого соединена с группой тактовых входов блока задания функции ведущего, группа информационных выходов которого соединена с второй группой информационных входов- шыходов блока связи с магистралью, первая группа управляющих входов которого соединена с первой группой тактовых выходов блока синхронизации связи, разрешающий вход которого соединен с первым выходом дешифратора управления, группа управляющих вхо

дов которого соединена с второй I pyn- пой тактовых выходов блока синхрони- з&ции связи, синхровход которого соединен с разрешающим входом блока анализа состояния канала, со стробирую- пфм входом блока связи с магистралью, с управляющим входом дешифратора уп- р&вления и с выходом управления свя-.- з|ью операционного блока, синхровыход которого соединен с синхровходом ге- |Н2ратора тактовых импульсов, второй ;:а нхровыход которого соединен с син- хэовходом блока управления вводом-выводом и с разрешающим входом блока задания функции ведущего, выход переполнения которого соединен с вторым установочным входом блока анализа состояния канала, выход запроса пре- Рзшания которого соединен с входом запроса прерывания блока прерывания -и с входом запроса прерывания операционного блока, группа управляющих Взгходов которого соединен с группой управляющих входов системного блока управления, вторая группа входов-вь5хо дрв логического условия которого со- д нинена с группой, информационных вkoдoв-выxoдoв операционного блока, гЬуппа управляющих входов к вход запроса захвата .которого соединены соответственно с группой синхровыходов г|енератора тактовых импульсов и с так Т|Овым выходом блока синхронизации с|вязи, второй выход дешифратора уп- р авления соединен с установочным вход;ом блока управления вводом-выводом, первый и второй входы логического УСЛОВИЯ которого соединены соответст- йе.нно с младшими разрядами второй г руппы тактовых выходов блока синхрон|изации связи и группы адресных выходов операционного блока, группа входов чтения-записи блока ввода-вывода соединена с первой группой выходов чтения-записи системного блока управления , вторая группа выходов чтения- записи которого соединена с группой входов управления чтением-записью блока управления вводом-выводом, группа выходов и выход которого соединены соответственно с второй группой управляющих входов блока связи с магист- рапью и синхровходом блока памяти,

0

Q 5 5 50- 0

вый вход первого элемента И являются . соответственно установочным входом, синхровходом и первым входом логического условия блока, первый вход второго элемента И соединен с первым входом третьего элемента И и является вторым входом логического условия блока, первый вход и второй вход четвертого .элемента И, соединенный с вторым входом третьего элемента И, образуют группу входов управления чтением-записью блока, единичный выход триггера, соединенный с первым входом пятого элемента И, выходы пятого и первого элемента И образуют группу выходов блока, выход третьего элемента И является выходом блока, при этом в блоке управления вводом- выводом выход четвертого элемента И соединен с вторьм входом второго элемента И, выход которого соединен с вторым входом пятого элемента И, второй вход первого элемента И соединен с нулевым выходом триггера, информационный вход которого подключен к шине нулевого потенциала устройства.

А. Устройство по п. 1, о т л и - чающееся тем, что блоканали3 143253732

за состояния канала содержит дешифра-Таблица2

тор, два триггера, элемент ИЛИ, при-т

чем единичные входы первого и второгоРазряды адреса Содержание

триггеров являются соответственно

вым и вторым установочными входами

блока, управляющий вход и группа ин-А7 j А2 Базовый адрес системы

формационных входов дешифратора об-(Абаз)

разуют соответственно разрешающийА1 - А0 Адрес внутренних элевход и группу информационных входов JOментов (регистров)

блока, первый, второй выходы дешифра-системы

тора образуют группу информационных

выходов блока, выход .элемента ИЛИ является выходом запроса прерьюания

блока, при этом в блоке диализа сое- f5ТаблицаЗ

тояния канала третий и четвертый вы-|

ходы дешифратора соединены соответ-Г

ственно с нулевыми входами первого и

второго триггеров, выходы которыхРазряды адреса Выходы дешифратора 119

соединены соответственно с первым и 20 входа 57

вторым входами элемента ШШ.j | I 1

Таблица А15 1-й | 2-й I 3-й 4-й

входов

Направление передачи узла 61

1 Из порта В в порт А 0 0 Из порта А в порт В

Разряды адреса с магистрали 9

Управляющие сигналы

А1

А0

Прием (вход 76; 2)

0

0

0 0

9 0

0

0

5

0

0

0 1

1

0 1

0 1

0 1

1 1

1

И

1 1

1

1 0

1 1 1

0

Таблица4

Режим работы эле- ментов

Выдача

(вход

Запись информации в узел 60 (фиг,2) Запись информации в счетчик 58 адреса (старший байт адреса) (фиг.2) Запись информации в счетчик адреса 59 (младший байт) Сброс прерывания. Установка в единицу триггера 78 маски (фиг.5)

Чтение информации из узла 60 (фиг.2)

33143253734

ТаблицаЗ РазрядЗначение разряда

1 I

D0 Действие не Установка маски за- выполняется проса прерывания

триггером 78 (фиг.5)

D1 То же Сброс маски запроса прерывания на триггере 78 (фиг.5).

D2 Сброс триггера 79 запроса прерывания (фиг.5)

Таблицаб

ии Код функцииСодержание сете-j,г--чj--Vj-- вой функции

.IiIidldLLi.

1 X X X 0 0 0 1 Запись

1 X X X 0 10 1 Передача управления каналом

I

1 X X X 1 1 0 Возврат управления каналом

0 X X X 0 0 0 1 Подтверл;цение

приема сообщения

римечание. Х- безразличное состояние.

ФиеЛ

Фи&.2

Фие.з

Фиг. 6

Фаз. 7

0lft.e

Фи,&,Э

.Ю

Фиг.11

Станция 2

Ястройстбо для сопряжения

Средства связи.

j L.J Т

Канал связи.

ч

Вход

Задание 6ji. 103 Ьрв.мени ожиданий перевода 6 редким бедущего

(Программа Sedof b/u J

HIT

Лро&рам/ а В e до моео

Станция N

j

Iwraiucca аяажянщкщявял ей ттвяяЛ

Т

Фие.12

Стр /к/пура локальной 8ы исли/п&лбти сети

Уменьшение содержимого счет( Времени

npoapaf Ma 6edyu4eso

Фив. 13

32

9BM (SYA/)

)

(VIR

Y

,ilОсновной ffOfiQHdHutt/ цим МП

мнп

Pi/S. /

шины

| Авторское свидетельство СССР № 756400, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для обмена данными | 1981 |

|

SU1012235A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-10-23—Публикация

1987-04-27—Подача