Изобретение относится к области автоматизации энергетических систем и может быть использовано в релейной защите и противоаварийной автоматике.

Цель изобретения - повышение чувствительности устройства в условиях изменения нагрузки.

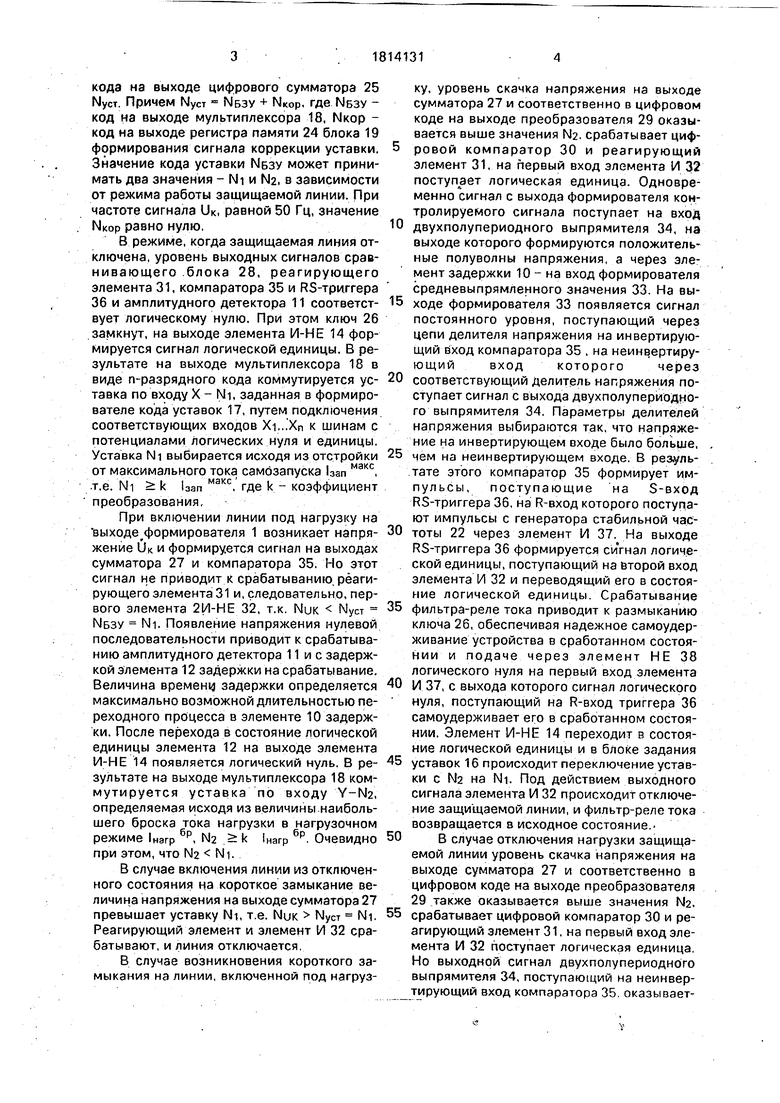

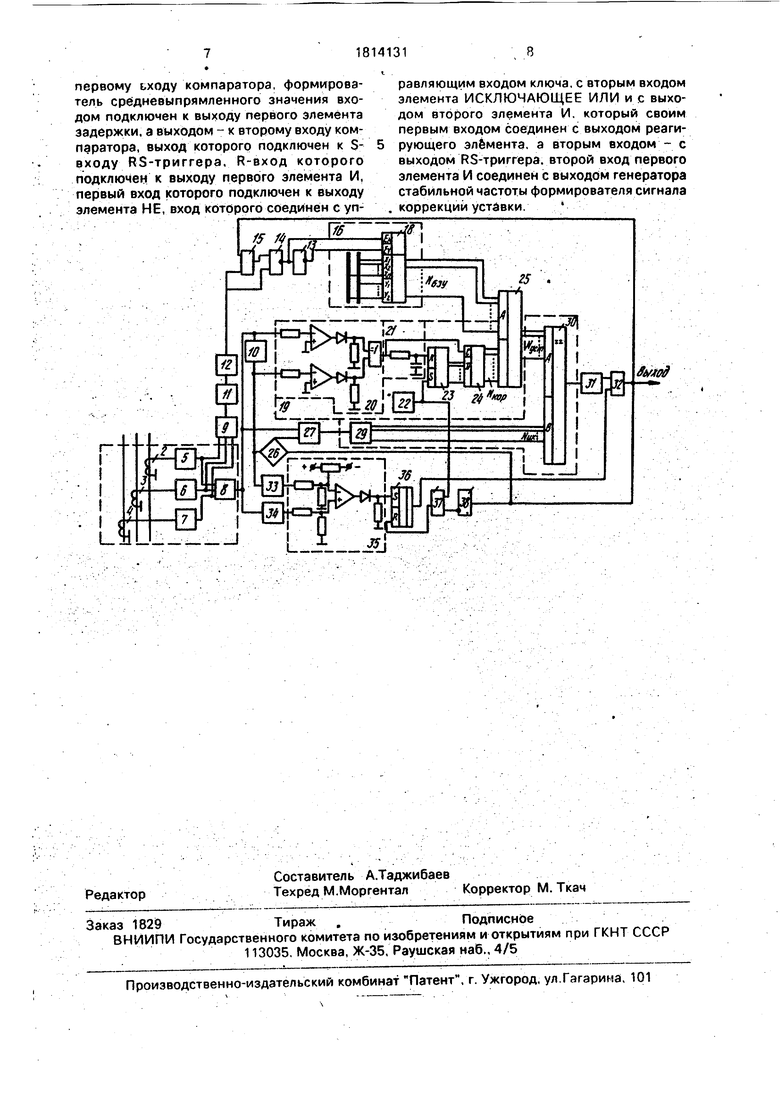

На. чертеже представлена схема фильтр- реле тока. Фильтр-реле тока содержит формирователь 1 контролируемого сигнала, включающий трансформаторы 2-4 тока, входные преобразователи 5-7 тока и фильтр 8 симметричных составляющих, первый элемент задержки 10, фильтр 9 прямой после- довательнрсти, амплитудный детектор 11, элемент задержки на срабатывание 12, элемент НЕ 13, элемент И-НЕ 14, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 15, блок формирования уставки 19, включающий фазовый детектор 20, второй элемент задержки 21, генератор стабильной частоты 22, счетчик 23 и регистр памяти 24, цифровой сумматор 25, ключ 26, сумматор 27, сравнивающий блок 28, включающий аналого-цифровой преобразователь 29 и цифровой компаратор 30, реагирующий элемент 31. Формирователь средневыпрямленного значения 33, двухполупериодный выпрямитель 34, компаратор 35, RS-триггер 36, элементы И 32 и 37 и .элемент НЕ 38. Устройство работает следующим образом. На выходе формирователя 1 формируется сигнал UK в виде напряжения,, пропорционального току прямой, обратной или нулевой последовательности, или их комбинации. На выходе Сумматора 27 выделяется аварийная составляющая сигнала Ок путём суммирования его с выходным сигналом элемента задержки 10, представляющим собой фазовый фильтр с коэффициентом передачи по амплитуде, равным единице, и фазовым запаздыванием, равным 180°, на частоте 50 Гц. Цифровым компаратором 30 сравнивающего блока 28 производится сравнение кода ана- лого-цифрового преобразователя 29 NUK и

ел

с

со Jv

ш-А

00

кода на выходе цифрового сумматора 25 Муст. Причем Муст - NBSV + NKOp, где МБЗУ - код на выходе мультиплексора 18, Мкор - код на выходе регистра памяти 24 блока 19 формирования сигнала коррекции уставки. Значение кода уставки МБЗУ может принимать два значения - NI и N2, в зависимости от режима работы защищаемой линии. При частоте сигнала UK, равной 50 Гц, значение Мкор равно нулю.

В режиме, когда защищаемая линия отключена, уровень выходных сигналов сравнивающего .блока 28, реагирующего элемента 31, компаратора 35 и RS-триггера 36 и амплитудного детектора 11 соответствует логическому нулю. При этом ключ 26 замкнут, на выходе элемента И-НЕ 14 формируется сигнал логической единицы. В результате на выходе мультиплексора 18 в виде п-разрядного кода коммутируется ус- тавка по входу X - NI, заданная в формирователе кода уставок 17, путем подключения соответствующих входов Xi...Xn к шинам с потенциалами логических нуля и единицы. Уставка NI выбирается исходя из отстройки от максимального тока самбзапуска 1зап мзкс, .т.е. NI k laan макс, где k - коэффициент преобразования.

При включении линии под нагрузку на Ъыходе формирователя 1 возникает напряжение О и формируется сигнал на выходах сумматора 27 и компаратора 35. Но этот сигнал не приводит к срабатыванию, реагирующего элемента 31 и, следовательно, первого элемента 2И-НЕ 32, т.к. NUK Nycr МБЗУ NH. Появление напряжения нулевой последовательности приводит к срабатыванию амплитудного детектора 11 и с задержкой элемента 12 задержки на срабатывание. Величина времен задержки определяется максимально возможной длительностью переходного процесса в элементе 10 задержки. После перехода в состояние логической единицы элемента 12 на выходе элемента И-НЕ 14 появляется логический нуль, В результате на выходе мультиплексора 18 коммутируется уставка по входу Y-N2, определяемая исходя из величины наибольшего броска тока нагрузки в нагрузочном режиме нэгр 6р, N2 k Нагр 6р. Очевидно при этом, что N2 NL

В случае включения линии из отключенного состояния на короткое замыкание величина напряжения на выходе сумматора 27 превышает уставку NI, т.е. NUK Nycr N1. Реагирующий элемент и элемент И 32 срабатывают, и линия отключается.

В случае возникновения короткого замыкания на линии, включенной под нагрузку, уровень скачка напряжения на выходе сумматора 27 и соответственно в цифровом коде на выходе преобразователя 29 оказывается выше значения N2. срабатывает цифровой компаратор 30 и реагирующий элемент 31, на первый вход элемента И 32 поступает логическая единица. Одновременно сигнал с выхода формирователя контролируемого сигнала поступает на вход

0 двухполупериодного выпрямителя 34, на выходе которого формируются положительные полуволны напряжения, а через элемент задержки 10 - на вход формирователя средневыпрямленного значения 33. На вы5 ходе формирователя 33 появляется сигнал постоянного уровня, поступающий через цепи делителя напряжения на инвертирующий вход компаратора 35 , на неинвертирующий вход которого через

0 соответствующий делитель напряжения поступает сигнал с выхода двухполупериодного выпрямителя 34. Параметры делителей напряжения выбираются так, что напряжение на инвертирующем входе было больше,

5 чем на неинвертирующем входе. В резуль- .тате этого компаратор 35 формирует импульсы, поступающие на S-вход RS-триггера 36, на R-вход которого поступают импульсы с генератора стабильной час0 тоты 22 через элемент И 37. На выходе RS-триггера 36 формируется сигнал логической единицы, поступающий на второй вход элемента И 32 и переводящий его в состояние логической единицы. Срабатывание

5 фильтра-реле тока приводит к размыканию ключа 26, обеспечивая надежное самоудерживание устройства в сработанном состоянии и подаче через элемент НЕ 38 логического нуля на первый вход элемента

0 и 37, с выхода которого сигнал логического нуля, поступающий на R-вход триггера 36 самоудерживает его в сработанном состоянии. Элемент И-НЕ 14 переходит в состояние логической единицы и в блоке задания

5 уставок 16 происходит переключение уставки с N2 на NI, Под действием выходного сигнала элемента И 32 происходит отключение защищаемой линии, и фильтр-реле тока возвращается в исходное состояние.

0 В случае отключения нагрузки защищаемой линии уровень скачка напряжения на выходе сумматора 27 и соответственно в цифровом коде на выходе преобразователя 29 также оказывается выше значения N2,

5 срабатывает цифровой компаратор 30 и реагирующий элемент 31, на первый вход элемента И 32 поступает логическая единица. Но выходной сигнал двухполупериодного выпрямителя 34, поступающий на неинвертирующий вход компаратора 35. оказывается меньше, чем выходной сигнал формирователя средневыпрямленногр значения 33, поступающий на инвертирующий вход компаратора 35. В результате этого на выходе компаратора 35 присутствует сигнал ло.гиче- 5 ского нуля, поступающий на S-вход триггера 36 и не приводящий к его срабатыванию. Следовательно, логический нуль, поступающий с выхода триггера 36 на второй вход элемента И 32,блокирует его срабатывание 10 и соответственно всего устройства в целом. При работе на номинальной частоте IHOM входное и выходное напряжения элемента 10 задержки находятся в противофа- зе. На выходе фазового детектора 20 15 формируется сигнал логической единицы, мере элемент задержки 21 удерживая счетчик в обнуленном состоянии . В результате NKOP О..При отклонении частоты сигнала от номинальной (f ± fnOM) на выходе суммато- 20 ра 27 возникает напряжение небаланса UHE. а на выходе аналого-цифрового преобразователя 29 - код небаланса МНБ. Одновременно фазовый сдвиг входного и выходного напряжений элемента задержки 25 1.0 становится отличным на 180°, на выходе детектора 20 появляется дважды за период Ок импульс нулевого уровня, длительного KOTOporo гфд пропорциональна отклоне- нию частоты Ок. Генератор 22 вырабатывает 30 импульсы с частотой fri/i, которыми наполняется счетчик 23 за время гфд . .Сигнал в виде кода Мкор переписывается из счетчика 23 в регистр 24 памяти в момент появления им- s пульса единичного уровня на выходе дётек- 35 тора 20. Элемент задержки 21 в виде RC-цепи служит для задержки поступления импульса единичного уровня на R-вход счет- . чика 23 с целью надежного считывания кода Мкор регистром памяти 24. Значение кода 40 коррекции уставки:

N

кор

гфд-frn

Кг

где Кд - коэффициент деления счетчика 23.

Работа формирователя сигнала коррекции уставки идентична при f fHoM и f THOM.

Цифровым сумматором 25 производится сложение кодов ЫБЗУ и Мкор, т.е. Nycr Мкор + МБЗУ. В результате при отклонении в нормальном режиме частоты от номинальной производится коррекция Мусттак; что Мкор NHB. Загрубление фильтра-реле тока в этом случае происходит только при f

fHOMТаким образом, введение канала, определяющего знак приращения амплитуды контролируемого сигнала, позволяет обес510 15 20 25 30 35 . 0

5

0 5

печить высокую чувствительность фильтра- реле тока в условиях изменения нагрузки. Формула изобретения Фильтр-реле тока, содержащий формирователь контролируемого сигнала, выполненный в виде входных преобразователей тока, подключенных входами к соответствующим трансформаторам тока линии, а выходами к входам фильтра симметричных составляющих, выход которого является выходом формирователя контролируемого сигнала и подключен к первому входу сумматора и через последовательно соединенные „первый элемент задержки и информационный вход ключа к второму входу сумматора, выход которого соединен с первым входом сравнивающего блока, выход которого соединен с входом реагирую- щего элемента, к выходам входных преобразователей тока формирователя контролируемого сигнала подключены последовательно соединенные фильтр прямой последовательности, амплитудный детектор и элемент задержки на срабатывание, выход последнего подключен к первому входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и первому входу элемента И-НЕ, второй вход которого соединен с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, а выход - с первым входом блока задания уставки и с входом первого элемента НЕ, выход которого подключен к второму входу блока задания уставки, выход которого соединен с первыми входами цифрового сумматора, к вторым входам которого подключен выход формирователя сигнала коррекции уставки, выполненного в виде генератора стабильной частоты и последовательно соединенных фазового детектора второго элемента задержки, R-входа счетчика и D-входов регистра памяти, причем первый и второй входы фазового детектора подключены соответственно к входу и выходу первого элемента задержки, выход генератора стабильной частоты подключен к S-входу счетчика, выход фазового детектора также подключен к С- входу регистра памяти, выход которого является выходом формирователя сигнала коррекции сигнала, выходы цифрового сумматора подключены к вторым входам сравнивающего блока, отличающийся тем, что, с целью повышения чувствительности в условиях изменения нагрузки, в него дополнительно введены формирователь средневып- рямленного значения, двухполупериодный выпрямитель, компаратор, RS-триггер, первый и второй элементы И и второй элемент НЕ, причем двухполупериодный выпрямитель входом подключен к выходу формирователя контролируемого сигнала, а выходом - к

первому ьходу компаратора, формирователь срёдневыпрямленного значения входом подключен к выходу первого элемента задержки, а выходом - к второму входу компаратора, выход которого подключен к $- входу RS-триггера, R-вход которого подключен к выходу первого элемента И, первый вход которого подключен к выходу элемента НЕ, вход которого соединен с управляющим входом ключа, с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и с выходом второго элемента И. который своим первым входом соединен с выходом реагирующего элемента, а вторым входом - с выходом RS-триггера. второй вход первого элемента И соединен с выходом генератора стабильной частоты формирователя сигнала коррекции уставки.

| название | год | авторы | номер документа |

|---|---|---|---|

| Фильтр - реле тока | 1989 |

|

SU1697138A1 |

| Фильтр-реле тока | 1987 |

|

SU1541700A1 |

| Измерительное устройство к балансировочному станку | 1984 |

|

SU1165905A1 |

| Устройство для защиты от замыканий на землю | 1987 |

|

SU1492409A1 |

| Аналого-цифровой частотомер | 1988 |

|

SU1712894A1 |

| Умножитель частоты | 1988 |

|

SU1608779A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ УГЛА | 1996 |

|

RU2115229C1 |

| ЦИФРОВОЕ РЕЛЕ ЧАСТОТЫ ВРАЩЕНИЯ С ФУНКЦИЕЙ РЕКОНСТРУКТИВНОЙ ДИАГНОСТИКИ | 2016 |

|

RU2618495C1 |

| ПИКОВЫЙ ДЕТЕКТОР | 2012 |

|

RU2506598C1 |

| Устройство для защиты фильтра высших гармоник | 1985 |

|

SU1297164A1 |

Сущность изобретения: введение канала, определяющего знак приращения амплитуды контролируемого сигнала и включающего формирователь средневып- рямленного значения, двухполупериодный выпрямитель, компаратор, RS-триггер, первый и второй элементы И, второй элемент НЕ, позволяет повысить чувствительность-в условиях изменения нагрузки. 1 ил.

| Фильтр-реле тока | 1987 |

|

SU1541700A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Фильтр - реле тока | 1989 |

|

SU1697138A1 |

Авторы

Даты

1993-05-07—Публикация

1991-02-04—Подача