Изобретение относится к средствам автоматизации и может быть использовано, в частности, в системах управления электроагрегатов генераторных с приводом от двигателя внутреннего сгорания.

Известны аналоговые реле частоты вращения (РЧВ) различного типа, содержащие измерительный преобразователь и выходной каскад, использующие различные способы измерения частоты /1, 2/.

Их недостатками являются ограниченные функциональные возможности, в частности достоверность выходной информации и точность настройки.

Известен цифровой измеритель скорости вращения, содержащий импульсный датчик, генератор эталонной частоты, счетчик импульсов, элемент задержки и электронные ключи /3/. Он обеспечивает удовлетворительную точность.

Его недостатком являются невысокие функциональные возможности, заключающиеся в наличии лишь одного выходного канала, и невысокая достоверность выходной информации.

Наиболее близким по технической сущности к изобретению является РЧВ с трехканальным выходом по числу уставок, содержащее формирователь коротких импульсов, преобразователь частоты в постоянное напряжение, три пороговых устройства с задатчиками уставок, шесть индикаторов состояния и выходное устройство с тремя каскадами /3/. Наличие трех выходных каналов расширяет возможности РЧВ.

Однако возможные сбои в измерительной части и в выходных каналах при отсутствии самодиагностики отражаются на достоверности выходной информации РЧВ и могут привести к сбою в работе системы управления.

Цель изобретения - расширение функциональных возможностей путем повышения достоверности выходной информации.

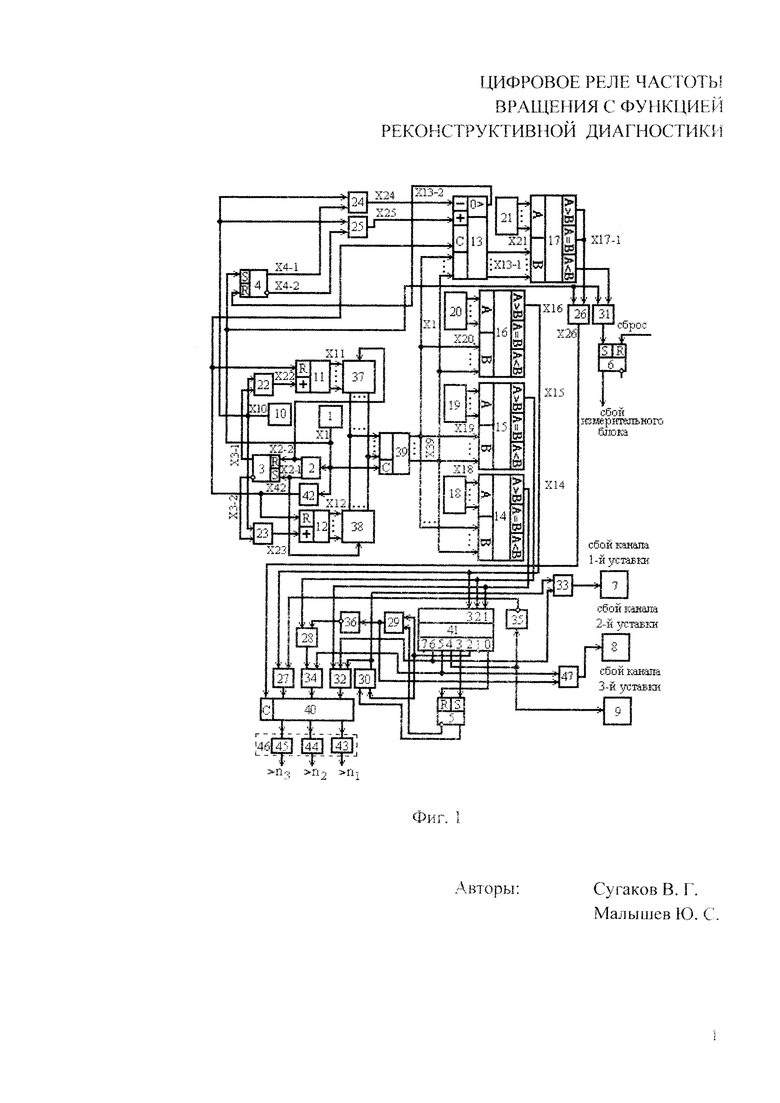

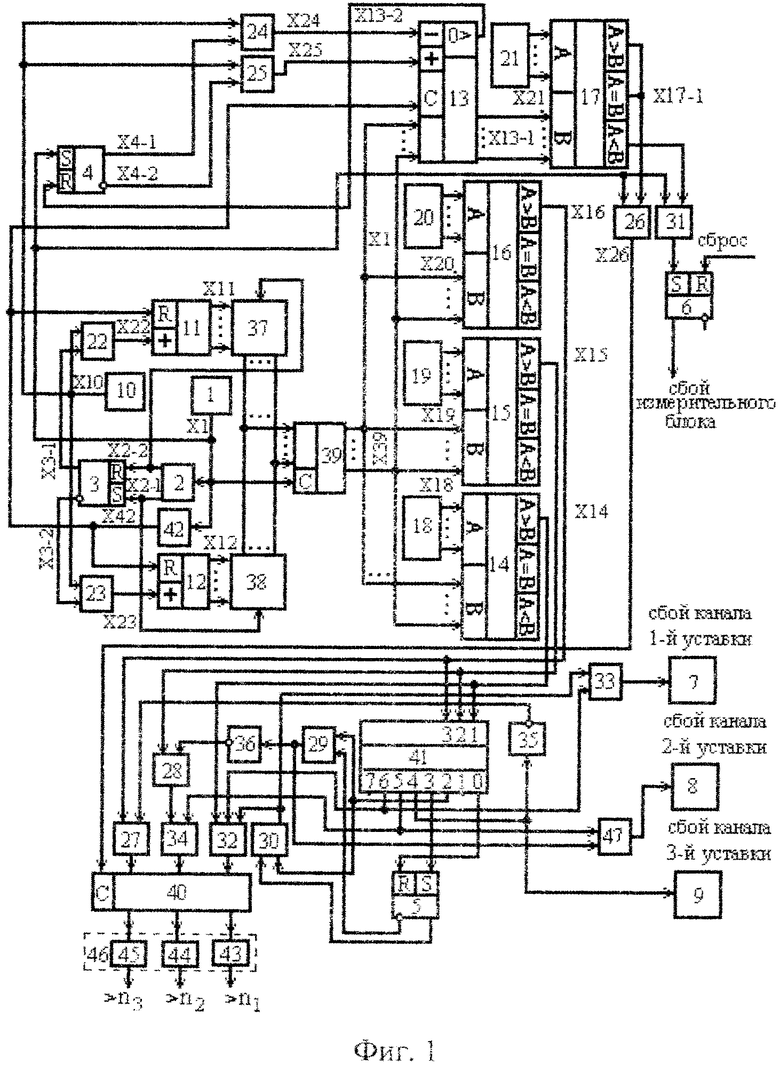

Цель изобретения достигается тем, что цифровое реле частоты вращения с функцией реконструктивной диагностики, содержащее формирователь коротких импульсов, первый, второй и третий числовые компараторы, к разрядам первых входов которых подключены соответствующие разряды выходов соответственно первого, второго и третьего задающего регистра и выходное устройство с тремя выходными каскадами, снабжено распределителем импульсов, с первого по четвертый RS-триггерами. генератором импульсов стабильной частоты, первым и вторым счетчиком импульсов, реверсивным счетчиком, четвертым числовым компаратором и четвертым задающим регистром, с первого по десятый логическими элементами И, с первого по четвертый логическими элементами ИЛИ, первым и вторым логическим элементом НЕ, первым и вторым электронным ключом, первым и вторым регистром памяти, дешифратором и элементом задержки, выход которого подключен к сбросовым входам первого и второго счетчика и входу записи исходного числа реверсивного счетчика, а вход соединен с выходом формирователя коротких импульсов, к которому так же подключены: вход распределителя импульсов, вход записи первого регистра памяти, единичный вход второго RS-триггера и первые входы пятого и десятого логического элемента И, вторые входы которых подключены соответственно к первому и третьему выходу четвертого числового компаратора, первый и второй выходы которого объединены, а разряды первого входа соединены с соответствующими разрядами выхода четвертого задающего регистра, разряды второго входа - с соответствующими разрядами выхода реверсивного счетчика, суммирующий вход которого подключен к выходу четвертого логического элемента И, вычитающий вход - к выходу третьего логического элемента И, а выход заема - к сбросовому входу второго RS-триггера, прямой и инверсный выходы которого соответственно соединены со вторыми входами третьего и четвертого логических элементов И, первые входы которых подключены к выходу генератора импульсов стабильной частоты, к которому так же подключены первые входы первого и второго логических элементов И, ко вторым входам которых подключены соответственно прямой и инверсный выходы первого RS-триггера, а к выходам - счетные входы соответственно первого и второго счетчика, разряды выходов которых соответственно через первый и второй электронные ключи подключены к соответствующим разрядам входа первого регистра памяти, причем управляющий вход первого электронного ключа связан со вторым выходом распределителя импульсов и сбросовым входом первого RS-триггера, а управляющий вход второго электронного ключа - с первым выходом распределителя импульсов и единичным входом первого RS-триггера, кроме того, соответствующие разряды выхода первого регистра памяти подключены к соответствующим разрядам входа исходного числа реверсивного счетчика и вторых входов первого, второго и третьего числовых компараторов, выходы БОЛЬШЕ которых подключены соответственно к первому, второму и третьему разрядам входа дешифратора, нулевой выход которого подключен к сбросовому входу третьего RS-триггера, инверсный выход которого соединен с первым входом восьмого логического элемента И, прямой выход - с первым входом девятого логического элемента И, а единичный вход - с третьим выходом дешифратора, второй выход которого подключен к вторым входам восьмого и девятого логического элемента И, четвертый выход - к входу третьего индикатора, входу первого логического элемента НЕ, выход которого подключен ко второму входу шестого логического элемента И, соединенного первым входом с выходом третьего числового компаратора, а выходом - с третьим разрядом входа второго регистра памяти, первый, второй и третий разряды выхода которого подключены соответственно к входам первого, второго и третьего выходного каскада, второй разряд входа - к выходу третьего логического элемента ИЛИ, а первый разряд входа - к выходу первого логического элемента ИЛИ, первый вход которого связан с выходом первого числового компаратора, второй вход - с вторым входом второго логического элемента ИЛИ и шестым выходом дешифратора, пятый выход которого соединен со вторым входом третьего логического элемента ИЛИ и первым входом четвертого логического элемента ИЛИ, выход которого подключен к входу второго индикатора, а второй вход - к выходу восьмого логического элемента И, связанного с входом второго логического элемента НЕ, выход которого соединен со вторым входом седьмого логического элемента И, подключенного выходом к первому входу третьего логического элемента ИЛИ, а первым входом - к выходу второго числового компаратора, кроме того, выход девятого логического элемента И связан с третьим входом первого логического элемента ИЛИ и первым входом второго логического элемента ИЛИ, связанного выходом со входом первого индикатора, а выход десятого логического элемента И соединен с единичным входом четвертого RS-триггера, сбросовый вход которого подключен к шине сброс, а выход пятого логического элемента И - к входу записи второго регистра памяти.

Генератор импульсов стабильной частоты, распределитель импульсов, первый и второй счетчики, первый и второй логические элементы И, первый и второй электронные ключи, элемент задержки, первые RS-триггер и регистр памяти с их связями образуют измерительный блок реле. Он выдает цифровую информацию о частоте вращения. Третий, четвертый, пятый и десятый логические элементы И, второй и четвертый RS-триггеры, реверсивный счетчик, четвертые числовой компаратор и задающий регистр и их связи образуют блок диагностики измерительного блока реле. Он контролирует работу измерительного блока и предотвращает прохождение недостоверной информации. Дешифратор, второй регистр памяти, шестой, седьмой, восьмой и девятый логические элементы И, первый, второй, третий и четвертый логические элементы ИЛИ, первый и второй логические элементы НЕ и третий RS-триггер с их связями образуют блок диагностики каналов уставок реле. Он контролирует исправность каналов уставок и корректирует выходную информацию при возникновении сбоев.

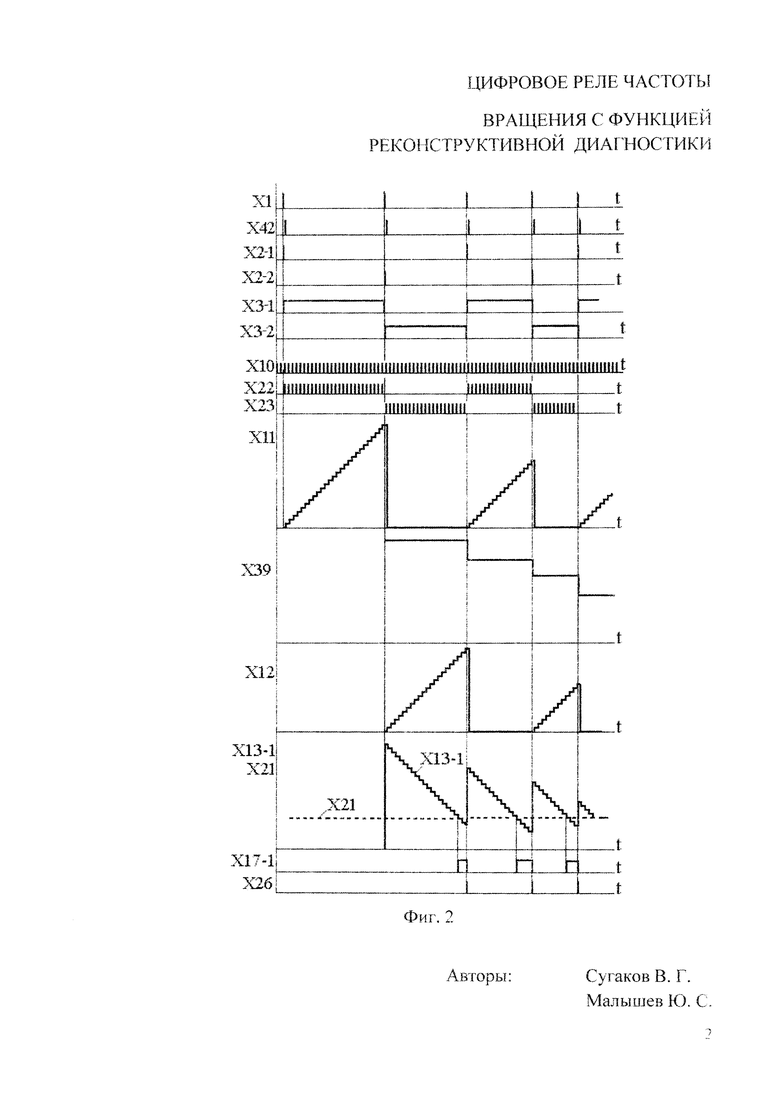

На фиг. 1 представлена схема цифрового реле частоты вращения (ЦРЧВ), на фиг. 2 - эпюры сигналов на основных элементах устройства.

ЦРЧВ (фиг. 1) включает формирователь коротких импульсов 1, распределитель импульсов 2, первый 3, второй 4, третий 5 и четвертый 6 RS-триггеры, первый 7, второй 8 и третий 9 индикаторы состояния, генератор 10 импульсов стабильной частоты, первый 11 и второй 12 счетчики импульсов, реверсивный счетчик 13, первый 14, второй 15, третий 16 и четвертый 17 числовые компараторы, первый 18, второй 19, третий 20 и четвертый 21 задающие регистры, первый 22, второй 23, третий 24, четвертый 25, пятый 26, шестой 27, седьмой 28, восьмой 29, девятый 30 и десятый 31 логические элементы И, первый 32, второй 33 и третий 34 логические элементы ИЛИ, первый 35 и второй 36 логические элементы НЕ, первый 37 и второй 38 электронные ключи, первый 39 и второй 40 регистры памяти, дешифратор 41 и элемент задержки 42, первый 43, второй 44 и третий 45 выходные каскады, которые образуют выходное устройство 46, четвертый логический элемент ИЛИ 47.

ЦРЧВ работает следующим образом. На выходах задающих регистров 18, 19 и 20 соответственно устанавливают коды частоты вращения нижней X18, средней X19 и верхней Х20 уставок. При этом выполняется соотношение кодов X18>Х19>Х20. На выходе задающего регистра 21 устанавливают код Х21 предельно возможного приращения частоты вращения за время между импульсами на выходе формирователя 1. С началом вращения вала контролируемого объекта появляются импульсы X1 на выходе формирователя 1, интервал между которыми равен периоду вращения или фиксированной части этого периода.

При появлении первого импульса X1 появляется импульс Х2-1 на первом выходе распределителя 2, которым триггер 3 переводится в единичное состояние, и появляется сигнал Х3-1 на его прямом выходе, подготавливающий элемент И22 по второму входу. На счетный вход счетчика 11 через элемент И22 начинают поступать импульсы Х10 с выхода 10 генератора импульсов. На выходе счетчика 11 начинает формироваться код X11 текущей частоты (периода) вращения.

С приходом второго импульса X1 с выхода формирователя 1 появляется импульс Х2-2 на втором выходе распределителя 2, поступающий на сбросовый вход триггера 3, который, меняя состояние, подготавливает по второму входу элемент И23 и закрывает элемент И22, завершая формирование кода X11 текущей частоты на выходе счетчика 11. Одновременно импульс Х2-2 со второго выхода распределителя 2 открывает электронный ключ 37, а импульс X1 с выхода формирователя 1 записывает в регистр 39 код текущей частоты с выхода счетчика 11. После чего счетчик 11 обнуляется импульсом Х42 с выхода элемента задержки, подготавливаясь к очередному циклу формирования кода частоты.

Через элемент И23, подготовленный по второму входу сигналом Х3-2 с инверсного выхода триггера 3, начинают поступать импульсы с выхода генератора 10 на счетный вход счетчика 12, на выходе которого формируется очередной код Х12 частоты до появления следующего импульса X1 на выходе формирователя 1. С его приходом импульсом Х2-1 с первого выхода распределителя 2 триггер 3 переходит в единичное состояние и элемент И23 закрывается по второму входу. В то же время открывается электронный ключ 38 и с выхода счетчика 12 в регистр 39 переписывается очередное значение кода текущей частоты. Далее процесс поочередного формирования кода на выходах счетчиков 11 и 12 повторяется. В результате измерительная часть реле обеспечивает на выходе регистра 39 постоянное присутствие кода Х39 текущей частоты вращения. Код Х39 с выхода регистра 39 поступает на вторые входы компараторов 14, 15 и 16, где сравнивается с кодами X18, Х20 и Х21 уставок частоты, поданными на первые входы компараторов с выходов регистров 18, 19 и 20 соответственно.

Результаты обработки кода частоты поступят на выход реле и далее в систему управления при условии исправности измерительной части, что оценивается по величине приращения кода частоты следующим образом.

Сформированный в предыдущем цикле измерения, например на выходе счетчика 11, код частоты X11 (фиг. 2) заносится в регистр 39 импульсом X1 с выхода формирователя и далее в реверсивный счетчик 13 импульсом Х42 с выхода элемента задержки 42. Одновременно с приходом импульса X1 с выхода формирователя 1 начинается формирование очередного кода частоты, а триггер 4 переводится в единичное состояние, подготавливая по второму входу элемент И24. Через первый вход элемента И24 с выхода генератора 10 на вычитающий вход счетчика 13 начинают поступать импульсы, и код X13-1 на выходе счетчика 13 уменьшается. К концу (i+l)-гo цикла измерения частоты на выходе счетчика 13 формируется код разности кодов частоты, сформированных при предыдущем X39i и последующем X39i+1 измерении, X13-li+1=|X39i-X39i+1|. Этот код характеризует приращение частоты. Он поступает на второй вход компаратора 17 и сравнивается с кодом Х21 (фиг. 2) допустимого приращения частоты (периода), поданным на первый вход компаратора 17 с выхода регистра 21.

Если произошел сбой в измерительной части реле и очередное измерение частоты имеет запредельное приращение, то к моменту завершения цикла измерения, когда появится импульс X1, элемент И31 будет подготовлен сигналом X17-2 со второго выхода компаратора 17. Импульс X1 с выхода формирователя 1 через элемент И31 поступит на единичный вход триггера 6, который изменит свое состояние и выдаст сигнал «сбой измерительного блока» в систему управления. Одновременно компаратором 17 блокируется элемент И26, препятствуя записи в регистр 40 недостоверной информации.

Если приращение частоты (периода) соответствует механической постоянной времени контролируемого объекта, то к моменту завершения цикла измерения появляется сигнал X17-1 (фиг. 2) на первом выходе компаратора 17, который подготавливает по второму входу элемент И26. С приходом импульса X1 с выхода формирователя 1 элемент И26 открывается и подает импульс Х26 на вход записи регистра 40, в который записывается новая информация.

Если контролируемая частота вращения снижается, то в процессе счета на информационном выходе счетчика 13 появляется нулевой код и далее появляется сигнал X13-2 на выходе заема, который поступает на сбросовый вход триггера 4. Сигнал на прямом выходе триггера 4 исчезает, закрывая элемент И24, и появляется сигнал на инверсном выходе триггера 4, подготавливающий элемент И25 по второму входу. Счетчик 13 меняет направления счета. Импульсы с выхода генератора 10 через элемент И25 поступают на суммирующий вход счетчика 13 и к концу цикла измерения на его выходе формируется код приращения частоты. Далее он анализируется, как описано выше при возрастающей частоте.

Анализ исправности каналов уставок реле осуществляется по последовательности появления сигналов уставок.

При монотонном возрастании частоты вращения вала контролируемого объекта код Х39 частоты (периода) соответственно уменьшается. В начальный момент разгона вала на выходах компараторов 14, 15 и 16 сигналы X14, X15 и X16 отсутствуют и на разрядах входа дешифратора 41 оказывается нулевой код (0002). По мере разгона появляется сигнал Х14 на выходе компаратора 14, который поступает на младший разряд входа дешифратора 41 (код на входе дешифратора 0012). Дальнейшее увеличение частоты приводит к появлению сигнала X15 на выходе компаратора 15, а на входе дешифратора появляется код 0112. При достижении третей уставки частоты дополнительно появляется сигнал X16 на выходе компаратора 16 и на вход дешифратора поступает код 1112. Последовательность появления кодов 0002, 0012, 0112 и 1112 является естественной последовательностью кодов при разгоне и исправности каналов уставок. Они без коррекции записываются в регистр 40 и выдают сигналы на выходные каскады 43, 44 и 45 следующим образом.

При наличии кода 0002 на входе дешифратора 41 появляется сигнал на его нулевом выходе, которым триггер 5 переводится в нулевое состояние. Элемент И30 закрыт по первому входу. На входах элемента ИЛИ 32 сигналы отсутствуют, поэтому на первом разряде входа регистра 40 сигнал «0». Элемент И28 закрыт по первому входу сигналом X15 и сигнал на его выходе отсутствует. На входах элемента ИЛИ 34 сигналы отсутствуют, поэтому на втором разряде регистра 40 сигнал «0». Элемент И27 закрыт сигналом X16, поэтому на третьем разряде входа регистра 40 также присутствует «0». С приходом сигнала на вход записи в регистр 40 заносится код 0002 и на выходные каскады 43, 44 и 45 сигналы не поступают.

При появлении на входе дешифратора 41 кода 0012 сигнал перемещается на первый его выход. Сигнал X14 с выхода компаратора 14 через элемент ИЛИ 32 поступает на первый разряд входа регистра 40. Уровень сигналов на втором и третьем разряде входа регистра 40 не изменяется и в него записывается 0012. На выходной каскад 43 первой уставки поступает сигнал.

С появлением на входе дешифратора 41 кода 0112 сигнал перемещается на третий его выход и переводит триггер 5 в единичное состояние. Элемент И29 закрыт, сигнал на его выходе отсутствует. Появляется сигнал на выходе элемента НЕ 36, который подготавливает элемент И28 по второму входу. Через элемент И28 и элемент ИЛИ 34 с выхода компаратора 15 поступает сигнал на второй разряд входа регистра 40. На первом и третьем разряде входа регистра 40 сигналы не меняются. В регистр 40 заносится код 0112, на выходные каскады 43 и 44 подаются сигналы.

При наличии кода 1112 на входе дешифратора 41 появляется сигнал на его седьмом выходе. Сигнал на входе элемента НЕ 35 отсутствует и с его выхода сигнал подготавливает по второму входу элемент И27. Через него на третий разряд входа регистра 40 поступает сигнал Х16 с выхода компаратора 16. На первом и втором разряде входа регистра 40 сигналы не меняются. В регистр 40 заносится код 1112, с подачей сигналов на выходные каскады 43, 44 и 45.

Появление на входе дешифратора 41 дефектных кодов (0102, 1002, 1012 и 1102), не входящих в естественную последовательность, служит признаком выхода из строя канала определенной уставки. В этом случае до записи в регистр 40 код требует коррекции следующим образом.

Код 0102 на входе дешифратора 41 возникает при сбое в канале второй или первой уставки. В обоих случаях появляется сигнал на втором выходе дешифратора 41, который подготавливает по вторым входам элементы И29 и 30. Если коду 0102 предшествовал код 0002, при котором триггер 5 переходит в сбросовое состояние, то появляется сигнал на выходе элемента И29, который поступает через элемент ИЛИ 47 на индикатор 8, указывая причину неисправности «сбой канала 2-й уставки». В то же время исчезает сигнал на выходе элемента НЕ 36, закрывая элемент И28. На входах элемента ИЛИ 31 сигналы отсутствуют, поэтому на вход второго разряда регистра 41 подается «0» и в него записывается исправленный код 0002. Если коду 0102 предшествовал код 0112, при котором триггер 5 переводится в единичное состояние, то появляется сигнал на выходе элемента И30. Сигнал с выхода элемента И30 через элемент ИЛИ 33 поступает на вход индикатора 7 для указания поврежденной части реле «сбой канала 1-й уставки», а через элемент ИЛИ 32 - на первый разряд входа регистра 40 для коррекции кода. В регистр 40 заносится исправленный код 0112.

Код 1002 возникает на входе дешифратора 41 при сбое в канале третей уставки. Сигнал появляется на четвертом выходе дешифратора 41 и поступает на вход индикатора состояния 9, указывая причину неисправности «сбой канала 3-й уставки». Одновременно поступает сигнал на вход элемента НЕ 35 и сигнал на его выходе исчезает, закрывая элемент И27. В регистр 40 записывается откорректированный код 0002.

Причиной установки кода 1012 на входе дешифратора 41 является сбой в канале второй уставки. В этом случае появляется сигнал на пятом выходе дешифратора. Он поступает через элемент ИЛИ 47 на индикатор 8 для указания причины неисправности «сбой канала 2-й уставки» и через элемент ИЛИ 34 на второй разряд входа регистра 40, в который заносится исправленный код 1112.

Код 1102 поступает на вход дешифратора 41 при сбое в канале первой уставки. При этом сигнал с шестого выхода дешифратора 41 поступает через элемент ИЛИ 33 на индикатор 7 для указания причины неисправности «сбой канала 1-й уставки». Одновременно этот сигнал поступает через элемент ИЛИ 32 на первый разряд входа регистра 40 для коррекции кода. В регистр 40 записывается исправленный код 1112.

В результате происходит коррекция каждого дефектного кода и выдача на выходное устройство 46 достоверной информации.

Таким образом, реле имеет расширенные функциональные возможности, заключающиеся в повышении достоверности выходной информации путем введения функций диагностики измерительной части и каналов уставок реле и коррекции информации при сбоях.

Источники информации

1. Сугаков В.Г. Основы автоматизации военных передвижных источников электрической энергии: учеб. пособие. - Кстово: НФВИУ, 2003, 168 с.

2. Дудченко В.К, Аверкиев А.Н. Измерение неэлектрических величин: конспект лекций. - Кстово: НВВИКУ, 1997, 54 с.

3. Цифровой измеритель скорости вращения. Описание изобретения к авторскому свидетельству RU 1075167, 1984.

4. Комплекс средств контроля дизеля КСКД 17.5. Техническое описание и инструкция по эксплуатации ЗУ2.008.006 ТО. 1994. С. 35-37.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЕ ПЯТИКАНАЛЬНОЕ РЕЛЕ С ФУНКЦИЕЙ САМОДИАГНОСТИКИ | 2017 |

|

RU2671545C1 |

| ЦИФРОВОЕ N-КАНАЛЬНОЕ РЕЛЕ С ФУНКЦИЕЙ САМОДИАГНОСТИКИ | 2018 |

|

RU2685445C1 |

| ЦИФРОВОЕ ЧЕТЫРЕХКАНАЛЬНОЕ РЕЛЕ С ФУНКЦИЕЙ РЕКОНСТРУКТИВНОЙ ДИАГНОСТИКИ | 2017 |

|

RU2659990C1 |

| ДВУНАПРАВЛЕННОЕ УСТРОЙСТВО ДОПУСКОВОГО КОНТРОЛЯ ПЕРЕХОДНОГО ОТКЛОНЕНИЯ ЧАСТОТЫ | 2024 |

|

RU2826860C1 |

| УСТРОЙСТВО ДОПУСКОВОГО КОНТРОЛЯ УСТАНОВИВШЕГОСЯ ОТКЛОНЕНИЯ ЧАСТОТЫ | 2022 |

|

RU2795501C1 |

| УСТРОЙСТВО ДОПУСКОВОГО КОНТРОЛЯ ПЕРЕХОДНОГО ОТКЛОНЕНИЯ ЧАСТОТЫ ДВУНАПРАВЛЕННОЕ | 2024 |

|

RU2819573C1 |

| ИЗМЕРИТЕЛЬ ЧАСТОТЫ ВРАЩЕНИЯ ВАЛА | 1993 |

|

RU2084899C1 |

| ДВУНАПРАВЛЕННОЕ УСТРОЙСТВО ДОПУСКОВОГО КОНТРОЛЯ ВРЕМЕНИ ВОССТАНОВЛЕНИЯ ЧАСТОТЫ | 2023 |

|

RU2817045C1 |

| ДВУЗОННОЕ УСТРОЙСТВО ДОПУСКОВОГО КОНТРОЛЯ УСТАНОВИВШЕГОСЯ ОТКЛОНЕНИЯ ЧАСТОТЫ | 2023 |

|

RU2799658C1 |

| УСТРОЙСТВО ДОПУСКОВОГО КОНТРОЛЯ ВРЕМЕНИ ВОССТАНОВЛЕНИЯ ЧАСТОТЫ ДВУНАПРАВЛЕННОЕ | 2024 |

|

RU2820839C1 |

Изобретение относится к средствам автоматизации и может быть использовано, в частности, в системах управления электроагрегатов генераторных с приводом от двигателя внутреннего сгорания. Схема устройства включает формирователь коротких импульсов 1, распределитель импульсов 2, первый 3, второй 4, третий 5 и четвертый 6 RS-триггеры, первый 7, второй 8 и третий 9 индикаторы состояния, генератор 10 импульсов стабильной частоты, первый 11 и второй 12 счетчики импульсов, реверсивный счетчик 13, первый 14, второй 15, третий 16 и четвертый 17 числовые компараторы, первый 18, второй 19, третий 20 и четвертый 21 задающие регистры, первый 22, второй 23, третий 24, четвертый 25, пятый 26, шестой 27, седьмой 28, восьмой 29, девятый 30 и десятый 31 логические элементы И, первый 32, второй 33 и третий 34 логические элементы ИЛИ, первый 35 и второй 36 логические элементы НЕ, первый 37 и второй 38 электронные ключи, первый 39 и второй 40 регистры памяти, дешифратор 41 и элемент задержки 42, первый 43, второй 44 и третий 45 выходные каскады, которые образуют выходное устройство 46, четвертый логический элемент ИЛИ 47. Реле имеет расширенные функциональные возможности, заключающиеся в повышении достоверности выходной информации путем введения функций диагностики измерительной части и каналов уставок реле и коррекции информации при сбоях. Техническим результатом заявленного изобретения является расширение функциональных возможностей путем повышения достоверности выходной информации. 2 ил.

Цифровое реле частоты вращения с функцией реконструктивной диагностики, содержащее формирователь коротких импульсов, первый, второй и третий числовые компараторы, к разрядам первых входов которых подключены соответствующие разряды выходов соответственно первого, второго и третьего задающего регистра, выходное устройство с тремя выходными каскадами и три индикатора, отличающееся тем, что с целью расширения функциональных возможностей путем повышения достоверности выходной информации снабжено распределителем импульсов, с первого по четвертый RS-триггерами. генератором импульсов стабильной частоты, первым и вторым счетчиком импульсов, реверсивным счетчиком, четвертым числовым компаратором и четвертым задающим регистром, с первого по десятый логическими элементами И, с первого по четвертый логическими элементами ИЛИ, первым и вторым логическим элементом НЕ, первым и вторым электронным ключом, первым и вторым регистром памяти, дешифратором и элементом задержки, выход которого подключен к сбросовым входам первого и второго счетчика и входу записи исходного числа реверсивного счетчика, а вход соединен с выходом формирователя коротких импульсов, к которому так же подключены: вход распределителя импульсов, вход записи первого регистра памяти, единичный вход второго RS-триггера и первые входы пятого и десятого логического элемента И, вторые входы которых подключены соответственно к первому и третьему выходу четвертого числового компаратора, первый и второй выходы которого объединены, а разряды первого входа соединены с соответствующими разрядами выхода четвертого задающего регистра, разряды второго входа - с соответствующими разрядами выхода реверсивного счетчика, суммирующий вход которого подключен к выходу четвертого логического элемента И, вычитающий вход - к выходу третьего логического элемента И, а выход заема - к сбросовому входу второго RS-триггера, прямой и инверсный выходы которого соответственно соединены со вторыми входами третьего и четвертого логических элементов И, первые входы которых подключены к выходу генератора импульсов стабильной частоты, к которому так же подключены первые входы первого и второго логических элементов И, ко вторым входам которых подключены соответственно прямой и инверсный выходы первого RS-триггера, а к выходам - счетные входы соответственно первого и второго счетчика, разряды выходов которых соответственно через первый и второй электронные ключи подключены к соответствующим разрядам входа первого регистра памяти, причем управляющий вход первого электронного ключа связан со вторым выходом распределителя импульсов и сбросовым входом первого RS-триггера, а управляющий вход второго электронного ключа - с первым выходом распределителя импульсов и единичным входом первого RS-триггера, кроме того, соответствующие разряды выхода первого регистра памяти подключены к соответствующим разрядам входа исходного числа реверсивного счетчика и вторых входов первого, второго и третьего числовых компараторов, выходы БОЛЬШЕ которых подключены соответственно к первому, второму и третьему разрядам входа дешифратора, нулевой выход которого подключен к сбросовому входу третьего RS-триггера, инверсный выход которого соединен с первым входом восьмого логического элемента И, прямой выход - с первым входом девятого логического элемента И, а единичный вход - с третьим выходом дешифратора, второй выход которого подключен к вторым входам восьмого и девятого логического элемента И, четвертый выход - к входу третьего индикатора, входу первого логического элемента НЕ, выход которого подключен ко второму входу шестого логического элемента И, соединенного первым входом с выходом третьего числового компаратора, а выходом - с третьим разрядом входа второго регистра памяти, первый, второй и третий разряды выхода которого подключены соответственно к входам первого, второго и третьего выходного каскада, второй разряд входа - к выходу третьего логического элемента ИЛИ, а первый разряд входа - к выходу первого логического элемента ИЛИ, первый вход которого связан с выходом первого числового компаратора, второй вход - с вторым входом второго логического элемента ИЛИ и шестым выходом дешифратора, пятый выход которого соединен со вторым входом третьего логического элемента ИЛИ и первым входом четвертого логического элемента ИЛИ, выход которого подключен к входу второго индикатора, а второй вход - к выходу восьмого логического элемента И, связанного с входом второго логического элемента НЕ, выход которого соединен со вторым входом седьмого логического элемента И, подключенного выходом к первому входу третьего логического элемента ИЛИ, а первым входом - к выходу второго числового компаратора, кроме того, выход девятого логического элемента И связан с третьим входом первого логического элемента ИЛИ и первым входом второго логического элемента ИЛИ, связанного выходом со входом первого индикатора, а выход десятого логического элемента И соединен с единичным входом четвертого RS-триггера, сбросовый вход которого подключен к шине сброс, а выход пятого логического элемента И - к входу записи второго регистра памяти.

| ИЗМЕРИТЕЛЬ ЧАСТОТЫ ВРАЩЕНИЯ ВАЛА | 1993 |

|

RU2084899C1 |

| Цифровой измеритель частоты вращения | 1989 |

|

SU1697009A1 |

| WO 8600714 A1, 30.01.1986 | |||

| US 0004615410 A1, 07.10.1986. | |||

Авторы

Даты

2017-05-03—Публикация

2016-03-30—Подача