Изобретение отнорится к радиотехнике и может быть использовано в различных устройствах автоматики и измерительной техники.

Цель изобретения - повышение точности умножения при изменении частоты входных сигналов.

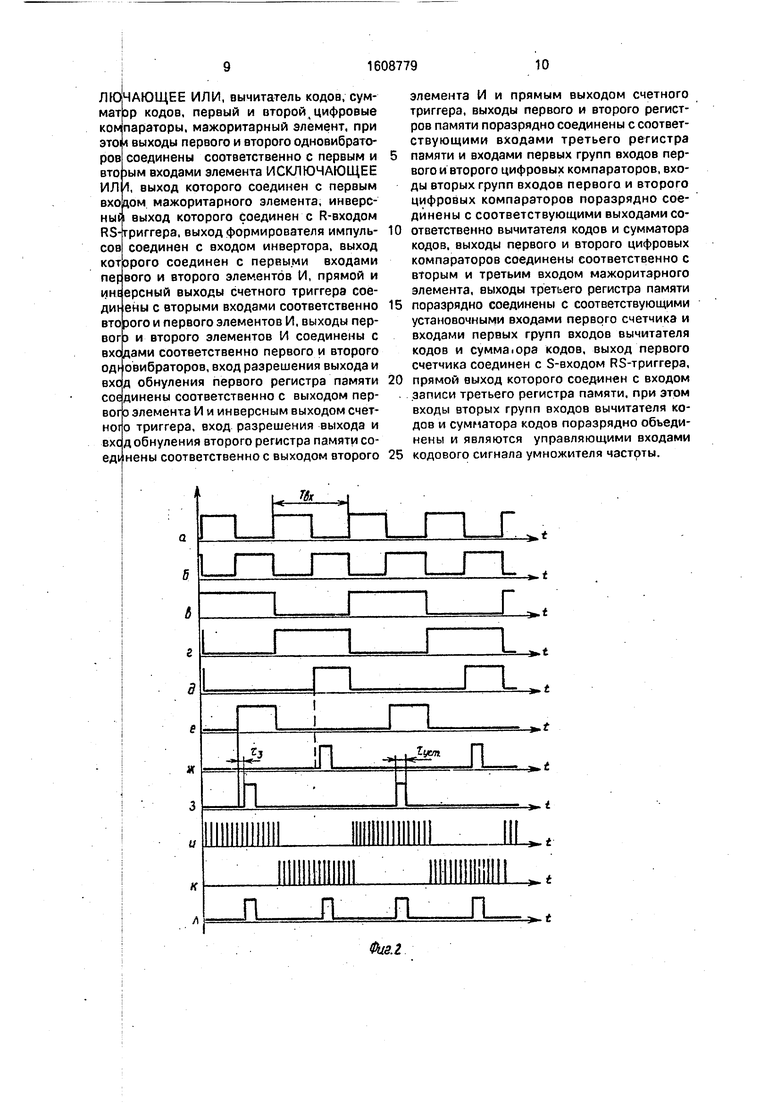

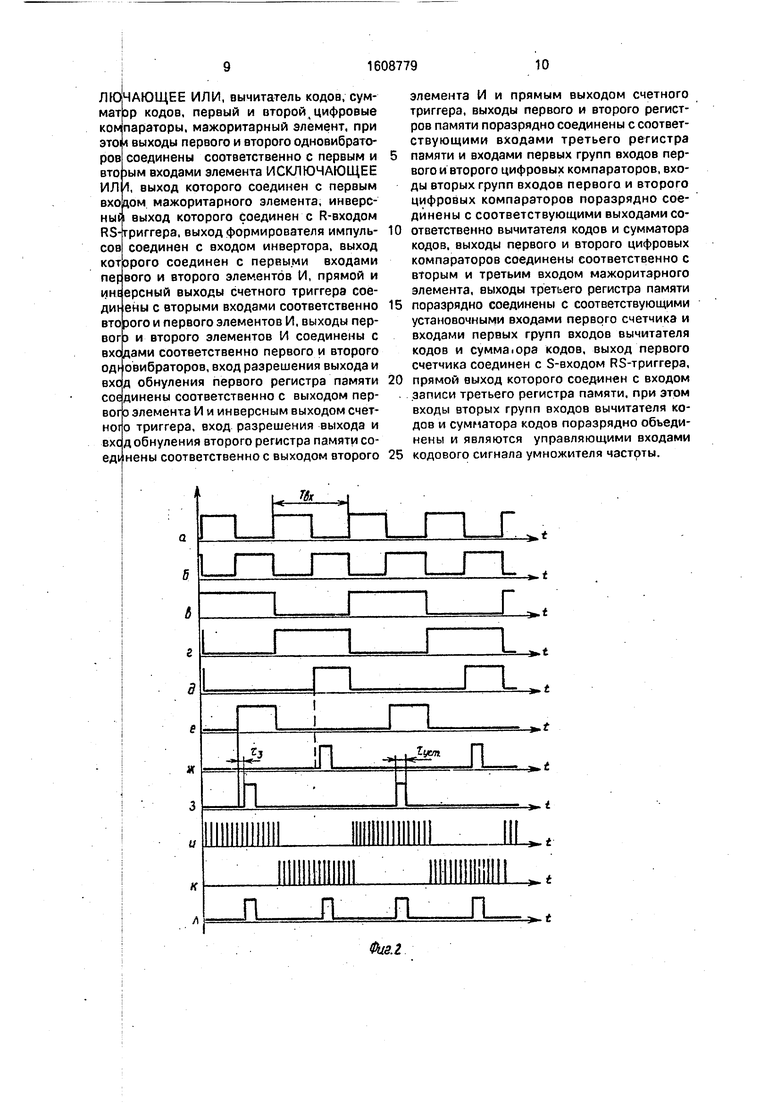

На фиг, 1 представлена схема умножителя частоты; на фиг. 2 - эпюры.

Умножитель частоты содержит формирователь 1 импульсов, генератор 2 тактовых импульсов, инвертор 3, счетный триггер 4, второй 5 и первый 6 ключи, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 7, первый 8 и второй 9 элементы И, первый одновибратор 10, второй счетчик 11, первый регистр 12 памяти, вычитатель 13 кодов, п.ервый цифровой ком- паратор 14, мажоритарный элемент 15. второй одновибратор 16, третий счетчик 17, второй 18. третий 19 регистры памяти, сумматор 20 кодов,-цифровой компаратор 21, RS-Tpvirrep 22. делитель 23 частоты, фазовый детектор 24. фильтр 25 нижних частот, управляемый генератор 26, первый счетчик 27. Измерение длительности нечетных периодов осуществляется схемой, состоящей из ключа 6 м счетчика 11, а четных периодов ключом 5 и счетчиком 17. Коды с выходов счетчиков 11 и17заносятсяврегистры 12и 18 соответственно и определяют коэффициент деления счетчика 27, Сущность изобретения состоит в исключении влияния погрешности квантования каждого периода входного сигнала, на текущее значение коэффициента деления счетчика 27, который сохраняется постоянным при отклонении результата измерения очередного периода входной частоты.

Умножитель частоты работает следующим образом.

Поступающий на вход устройства сигнал преобразуется формирователем 1 к нормированному значению уровня и длительности перепада (фиг.2а).

Предположим, что до поступления импульсов с выхода формирователя .1 счетный триггер 4 находится в состоянии логического . О. Пусть в этом случае первый ключ 6 закрыт; а второй ключ 5 открыт. Изменение состояния счетного триггера 4 осуществляется, например, положительным перепадом уровня выходного сигнала формирователя 1. С поступлением первого (и затем каж- дого нечетного) положительного перепада уровня выходного сигнала формирователя 1 счетный триггер 4 устанавливается в состояние логической 1. открывая первый ключ 6 и закрывая второй ключ 5. Второй (и каж- дый четный) такой перепад возвращает счетный триггер 4 в состояние логическо р

О. При этом на выходе счетного триггера 4 формируются импульсы , длительность которых равна периоду входного сигнала Твх (фиг.2в).

Измерение длительности каждого нечетного периода входного сигнала осуществляется подсчетом числа квантующих имп ульсов, прошедших через открытый первый ключ 6 от генератора тактовых импульсов 2 на вход вто- 0 рого счетчика 11 (фиг.2и). Длительность каждого нечетного периода входного сигнала измеряется аналогично схемой, состоящей из второго ключа 5 и третьего счетчика 17.

В течение первого периода входного сиг- 5 нала Твх1 количество квантующих импульсов с периодом То, поступивших на вход второго счетчика 11 через первый ключ 6, равно

Ni TBxi/To±1.

Частота fan 1/То выходного сигнала 0 генератора тактовых импульсов 2 выбирается исходя из условия обеспечения допустимого значения погрешности от квантования при измерении минимальной длительности периода входного сигнала. 5 После окончания первого (каждого нечетного) периода входного сигнала и установки счетного триггера 4 в состояние логического О разрядные выходы первого регистра 12 переходят в высокоимпеданс- 0 ное состояние и отключаются от шины данных, образованной соединенными между собой соответствующими выходами первого 12 и второго 18 регистров, входами первых групп входов первого 14 и- второго 21 5 цифровых компараторов, а также входами третьего регистра 19. Подключение первого регистра 12 осуществляется низким уровнем инверсного выходного сигнала U4(t) (фиг,26) счетного триггера 4, а подключение 0 второго регистра 18 - низким уровнем прямого выходного сигнала U4(t) счетного триггера 4.

На второй вход первого элемента И 8 устанавливается уровень логической Г. С 5 поступлением уровня логической 1 U3(t) (фиг.26) с выхода инвертора 3 на первый вход элемента И 8 на выходе последнего формируется прямоугольный сигнал U8(t) (фиг.2г,д), положительный перепад которого 50 запускает первый одновибратор 10 и осуществляет запись кода Ni в первый регистр 12. Первый одновибратор 10 с задержкой Гз, равной времени записи кода Ni в первый регистр 12, формирует импульсы Uio(t) 55 (фиг.2ж) длительностью Туст , обнуляющие второй счетчик 11, подготавливая его тем самым к измерению очередного нечетного периода входного сигнала (в данном случае

ТвхЗ).

I В течение второго (и каждого четного) периода Твх2 входного сигнала на вход вто- ро го регистра 18 через второй ключ 5 поступают импульсы и5(0(фиг.2к) от генератора 2 тестовых импульсов, количество которых равно

М2 Твх2/То-И.

в момент начала третьего периода третьим положительнь1м перепадом уровня выходного напряжения формирователя 1 счетный триггер 4 устанавливается в состо- логической Г. При этом разрядные выходы первого регистра 12 подключаются, а разрядные выходы второго регистра 18 отключаются от шины данных. С поступлением на первый вход второго элемента И 9 с 1 ыхода инвертора 3 уроьня логической 1 нл ее выходе формируется прямоугольное напряжение UsW (фиг.2е), положительные п(1репады которого запускают второй одно- вибратор 16 и осуществляют запись резуль- тгта измерения второго (каждого четного) п(риода Na во второй регистр 18. Второй одновибратор 16с задержкой з формирует импульсы Ui6{t). обнуляющие третий счет-, чик 17.

После подключения выходов первого р(гистра 12 осуществляется сравнение кода NI с текущим значением кода NT, который записан в третьем регистре 19 и определяет коэффициент деления первого счетчика 27. Е:лиотклонение значения кода Ni отзначе- н 1я кода NT превышает по модулю установ- Л1;нное пороговое значение Nnop, то код Ni записывается в третий регистр 19. в против- нзм случае в третьем регистре 19 остается з тисанным код NT.

Код NT с выхода третьего регистра 19 пэступает на входы первой груп пы входов в з)читателя 13 и входы первой группы вхо- дэв сумматора 20, а также на соответствую- и1ие установочные входы первого счетчика ...

На выходах вычитат.еля 13 формируется нижнее граничное значение кода NT - Nnop. кэторое сравнивается с первым цифровым компаратором 14 с кодом. NI. Если T-Nrtop N1, то на выходе первого цифрового компаратора 14 устанавливается уро- бень логической 1, если NT-Nnop N1 - уровень логического О. На выходах 20 фор- иpyeтcя верхнее граничное значение кода h т + Nnop. которое также сравнивается со значением кода Ni вторым цифровым компаратором 21. Если NT + Nnop NI, то на выходе второго цифрового компаратора 21 формируете уровень логической 1, если Мт + Nnop Ji уровень логического О.

Выходные напряжения первого 14 и Еторого 21 цифровых компараторов подаются на второй и третий входы мажоритар- ного элемента 15 соответственно. На первый вход этого элемента поступает стробирую- щий импульс U7(t) (фиг.2л), формируемый

элементом ИСКЛЮЧАЮЩЕЕ ИЛИ 7 (к входам этого элемента подключены выходные сигналы Uio(t) (фиг.2ж) и Ui6(t) {фиг.2з) первого и второго одновибраторов 10 и 16 соот: ветственно).

Допустим, значение кода Ni соответствует одному из условий

NT-Nnop Ni

или(1)

NT + ,

что означает наличие на выходе одного из цифровых компараторов 14 или 21 уровня логической 1. Тогда в момент поступления стробирующего импульса U7(t) на первый вход мажоритарного элемента 15 на выходе

последнего формируется отрицательный импульс, обнуляющий RS-триггер 22. Длительность этого импульса равна длительности стробирующего импульса U7(t) и определяется длительностью Туст импульсов выходных напряжений Uio(t) или Ui6(t) первого и

второго одновибраторов 10 или 16 соответственно.

RS-триггер 22 обеспечивает синхронизацию момента записи кода Ni в третий регистр 19.

После окончания стробирующего импульса UvW и установки на инверсном выходе мажоритарного элемента 15 уровня логической 1 первым положительным перепадом выходного сигнала умножителя

частоты RS-триггер 22 снова взводится в состояние логической 1, осуществляя тем самым запись кода Ni в третий регистр 19.

Длительность ctpoбиpyющeгo импульса

Густ выбирается исходя из минимального

значения периода входного сигнала Твх.мин и

должна соответствовать условию Туст

Твх.мин/2 + т вых.

Первый счетчик 27, работающий в режиме вычитания, осуществляет обратный счет импульсов, поступающих с выхода управляемого генератора 26. При нулевом состоянии первого счетчика 27 на его выходе формируется импульс записи кода Ni через усг

тановочные входы в этот же счетчик из третьего регистра 19.

После поступления Ni иМпульсрв от управляемого генератора 26 на вход первого счетчика 27. последний снова устанавлй вается в нулевое состояние и формирует следующий импульс записи кода Ni в счетчик. В дальнейшем весь этот процесс цикличе- ски повторяется.

Среднее значение частоты fyr сигнала генератора 26 связано с частотой fr™ генератора 2 тактовых импульсов и определяется заданным значением коэффициента умножения частоты Кумн:

fyr ffTH Кумн.

Период следования выходных сигналов первого счетчика 27 равен

Теых Туг NI Туг TBX/TO Твх/Кумн.

Таким образом, умножителем осуществляется деление периода входного сигнала или, что то же самое, умножение его частоты.

Аналогичные процессы осуществляются В1 умножителе после измерения всех последующих (четных и нечетных) периодов Тех входного сигнала. При этом, если какое- либо значение кода периода, например N2, не удовлетворяет ни одному из условий (1), то оно не переписывается в третий регистр 19. На предустановочные входы первого счетчика 27 по-прежнему поступает код NI (для рассмотренного конкретного примера).

Погрешность умножения, возникающая вследствие погрешности от квантования при измерении периода входного сигнала устраняется соответствующей подстройкой частоты управляемого генератора 26, которая выполняется схемой фазовой автоматической подстройки частоты (ФАПЧ).

В состав следящей схемы ФАПЧ входят делитель 23 частоты с коэффициентом деления, равным Кумн., фазовый детектор 24 и фильтр 25 нижних частот.

Устранение погрешности умножения осуществляется подстройкой частоты сигнала управляемого генератора 26 до достижения равенства частот входного сигнала fax и выходного сигнала делителя 23, частота которого равна 1вых/Кумн. Сравнение частот этих сигналов выполняется фазовым детектором 24, На его выходе формируется сигнал рассогласования, постоянная или низкочастотная составляющая которого, выделяемая фильтром 25 нижних частот, используется для управления Частотой выходного сигнала управляемого генератора 26.

Схема ФАПЧ обеспечивает необходимую для устранения погрешности умножения подстройку частоты сигнала управляемого генератора при начальном отклонении частоты входного сигнала в пределах полосы захвата A.f3axB.

Разрешающая способность кода NT по частоте входного сигнала (полоса частот входного сигнала Д(мт , соответствующая определенному значению кода NT) для осуществления захвата частоты схемой ФАПЧ должна удовлетворять условию

AfNr Afaaxe.(2)

Разрешающая способность кода NT зависит от соотношения длительностей периодов входного и квантующего сигналов (при

возрастании частоты входного сигнала fax, т.е. уменьшении его периода, разрешающая способность кода NT ухудшается, что соответствует увеличению полосы частот AfNT ) Кроме того, разрешающая способность кода NT зависит от порогового значения Nnop и ухудшается с увеличением последнего.

Минимальное пороговое значение кода Nnop., ограничивается максимальным отклонением результатов измерения каждого из

поступающих на вход умножителя последовательности периодов, обусловленного погрешностью от квантования.

Выбор максимального значения Nnop ограничивается разрешающей способностью кода NT на границе высокочастотной области рабочего диапазона, т.е. должно выполняться условие (2).

Дополнительным положительным эффектом предлагаемого умножителя частоты

является расширение рабочего диапазона частот, которое обуславливается снижением требований к точности измерения периода входного сигнала.

30

Формула изобретения

Умножитель частоты, содержащий последовательно соединенные фазовый детектор, фильтр нижних частот, управляемый генератор, первый счетчик, выход которого соединен с его входом предварительной записи, и делитель частоты, выход которого соединен с первым входом фазового детектора, второй вход которого соединен с выходом

формирователя импульсов, последовательно соединенные генератор тактовых импульсов, первый ключ, второй счетчик и первый регистр памяти, последовательно соединенные второй ключ, вход которого

соединен с выходом генератора тактовых импульсов, третий счетчик и второй регистр памяти, а также г;5-триггер, третий регистр памяти, первый и второй одновибраторы, выходы которых соединены с входами обнуления соответственно второго и третьего счетчиков, счетный триггер, прямой и инверсный выходы которого соединены с входами управления соответственно первого и второго ключей, а вход счетного триггера соединен

с выходом формирователя импульсов, о т- л.и чающийся тем, что, с целью повышения точности умножения при изменении частоты входных сигналов, введены инвертор, первый и второй элементы И, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, вычитатель кодов, сум- матэр кодов, первый и второй,цифровые компараторы, мажоритарный элемент, при ЭТ01 х выходы первого и второго одновибрато- ров соединены соответственно с первым и ВТО )ым входами элемента ИСКЛЮЧАЮЩЕЕ ИЛ I, выход которого соединен с первым вхоцом мажоритарного элемента, инверсный выход которого соединен с R-входом RS-триггера, выход формирователя импуль- сов соединен с входом инвертора, выход которого соединен с первыми входами первого и второго элементов И, прямой и инЕерсный выходы счетного триггера сое- диь ены с вторыми входами соответственно второго и первого элементов И, выходы пер- вогэ и второго элементов И соединены с входами соответственно первого и второго oд овибраторов, вход раэрешения выхода и вход обнуления первого регистра памяти соединены соответственно с выходом первого элемента И и инверсным выходом счетною триггера, вход раэрешения выхода и вхс д обнуления второго регистра памяти со- нены соответственно с выходом второго

элемента И и прямым выходом счетного триггера, выходы первого и второго регистров памяти пораэрядно соединены с соответствующими входами третьего регистра памяти и входами первых групп входов первого и второго цифровых компараторов, входы вторых групп входов первого и второго цифровых компараторов пораэрядно соединены с соответствующими выходами соответственно вычитателя кодов и сумматора кодов, выходы первого и второго цифровых компараторов соединены соответственно с вторым и третьим входом мажоритарного элемента, выходы третьего регистра памяти поразрядно соединены с соответствующими установочными входами первого счетчика и входами первых групп входов вычитателя кодов и суммагора кодов, выход первого счетчика соединен с S-входом RS-триггера, прямой выход которого соединен с входом Эаписи третьего регистра памяти, при этом входы вторых групп входов вычитателя кодов и сумматора кодов пораэрядно обьеди- нены и являются управляющими входами кодового сигнала умножителя частоты.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления непосредственным преобразователем частоты | 1985 |

|

SU1265944A1 |

| Устройство для цифрового измерения частоты | 1989 |

|

SU1666965A2 |

| Цифровой частотный демодулятор | 1991 |

|

SU1817249A1 |

| Устройство для исследования пульсовой динамики сердечно-сосудистой системы | 1987 |

|

SU1512561A1 |

| Аналого-цифровой преобразователь | 1981 |

|

SU984041A1 |

| Устройство индикации пеленга | 1983 |

|

SU1167555A1 |

| Устройство для измерения нелинейности пилообразного напряжения | 1990 |

|

SU1777101A1 |

| АВТОМАТИЧЕСКИЙ СЛЕДЯЩИЙ ДЕЛИТЕЛЬ ПЕРИОДОВ ИМПУЛЬСНЫХ СИГНАЛОВ | 1992 |

|

RU2105410C1 |

| Цифровой термометр | 1983 |

|

SU1158873A1 |

| Умножитель частоты | 1986 |

|

SU1385230A1 |

Изобретение относится к радиотехнике и может быть использовано в различных устройствах автоматики и измерительной техники при разработке фазометров, частотомеров, фазовращателей. Цель изобретения - повышение точности умножения при изменении частоты входных сигналов. Умножитель частоты содержит формирователь 1 импульсов, генератор тактовых импульсов 2, инвертор 3, счетный триггер 4, второй ключ 5, первый ключ 6, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 7, первый и второй элементы И 8 и 9, первый одновибратор 10, второй счетчик 11, первый регистр 12 памяти, вычитатель 13 кодов, первый цифровой компаратор 14, мажоритарный элемент 15, второй одновибратор 16, третий счетчик 17, второй регистр 18 памяти, третий регистр 19 памяти, сумматор 20 кодов, второй цифровой компаратор 21, RS-триггер 22, делитель частоты 23, фазовый детектор 24, фильтр нижних частот 25, управляемый генератор 26 и первый счетчик 27. 2 ил.

%

И .

б &

г д

IR

LJL..

..

L.

н П

| Пуговица | 0 |

|

SU83A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Способ изготовления электрических сопротивлений посредством осаждения слоя проводника на поверхности изолятора | 1921 |

|

SU19A1 |

Авторы

Даты

1990-11-23—Публикация

1988-03-09—Подача