Изобретение относится к электротехнике, в частности к технике преобразования параметров электрической энергии, и может быть использовано при создании преобразующих устройств автоматики и стабилизированных вторичных источников электропитания электро-радиоэлектронной аппаратуры, преимущественно при напряжении первичного источника 3-15 В,

Целью изобретения является повышение КПД.

Цель достигается тем, что в транзисторный инвертор, содержащий первый и второй транзисторы, эмиттеры которых подключены к первому входному выводу инвертора, коллекторы подключены к крайним выводам первичной обмотки трансформатора, отвод от средней точки которой соединен со вторым входным выводом инвертора, а базы соединены с первыми парафазными выходами предварительного усилителя, парафазными входами соединенного с выходами первого и второго основных логических элементов, первые входы которых подключены к выходу задающего генератора, причем трансформатор имеет дополнительную обмотку с отводом от средней точки, введены две последовательные RC-цепочки, третий, четвертый, пятый и шестой транзисторы, при этом третий и четвертый транзисторы соединены коллектором с базой, эмиттером с эмиттером соответственно первого и второго транзисторов, а базой - с эмиттером соответственно пятого и шестого транзисторов, коллекторы которых соединены со вторым входом соответственно второго и первого основных логических элементов и через введенные первый и второй резисторы - со вторым входным выводом инвертора, а базы через соответствующую последовательную RC- цепочку - с крайними выводами дополнительной обмотки, отводом от средней точки подключенной ко второму входному вы воду инвертора, и через введенные третий и четвертый резисторы - с коллекторами соответственно первого и второго транзисторов, при этом предварительный усилитель выполнен на седьмом и восьмом транзисторах, эмиттер которых соединен с соответствующим первым парафазным выходом усилителя, коллекторы - с соответствующим крайним выводом дополнительной обмотки трансформатора, а база через соответственно пятый и шестой резисторы - с соответствующим парафазным входом усилителя, и с входом дополнительного логического элемента, выход которого через седьмой и восьмой резистор - с вторыми парафазными выходами предварительного усилителя,

подключенными к базам соответственно третьего и четвертого транзисторов. В случае выполнения всех транзисторов п-р-п типа все логические элементы ИЛИ-НЕ ти5 па, а в случае выполнения всех транзисторов p-n-р типа все логические элементы И-НЕ типа. Кроме того, в цепь третьего и четвертого резисторов последовательно включены введенные в трансформатор соответственно первая и вторая вспомогательные обмотки в противофазе по отношению к соединенной с ними половине первичной обмотки. В цепь каждой половины дополнительной обмотки включен после5 довательно .введенные пятый и десятый резисторы соответственно.

Сущность изобретения заключается в том, что из противофазных прямоугольных напряжений, снимаемых с выходов генера0 тора и задерживаемых с помощью первого и второго логических элементов на время включения транзистора двухтактного усилителя мощности, работавшего в окончившемся полупериоде генератора, получают

5 базовые токи первого и второго транзисторов указанного усилителя через согласующие транзисторы, каждый из которых совместно с относящимся к нему транзистором усилителя образует составной транзи0 стор с той особенностью, что переходы база-эмиттер первого и второго транзисторов шунтируются в нерабочие полупериоды третьим и четвертым транзисторами, базовые токи которых в закрытом состоянии

5 шунтируемых транзисторов являются токами эмиттеров пятого и шестого транзисторов, с коллекторов которых снимается информация для логических элементов о состояниях первого и второго транзисторов

0 ключевого преобразователя; сигналы на базы пятого и шестого транзисторов поступают от коллекторов согласующих транзисторов (седьмой и восьмой транзисторы) через дифференцирующие RC-цепи, выпол5 ненные на первом, втором резисторах и первом и втором конденсаторах, и от первого и второго транзисторов усилителя мощности через третий и четвертый резисторы. Сигналы с RC-цепей запирают последова0 тельно во времени пятый и шестой транзисторы, а. значит, третий и четвертый транзисторы, чем разрешается работа первому или второму транзисторам. Токи без пятого и шестого транзисторов через третий

5 и четвертый резисторы наоборот, открывают пары транзисторов: пятый, третий и шестой, четвертый в моменты времени, когда относящийся к ним первый или второй транзисторы закрываются; в первоначальный момент времени, когда начался для первого

или второго транзисторов нерабочий полупериод, а сам этот транзистор еще остается открытым из-за рассасывания неосновных носителей, процесс рассасывания ускоряется введением в действие шун- тирующих (третьего или четвертого) транзисторов от третьего логического элемента, на обоих входах которого во время рассасывания любого из первого и второго транзисторов образуются одинаковые логические уровни: нули или единицы в зависимости от того, транзисторы инвертора типа проводимости п-р-п или р-п-р.

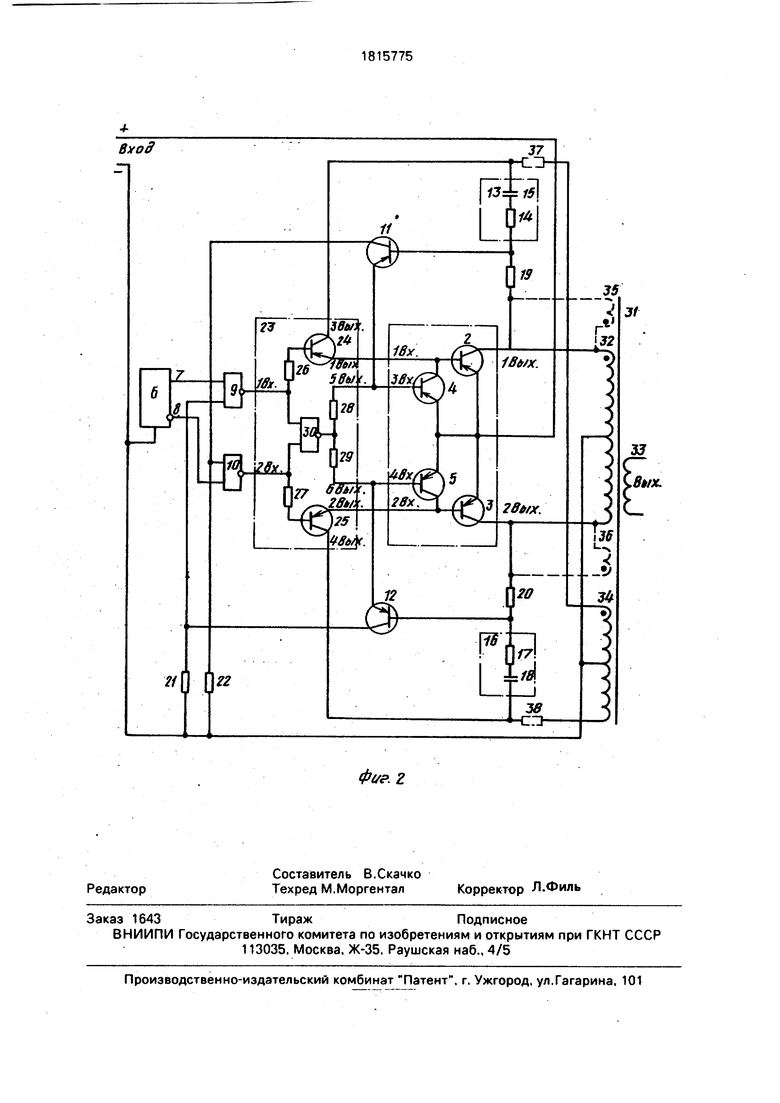

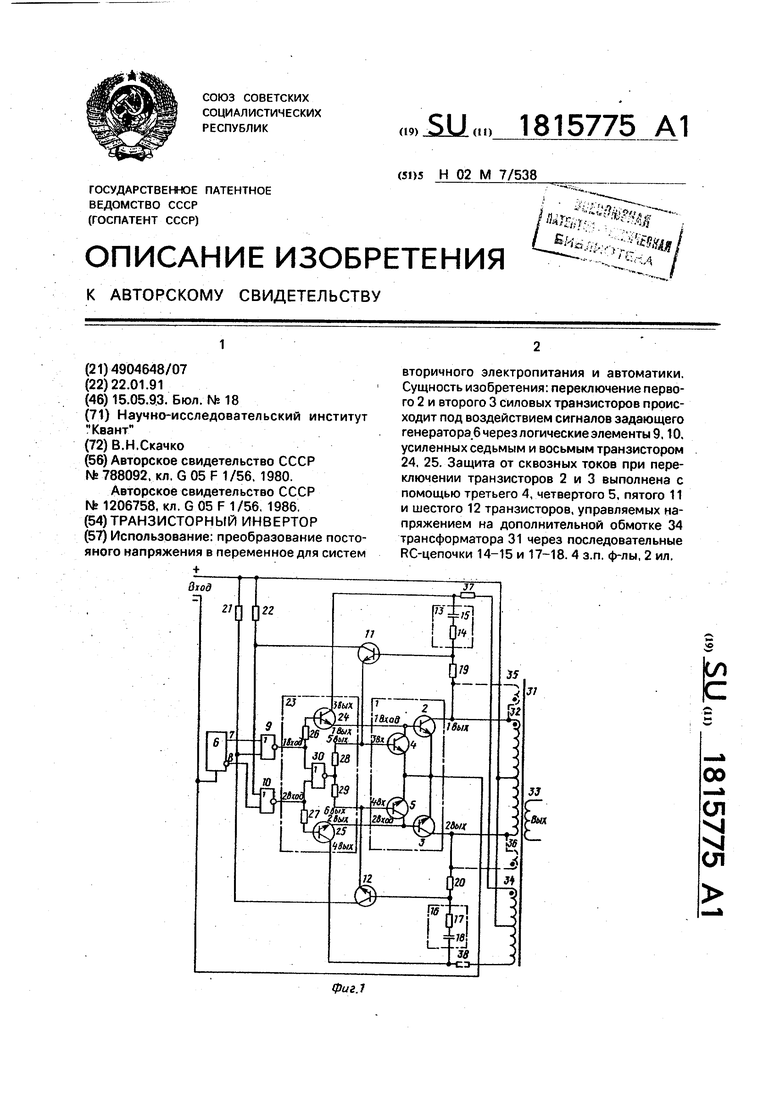

На фиг.1 и 2 представлены схемы транзисторного инвертора соответственно для случаев применения в нем транзисторов п- р-п и р-п-р.

Транзисторный инвертор состоит из первого 1, второго 2, третьего 3 и четвертого 4 транзисторов, образующих усилитель мощности 5, из генератора 6 прямоугольного напряжения с взаимно инверсными выходами 7 и 8, первого 9 и второго 10 логических элементов ИЛИ-НЕ или И-НЕ в зависимости от типа проводимости применяемых в инверторе транзисторов: п-р-п или, соответственно, р-п-р, из пятого 11 и шестого 12 транзисторов, первой RC-цепи 13, выполненной на последовательно соединенных первом резисторе 14 и первом конденсаторе 15, второй RC-цепи 16 на втором резисторе 17 и втором конденсаторе 18, которые также последовательно соединены между собой, из третьего 19, четвертого 20, пятого 21, шестого 22 резисторов, из предварительного усилителя мощности 23, содержащего седьмой 24, восьмой 25 транзисторы, седьмой 26, восьмой 27, девятый 28, десятый 29 резисторы и третий логический элемент 30, а также из трансформатора 31 с первичной обмоткой 32 со средним выводом, с первой вторичной обмоткой 33, являющейся в данном конкретном случае выполнения выходом инвертора, со второй вторичной обмоткой 34 с меньшим числом витков, чем у первичной обмотки и имеющей средний вывод, соединенный со средним выводом первичной обмотки, а также из одиннадцатого 37 и двенадцатого 38 резисторов. Выходы 7, 8 генератора 6 прямоугольного напряжения, который может быть активным или пассивным (триггер), подключены к первым входам логических элементов 9,10, выходы которых соединены с первым и вторым входами предварительного усилителя мощности 23, в котором они подключены ко входам логи ческого элемента 30, а через резисторы 26 и 27 соответственно к базам транзисторов 24 и 25. Выход третьего логического элемента

30 через резисторы 28 и 29 подключен к пятому и шестому выходам предварительного усилителя мощности. Эмиттеры транзисторов 24, 25 через соответственно 5 первый и второй выходы предварительного усилителя мощности и первый и второй входы усилителя мощности 5 подключены к базам его транзисторов 1 и 2, а коллекторы транзисторов 24, 25 через образуемые ими

0 третий и четвертый выходы предварительного усилителя 23 подключены через резисторы 37 и 38 соответственно к началу и концу обмотки 34 трансформатора 31. Эмиттеры транзисторов 1,2, 3 и 4 усилителя мощ5 ности 5 подключены к первой шине питания. Коллекторы транзисторов 1 и 2 через образуемые ими первый и второй выходы-усилителя мощности 5 подключены соответственно к началу и концу обмотки 32

0 трансформатора 31, средний вывод которой вместе со средним выводом обмотки 34 подключены ко второй шине питания. База транзистора 11 через RC-цепь 13 подключена к третьему выходу предварительного уси5 лителя мощности, а через резистор 19 и последовательно соединенную с ним обмотку 35 - к первому выходу усилителя мощности 5. Аналогично, база транзистора 12 через RC-цепь 16 подключена к четвертому

0 выходу предварительного усилителя мощности 23, а через резистор 20 и последовательно соединенную с ним обмотку 36 - ко второму выходу усилителя мощности 5. Эмиттеры транзисторов 11 и 12 соединены

5 соответственно с пятым и шестым выходами предварительного усилителя мощности, и через третий и четвертый входы усилителя мощности соединены с базами транзисторов 3 и 4, а коллекторы транзисторов 11 и 12

0 подключены ко вторым входам логических элементов соответственно 10 и 9 и через резисторы 21 и 22 - ко второй шине питания. Работает инвертор (см. фиг.1) следующим образом. В исходном состоянии тран5 зисторы 11,3, 12, 6 открыты за счет тока от положительной шины питания по половине обмотки 34, резистору 19 и последовательно соединенным обмотке 35, переходам база-эмиттер транзисторов 11,3 и аналогично

0 этому - по второй половине обмотки 34, резистору 20 и последовательно соединенным обмотке 36, переходам база-эмиттер транзисторов 12 и 4. В силу того, что падение напряжения на переходах коллектор5 эмиттер маломощных транзисторов 3, 4 всегда меньше напряжения переходов база-эмиттер мощных транзисторов 1, 2 в состоянии их проводимости, переходы коллектор-эмиттер открытых транзисторов 3. 4 блокируют переходы база-эмиттер

транзисторов 1, 2, а через переходы коллектор-эмиттер транзисторов 11, 12 на вторых входах логических элементов ИЛИ-НЕ 10, 9 устанавливаются логические нули. Кэк только на первом входе одного из этих логических элементов, допустим 9, от генератора 6 прямоугольного напряжения тоже появится логический нуль (от его выхода 7), на выходе данного логического элемента образуется логическая единица, пойдет базовый, а, значит, и коллекторный ток транзистора 24, причем ток от его эмиттера пойдет сначала не через переход база- эмиттер транзистора 1, а через переход коллектор-эмиттер транзистора 3, которым транзистор 1 блокирован. За счет возникшего падения напряжения на коллекторе транзистора 24 через RC-цепь 13 на базу транзистора 11 будет передан отрицательный всплеск, и он одновременно с транзистором 3 закроется. Теперь ток эмиттера транзистора 24 пойдет на база-эмиттерный переход транзистора 1, ион откроется. Пойдет ток по половине обмотки 29 от положи- тельной шины питания на коллектор транзистора 1. Так как потенциал коллектора транзистора 1 понизится, транзисторы 11 и 3 будут оставаться закрытыми и после окончания всплеска от RC-цепи 13, так как падение напряжения перехода коллектор- эмиттер открытого (до насыщения) транзистора 1, даже если он мощный, меньше суммарного напряжения переходов база- эмиттер двух маломощных транзисторов 11 и 3. На время закрытого состояния транзистора 11 второй вход логического элемента 10 примет положительный потенциал благодаря его связи через резистор 21с положительной шиной питания. Если напряжение первичной сети повышено (5...15 В), то во избежание дополнительных потерь мощности на резисторах 19, 20 целесообразно уменьшить падение напряжения на этих резисторах за счет противофазного включения в цепи их тока дополнительных обмоток 35 и 36.

После смены полупериодов генератора 6 прямоугольного напряжения транзисторы 24, 1 (особенно 1) закрываются с задержкой из-за явления рассасывания в них неосновных носителей. До тех пор, пока транзистор 1 остается открытым, на втором входе логического элемента 10 будет поддерживаться логическая единица, на его выходе - логический нуль и транзисторы 25 и 2 не откроются. Так как в этом состоянии схемы на обоих входах логического элемента 2ИЛИ-НЕ 30 будут логические нули, то током от его выхода через резистор 28 будет открыт транзистор 3, шунтирующий переход

база-эмиттер транзистора 1, что ускоряет его закрывание (рассасывание неосновных носителей). Ток от выхода элемента 30 через резистор 29 на базу транзистора 4 не меняет его состояния, потому что он все равно открыт током от эмиттера транзистора 12. По окончанию процесса выключения транзистора 1, когда возрастет потенциал его коллектора, откроется транзистор 11, в ре0 зультате чего исчезнет логическая единица со второго входа логического элемента 10. При наличии логического нуля, ранее установившегося на первом входе этого логического элемента (от выхода 8 генератора

5 прямоугольного напряжения) появится логическая единица на выходе логического элемента 10, а на выходе элемента 30- нуль. Ток базы транзистора 3 со стороны выхода логического элемента 30 прекратится, одна0 ко он будет оставаться в открытом состоянии - теперь уже током базы от эмиттера транзистора 11. Поэтому транзистор 1 будет и далее блокироваться по переходу база- эмиттер.

5 От установившегося положительного уровня выхода логического элемента 10 откроется транзистор 25 и будут развиваться описанные процессы во втором полупериоде, которые приведут к закрыванию транзи0 сторов 12 и 4 (всплеском отрицательной полярности со стороны RC-цепи 17), открыванию транзистора 1, удерживанию транзисторов 12 и 4 в закрытом состоянии и протягиванию во времени наличия запре5 щающей логической единицы на втором входе логического элемента 9, пока фактически не выключится транзистор 2 после очередной смены полупериодов генератора 6 и станет допустимым включение транзи0 сторов 24 и 1. Ускорение рассасывания транзистора 2 в конце его рабочего полупериода будет обеспечено открыванием транзистора 4 током базы (через резистор 29) от выхода логического элемента 30, на входах

5 которого опять образуется совпадение логических нулей: на первом входе из-за того (и поскольку) еще поддерживается логическая единица на коллекторе транзистора 12, а на втором входе - потому что на первый

0 вход логического элемента 10 уже поступила логическая единица от генератора 6.

Транзисторы 3 и 4 выполняют роль электронных ключей, заменяющих резисторы между базой и эмиттером силовых транзи5 сторов 1 и 2, которые обычно должны быть малой величины (не больше 10 Ом). Но физически эти резисторы нужны лишь когда транзисторы закрыты, а в открытом состоянии они бесполезны, так как на них рассей- вается часть мощности управления, Каждый

из этих двух ключей во время работы относящегося к ним силового транзистора закрыт и наоборот, открывается сам, когда закрывается обслуживаемый им силовой транзистор.

Управление вторыми входами логических элементов 10 и 9 со стороны транзисторов 11 и 12, переключающимися одновременно с транзисторами 3 и 4, позволяет устранить одновременную работу силовых транзисторов 1, 2 (и согласующих транзисторов 24, 25), чем предотвращаются сквозные токи (токи перекрытия), уменьшающих надежность и КПД инвертора.

Инвертор на p-n-р транзисторах (фиг.2) работает таким же образом с тем отличием, что если логические элементы ИЛИ-НЕ инвертора с п-р-п транзисторами управляются логическими нулями по их совпадению на обоих входах, то в инверторе на p-n-р транзисторах логические элементы И-НЕ управляются логическими единицами при их одновременном присутствии на двух входах такого логического элемента. Исходным уровнем на вторых входах двух первых элементов И-НЕ 9, 10 инвертора по фиг.2 являются логические единицы, поступающие на эти входы от коллекторов открытых транзисторов 11 и 12 типа p-n-р. С поступлением от генератора б логической единицы на первый вход одного из логических элементов 9 и 10 на его выходе устанавливается логический нуль, наступает состояние проводимости относящегося к нему согласующего транзистора 24 или 25, что кладет начало вышеописанным процессам при противоположной полярности напряжений на электродах транзисторов. Роль логического элемента 2И-НЕ 30 в этом случае та же: по окончанию полупериода, в котором работает один из транзисторов 1, 2, открыть ключевой транзистор, к нему относящийся (3 или 4) раньше, чем закроется транзистор 1 или 2, а именно сразу же после смены рабочего для этого транзистора полупериода (транзисторы 3, 4 в этом случае p-n-р, а сигнал на выходе логического элемента 2И- НЕ 30 формируется в виде логического нуля).

Настоящий транзисторный инвертор может работать, подобно прототипу, в режиме внешнего управления, являясь в этом случае регулируемым.

Такое управление можно осуществить, например, применив логические элементы 9, 10 с тремя входами, подавая на третьи входы сигналы управления. На время, когда на третьих входах на части продолжительности полупериода будет логическая единица для элементов ЙЛИ-НЕ или логический

нуль для элементов И-НЕ, в выходном напряжении инвертора будет пауза - одинаковая по длительности в каждом полупериоде. Так становится возможным создание регу- 5 лируемого инвертора по принципу широт- но-импульсной модуляции, что присуще прототипу.

Подключение широтно-импульсного модулятора к инвертору возможно не толь0 ко через вводимые третьи входы логических элементов, но и при использовании двух- входовых логических элементов, если последовательно с какими-либо их входами установить дополнительные резисторы.

5 Тогда широтно-импульсный модулятор может быть подключен к этим, снабженным дополнительными резисторами входам, при этом выходной каскад широтно-импульсного модулятора должен работать на измене0 ние (в части полупериода) логического нуля (если используются логические элементы ИЛИ-НЕ) или логической единицы (при логических элементах И-НЕ) на противоположный логический уровень. Это может

5 быть реализовано, например, включением коллектор-эмиттерных переходов транзисторов выходных каскадов таких широтно- импульсных модлуяторов между входами логических элементов, используемых для

0 управления, и первой шиной питания (противоположной той, к которой подключены резисторы 21, 22). Выходом заявленного транзисторного инвертора может быть не только отдельная обмотка его трансформа5 тора, но и непосредственно коллекторы силовых транзисторов 1, 2, что удобно, например, для удвоения напряжения первичного источника питания.

Предложенный транзисторный инвер0 тор с логическими элементами выгодно отличается от прототипа тем, что он позволяет получить большую выходную мощность при большем КПД. Это стало возможным благодаря тому, что выходные сигналы логиче5 ских элементов, имеющих ограниченную нагрузочную способность, усиливаются двумя противофазными промежуточными (не классически составными) каскадами, в коллекторы транзисторов которых включена

0 дополнительная обмотка трансформатора инвертора. На обслуживание этого каскада не требуется дополнительная мощность; ба- за-эмиттерные резисторы силовых транзисторов заменены дополнительными

5 ключевыми транзисторами, состояние проводимости которых противоположно состо- янию обслуживаемых ими силовых транзисторов инвертора, чем исключены потери мощности управления этими транзисторами; для того, чтобы управлять транэисторами (11, 12), реализующими совместно с логическими элементами (10, 9) функцию автоматической задержки включения силовых транзисторов, не потребовалось дополнительной энергии на протяжении преобладающей части полупериода. Для управления этими транзисторами и дополнительными ключевыми транзисторами (3, 4) используются одни и те же управляющие сигналы, так как база-эмиттерные переходы пар транзисторов 11, 3 и 12, 4 включены последовательно и управление ими совместно. И только на время рассасывания выключаемых силовых транзисторов базовый ток этих транзисторов создается от выхода логического элемента 30.

.Формула изобретения 1. Транзисторный инвертор, содержащий первый и второй транзисторы, эмиттеры которых подключены к первому входному выводу инвертора, коллекторы подключены к крайним выводам первичной обмотки трансформатора, отвод от средней точки которой соединен с вторым входным выводом инвертора, а базы соединены с первыми парафазными выходами предварительного усилителя, парафазными входами соединенного с выходами первого и второго основных логических элементов, первые входы которых подключены к выходу задающего генератора, причем трансформатор имеет дополнительную обмотку с отводом от средней точки, от личающий- с я тем, что, с целью повшыения КПД, введены две последовательные RC-цепочки, третий, четвертый, пятый и шестый транзисторы, при этом третий и четвертый транзисторы соединены коллектором с базой, эмиттером - с эмиттером соответственно первого и второго транзисторов, а базой -с эмиттером соответственно пятого и шестого транзисторов, коллекторы которых соединены с вторым входом соответственно второго и первого основных логических элементов и через введенные первый и второй резисторы - с вторым входным выводом инвертора, а базы через соответствующую последовательную RC-цепочку - с крайними выводами дополнительной обмотки, отводом от средней точки подключенной к второму входному выводу инвертора, и через введенные третий и четвертый резисторы - с коллекторами соответственно первого и второго транзисторов,

при этом предварительный усилитель выполнен на седьмом и восьмом транзисторах, эмиттер которых соединен с соответствующим первым парафазным выходом усилителя, коллекторы - с соответствующим крайним выводом дополнительной обмотки трансформатора, а база через соответственно пятый и шестой резисторы - с соответствующим парафазным входом усилителя, и с входом дополнительного логического элемента, выход которого через седьмой и восьмой резистор - с вторыми парафазными выходами предварительного усилителя, подключенными к базам соответственно третьего и четвертого транзисторов.

2. Инвертор по п. 1, о т л и ч а ю щ и и - с я тем, что все транзисторы выполнены с проводимостью n-p-n-типа, а все логические элементы - ИЛИ-НЕ-типа.

3. Инвертор поп.1,отличающий- с я тем, что все транзисторы выполнены с проводимостью p-n-p-типа, а все логические элементы - И-НЕ-типа.

4. Инвертор поп.1,отличающий- с я тем, что в цепь третьего и четвертого резисторов последовательно включены введенные в трансформатор соответственно первая и вторая вспомогательные обмотки в противофазе по отношению к соединен- ной с ними половине первичной обмотки.

5. Инвертор пол.1,отличающий- с я тем, что в цепь каждой половины дополнительной обмотки включены последовательно введенные девятый и десятый резисторы соответственно.

| название | год | авторы | номер документа |

|---|---|---|---|

| Транзисторный инвертор | 1988 |

|

SU1818673A1 |

| СТАБИЛИЗИРОВАННЫЙ ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ С ЦИФРОВЫМИ МИКРОСХЕМАМИ | 1991 |

|

RU2014713C1 |

| Стабилизированный преобразователь постоянного напряжения | 1990 |

|

SU1728950A1 |

| Источник вторичного электропитания для сети постоянного напряжения | 1990 |

|

SU1786476A1 |

| Преобразователь постоянного напряжения в переменное | 1990 |

|

SU1734178A1 |

| Преобразователь постоянного напряжения | 1981 |

|

SU1056390A1 |

| Транзисторный инвертор | 1990 |

|

SU1757069A1 |

| СПОСОБ И УСТРОЙСТВО ЗАЩИТЫ МИКРОПРОЦЕССОРНЫХ СИСТЕМ ЖЕЛЕЗНОДОРОЖНОЙ АВТОМАТИКИ ОТ АППАРАТНЫХ И ПРОГРАММНЫХ НАРУШЕНИЙ В РАБОТЕ И УСТРОЙСТВО СРАВНЕНИЯ ПАРАФАЗНЫХ СИГНАЛОВ С ЗАЩИТОЙ ОТ ОПАСНЫХ ОТКАЗОВ | 2009 |

|

RU2385521C1 |

| Стабилизированный преобразователь постоянного напряжения | 1989 |

|

SU1700539A1 |

| ИСТОЧНИК ВТОРИЧНОГО ЭЛЕКТРОПИТАНИЯ | 1995 |

|

RU2074492C1 |

Использование: преобразование посто- яного напряжения в переменное для систем + вход вторичного электропитания и автоматики. Сущность изобретения: переключение первого 2 и второго 3 силовых транзисторов происходит под воздействием сигналов задающего генератора б через логические элементы 9.10. усиленных седьмым и восьмым транзистором 24. 25. Защита от сквозных токов при переключении транзисторов 2 и 3 выполнена с помощью третьего 4, четвертого 5, пятого 11 и шестого 12 транзисторов, управляемых напряжением на дополнительной обмотке 34 трансформатора 31 через последовательные RC-цепочки 14-15 и 17-18. 4 з.п. ф-лы, 2 ил.

| Устройство для управления вторичным источником питания | 1979 |

|

SU788092A1 |

| кл | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

| Ключевой стабилизатор постоянного напряжения | 1983 |

|

SU1206758A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1993-05-15—Публикация

1991-01-22—Подача