Предлагаемое технические решение относится к радиотехнике, в частности к усилительной технике звуковой частоты.

Целью предлагаемого технического решения является исключение помех (щелчков), возникающих на выходе усилителя (в громкоговорителе) в моменты коммутации напряжения питания в усилителях класса ВС.

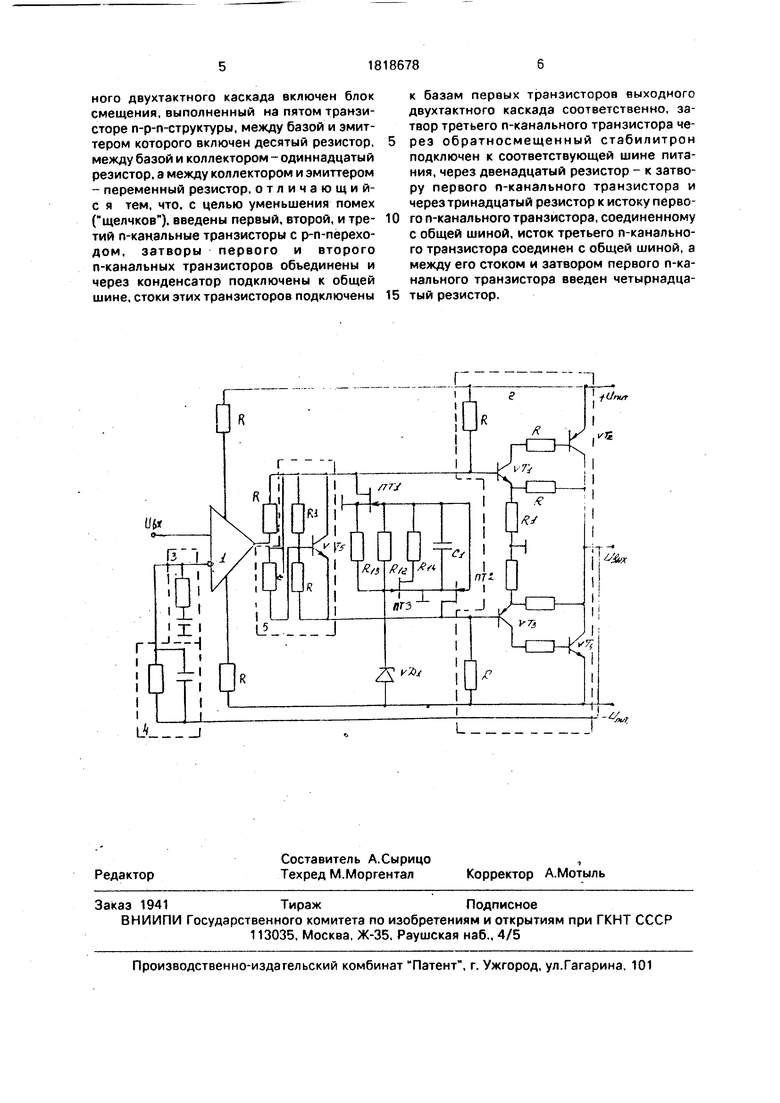

На чертеже представлена принципиальная схема усилителя.

Входной сигнал усиливается по напряжению операционным усилителем 1, а затем по мощности двухтактным выходным 2 каскадом, схема смещения 5 осуществляет установку и стабилизацию тока покоя выходных транзисторов.

При включении двухполярного источника питания ± ипит величина его увеличивается со скоростью, пропорциональной постоянной времени сглаживающего фильтра. Помехи, возникающие при этом в усилителе, не могут проникнуть на выход усилителя (в нагрузку), так как транзисторы VT1-VT4 оказываются закрытыми. Причиной этого является открытое .состояние полевых транзисторов ПТ1 и ПТ2, исключающие прохождение токов через транзисторы VT1 и VT3. В свою очередь, открытое состояние полевых транзисторов ПТ1 и ПТ2 является следствием отсутствия

00

со о

Х| 00

напряжения затвор - исток при разряженном конденсаторе С в открытом полевом транзисторе ПТЗ. Такое состояние в усилителе сохраняется в течение времени, необходимого для увеличения напряжения питания от нуля до величины напряжения стабилизации стабилитрона VDI. Этого времени обычно достаточно для подавления основных составляющих помех, Дальнейший рост напряжения питания вызывает увеличение запирающего напряжения полевого транзистора ПТЗ до полного закрытия, а затем и закрытия полевых транзисторов ГТИ и ПТ2. Плавность установления нормального режима работы усилителя опреде- ляется скоростью закрытия полевых транзисторов ПТ1 и ПТ2 и зависит от постоянной времени R12CI, напряжений отсечки полевых транзисторов ПТ1-ПТЗ, напряжения стабилизации стабилитрона VDI. При нормальном режиме работы усилителя полевые транзисторы ПТ1 и ПТ2 надежно закрыты и не оказывают влияния на его характеристики.

При отключении источника питания ±ипит величина напряжения питания уменьшается со скоростью, значительно меньшей скорости увеличения напряжения при включении, что приводит к значительно меньшей величине помехи. Исключение этого вида помехи в усилителе достигается закрытием транзисторов VT1-VT4. При уменьшении напряжения питания ±Упит ниже аеличины, равной напряжению стабилизации стабилитрона VDI, происходит его закрытие. При этом напряжение затвор-исток полевого транзистора ПТЗ становится равным нулю, он открывается и через четырнадцатый R14 резистор разряжает конденсатор CI, что приводит к открытию полевых транзисторов ПТ 1 и ПТ2 и закрытию VT1- VT4. Таким образом, транзисторы VT1-VT4 будут находиться в закрытом состоянии при уменьшении напряжения питания±11пит в пределах от аеличины напряжения стабилизации стабилитрона VDI до нуля, т. е. помеха при выключении будет отсутствовать. Постоянная времени R14CI выбирается достаточно малой с учетом реальных возможностей коммутации питающего напряжения.

При использовании схемы подавления помех в усилителях класса ВС со значительным колебанием величины напряжения питания достаточно выбрать соответствующим образом величину напряжения стабилизации стабилитрона VDI.

Благодаря приведенному составу усилителя и функциональным связям предлагаемого технического решения, преимущество которого по сравнению с прототипом заключается в том, что позволяет автоматически достичь стабильное и надежное предотвращение появления помех на выходе усилителя, за счет управления зарядным и разрядным током конденсатора, который осуществляет управлением работой транзисторов двухтактного выходного 2 каскада

при неблагоприятно возникающих условий.

Пример реализации схемы.

При изменении величины напряжения

питания схемы усилителя в пределах от ± 43

до ±70В номиналы резисторов в схеме могут быть выбраны следующими: R14 -1 кОм R12 - 2 мОм, R13 - 10 кОм. Диоды: VDI - КС531В. Транзисторы: ПТ1-ПТЗ КПЗОЗЕ. Конденсатор CI - 2 мкф. В данном случае для защиты от превышения допустимой величины напряжения между затвором и истоком у ПТ1-ПТЗ следует дополнительно включить стабилитрон типа КС515А параллельно резистору R13 и последовательно с VDI - резистор R 10 кОм.

Формула изобретения

Усилитель, содержащий входной каскад и выходной двухтактный каскад, при этом каскад выполнен на операционном усилителе, неинвертирующий вход которого являет

ся входом усилителя, а инвертирующий вход через последовательную RC-цепь подключен к общей шине и через параллельную RC-цепь к выходу выходного двухтактного каскада, каждое плечо которого выполнено на первом и втором транзисторах разной

структуры, включенных по схеме с общим эмиттером, причем транзисторы одного плеча и другого плеча также выполнены на транзисторах разной структуры, в цепи

эмиттеров первых транзисторов обоих плеч включены первый и второй резисторы соответственно и точка их соединения подключена к общей шине, коллекторы вторых транзисторов соединены через соответствующие третий и четвертый резисторы с эмиттерами первых транзисторов соответственно, база первого транзистора первого плеча через пятый резистор подключена к одной шине питания, а коллектор - через

шестой резистор к базе второго транзистора этого плеча, база первого транзистора второго плеча через седьмой резистор подключена к другой шине питания, а коллектор через восьмой резистор к

базе второго транзистора этого плеча, между выходом операционного усилителя и базой первого транзистора первого плеча введен девятый резистор, между базами первых транзисторов выходного двухтактного каскада включен блок смещения, выполненный на пятом транзисторе n-p-n-структуры, между базой и эмиттером которого включен десятый резистор, между базой и коллектором - одиннадцатый резистор, а между коллектором и эмиттером - переменный резистор, отличающий- с я тем, что. с целью уменьшения помех (щелчков), введены первый, второй, и третий n-канальные транзисторы с р-п-перехо- дом, затворы первого и второго n-канальных транзисторов объединены и через конденсатор подключены к общей шине, стоки этих транзисторов подключены

0

5

к базам первых транзисторов выходного двухтактного каскада соответственно, затвор третьего п-канального транзистора через обратносмещенный стабилитрон подключен к соответствующей шине питания, через двенадцатый резистор - к затвору первого n-канального транзистора и через тринадцатый резистор к истоку первого n-канального транзистора, соединенному с общей шиной, исток третьего п-канального транзистора соединен с общей шиной, а между его стоком и затвором первого п-канального транзистора введен четырнадцатый резистор.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ЭЛЕКТРОСТАТИЧЕСКИХ ПОТЕНЦИАЛОВ | 1993 |

|

RU2083990C1 |

| Способ формирования амплитудно-частотной характеристики усилителя для воспроизведения сигнала, записанного на грампластинку (RIAA корректор) | 2021 |

|

RU2783838C1 |

| Прецизионный арсенид-галлиевый операционный усилитель с малым уровнем систематической составляющей напряжения смещения нуля и повышенным коэффициентом усиления | 2023 |

|

RU2813370C1 |

| ГЕНЕРАТОР | 2011 |

|

RU2453983C1 |

| КОММУТАЦИОННОЕ УСТРОЙСТВО | 1997 |

|

RU2175166C2 |

| СПОСОБ УПРАВЛЕНИЯ КОЭФФИЦИЕНТОМ ПЕРЕДАЧИ РЕШАЮЩЕГО УСИЛИТЕЛЯ | 2014 |

|

RU2573241C1 |

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2003 |

|

RU2234797C1 |

| ДВУХТАКТНЫЙ УСИЛИТЕЛЬ МОЩНОСТИ | 2002 |

|

RU2298282C2 |

| ДВУХТАКТНЫЙ УСИЛИТЕЛЬ | 2012 |

|

RU2510569C1 |

| КОММУТАЦИОННОЕ УСТРОЙСТВО | 1996 |

|

RU2124806C1 |

Использование: в радиотехнических усилителях, устройствах звуковой частоты. Сущность изобретения: устройство содержит входной и выходной двухтактный каскады. Входной каскад выполнен на операционном усилителе, инвертирующий вход которого через последовательную LC- цепь подключен к общей шине, и через параллельную LC- цепь - к выходу выходного двухтактного каскада. Каждое плечо двухтактного каскада выполнено на первом и втором транзисторах разной структуры, включенных по схеме с общим эмиттером. Устройство содержит также три п-каналь- ных транзистора с р-п-переходом. Затворы первого и второго n-канальных транзисторов объединены и через конденсатор подключены к общей шине, стоки этих транзисторов подключены к базам первых транзисторов выходного двухтактного каскада соответственно. Затвор третьего п-ка- нального транзисторачерез обратно-смещенный стабилитрон подключен к шине питания, через соответствующий резистор - к затвору первого п-канального транзистора и через другой резистор подсоединен к истоку первого n-канального транзистора, соединенного с общей шиной, к которой подключен исток третьего п-канального транзистора. 1 ил. fe

| Алексенко А.Г | |||

| и др | |||

| Применение прецизионных аналоговых микросхем | |||

| М.: Радио и связь, 1985, с | |||

| Упругая металлическая шина для велосипедных колес | 1921 |

|

SU235A1 |

Авторы

Даты

1993-05-30—Публикация

1991-06-05—Подача