Изобретение относится к технике телевидения и может быть использовано в цифровых телевизионных (ТВ) системах передачи изображений графических и текстовых документов по узкополосным каналам связи, а также для ввода телевизионной информации в ЭВМ.

Цель изобретения - повышение точности формирования бинарного телевизионного сигнала путем уменьшения вероятности ошибки бинарного квантования исходного сигнала с шумом.

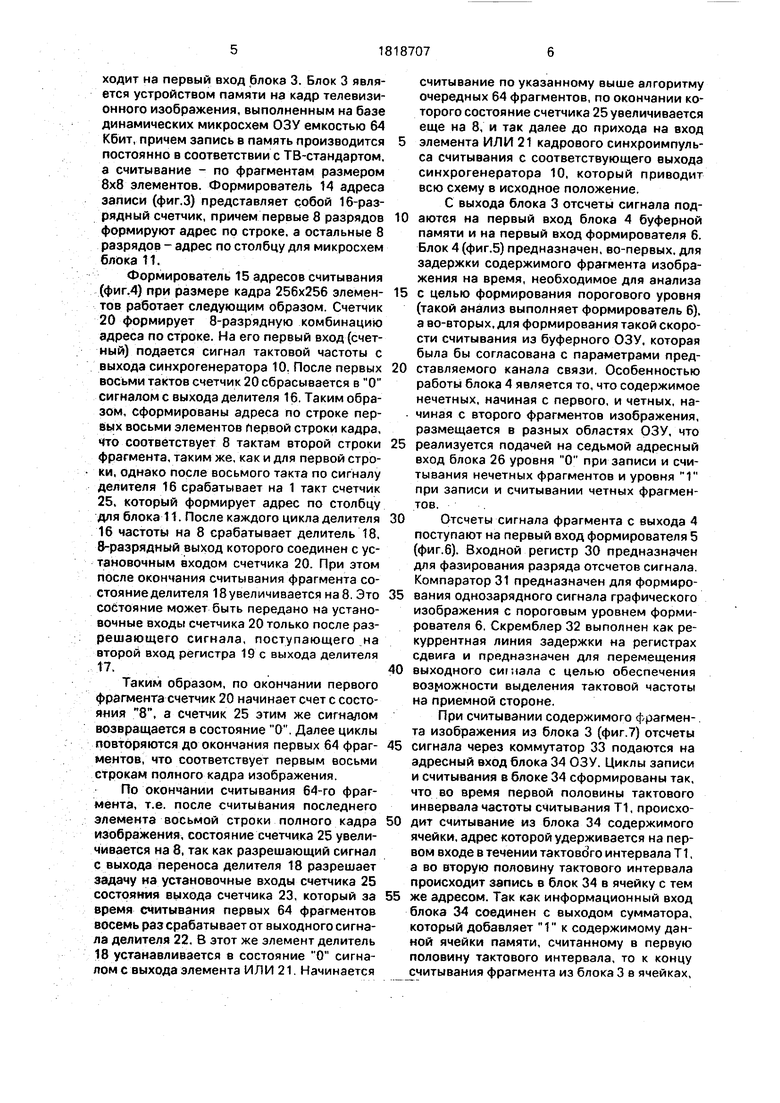

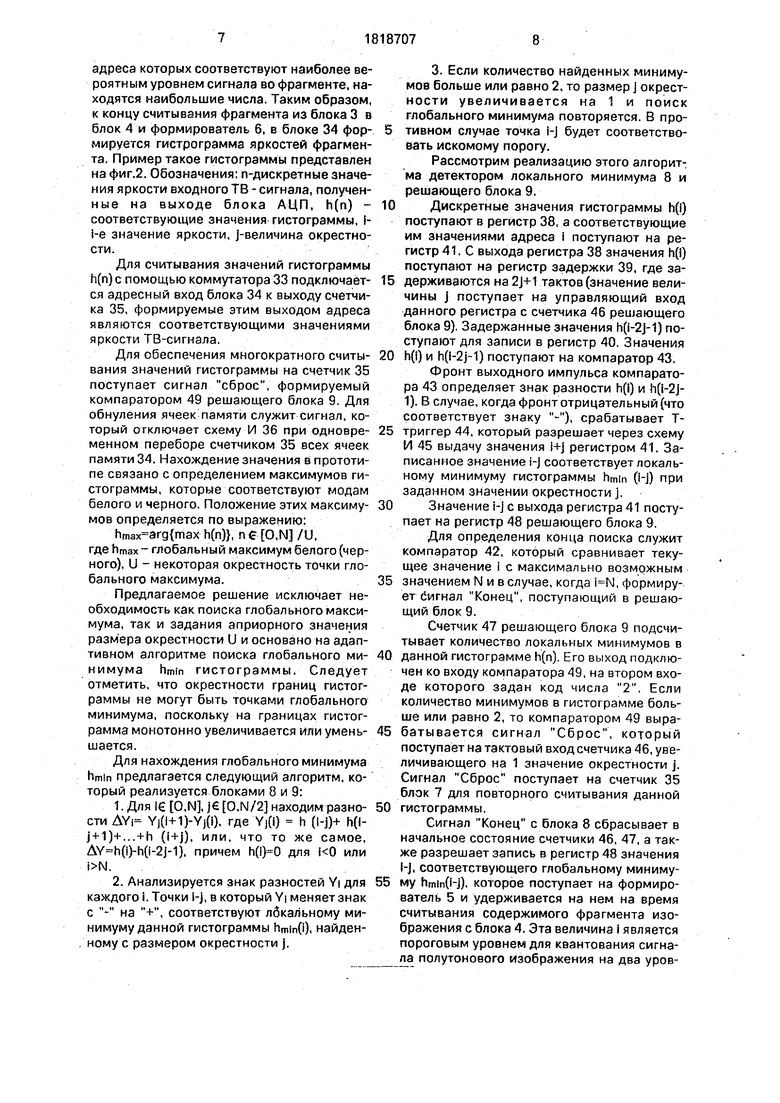

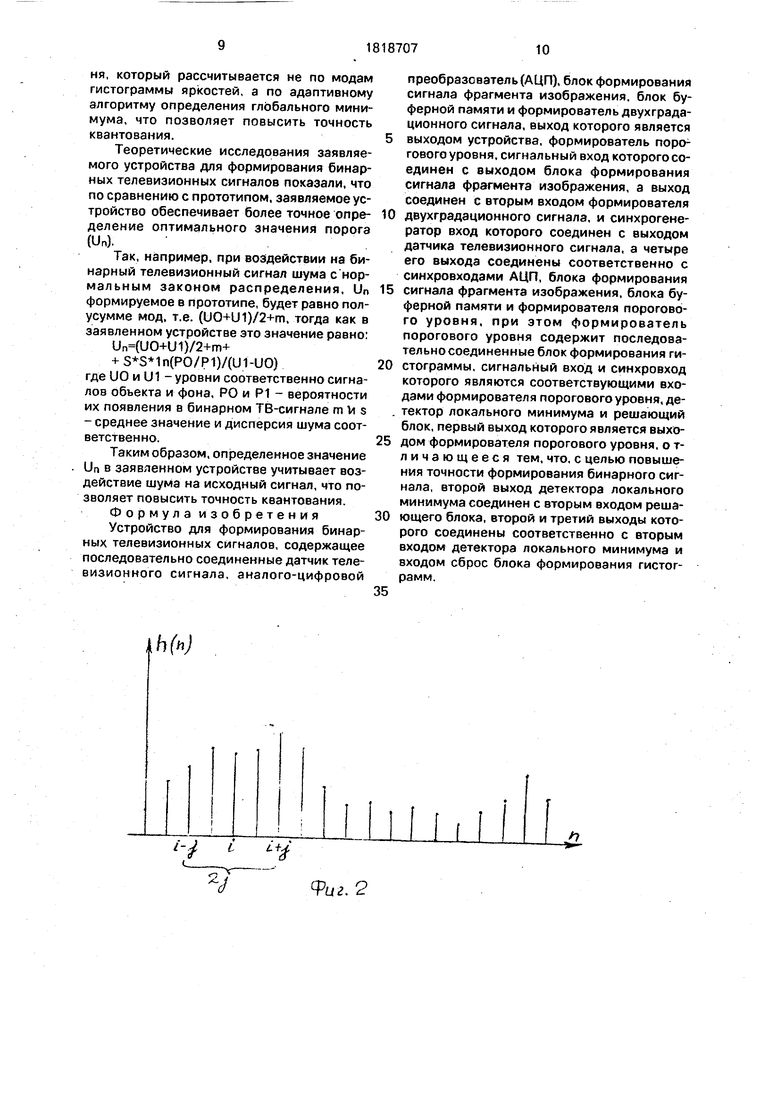

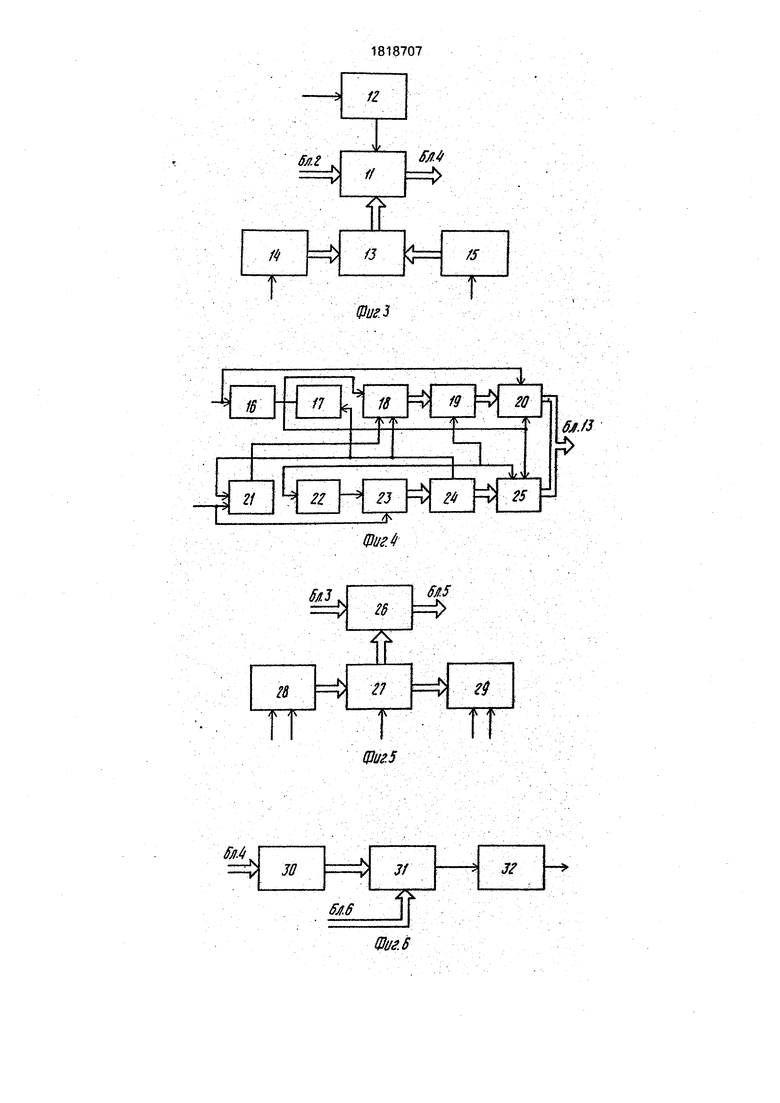

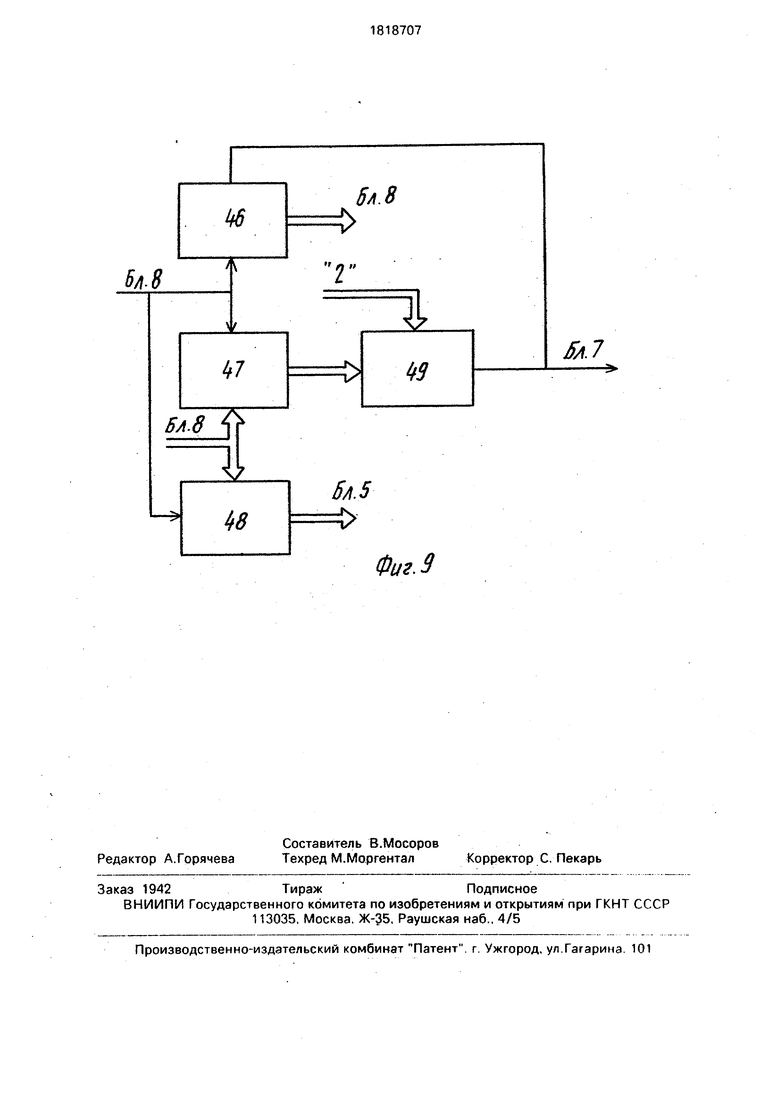

На фиг.1 представлена структурная электрическая схема устройства для формирования бинарных ТВ - сигналов; на фиг.2 -пример гистограммы распределения яркостей фрагмента; на фиг.З - структурная электрическая схема блока формирования сигнала фрагмента изображения; на фиг.4 - схема формирователя адреса считывания; на фиг.5- схема блока буферной памяти; на фиг.б - схема формирователя двухградаци- омного сигнала; на фиг,7 - схема блока формирования гистограммы; на фиг.8 - схема детектора локального минимума; на фиг.9 - схема решающего блока.

Устройство (фиг. 1) содержит последовательно соединенные датчик 1 ТВ-сигнала, зналого-цифровой преобразователь 2, блок 3 формирования сигнала фрагмента изображения, блок 4 буферной памяти и формирователь5 двухградационного ситналэ.а также формирователь 6 порогового уровня, выполненный в виде последовательного соединенных блока 7 формирования гистрог- рамм, детектора 8 локального минимума и решающего блока 9. Кроме этого, устройство содержит синхрогенератор 10, первый, второй, третий, четвертый выходы которого соединены с выходами синхронизации ана- логр-цифрового преобразователя 2, блока 3 Формирования сигнала фрагмента изображения, блока 4 буферной памяти и формирователя б порогового уровня. Второй вход формирователя 5 двухградационного сигнала соединен с выходом формирователя 6 порогового уровня, сигнальный вход которого соединен с выходом блока 3 формирования сигнала фрагмента.

Аналого-цифровой преобразователь 2 может быть выполнен в виде последовательно соединенных фильтра нижних частот, блока фиксации уровня видеосигнала и собственно, аналого-цифрового преобразователя.

Блок 3 формирования сигнала фрагмента изображения (фиг.З) содержит блок 11 ОЗУ, формирователь 12 сигналов RAS, CAS, WE, коммутатор 13 адресов, формирователи адресов записи 14 и считывания 15,

Формирователь 15 адресов считывания (фиг.4) содержит делители 16-18, счетчик 20, элемент ИЛИ 21, делитель 22, счетчик 23, регистр 24, счетчик 25.

Блок буферной памяти 4 (фиг.5) содержит блок 26 буферного ОЗУ, коммутатор 27 адресов, счетчик - формирователь 28 адресов записи и счетчик - формирователь 29 адресов считывания,

.0Формирователь 5 двухградационного сигнала (фмг.6) содержит входной регистр 30, компаратор 31 и скремблер 32.

Блок формирования гистограммы 7 (фиг.7) содержит коммутатор 33, блок 34

5 ОЗУ, счетчик 35, элемент И 36 и сумматор 37..

Детектор локального минимума (ДЛМ) 8 (фиг.8) содержит регистр 38, регистр задержки 39, регистры 40,41, компараторы 42,43,

0 Т-триггер 44, схему И 45. Вход регистра 38 подсоединен к выходу ОЗУ 34 блока 7, а выход - к входам регистра задержки 39 и компаратора 43, второй вход которого подключен к выходу регистра 40. Вход регистра

5 40 подключен к выходу регистра задержки 39.

Выход компаратора 43 соединен со входами Т-триггера 44 и схемы 1Л 45, второй вход которой соединен с выходом Т-тригге0 ра 44. Входы регистра 41 и компаратора 42 соединены с выходом счетчика 35 блока 7. Вход разрешения записи регистра 41 соединен с выходом схемы 1/145, а выход является первым выходом детектора локального ми5 нимума 8. На вход компаратора 42 подается

значение N, а выход его является вторым

выходом детектора локального минимума 8.

Решающий блок (РБ) 9 (фиг.9) содержит

счетчики 46, 47, регистр 48. компаратор 49.

0 Вход Сброс счетчиков соединен с выходим компаратора 42 детектора 8. Выход .счетчика 46 подсоединен с управляющему входу регистра задержки 39 детектора 8, а счетный вход к выходу компаратора 49, ко5 торый также является выходом решающего блока 9, На первый вход компаратора 49 подается код числа 2, а второй вход соединен; с выходом счетчика 47, управляющий вход которого соединен с выходом регистра

0 41 детектора 8.

Управляющий вход регистра 48 соединен с выходом компаратора 42, а второй вход соединен с выходом регистра 41 детектора 8, а выход является первым выходом

5 решающего блока 9.

Устройство работает следующим образом.

ТВ-сигнал с выхода датчика 1 поступает на первый вход АЦП 2, с выхода которого (в цифровой форме) по 6-разрядной шине проходит на первый вход блока 3. Блок 3 является устройством памяти на кадр телевизионного изображения, выполненным на базе динамических микросхем ОЗУ емкостью 64 Кбит, причем запись в память производится постоянно в соответствии с ТВ-стандартом, а считывание - по фрагментам размером 8x8 элементов. Формирователь 14 адреса записи (фиг.З) представляет собой 16-разрядный счетчик, причем первые 8 разрядов формируют адрес по строке, а остальные 8 разрядов - адрес по столбцу для микросхем блбка 11.

Формирователь 15 адресов считывания (фиг.4) при размере кадра 256x256 элемен- тов. работает следующим образом. Счетчик 20 формирует 8-разрядную комбинацию адреса по строке. На его первый вход (счетный) подается сигнал тактовой частоты с выхода синхрогенератора 10, После первых восьми тактов счетчик 20 сбрасывается в О сигналом с выхода делителя 16. Таким образом, сформированы адреса по строке первых восьми элементов первой строки кадра, что соответствует 8 тактам второй строки фрагмента, таким же, как и для первой строки, однако после восьмого такта по сигналу делителя 16 срабатывает на 1 такт счетчик 25, который формирует адрес по столбцу для блока 11. После каждого цикла делителя 16 частоты на 8 срабатывает делитель 18, 8 разрядный выход которого соединен с установочным входом счетчика 20. При этом после окончания считывания фрагмента состояние делителя 18 увеличивается на 8. Это состояние может быть передано на установочные входы счетчика 20 только после разрешающего сигнала, поступающего на второй вход регистра 19с выхода делителя 17.

Таким образом, по окончании первого фрагмента счетчик 20 начинает счет с состояния 8, а счетчик 25 этим же сигналом возвращается в состояние О. Далее циклы повторяются до окончания первых 64 фраг- ментов, что соответствует первым восьми строкам полного кадра изображения.

По окончании считывания 64-го фрагмента, т.е. после считывания последнего элемента восьмой строки полного кадра изображения, состояние счетчика 25 увеличивается на 8, так как разрешающий сигнал с выхода переноса делителя 18 разрешает задачу на установочные входы счетчика 25 состояния выхода счетчика 23, который за время считывания первых 64 фрагментов восемь раз срабатывает от выходного сигнала делителя 22. В этот же элемент делитель 18 устанавливается в состояние О сигналом с выхода элемента ИЛИ 21. Начинается

считывание по указанному выше алгоритму очередных 64 фрагментов, по окончании которого состояние счетчика 25 увеличивается еще на 8, и так далее до прихода на вход элемента ИЛИ 21 кадрового синхроимпульса считывания с соответствующего выхода синхрогенератора 10, который приводит всю схему в исходное положение.

С выхода блока 3 отсчеты сигнала подаются на первый вход блока 4 буферной памяти и на первый вход формирователя 6. Блок 4 (фиг.5) предназначен, во-первых, для задержки содержимого фрагмента изображения на время, необходимое для анализа с целью формирования порогового уровня (такой анализ выполняет формирователь 6). а во-вторых, для формирования такой скорости считывания из буферного ОЗУ, которая была бы согласована с параметрами представляемого канала связи. Особенностью работы блока 4 является то, что содержимое нечетных, начиная с первого, и четных, начиная с второго фрагментов изображения, размещается в разных областях ОЗУ, что реализуется подачей на седьмой адресный вход блока 26 уровня О при записи и считывания нечетных фрагментов и уровня 1 при записи и считывании четных фрагментов..

Отсчеты сигнала фрагмента с выхода 4 поступают на первый вход формирователя 5 (фиг.6). Входной регистр 30 предназначен для фазирования разряда отсчетов сигнала. Компаратор 31 предназначен для формирования однозарядного сигнала графического изображения с пороговым уровнем формирователя 6. Скремблер 32 выполнен как рекуррентная линия задержки на регистрах сдвига и предназначен для перемещения выходного сиглала с целью обеспечения возможности выделения тактовой частоты на приемной стороне.

При считывании содержимого фрагмен-. та изображения из блока 3 (фиг.7) отсчеты сигнала через коммутатор 33 подаются на адресный вход блока 34 ОЗУ. Циклы записи и считывания в блоке 34 сформированы так, что во время первой половины тактового инвервала частоты считывания Т1, происходит считывание из блока 34 содержимого ячейки, адрес которой удерживается на первом входе в течении тактово го интервала Т1, а во вторую половину тактового интервала происходит запись в блок 34 в ячейку с тем же адресом. Так как информационный вход блока 34 соединен с выходом сумматора, который добавляет 1 к содержимому данной ячейки памяти, считанному в первую половину тактового интервала, то к концу считывания фрагмента из блока 3 в ячейках.

адреса которых соответствуют наиболее вероятным уровнем сигнала во фрагменте, находятся наибольшие числа. Таким образом, к концу считывания фрагмента из блока 3 в блок 4 и формирователь 6, в блоке 34 формируется гистрограмма яркостей фрагмента. Пример такое гистограммы представлен на фиг.2. Обозначения; п-дискретные значения яркости входного ТВ - сигнала, получен- ные на выходе блока АЦП, h(n) - соответствующие значения гистограммы, (- i-e значение яркости, j-величина окрестности.

Для считывания значений гистограммы h(n)c помощью коммутатора 33 подключается адресный вход блока 34 к выходу счетчика 35, формируемые этим выходом адреса являются соответствующими значениями яркости ТВ-сигнала.

Для обеспечения многократного считывания значений гистограммы на счетчик 35 поступает сигнал сброс, формируемый компаратором 49 решающего блока 9. Для обнуления ячеек памяти служит сигнал, который отключает схему И 36 при одновременном переборе счетчиком 35 всех ячеек памяти 34. Нахождение значения в прототипе связано с определением максимумов гистограммы, которые соответствуют модам белого и черного. Положение этих максимумов определяется по выражению:

hmax arg{max h(n)}, ,N /U, где hmax - глобальный максимум белого (черного), U - некоторая окрестность точки глобального максимума.

Предлагаемое решение исключает необходимость как поиска глобального максимума, так и задания априорного значения размера окрестности U и основано на адаптивном алгоритме поиска глобального минимума hmin гистограммы. Следует отметить, что окрестности границ гистограммы не могут быть точками глобального минимума, поскольку на границах гистограмма монотонно увеличивается или уменьшается.

Для нахождения глобального минимума hmin предлагается следующий алгоритм, который реализуется блоками 8 и 9:

1. -Для ie 0,N, j€ 0,1X1/2 находим разности AYi Yj(l+1)-Yj(i). где Yj(i) h (l-j)+ h(i- j + 1)+...+h (i+)) или, что то же самое, (l)-h(i-2j-1}, причем h(H для КО или .

2. Анализируется знак разностей YI для каждого i. Точки I-J, в который YI меняет знак с - на +, соответствуют лбкальному минимуму данной гистограммы hmin(i), найденному с размером окрестности j.

3. Если количество найденных минимумов больше или равно 2, то размер j окрестности увеличивается на 1 и поиск глобального минимума повторяется. В противном случае точка i-j будет соответствовать искомому порогу.

Рассмотрим реализацию этого алгорит-; ма детектором локального минимума 8 и решающего блока 9.

0 Дискретные значения гистограммы h(l) поступают в регистр 38, а соответствующие им значениями адреса i поступают на регистр 41. С выхода регистра 38 значения h(i) поступают на регистр задержки 39, где за5 держиваются на 2J+1 тактов (значение величины j поступает на управляющий вход данного регистра с счетчика 46 решающего блока 9). Задержанные значения h(i-2j-1) поступают для записи в регистр 40. Значения

0 h(i) и h(i-2j-1) поступают на компаратор 43.

Фронт выходного импульса компаратора 43 определяет знак разности h(i) и h(i-2j- 1). В случае, когда фронт отрицательный (что соответствует знаку -), срабатывает Т5 триггер 44, который разрешает через схему И 45 выдачу значения }+| регистром 41. Записанное значение i-j соответствует локальному минимуму гистограммы hmin (i-j) при заданном значении окрестности j.

0 Значение i-j с выхода регистра 41 поступает на регистр 48 решающего блока 9.

Для определения конца поиска служит компаратор 42, который сравнивает текущее значение i с максимально возможным

5 значением N и в случае, когда , формирует би гнал Конец, поступающий в решающий блок 9.

Счетчик 47 решающего блока 9 подсчитывает количество локальных минимумов в

0 данной гистограмме h(n). Его выход подключен ко входу компаратора 49, на втором входе которого задан код числа 2. Если количество минимумов в гистограмме больше или равно 2, то компаратором 49 выра5 батывается сигнал Сброс, который поступает на тактовый вход счетчика 46, увеличивающего на 1 значение окрестности j. Сигнал Сброс поступает на счетчик 35 блок 7 для повторного считывания данной

0 гистограммы.

Сигнал Конец с блока 8 сбрасывает в начальное состояние счетчики 46, 47, а также разрешает запись в регистр 48 значения I-j, соответствующего глобальному миниму5 му hmin(i-j), которое поступает на формирователь 5 и удерживается на нем на время считывания содержимого фрагмента изображения с блока 4. Эта величина i является пороговым уровнем для квантования сигнала полутонового изображения на два уровня, который рассчитывается не по модам гистограммы яркостей, а по адаптивному алгоритму определения глобального минимума, что позволяет повысить точность квантования.

Теоретические исследования заявляемого устройства для формирования бинарных телевизионных сигналов показали, что по сравнению с прототипом, заявляемое устройство обеспечивает более точное определение оптимального значения порога

(Un).

Так, например, при воздействии на бинарный телевизионный сигнал шума с нормальным законом распределения, Un формируемое в прототипе, будет равно полусумме мод, т.е. (UO+U1)/2+m, тогда как в заявленном устройстве это значение равно:

Un(UO+U1)/2+m+

+ (PO/P1)/(U1-UO) где UO и U1 - уровни соответственно сигналов объекта и фона, РО и Р1 - вероятности их появления в бинарном ТВ-сигнале m Vi s - среднее значение и дисперсия шума соответственно.

Таким образом, определенное значение Un в заявленном устройстве учитывает воздействие шума на исходный сигнал, что позволяет повысить точность квантования.

Формула изобретения

Устройство для формирования бинарных телевизионных сигналов, содержащее последовательно соединенные датчик телевизионного сигнала, аналого-цифровой

преобразователь(АЦП), блок формирования сигнала фрагмента изображения, блок буферной памяти и формирователь двухграда- ционного сигнала, выход которого является

выходом устройства, формирователь порогового уровня, сигнальный вход которого соединен с выходом блока формирования сигнала фрагмента изображения, а выход соединен с вторым входом формирователя

двухградационного сигнала, и синхрогене- ратор вход которого соединен с выходом датчика телевизионного сигнала, а четыре его выхода соединены соответственно с синхровходами АЦП, блока формирования

сигнала фрагмента изображения, блока буферной памяти и формирователя порогового уровня, при этом формирователь порогового уровня содержит последовательно соединенные блок формирования гистограммы, сигнальный вход и синхровход которого являются соответствующими входами формирователя порогового уровня, детектор локального минимума и решающий блок, первый выход которого является выходом формирователя порогового уровня, о т- личающееся тем, что, с целью повышения точности формирования бинарного сигнала, второй выход детектора локального минимума соединен с вторым входом решающего блока, второй и третий выходы которого соединены соответственно с вторым входом детектора локального минимума и входом сброс блока формирования гистограмм.

| название | год | авторы | номер документа |

|---|---|---|---|

| Телевизионное устройство для формирования двухградационного сигнала графических изображений | 1986 |

|

SU1356260A1 |

| Телевизионное устройство для формирования двухградационного сигнала графических изображений | 1988 |

|

SU1633522A2 |

| ТЕЛЕВИЗИОННЫЙ ИЗМЕРИТЕЛЬ КООРДИНАТ ПОДВИЖНЫХ ТОЧЕЧНЫХ ОБЪЕКТОВ | 1989 |

|

SU1623537A1 |

| Телевизионное устройство для формирования двухградационного сигнала графических изображений | 1988 |

|

SU1663778A1 |

| Устройство для бинарного квантования телевизионного видеосигнала | 1983 |

|

SU1129745A1 |

| Телевизионный координатор | 1983 |

|

SU1109956A1 |

| Устройство для селекции изображений объектов | 1986 |

|

SU1429141A1 |

| Устройство для определения экстремальных значений | 1989 |

|

SU1615747A1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1993 |

|

RU2037842C1 |

| Устройство для коррекции изображений объектов | 1989 |

|

SU1755305A2 |

IhW

Фиг. 2

№.

5Л.6

fart

Й

IT

зг

Ж

1

„if

Фиг8

W

S

5/1.8

л

г

V

Ј

Бл.8

-

8

6/1.5

D

бл.8

1

ia

&I.7

Фиг. 9

Авторы

Даты

1993-05-30—Публикация

1991-05-24—Подача