Изобретение относится к ускорительной технике, в частности к системам высокочастотного питания резонансных линейных ускорителей заряженных частиц.

Цель изобретения повышение КПД и надежности стабилизации амплитуды высокочастотного поля в резонаторе ускорителя.

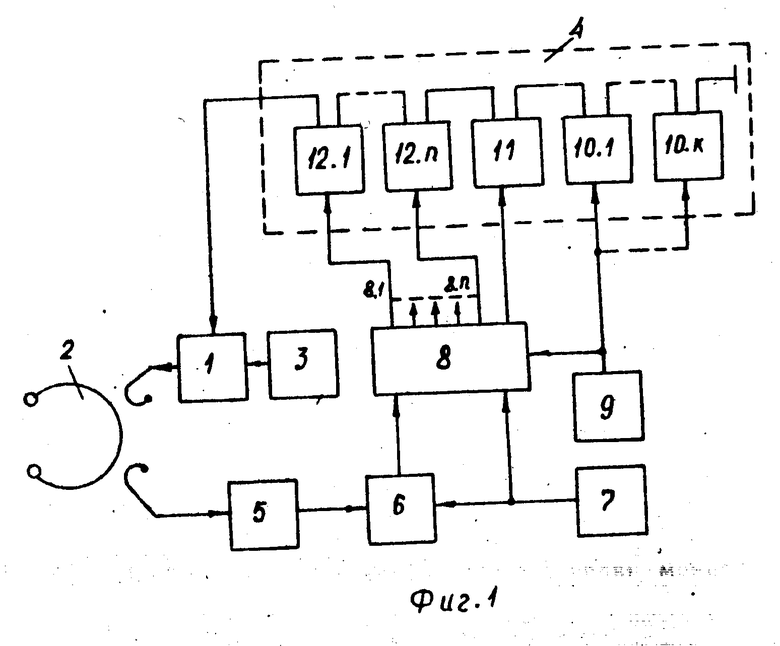

На фиг. 1 приведена структурная схема предлагаемого устройства стабилизации амплитуды высокочастотного поля в резонаторе ускорителя; на фиг. 2 приведена структурная схема анодного модулятора; на фиг. 3 структурная схема блока аналого-дискретного управления; на фиг. 4 и 5 показаны временные диаграммы работы основных узлов предлагаемого устройства.

Устройство стабилизации амплитуды высокочастотного поля в резонаторе ускорителя содержит усилитель мощности 1, выход которого подключен к резонатору 2 ускорителя, а вход соединен с выходом возбудителя 3, анодный модулятор 4 с выходом, подключенным к анодной цепи усилителя мощности, цепь отрицательной обратной связи, включающую в себя амплитудный детектор 5, подключенный к резонатору 2, схему сравнения 6, входы которой подключены к выходам амплитудного детектора 5 и источника опорного напряжения 7, блок аналого-дискретного управления 8 с двумя аналоговыми входами управления, один из которых подключен к выходу схемы сравнения 6, а другой к выходу источника опорного напряжения 7, и с выходами управления, подключенными к соответствующим входам управления анодного модулятора 4, и с входом синхронизации, подключенным к выходу формирователя синхроимпульсов 9, к которому также подключен ряд входов управления анодного модулятора 4.

Усилитель мощности 1 усиливает высокочастотный сигнал возбудителя 3 и передает его в резонатор ускорителя 2. Усилитель мощности 1 работает в перенапряженном режиме и уровень поля в резонаторе 2 в сильной степени зависит от величины напряжения анодного питания усилителя мощности 1, которое вырабатывает анодный модулятор 4.

Анодный модулятор 4 содержит k (где k 1, 2, 3.) модуляторных ячеек 10 с нерегулируемыми выходными напряжениями и управляемых помимо цепи отрицательной обратной связи непосредственно от формирователя синхроимпульсов 9, одну модуляторную ячейку 11 с регулируемым выходным напряжением и управляемую сигналом обратной связи от аналогового выхода блока аналого-дискретного управления 8, n (где n 1, 2, 3.) модуляторных ячеек 12 с нерегулируемыми выходными напряжениями и управляемых сигналом обратной связи от n логических выходов блока аналого-дискретного управления 8. Последовательно соединенные выходы всех модуляторных ячеек создают суммарное импульсное напряжение, которое подается в анодную цепь усилителя мощности 1. Суммарное выходное напряжение модулятора и его мощность определяются требуемым напряжением анодного питания и установленной мощностью усилителя, энергетическими возможностями и количеством модуляторных ячеек. Сложение выходных напряжений модуляторных ячеек может быть реализовано непосредственным последовательным соединением нагрузочных зажимов ячеек, но при этом схема каждой последующей ячейки оказывается под высоким суммарным потенциалом предыдущих ячеек, а источник первичного электропитания модуляторных ячеек и аналого-дискретного управления, находящееся под "нулевым" потенциалом, должны быть отделены от входных зажимов питания и управления модуляторных ячеек разделительными трансформаторами с высоковольтной изоляцией. Более просто анодный модулятор 4 может быть реализован по схеме, приведенной на фиг. 2. Здесь все модуляторные ячейки 10, 11, 12 находятся под "нулевым" потенциалом и непосредственно связаны с источником питания 13 и блоком аналого-дискретного управления 8, а сложение выходных напряжений модуляторных ячеек осуществляется с помощью импульсных трансформаторов 14, имеющих высоковольтную разделительную изоляцию. Вторичные обмотки импульсных трансформаторов 14 соединены последовательно и зашунтированы диодами 15.

Диоды 15 обеспечивают прохождение тока нагрузки модулятора помимо выходных цепей выключенных модуляторных ячеек. Модуляторные ячейки 11, 12, управляемые сигналом отрицательной обратной связи, должны иметь накопитель энергии с частичным разрядом и в качестве коммутатора использовать транзистор или электронную лампу. В модуляторных ячейках 10, управляемых помимо цепи отрицательной обратной связи непосредственно от формирователя синхроимпульсов 9, могут быть использованы накопители энергии как с частичным, так и с полным разрядом, а в качестве коммутаторов любые типы из известных коммутирующих приборов.

Выполнение анодного модулятора в виде предложенного набора n+k модуляторных ячеек обусловлено тем, что в практических схемах минимальный уровень высокочастотного поля в резонаторе и минимальное выходное напряжение анодного модулятора заданы нижней границей диапазона авторегулирования, которая обычно лежит ниже номинальных значений поля и анодного напряжения не более чем на 10-30% При этом уровень поля в резонаторе до нижней границы диапазона авторегулирования может быть получен за счет одновременного включения k модуляторных ячеек 10 помимо цепи отрицательной обратной связи, непосредственно от формирователя синхроимпульсов 9. Набор из k модуляторных ячеек может быть заменен одной укрупненной модуляторной ячейкой с выходной мощностью и напряжением в k раз большими. Набор из n модуляторных ячеек 12 и модуляторная ячейка 11 управляются сигналом ошибки по цепи отрицательной обратной связи и обеспечивает автоматическое изменение выходного напряжения анодного модулятора в заданном динамическом диапазоне регулирования. При номинальном уровне поля в резонаторе, когда сигнал ошибки в цепи отрицательной обратной связи равен нулю, включены все модуляторные ячейки 10, модуляторная ячейка 11 и часть модуляторных ячеек 12. При отключении поля в резонаторе в меньшую сторону от номинального появляющийся положительный сигнал ошибки в зависимости от своей величины включает ряд дополнительных модуляторных ячеек 12, а при отключении в большую сторону сигнал ошибки меняет свой знак и осуществляет выключение ячеек 12, работающих при номинальном уровне поля в резонаторе. Одновременно происходит соответствующее изменение выходного напряжения модуляторной ячейки 11. Этим обеспечивается противофазное регулирование возбуждения резонатора и стабилизация амплитуды поля в нем. Включение и выключение необходимого числа ячеек из набора n модуляторных ячеек 12 в процессе регулирования выходного напряжения анодного модулятора 4 производится дискретно в зависимости от уровня сигнала ошибки логическими сигналами, поступающими на входы соответствующих ячеек в последовательности 1, 2, 3. n от n логических выходов блока аналого-дискретного управления 8. Модуляторные ячейки 12 работают в ключевом режиме, имеют равные и постоянные амплитуды импульсов выходных напряжений и обеспечивают дискретное регулирование выходного напряжения анодного модулятора. Модуляторная ячейка 11 с регулируемым выходным напряжением работает в линейном режиме и обеспечивает пропорциональное сигналу ошибки регулирование выходного напряжения модулятора. Модуляторная ячейка 11 осуществляет пропорциональное регулирование выходного напряжения модулятора в окне между установленными уровнями дискретного срабатывания любых двух смежных модуляторных ячеек 12. Размах линейного участка динамического диапазона регулирования выходного напряжения модуляторной ячейки 11 равен значению выходного напряжения модуляторной ячейки 12. Это обеспечивает возможность линейного регулирования в окне между уровнями срабатывания смежных модуляторных ячеек 12. Пропорциональное управление модуляторной ячейки 11 осуществляется от аналогового выхода блока аналого-дискретного управления 8.

Управляющий сигнал на входе блока аналого-дискретного управления 8 пропорционален сумме сигнала ошибки по амплитуде и напряжения опорного источника 7. Сигнал ошибки вырабатывается на выходе схемы сравнения 6 за счет сравнения продетектированного высокочастотного сигнала, поступающего с выхода амплитудного детектора 5, с сигналом источника 7 стабильного опорного напряжения. Высокочастотный сигнал обратной связи поступает на вход амплитудного детектора 5 по линии передачи из резонатора ускорителя 2. Схема сравнения может быть реализована на основе дифференциального усилителя. Формирователь синхроимпульсов 9 задает рабочую длительность и частоту следования импульсов выходного напряжения анодного модулятора 4, а следовательно, и временной режим работы усилителя мощности 1 и резонатора 2. Синхронизация работы системы стабилизации осуществляется путем одновременной подачи с выхода формирователя синхроимпульсов импульса разрешения заданной длительности на вход синхронизации блока аналого-цифрового управления и на входы k модуляторных ячеек 10.

Блок аналого-дискретного управления 8 осуществляет усиление сигнала ошибки, сложение его с напряжением опорного источника вырабатывает дискретные сигналы управления модуляторными ячейками 12 и аналоговый сигнал управления модуляторной ячейкой 11. Усиление сигнала ошибки обеспечивает получение необходимого коэффициента стабилизации в системе, а введение напряжения опорного источника в сигнал управления обеспечивает возможность исходной установки требуемого номинального уровня поля в резонаторе за счет регулировки опорного напряжения. В качестве преобразователя аналогового сигнала ошибки в дискретный сигнал управления, осуществляющий логическую операцию "включено-выключено", может быть использован компаратор напряжения.

Блок аналого-дискретного управления 8, построенный на основе компараторов напряжения, может быть реализован по схеме, приведенной на фиг. 3. В данной схеме n компараторов 16, каждый из которых имеет логический выход управления, логический вход стробирования и два аналоговых измерительных входа. Уровни срабатывания смежных компараторов сдвинуты на одинаковую фиксированную величину относительно друг друга и лежат в границах максимально ожидаемого диапазона абсолютного изменения сигнала ошибки в цепи обратной связи, что обеспечивается подключением аналоговых входов установки уровней компарирования к делителю напряжения 17, питаемого от источника напряжения 18. Другие аналоговые входы компараторов, куда поступает компарируемый сигнал обратной связи, подключены параллельно к выходу суммирующего усилителя 19, который усиливает сигнал ошибки, поступающий с выхода схемы сравнения 6, и суммирует его с сигналом источника опорного напряжения 7.

Выход суммирующего усилителя 19 также подключен к первому входу дифференциального усилителя 20, второй вход которого через n развязывающих диодов 21 и n ключей управления 22 подключен к n плечам делителя 17, задающих требуемые уровни срабатывания n компараторов 16. Вход управления каждого из ключей управления 22 подключен к логическому выходу соответствующего компаратора 16, что обеспечивает автоматическое изменение напряжения на втором входе дифференциального усилителя 20 до уровня срабатывания компаратора, имеющего максимальный уровень компарирования из всех включенных в данный момент компараторов. Выход дифференциального усилителя 20 через ключ стробирования 23 подключен к входу регулируемой модуляторной ячейки 11. Вход управления ключа стробирования 23 и логические выходы стробирования компараторов 16 подключены к выходу формирователя синхроимпульсов 9, по которому поступает сигнал разрешения на работу системы. Ключ стробирования 23 задает время работы регулируемой модуляторной ячейки 11. Предложенное подключение входов дифференциального усилителя 20 обеспечивает пропорциональное регулирование выходного напряжения модуляторной ячейки 11 в окне между уровнями срабатывания любых двух смежных модуляторных ячеек 12. Это обусловлено тем, что выходной сигнал дифференциального усилителя 20, пропорциональный разности между выходным сигналом суммирующего усилителя 19 и уровнем компарирования компаратора 16, представляет собой долю изменяющегося сигнала ошибки, заключенную в окне между уровнями компарирования смежных компараторов 16. Эта доля сигнала ошибки при своем изменении изменяет выходное напряжение модуляторной ячейки 11 на величину выходного напряжения модуляторной ячейки 12. При достижении выходным сигналом суммирующего усилителя 19 уровня срабатывания очередного компаратора 16 включается или выключается соответствующая модуляторная ячейка 12, изменяя скачком свое выходное напряжение. Одновременно выходным логическим сигналом сработавшего компаратора 16 включается или выключается соответствующий ключ управления 22 и выходной сигнал дифференциального усилителя 20 скачком изменяется от одного предельного значения до другого, изменяя выходное напряжение модуляторной ячейки 11 на величину выходного напряжения сработавшей модуляторной ячейки 12, но в противоположную сторону. Поэтому в момент скачкообразного включения или отключения очередной модуляторной ячейки 12 выходное напряжение анодного модулятора не изменяется, а его изменение происходит в окне между уровнями срабатывания смежных модуляторных ячеек 12 в процессе изменения сигнала ошибки за счет регулирования выходного напряжения модуляторной ячейки 11 и фиксируется срабатыванием очередной модуляторной ячейки 12. Тем самым реализуется режим квазилинейного регулирования выходного напряжения анодного модулятора, близкий к режиму регулирования в прототипе. Соотношение напряжений источника 18, питающего делитель 17, и опорного источника 7 выбирается так, чтобы при нулевом сигнале ошибки, когда уровень поля в резонаторе равен номинальному, из набора n модуляторных ячеек 12 было включено m ячеек, где m < n. Тогда m ячеек обеспечивают регулирование выходного напряжения анодного модулятора при возрастании поля в резонаторе, а n-m ячеек при его уменьшении.

Принцип работы предлагаемого устройства стабилизации поясняется эпюрами выходных напряжений основных узлов устройства, приведенными на временных диаграммах фиг. 4. Устройство работает следующим образом. В паузе между рабочими импульсами U9 формирователя синхроимпульсов 9 сигнал ошибки U6 на выходе схемы сравнения 6 имеет максимально возможное значение, определяемое уровнем напряжения опорного источника 7 и ограниченное нелинейностью амплитудной характеристики схемы сравнения. При этом суммирующий усилитель 19 и дифференциальный усилитель 20 также находятся в нелинейных режимах и их выходные напряжения U19, U20 имеют максимальные значения, превышающие уровни срабатывания всех компараторов 16 и границу линейного участка амплитудной характеристики модуляторной ячейки 11. На эпюрах U6, U19 границы линейности условно обозначены уровнями Uл. На эпюре U19 также условно нанесены дискретные уровни сигнала обратной связи, соответствующие уровням поля в резонаторе, при которых происходит включение или отключение модуляторных ячеек 10, 12 в последовательности 1, 2.k.k+m, k+m+1, k+m+2,m+k-1, n+k.

В момент времени t1 на входах стробирования компараторов 16 и входах управления ключа стробирования 23 и модуляторных ячеек 10 скачком появляется сигнал разрешения U9 с выхода формирователя синхроимпульсов 9, включаются все модуляторные ячейки 10, 12, а модуляторная ячейка 11 вырабатывает максимальное выходное напряжение, равное выходному напряжению модуляторной ячейки 12. Выходные напряжения модуляторных ячеек 10, 12, соответствующие дискретным уровням срабатывания, приведенным на эпюре U19 представлены эпюрами U12(n), U12(n-1).U12(m+2), U12(m+1), U12(m).U10(1...k). Выходное напряжение модуляторной ячейки 11 характеризуется эпюрой U11. В указанный момент времени t1 на выходе анодного модулятора 4 формируется фронт импульса полного напряжения U4 с максимально возможной амплитудой U4m, что обеспечивает форсированное нарастание фронта высокочастотного напряжения U2 в резонаторе 2. По мере нарастания амплитуды напряжения в резонаторе растет продетектированный амплитудным детектором 5 сигнал на входе схемы сравнения 6, разность между выходным напряжением амплитудного детектора 5 и напряжением опорного источника 7 уменьшается и схема сравнения 6 переходит в линейный режим работы, уменьшая сигнал ошибки на входах усилителей 19, 20.

В момент времени t2, когда напряжение в резонаторе U2 достигает величины, отличающейся от номинального уровня U2н на величину Δ U2н, соответствующую верхней границе линейности Uл усилителя 19, выходное напряжение U19 усилителя 19 уменьшается до уровня выключения компаратора n-й модуляторной ячейки 12, n-й компаратор 16 и n-я модуляторная ячейка 12 выключаются (эпюра U12(n)). Одновременно закрывается n-й ключ управления 22, скачком снижается напряжение на соответствующем входе дифференциального усилителя 20 от величины n-го плеча делителя 17 до величины (n-1)-го плеча. При этом выходное напряжение U20 усилителя 20 и выходное напряжение U11 модуляторной ячейки 11 сохраняют максимальные величины на границе линейности их амплитудных характеристик. С момента времени t2 происходит замедление нарастания поля в резонаторе и изменяющийся сигнал ошибки пропорционально уменьшает выходное напряжение усилителя 20 и выходное напряжение модуляторной ячейки 11, уменьшая тем самым выходное напряжение U4 модулятора. К моменту времени t3 сигнал ошибки на выходе усилителя 19 (U19) уменьшается до уровня выключения (n-1)-го компаратора 16, выходное напряжение дифференциального усилителя 20 уменьшается до нуля, а выходное напряжение модуляторной ячейки 11 и выходное напряжение модулятора 4 уменьшается на величину выходного напряжения модуляторной ячейки 12, выходное напряжение модуляторной ячейки 11 приобретает нулевое значение. В момент времени t3 выключаются (n-1)-й компаратор 16 и (n-1)-й ключ управления 27, (n-1)-я модуляторная ячейка 12 также выключается (эпюра U12(n-1)) и уменьшает свое выходное напряжение до нуля. Напряжение на входе усилителя 20, связанное с делителем 17, скачком уменьшается до величины n-2-го плеча делителя 17, а выходное напряжение U20 усилителя 20 скачком увеличивается от нуля до максимального значения, увеличивая выходное напряжение модуляторной ячейки 11 на величину выходного напряжения модуляторной ячейки 12. Таким образом, в коммутационных процессах, происходящих в момент времени t3, выходное напряжение U4 модулятора 4 не изменяется и фиксируется на уровне, заданном n+k-1 включенными ячейками 10, 12. Далее снова происходит уменьшение выходного напряжения модуляторной ячейки 11 и выходного напряжения модулятора 4 по закону изменения сигнала ошибки до момента выключения n-2-й модуляторной ячейки и фиксирования выходного напряжения модулятора 4 на уровне, заданном n+k-2 включенными ячейками 10, 12. В промежутке времени t3-t6 по мере уменьшения сигнала ошибки происходит последовательное выключение n-m числа регулируемых сигналов обратной связи модуляторных ячеек 12 в соответствии с установленными уровнями их срабатывания делителем 17. В промежутках между уровнями срабатывания модуляторных ячеек 12 осуществляется пропорциональное регулирование выходного напряжения модуляторной ячейки 11 с периодическим возвратом его к исходному значению в моменты срабатывания модуляторных ячеек 12. В целом, в описанном процессе управления реализуется квазилинейное регулирование выходного напряжения модулятора 4.

В момент времени t6 сигнал ошибки U6 становится равным нулю и в соответствии с заданным напряжением опорного источника 7 включенными остаются k+m модуляторных ячеек 10, 12, а выходное напряжение модуляторной ячейки 11 устанавливается на уровне своего минимального значения U11н. При этом полное выходное напряжение анодного модулятора 4 устанавливается на уровне U4н, соответствующем установившемуся номинальному уровню поля в резонаторе U2н. Нижняя граница динамического диапазона регулирования выходного напряжения анодного модулятора с помощью цепи отрицательной обратной связи ограничен уровнем U4нг, который задается числом k модуляторных ячеек 10, не охваченных кольцом отрицательной обратной связи.

После окончания процесса установления номинального уровня поля в резонаторе в момент времени t7 включается импульс тока ускоряемого пучка (эпюра In), который действует в течение времени t7-t12. При разомкнутом кольце отрицательной обратной связи интенсивный ускоряемый пучок в сильной степени возмущает высокочастотное поле в резонаторе, что сопровождается уменьшением интенсивности самого ускоряемого пучка. Спады интенсивности тока пучка и амплитуды высокочастотного поля в резонаторе для случая разомкнутой отрицательной обратной связи показаны пунктирами на эпюрах In, U2 и характеризуются максимальными величинами Δ In, Δ U2n. При замкнутом кольце отрицательной обратной связи в момент включения ускоряемого пучка возникающее отклонение амплитуды напряжения в резонаторе приводит к появлению сигнала ошибки на выходе схемы сравнения и пропорциональному нарастанию напряжений U19, U20 на выходах усилителей 19, 20. Одновременно пропорционально нарастает выходное напряжение U11 модуляторной ячейки 11 от уровня U11н до максимального значения. При достижении сигналом ошибки уровня срабатывания (k+m+1)-й модуляторной ячейки 12 указанная ячейка включается и фиксирует выходное напряжение модулятора 4 на достигнутом уровне, а выходное напряжение модуляторной ячейки 11 скачком уменьшается от максимального значения до исходного уровня U11н. Это обеспечивается за счет включения соответствующих компаратора 16, ключа управления 27 и скачкообразного изменения напряжения на входе усилителя 20, связанном с делителем 17. При дальнейшем нарастании сигнала ошибки процессы аналого-дискретного управления в устройстве носят такой же периодический характер, как и при формировании фронта импульса, но только протекают в обратной последовательности. Переходный процесс в устройстве заканчивается к моменту времени t11, а его длительность определяется замедляющейся скоростью возмущения высокочастотного поля пучком и запаздыванием в кольце регулирования. В момент времени t11 в резонаторе, нагруженном пучком, устанавливается стационарный уровень поля, который отличается от номинального на величину остаточного отклонения амплитуды поля Δ U2nс. Установившийся уровень поля под пучком поддерживается выходным напряжением анодного модулятора, равным в промежутке времени t11-t12 величине U4n. На эпюрах U19, U20, U11 условно принято, что уровень выходного напряжения анодного модулятора U4n создается суммой выходных напряжений n+k-1 включенных модуляторных ячеек 10, 12 и некоторым установившемся уровнем U11n выходного напряжения модуляторной ячейки 11, который задан уровнем U20n выходного напряжения усилителя 20 и соответствует доле сигнала ошибки, превышающей уровень срабатывания n-1-го компаратора 16. Величина остаточного отклонения амплитуды поля Δ U2nс, как и в других системах стабилизации, определяется коэффициентом усиления в разомкнутом кольце регулирования и величиной внешнего возмущения поля с точностью до линейности амплитудной характеристики системы в заданном динамическом диапазоне регулирования.

В момент времени t12 ускоряемый пучок выключается и процессы в устройстве протекают в обратном порядке по сравнению с вышеописанными при включении пучка. В момент времени t16 переходные процессы в устройстве заканчиваются и в резонаторе устанавливается исходный номинальный уровень поля U2н. В случае, когда на амплитуду поля в резонаторе воздействуют возмущающие факторы, приводящие к возрастанию уровня поля в резонаторе относительно номинального значения U2н, на выходе схемы сравнения образуется сигнал ошибки с обратным знаком по отношению к вышерассмотренным случаям, а выходное напряжение U19 усилителя 19 становится ниже уровня, заданного источником опорного напряжения 7. В этом случае регулирование осуществляется за счет выключения модуляторных ячеек 12 из числа m и периодического изменения выходного напряжения модуляторной ячейки 11 до уровня U11н до максимального значения. Остаточное отклонение уровня поля в резонаторе будет иметь обратный знак по отношению к остаточному отклонению при нагрузке пучком.

В момент времени t17 выключается сигнал разрешения U9 формирователя синхроимпульсов 9, что приводит к выключению компараторов 16, ключей 22, 23 и всех модуляторных ячеек 10, 11, 12. При этом разрывается цепь отрицательной обратной связи, а выходное напряжение анодного модулятора становится равным нулю. В резонаторе начинается свободный процесс рассеяния накопленной энергии и к моменту времени t18 напряжения U2 в резонаторе становится равным нулю. Одновременно напряжения на выходах схемы сравнения 6 и усилителей 19, 20 возвращаются к исходным значениям. С приходом следующего сигнала разрешения с выхода формирователя синхроимпульсов 9 все процессы в устройстве повторяются.

В предлагаемом устройстве стабилизации регулирующим органом является цепь формирования импульса анодного модулятора, которая включает в себя последовательно соединенные по выходам (n+k) модуляторных ячеек равной мощности, работающих в ключевом режиме, и одну модуляторную ячейку такой же мощности, работающую в линейном режиме. В прототипе КПД мощной регулирующей лампы, работающей в линейном режиме, в процессе регулирования изменяется от максимального значения (порядка 0,8-0,9) при максимальном выходном напряжении до минимального значения (порядка 0,2-0,3) при минимальном выходном напряжении. Здесь КПД мощного регулятора в процессе регулирования может ухудшиться в 3-4 раза. В предлагаемом устройстве стабилизации в процессе регулирования n+k модуляторных ячеек с нерегулируемыми выходами сохраняют постоянное значение КПД равное вышеуказанному максимальному значению, а изменяется в вышеуказанных пределах только КПД одной модуляторной ячейки с регулируемым выходом. Можно показать, что общий КПД мощного регулятора в предлагаемом устройстве определяется соотношением:

η  где n+k число модуляторных ячеек с нерегулируемыми выходами;

где n+k число модуляторных ячеек с нерегулируемыми выходами;

η1 КПД модуляторной ячейки с нерегулируемым выходом;

η2 КПД модуляторной ячейки с регулируемым выходом.

Из приведенного соотношения следует, что с ростом числа модулятоpных ячеек с нерегулируемыми выходами общий КПД регулятора растет и приближается к КПД одной модуляторной ячейки, работающей в ключевом режиме. Так, уже при n+k 10 КПД регулятора отличается не более чем на 20% от его максимального значения в любом самом широком диапазоне регулирования выходного напряжения анодного модулятора устройства стабилизации амплитуды. Высокий КПД регулятора наряду с повышением экономичности устройства снижает тепловые нагрузки в мощных цепях регулирующего органа, что повышает надежность системы и расширяет допустимый динамический диапазон регулирования амплитуды. При этом высоковольтный анодный модулятор может быть выполнен из низковольтных полупроводниковых модуляторных ячеек, что увеличивает его ресурс работы, а следовательно, и надежность в долговременной эксплуатации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь напряжения с многозонной импульсной модуляцией | 1983 |

|

SU1343521A2 |

| Устройство для регулирования мощности магнетрона СВЧ-печи | 1985 |

|

SU1617670A1 |

| СПОСОБ УПРАВЛЕНИЯ СЛЕДЯЩИМ МНОГОЯЧЕЙКОВЫМ ПРЕОБРАЗОВАТЕЛЕМ | 1991 |

|

RU2026601C1 |

| МИКРОВОЛНОВЫЙ РАДИОМЕТР | 2022 |

|

RU2794063C1 |

| Устройство для управления регулятором напряжения | 1986 |

|

SU1379918A1 |

| СПОСОБ ГЕНЕРАЦИИ ТОРМОЗНОГО ИЗЛУЧЕНИЯ С ПОИМПУЛЬСНЫМ ПЕРЕКЛЮЧЕНИЕМ ЭНЕРГИИ И ИСТОЧНИК ИЗЛУЧЕНИЯ ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2010 |

|

RU2452143C2 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ВРЕМЕНЕМ ЭКСПОЗИЦИИ, КОЭФФИЦИЕНТАМИ УСИЛЕНИЯ И ЦВЕТОВЫМ БАЛАНСОМ В МАТРИЧНЫХ ФОТОПРИЕМНИКАХ (ВАРИАНТЫ) | 2006 |

|

RU2333614C1 |

| ЭЛЕКТРОННАЯ СИСТЕМА СТАБИЛИЗАЦИИ | 2018 |

|

RU2704728C1 |

| ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕННОГО НАПРЯЖЕНИЯ | 1991 |

|

RU2020707C1 |

| ПРОГРАММИРУЕМЫЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕННОГО НАПРЯЖЕНИЯ | 1992 |

|

RU2020709C1 |

Изобретение относится к ускорительной технике, в частности к системам высокочастотного питания резонансных линейных ускорителей заряженных частиц. Использование изобретения позволяет повысить КПД и надежность стабилизации амплитуды высокочастотного поля в резонаторе ускорителя. Сущность изобретения достигается тем, что в устройство введен блок аналого-дискретного управления, входы которого соединены с выходом блока сравнения, источника опорного напряжения и формирователя синхроимпульсов, а выходы подключены к анодному модулятору, при этом сам блок аналого-дискретного управления выполнен в виде набора n компараторов напряжения, первые входы которых соединены с выходом суммирующего усилителя и первым входом дифференциального усилителя, подключенного к ключу стробирования, вторые входы компараторов соединены с делителем напряжения, подключенным к источнику напряжения, и через ключи управления и развязывающие диоды с вторым входом дифференциального усилителя, а выходы компараторов подключены к входам ключей управления, а анодный модулятор выполнен в виде набора n + k модуляторных ячеек. 2 з.п. ф-лы, 5 ил.

| Мурин Б.П | |||

| Стабилизация и регулирование высокочастотных полей в линейных ускорителях ионов | |||

| М.: Атомиздат, 1971, с.243-260. |

Авторы

Даты

1995-07-20—Публикация

1990-07-27—Подача