5/Sw- 4

Ни

о

J.f

f

JShff

0

САЭ СО СО

1 X

ПГ

ь

Ля

Изобретение относится к электротехнике, в частности к преобразовательной технике (регулированим и стабилизации постоянных и переменнъгх напряжений)о

Цель изобретения - повьпчение точности регулирования выходного напряжения.

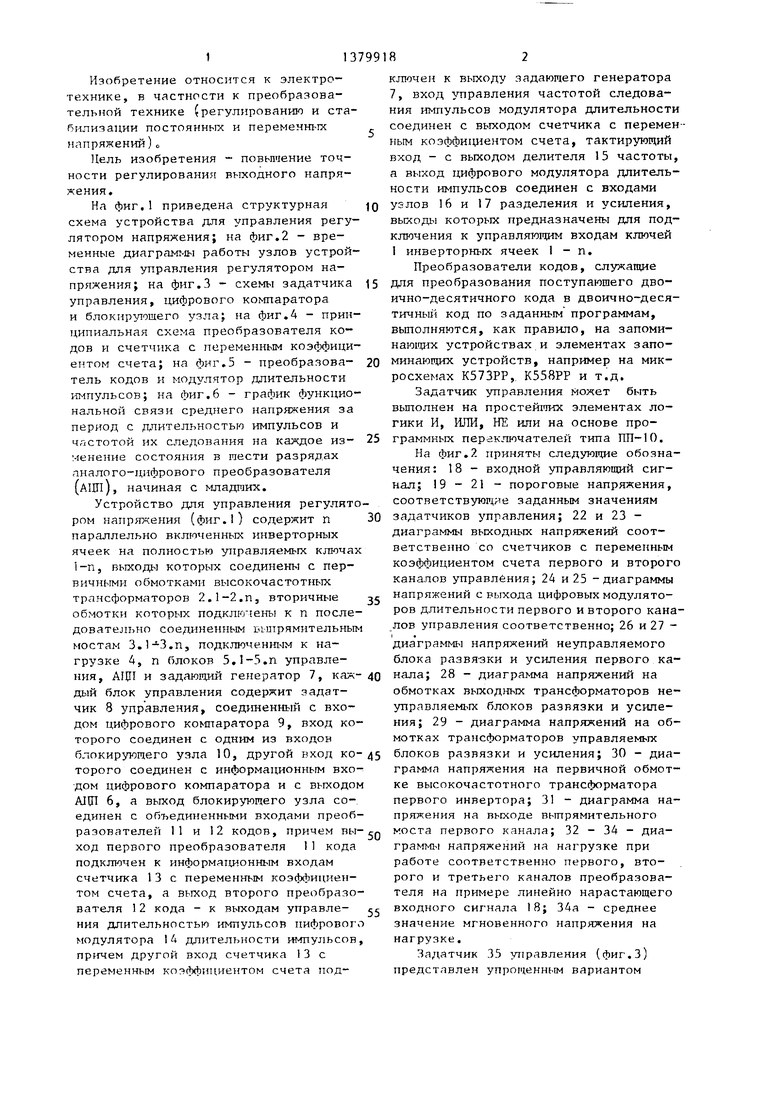

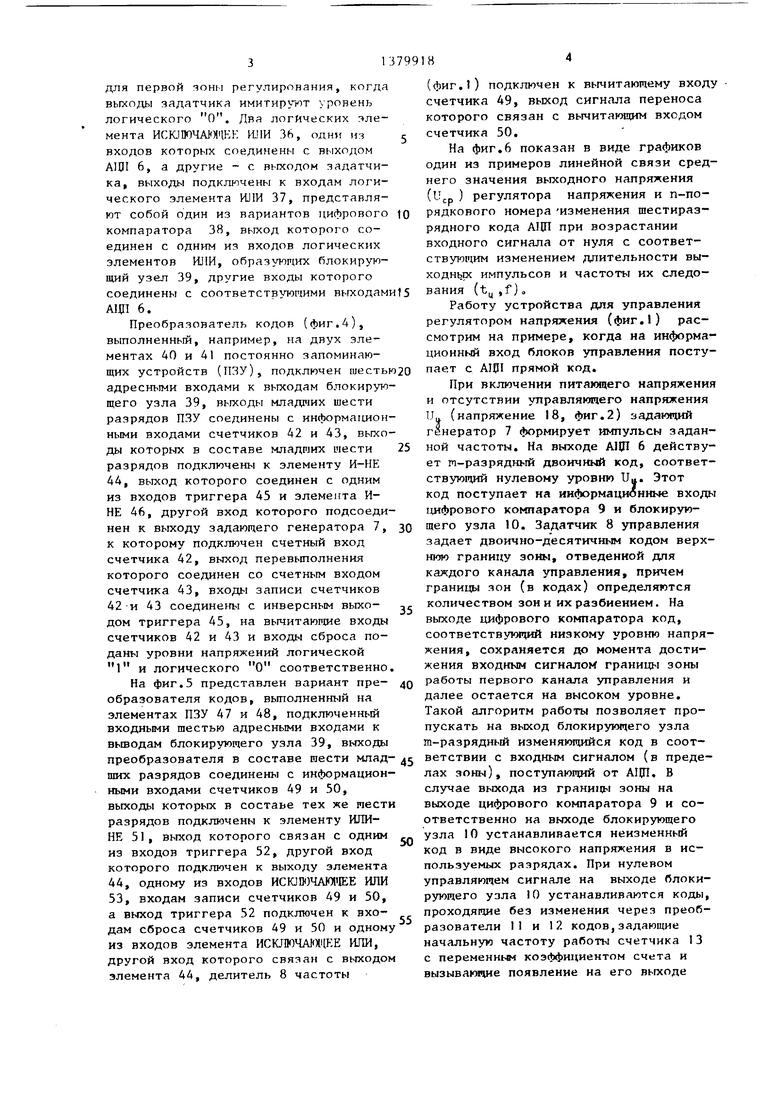

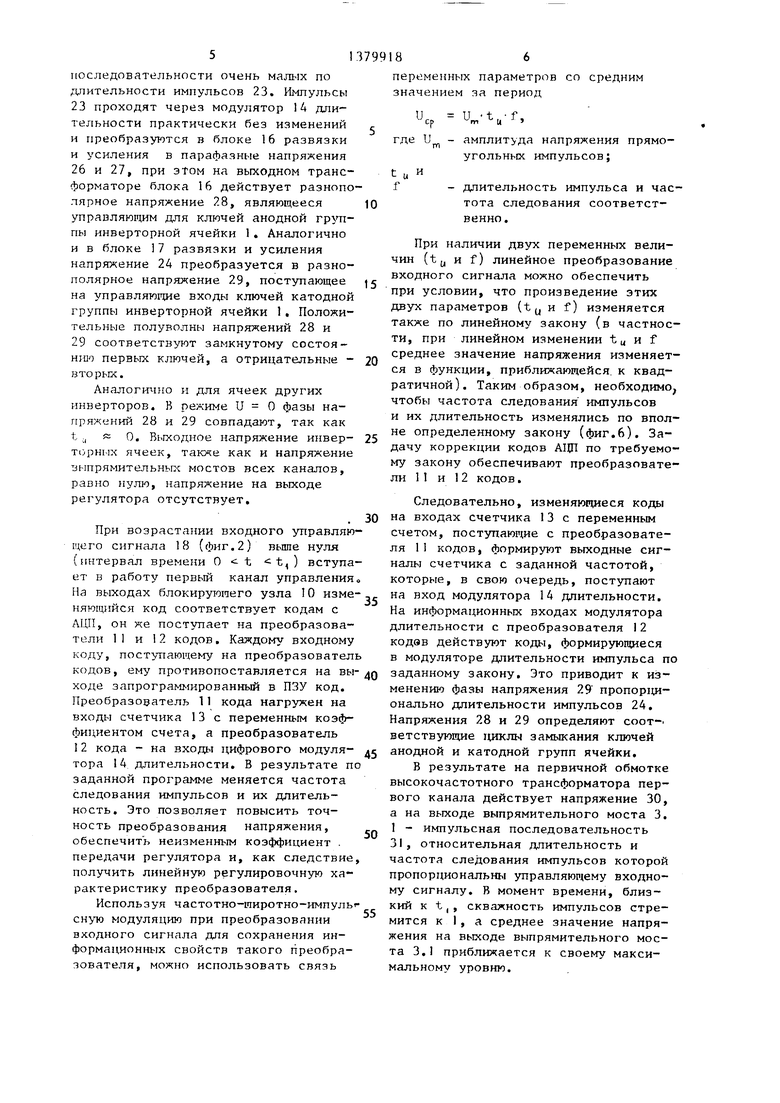

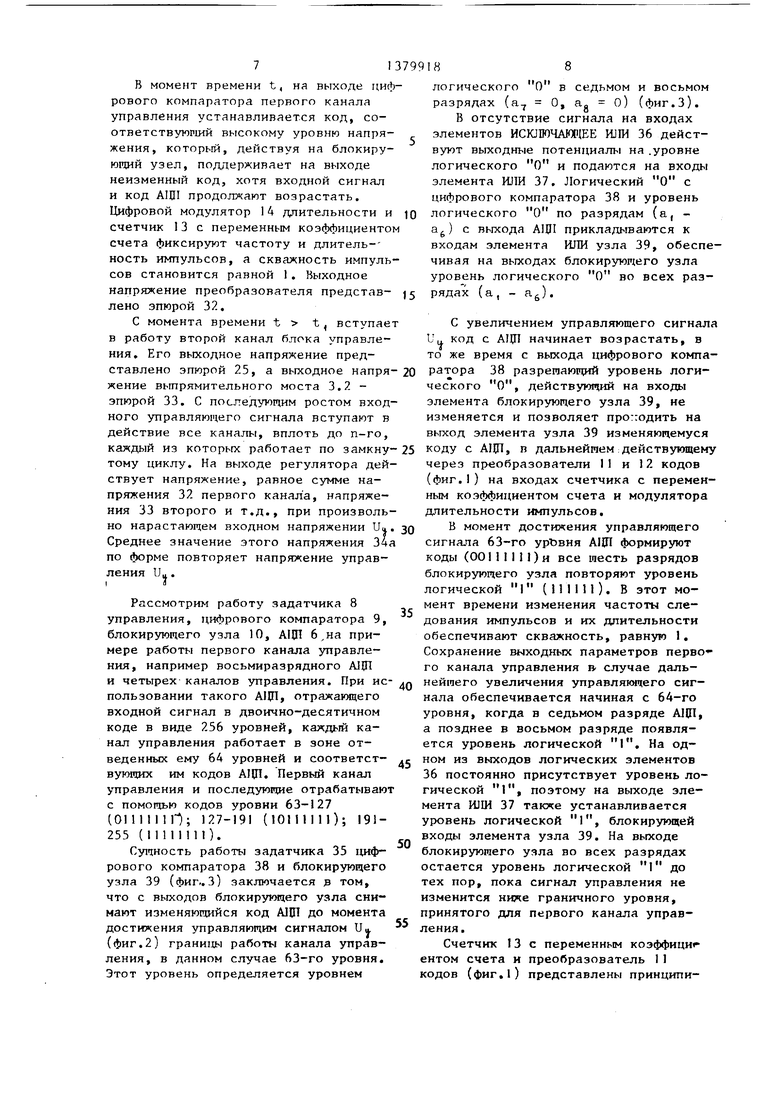

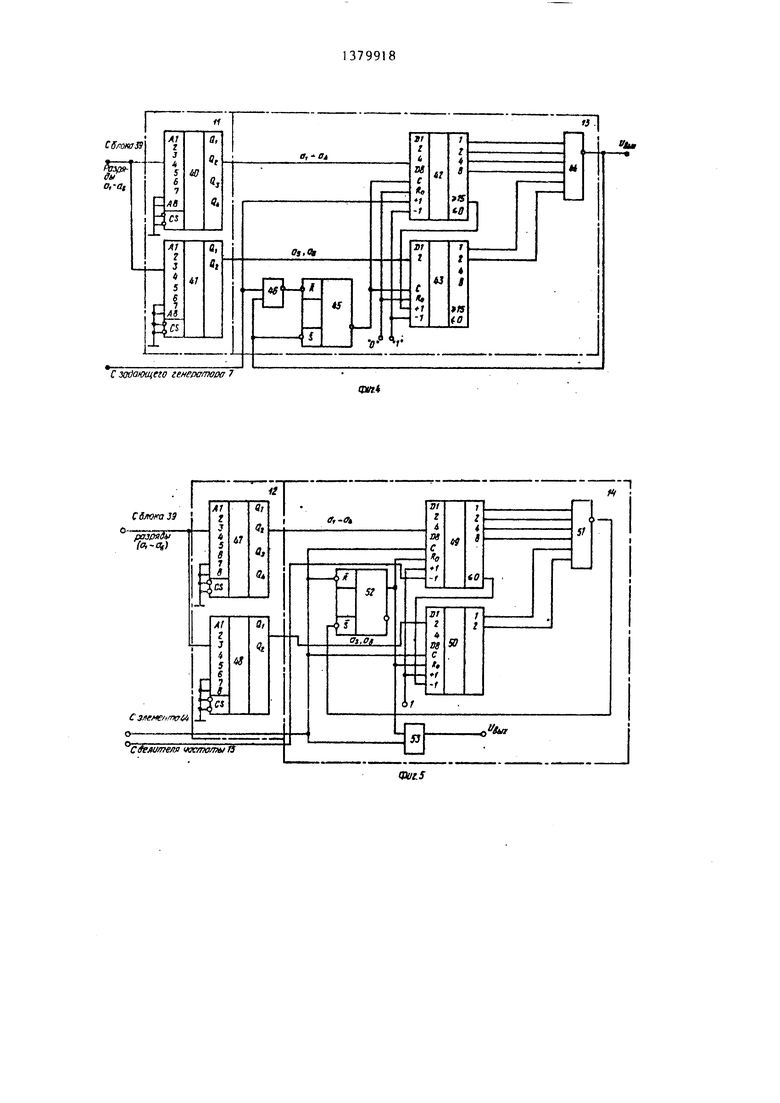

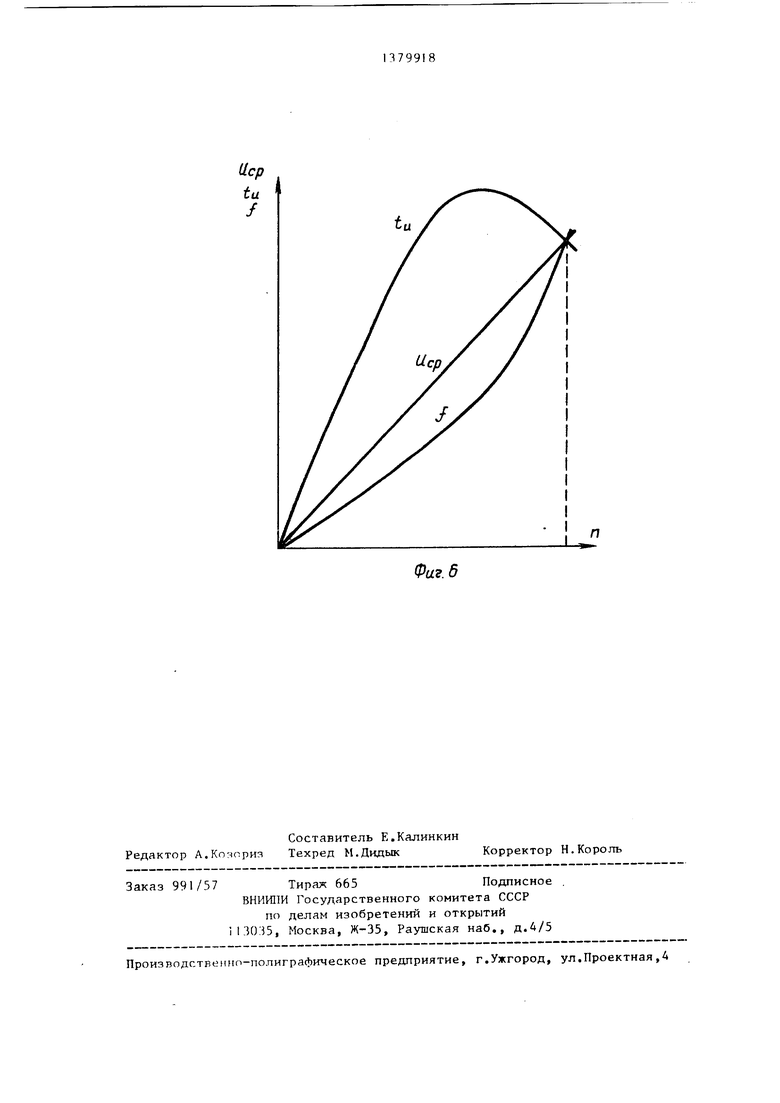

На фиг,1 приведена структурная схема устройства для управления регулятором напряжения; на фиг.2 - временные диагра п-а- работы узлов устройства для управления регулятором напряжения; на фиг.З - схемы задатчика управления, цифрового KONmapaTOpa и блокирующего узла; на фиг.4 - принципиальная схема преобразователя кодов и счетчика с переменным коэффициентом счета; на фиг.З - преобразова- тель кодов и модулятор длительности импульсов; на фиг.6 - график функциональной связи среднего напряжения за период с длительностью импульсов и частотой их следования на каждое из- менение состояния в шести разрядах аналого-цифрового преобразователя {АЦП), начиная с младглих.

Устройство для управления регулятором напряже 1ия {фиг.1) содержит п параллельно включенных инверторных ячеек на полностью управляемых ключах l-n, выходы которых соединены с первичными обмотками высокочастотных трансформаторов 2.1-2.П, вторичные обмотки которых подключены к п после- дoвaтeJП5Ho соединенным вштрямительным мостам 3..n, подключенным к нагрузке 4, п блоков 5,1-5.п управления, АЩ1 и задающий генератор 7, каж- дый блок управления содержит задат- чик 8 управления, соед шенный с входом цифрового ко таратора 9, вход которого соединен с одним из входов блокирующего узла 10, другой вход которого соединен с информационным входом цифрового компаратора и с выходом АЦП 6, а выход блокирующего узла соединен с объединенными входами преобразователей 11 и 12 кодов, причем иыход первого преобразователя 11 кода подключен к информационным входам счетчика I3 с переменным коэффициентом счета, а выход второго преобразователя 12 кода - к выходам управле- ния длительностью импульсов цифрового модулятора 14 длительности импульсов причем другой вход счетчика 13 с переменным коэффициентом счета подключен к выходу задающего генератора 7, вход управления частотой следования импульсов модулятора длительности соединен с выходом счетчика с переменным коэффициентом счета, тактирующий вход - с выходом делителя 15 частоты а выход цифрового модулятора длительности импульсов соединен с входами узлов 16 и 17 разделения и усиления, выходы которых предназначены для подключения к управляющим входам ключей I инверторных ячеек 1 - п.

Преобразователи кодов, служащие для преобразования поступающего двоично-десятичного кода в двоично-десятичный код по заданным программам, выполняются, как правило, на запоми- нающ-ix устройствах и элементах запоминающих устройств, например на микросхемах К573РР, К558РР и т.д.

Задатчик управления Может быть выполнен на простейгчих элементах логики И, ИЛИ, НЕ или на основе программных переключателей типа ПП-10.

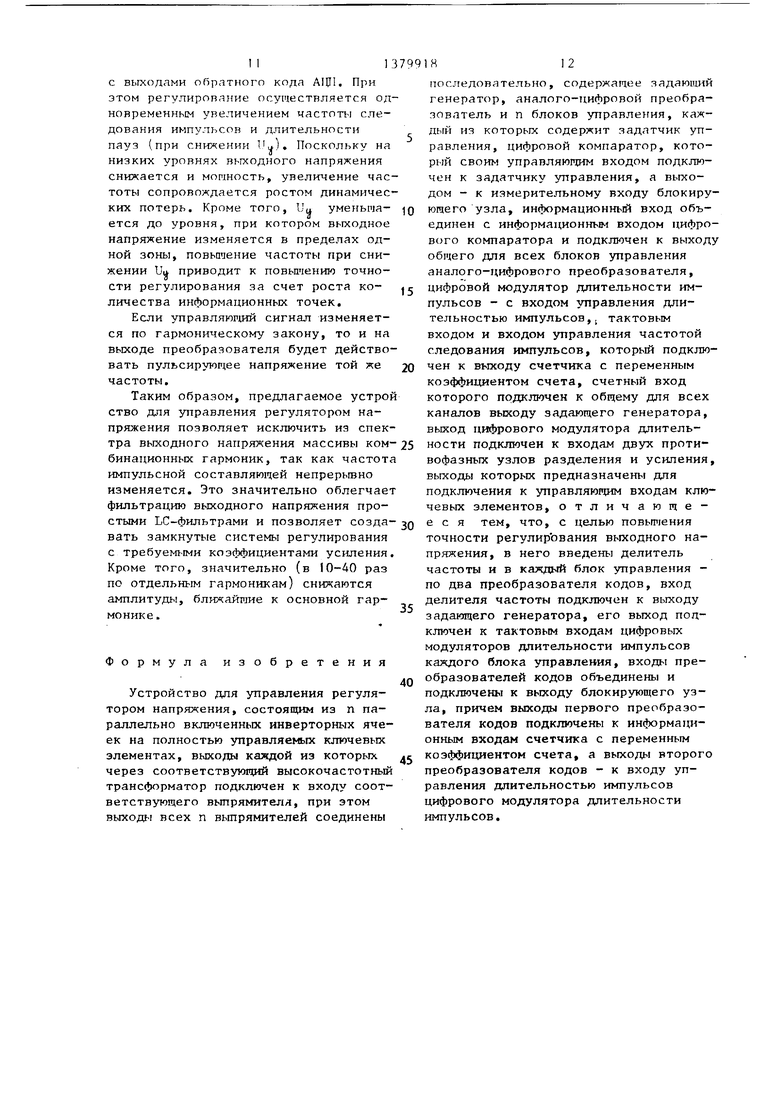

На фиг.2 приняты следующие обозначения: 18 - входной управляющий сигнал; 19-21 - пороговые напряжения, соответствующие заданным значениям задатчиков управления; 22 и 23 - диаграммы выходных напряжений соответственно со счетчиков с переменным коэффициентом счета первого и второго каналов управления; 24 и 25 -диаграммы напряжений с выхода цифровых модуляторов длительности первого и второго каналов управления соответственно; 26 и 27 - диаграммы напряжений неуправляемого блока развя-зки и усиления первого канала; 28 - диаграмма напряжений на обмотках выходных трансформаторов неуправляемых блоков развязки и усиления; 29 - диаграмма напряжений на обмотках трансформаторов управляемых блоков развязки и усиления; 30 - диаграмма напряжения на первичной обмотке высокочастотного трансформатора первого инвертора; 31 - диаграмма напряжения на выходе выпрямительного моста первого канала; 32 - 34 - диаграммы напряжений на нагрузке при работе соответственно первого, второго и третьего каналов преобразователя на примере линейно нарастающего входного сигнала 18; 34а - среднее значение мгновенного напряжения на нагрузке.

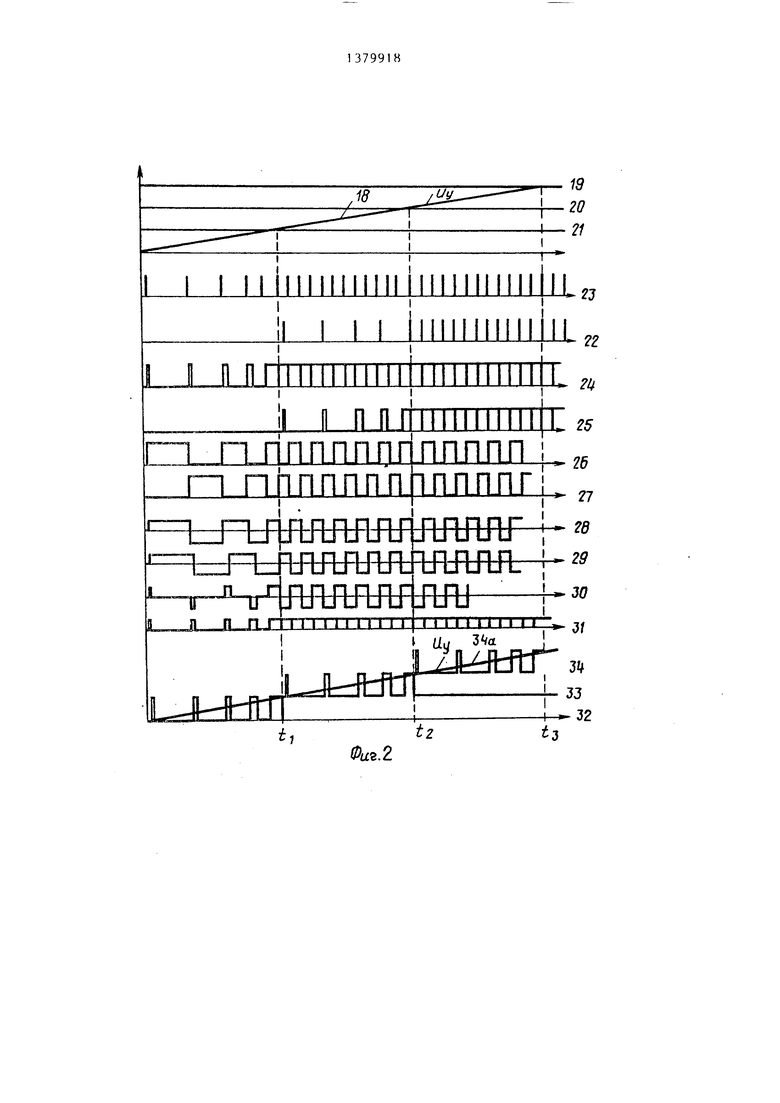

Задатчик 35 управления (фиг.З) представлен упрощенным вариантом

для первой зоны регулирования, когда выходы задатчика имитирутот уровень логического О. Два логических элемента ИСКЛЮЧА)1ЦЕЕ Ш1И 36, одни из входов которых соединены с выходом А1Ц1 6, а другие - с выходом задатчика, выходы подключены к входам логического элемента ИЛИ 37, представляют собой один из вариантов цифрового компаратора 38, выход которого соединен с одним из входов логических элементов ИЛИ, образующих блокирующий узел 39, другие входы которого соединены с соответствующими выходами А1Щ 6.

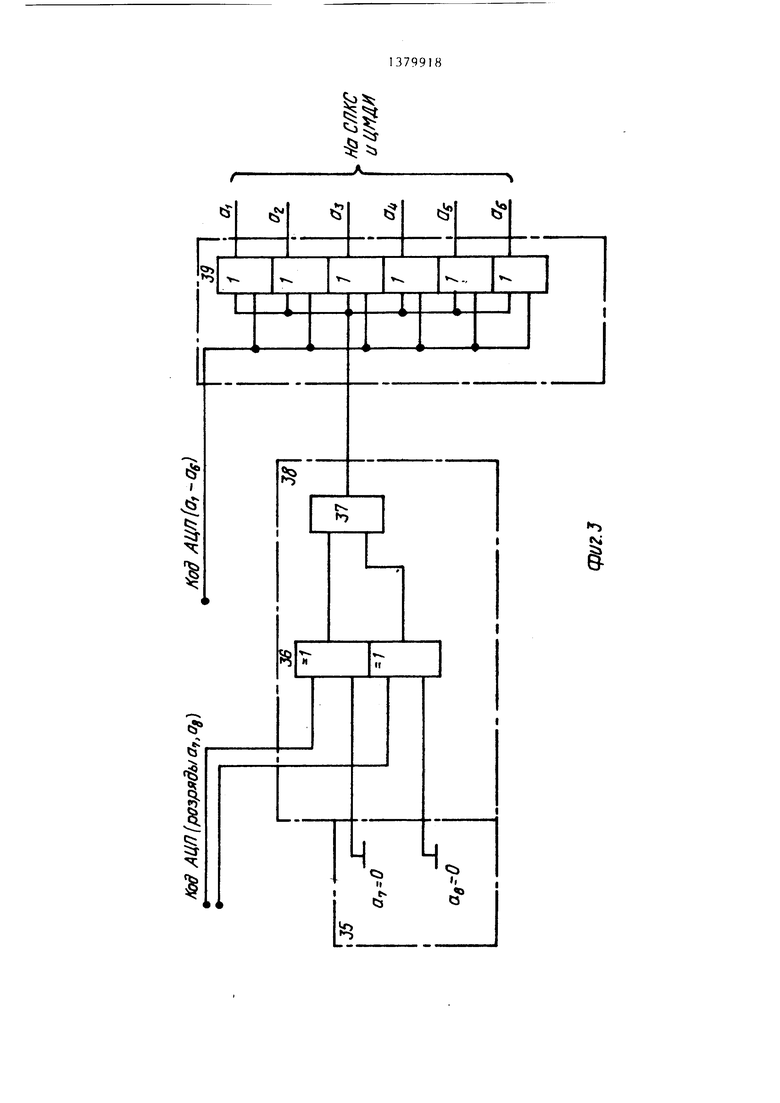

Преобразователь кодов (фиг.4), выполненный, например, на двух элементах 40 и 41 постоянно запоминающих устройств (), подключен шестью адресными входами к выходам блокирующего узла 39, выходы младиих шести разрядов ПЗУ соединены с информационными входами счетчиков 42 и 43, выходы которых в составе младших шести разрядов подключены к элементу И-НЕ 44, выход которого соединен с одним из входов триггера 45 и элемента И- НЕ 46, другой вход которого подсоединен к выходу задающего генератора 7, к которому подключен счетный вход счетчика 42, выход перевыполнения которого соединен со счетным входом счетчика 43, входы записи счетчиков 42-и 43 соединены с инверсным вько- дом триггера 45, на вычитаюпше входы счетчиков 42 и 43 и входы сброса поданы уровни напряжений логической 1 и логического О соответственно.

На фиг.5 представлен вариант пре- образователя кодов, выполненный на элементах ПЗУ 47 и 48, подключенный входными шестью адресными входами к вьшодам блокирующего узла 39, выходы преобразователя в составе шести млад- ших разрядов соединены с информационными входами счетчиков 49 и 50, выходы которых в составе тех же мести разрядов подключены к элементу ИЛИ- НЕ 51, выход которого связан с одним из входов триггера 52, другой вход которого подключен к выходу элемента 44, одному из входов ИСЮ)ЧАЮ1ЧЕЕ Ш1И 53, входам записи счетчиков 49 и 50, а выход триггера 52 подключен к входам сброса счетчиков 49 и 50 и одному из входов элемента ИСКЛЮЧАЛХЦЕЕ ИЛИ, другой вход которого связан с выходом элемента 44, делитель 8 частоты

(фиг.О подключен к вычитающему вход счетчика 49, выход сигнала переноса которого связан с вычитающим входом счетчика 50.

На фиг.6 показан в виде графиков один из примеров линейной связи среднего значения выходного напряжения ( ) регулятора напряжения и п-по- рядкового номера -изменения щестираз- рядного кода А1Щ при возрастании входного сигнала от нуля с соответствующим изменением длительности вы- ходн12рс импульсов и частоты их следования (ty ,f } ,

Работу устройства для управления регулятором напряжения (фиг.1) рассмотрим на примере, когда на информационный вход блоков управления поступает с А1Ц1 прямой код.

При включении питающего напряжени и отсутствии управляющего напряжения и,, (напряжение 18, фиг.2) задаюрщй генератор 7 формирует импульсы заданной частоты. На выходе А1Щ 6 действует п-разрядный двоичный код, соответствующий нулевому уровню и. Этот код поступает на информационные входы IJ фpoвoгo компаратора 9 и блокирующего узла 10. Задатчик 8 управления задает двоично-десятичным кодом верхнюю границу зоны, отведенной для каждого канала управления, причем границы зон (в кодах) определяются количеством зон и их разбиением. На выходе цифрового компаратора код, соответствующей низкому уровню напряжения, сохраняется до момента достижения входным сигналом границы зоны работы первого канала управления и далее остается на высоком уровне. Такой алгоритм работы позволяет пропускать на выход блокирующего узла т-разрядный изменяющийся код в соответствии с входным сигналом (в пределах зоны), поступающий от А1Щ. В случае выхода из границы зоны на выходе цифрового компаратора 9 и соответственно на выходе блокирующего узла 10 устанавливается неизменный код в виде высокого напряжения в используемых разрядах. При нулевом управляющем снгнале на выходе блокирующего узла 10 устанавливаются коды, проходящие без изменения через преобразователи II и 12 кодов,задающие начальную частоту работы счетчика I3 с переменньм коэффициентом счета и вызывакщие появление на его выходе

последовательности очень малых по длительности импульсов 23. Импульсы 23 проходят через модулятор 1А длительности практически без изменений и преобразуются в блоке 16 развязки и усиления в парафаяные напряжения 26 и 27, при этом на выходном трансформаторе блока 16 действует разнопо- лярное напряжение 28, являющееся управляющим для ключей анодной группы инверторной ячейки 1. Аналогично и в блоке 17 развязки и усиления напряжение 24 преобразуется в разно- полярное напряжение 29, поступающее на управляющие входы ключей катодной группы инверторной ячейки 1. Положительные полуволны напряжений 28 и 29 соответствуют замкнутому состоя- Him первых ключей, а отрицательные - вторых.

Аналогит-пю и для ячеек других инверторов. В режиме U О фазы напряжений 28 и 29 совпадают, так как t у я 0. Выходное напряжение инвер- ячеек, также как и напряжение зыпрямительньпх мостов всех каналов, равно нулю, напряжение на выходе регулятора отсутствует.

.

При возрастании входного управляющего сигнала 18 (фиг.2) выше нуля (интервал времени О t t, ) вступает в работу первый канал управления На выходах блокирующего узла 10 изме няющийся код соответствует кодам с АЦП, он же поступает на преобразователи 11 и 12 кодов. Каждому входному коду, поступающему на преобразовател кодов, ему противопоставляется на вы ходе запрограммированный в ПЗУ код. Преобразователь 11 кода нагружен на входы счетчика 13 с переменным коэффициентом счета, а преобразователь 12 кода - на вход1.1 цифрового модуля- тора 14 длительности. В результате п заданной программе меняется частота следования импульсов и их длительность. Это позволяет повысить точность преобразования напряжения, обеспечить неизменным коэффициент . передачи регулятора и, как следствие получить линейную регулировочную характеристику преобразователя.

Используя частотно-широтно-импуль модуляцию при преобразовании входного сигнала для сохранения информационных свойств такого преобразователя, можно использовать связь

переменных параметров со средним значением за период

ср .

ср

где и - амплитуда напряжения прямоугольных импульсов;

5

0

Q j

0

5

f - длительность импульса и частота следования соответственно.

При наличии двух переменных величин (t и f) линейное преобразование входного сигнала можно обеспечить при условии, что произведение этих двух параметров (t (j и f) изменяется также по линейному закону (в частности, при линейном изменении t и f среднее значение напряжения изменяется в функции, приближающейся, к квадратичной). Таким образом, необходимо, чтобы частота следования импульсов и их длительность изменялись по вполне определенноьгу закону (фиг.6). Задачу коррекции кодов А1Щ по требуемому закону обеспечивают преобразователи 11 и 12 кодов.

Следовательно, изменяющиеся коды на входах счетчика 13 с переменным счетом, поступающие с преобразователя II кодов, формируют выходные сигналы счетчика с заданной частотой, которые, в свою очередь, поступают на вход модулятора 14 длительности. На информационных входах модулятора длительности с преобразователя 12 кодвв действуют коды, формирующиеся в модуляторе длительности импульса по заданному закону. Это приводит к изменению фазы напряжения 29 nponopii i- онально длительности импульсов 24. Напряжения 28 и 29 определяют соот- ветствующие циклы замыкания ключей анодной и катодной групп ячейки.

В результате на первичной обмотке высокочастотного трансформатора первого канала действует напряжение 30, а на выходе выпрямительного моста 3. 1 - импульсная последовательность 31, относительная длительность и частота следования импульсов которой пропорциональны управляющему входному сигналу. В момент времени, близкий к t,, скважность импульсов стремится к 1, а среднее значение напряжения на выходе выпрямительного моста 3.1 приближается к своему максимальному уровню.

713

В момент времени t, на выходе цифрового компаратора первого канала управления устанавливается код, со- ответствуюиий высокому уровню напряжения, который, действуя на блокирующий узел, поддерживает на выходе неизменный код, хотя входной сигнал и код А1Ц1 продол5кают возрастать. Цифровой модулятор 14 /цтительности и

счетчик 13 с переменным коэффициентом счета фиксируют частоту и длитель- ность и тульсов, а скважность импульсов становится равной 1. Выходное напряжение преобразователя представлено эпюрой 32.

С момента времени t t, вступает в работу второй канал блока управления. Его выходное напряжение представлено эпюрой 25, а выходное напряжение выпрямительного моста 3.2 - эпюрой 33. С последующим ростом входного управляющего сигнала вступают в действие все каналы, вплоть до п-го.

логического О в седьмом и восьмом разрядах (а. О, Яд О) (фиг.З). В отсутствие сигнала на входах элементов ИСЮПОЧАКХЦЕЕ ИЛИ 36 действуют выходные потенциалы на .уровне логического О и подаются на входы элемента ИЛИ 37. Логический О с цифрового компаратора 38 и уровень логического О по разрядам (а, а) с выхода АЩ прикладываются к входам элемента ИЛИ узла 39, обеспечивая на выходах блокирующего узла уровень логического О во всех разJ5 рядах (а, - а).

С увеличением управляющего сигнала и,, код с А1Щ начинает возрастать, в то же время с выхода цифрового компаратора 38 разрегаающий уровень логического О, действующий на входа элемента блокирующего узла 39, не изменяется и позволяет протгодить на выход элемента узла 39 изменяющемуся

| название | год | авторы | номер документа |

|---|---|---|---|

| МОДУЛЯЦИОННЫЙ РАДИОМЕТР | 2001 |

|

RU2187824C1 |

| МОДУЛЯЦИОННЫЙ РАДИОМЕТР | 2002 |

|

RU2220426C1 |

| СПОСОБ ИЗМЕРЕНИЯ СКОРОСТИ ВРАЩЕНИЯ ВАЛА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2017156C1 |

| Устройство для управления регулятором напряжения | 1982 |

|

SU1043809A1 |

| Устройство для управления трехфазным мостовым инвертором | 1984 |

|

SU1297194A1 |

| Устройство для управления преобразователем частоты с непосредственной связью и широтно-импульсным регулированием | 1989 |

|

SU1624629A1 |

| Синтезатор частот | 1984 |

|

SU1293841A1 |

| Устройство для определения временного положения сигнала | 1985 |

|

SU1307442A1 |

| Устройство для кодирования звуковых сигналов с инерционным компандированием | 1985 |

|

SU1356233A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ИНФОРМАЦИИ ПО ДВУХПРОВОДНОЙ ЛИНИИ СВЯЗИ | 1991 |

|

RU2023310C1 |

Изобретение относится к электротехнике и может быть использовано три управлении регуляторами напряжения. Цель изобретения - повыиение точности регулирования выходного напряжения. Устройство содержит п блоков 5.1 - 5.П управления, к кото- РЬ1М подключены аналого-цифровой преобразователь 6 и задающий генера- тор 7. Блоки управления включают задатчик 8 управления, компаратор 9, блокирукичий узел 10, цифровой модулятор 14 длительности импульсов. За счет введения в блоки 5.1-5.П управления преобразователей кодов М и I2 и использования делителя 15 частоты из спектра выходного напряжения исключены массивы комбинационных гармоник, так как частота импульсной составляющей непрерывно изменяется. 6 ил. (Л

тому циклу. На выходе регулятора действует напряжение, равное сумме напряжения 32 первого канала, напряжения 33 второго и т.д., при произвольно нарастающем входном напряжении Uu. 30 Среднее значение этого напряжения Зца по форме повторяет напряжение управления и

Г

35

40

каждый из которых работает по замкну-25 коду с А1Щ, п дальнейгаем;действующему

через преобразователи 11 и 12 кодов (фиг.1) на входах счетчика с переменным коэффициентом счета и модулятора длительности импульсов.

В момент достижения управляющего сигнала 63-го урЪвня А1Щ формируют коды (00111I11)и все шесть разрядов блокирующего узла повторяют уровень логической 1 (П11П). В этот момент времени изменения частоты следования импульсов и их длительности обеспечивают скважность, равную 1. Сохранение выходных параметров перво го канала управления в- случае дальнейшего увеличения управляющего сигнала обеспечивается начиная с 64-го уровня, когда в седьмом разряде АЦП, а позднее в восьмом разряде появляется уровень логической I. На одном из вьгходов логических элементов 36 постоянно присутствует уровень логической 1, поэтому на выходе элемента ИЛИ 37 также устанавливается уровень логической 1, блокирующей входы элемента узла 39. На выходе блокирующего узла во всех разрядах остается уровень логической I до тех пор, пока сигнал управления не изменится ниже граничного уровня, принятого для первого канала управления.

Счетчик 13 с переменным коэффици - ентом счета и преобразователь 11 кодов (фиг.О представлены принципиРассмотрим работу задатчика 8 управления, цифрового компаратора 9, блокирующего узла 10, А1Щ 6,на примере работы первого канала управления, например восьмиразрядного А1Щ и четырех каналов управления. При использовании такого АЦП, отражающего входной сигнал в дво1 чно-десятичном коде в виде 256 уровней, каждый канал управления работает в зоне отведенных ему 64 уровней и соответствующих им кодов АЦП. Первый канал управления и последующие отрабатывают с помощью кодов уровни 63-127 (01 11 1 I 1П; 127-191 (10111 1 11); 191- 255 (11111111).

Сущность работы задатчика 35 1шф- рового компаратора 38 и блокирующего узла 39 (фиг..З) заключается д том, что с вьгходов блокирующего узла снимают изменяющийся код АЦП до момента достижения управляющим сигналом Ua (фиг.2) границы работы канала управления, в данном случае 63-го уровня. Этот уровень определяется уровнем

45

50

55

35

40

45

50

55

913799

альной схемой (фиг.4) и работают сле- ДУЮ11ШМ образом.

Предположим, что на информационных входах счетчиков 42 и 43 логический , О. Логическая 1 с элемента 44 обуславливает логическую 1 на выходе Q триггера 45 и, сл едовательно, на входе С счетчиков 42 и A3, При

поступлении на счетный вход счетчика

42импульсов с выхода задающего генератора на выходах счетчиков 42 и

43появляется пестиразрядный нарастающий двоичный код. При поступлении 63-го импульса на вход счетчика на выходах его шести разрядов устанавливается уровень логической 1, а на выходе элемента 44 и соответственно

па входе S триггера 45 - перепад с

11,11 Ип

1 в О. В то же время на входе R триггера 45 устанавливается логическая 1. Триггер 45 опрокидывается и па его выходе О устанавливается нулевой уровень. Он ке прикладывается к входам С счетчиков 42 и 43. Счетчи производит запись сигналов, действу- югдах на информационных входах (с выходов ПЗУ на элементах 40 и 41). На вход + счетчика действует 64-й импульс с задающего генератора, а ло гичес кая 1 - с элемента 44 - на лход Я триггера 45, Одновременное воздействие логической 1 на входах элемента 46 приводит к появлению логического 0(но время действия 64-го импульса) на входе R триггера 45. Триггер опрокидывается с логического О в 1 и свое состояние не изменит до последук1Г1его изменения потенциала по входу S, которое про

изойдет вновь в случав установления на выходе, счетчиков логической

Г

в пести разрядах. Таким образом, счетчик с переменным коэффициентом счета выделяет из последовательности импульсов задающего генератора только те, которые приводят к переполнению шести разрядов счетчиков 42 и 43, а начало счета определяется от установочного двоично-десятичного кода с элементов 40 и 41 преобразователя кодов. Элементы 40 и 41 вьшолняют функцию преобразования кодов, посту- паюпщх с АЦП для обеспечения определенной функции преобразования Ug

f(f).

Цифровой модулятор 14 длительности импульсов и преобразователь 12 кодов (по фиг.1) представлены в виде прин8I О

ципиал1,ной схемы (фих .З) и таботают след тощим образом.

Преобразователь кодов, выполненный на элементах 47 и 48, противопоставляет входным кодам с ЛИЛ коды по определенной программе, которые действуют на информационные входы счетчиков 49 и 50.

После прихода со счетчика с переменным коэффипиентом счета импульса в виде перепада напряжения с логичес

кой

0

5 д

5

0

5

0

5

в логический

О триггер 52 устанавливается в нулевое состояние (Р, о, S 1), тем самым снимается сигнал сброса счетчиков 49 и 50 и производится запись данных по информационным входам счетчиков.

Импульсами с делителя частоты, действую1 Ц1ми на вычитаю1чий вход счетчика 49, изменяются выходные коды счетчиков 49 и 50 в сторону их уменьшения от записанного. Последующий сигнал после обнуления шести разрядов счетчигса приводит к появлению во всех разрядах логической 1 и на выходе элемента 51 действует уровень логического О, а на входе И элемента 52 - логическая 1. Происходит опрокидывание триггера 52 и на его выходе появляется логическая 1, являющаяся сбросовым сигналом счетчиков. Состояние триггера 52 изменится в момент появления сигнала с элемента 44. Выходной сигнал формируется элементом 53. С момента рассмотрения на обоих входах элемента ИСКЛЮЧАЮ1ЧЕЕ Ш1И 53 изменение уровней напряжений с логической 1 в О не изменит нулевого состояния на выходе элемента 53. В момент окончания импульса со счетчика с переменным коэффшщентом счета (выход элемента 44) действует уровень логической 1, а с выхода триггера 52 - логический О. На выходе элемента 53 формируется сигнал (перепад с О в 1), продолжающийся до момента опрокидывания триггера 52. Длительность выходного импульса определяется количеством импульсов с делителя частоты, действующих на вычитающих входах счетчиков 49 и 50 практически до момента их обнуления.

Для снижения динамических потерь в ключах инверторных ячеек Необходимо информационные входы цифрового компаратора и блокирующего узла каждого канала блока управления соединить

n13

с выходами обратного кода А1Ц1, При этом регулиропание осуществляется одновременным увеличением частоты следования импульсов и длительности пауз (при снижении i). Поскольку на низких уровнях выходного напряжения снижается и моиность, увеличение частоты сопровождается ростом динамических потерь. Кроме того, 1 уменыча- ется до уровня, при котором выходное напряжение изменяется в пределах одной зоны, повьпиение частоты при снижении Uu приводит к повьачению точности регулирования за счет роста ко- личества информационных точек.

Если управляюгщй сигнал изменяется по гармоническому закону, то и на выходе преобразователя будет действовать пульсирующее напряжение той же частоты.

Таким образом, предлагаемое устрой ство для управления регулятором напряжения позволяет исключить из спектра выходного напряжения массивы ком- бинадионных гармоник, так как частота импульсной составляющей непрерьшно изменяется. Это значительно облегчает фильтрацию выходного напряжения простыми LC-фильтрами и позволяет созда- вать замкнутые системы регулирования с требуемыми коэффициентами усиления. Кроме того, значительно (в 10-40 раз по отдельным гармоникам) снижаются амплитуды, ближайиие к основной гармонике .

Формула изобретения

Устройство для управления регулятором напряжения, состоящим из n параллельно включенных инверторных ячеек на полностью управляемых ключевых элементах, выходы каждой из которых через соответствующий высокочастотный трансформатор подключен к входу соответствующего выпрямителя, при этом выходы всех n выпрямителей соединены

8

12

JQ

0

5 Q

5

0

последовательно, содержащее задающий генератор, аналого-цифровой преобразователь и n блоков управления, каждый из которых содержит задатчик управления, цифровой компаратор, который своим управляюпщм входом подключен к задатчику управления, а выходом - к измерительному входу блокирующего узла, информационный вход объединен с информационньм входом цифрового компаратора и подключен к выходу общего для всех блоков управления аналого-цифрового преобразователя, цифровой модулятор длительности импульсов - с входом зтравления длительностью импульсов,( тактовым входом и входом управления частотой следования импульсов, который подключен к выходу счетчика с переменным коэффициентом счета, счетный вход которого прдключен к общему для всех каналов выходу задающего генератора, выход цифрового модулятора длительности подключен к входам двух противофазных узлов разделения и усиления, выходы которых предназначены для подключения к управляющим входам ключевых элементов, отличающееся тем, что, с целью повыиения точности регулир ования выходного напряжения, в него введены делитель частоты и в каждый блок управления - по два преобразователя кодов, вход делителя частоты подключен к выходу задающего генератора, его выход подключен к тактовым входам цифровых модуляторов длительности импульсов каждого блока управления, входы преобразователей кодов объединены и подключены к выходу блокирующего узла, причем выходы первого преобразователя кодов подключены к информационным входам счетчика с переменным коэффициентом счета, а выходы второго преобразователя кодов - к входу управления длительностью импульсов цифрового модулятора длительности импульсов.

I I II Illllllllllllllllllllllllll

ll I I I IIIIIHIIUIIII

Я 0 OlllllillllllllirTll

ll fl П ПII Hill III III

плпплп

ПАППП

ffcruinjuwinnr -L njTjmnjijtftfbimFb

Т

JL

IT

дшишгяги

П П I I i ll i 1 I I I II I t i 11 I 11

19

го

21

J

г

т

25

лпплл

шиитг

innr tfbimFb

29

30

Фиъ.2

Г зодающпо генератооо 7

С делителя «яятаг/и/ /У

Фиг. 6

| Устройство управления регулятором переменного напряжения со звеном повышенной частоты | 1976 |

|

SU624347A1 |

| С, 05 F 1/22, 1978 | |||

| Устройство для управления регулятором напряжения | 1983 |

|

SU1239800A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1988-03-07—Публикация

1986-06-16—Подача