Изобретение относится к преобразовательной технике и может быть использовано для управления преобразователями постоянного и переменного тока, к которым предъявляются повышенные требования по качеству выходной энергии.

Известен способ управления многоячейковым преобразователем, заключающийся в том, что выделяют сигнал текущей ошибки выходного параметра от заданного значения и формируют с его помощью сигналы переключения преобразовательными ячейками, в котором используется модулятор ширины импульсов, многоуровневый компаратор с обратными связями и сумматор [1].

Известный способ отличается большой сложностью и необходимостью тщательной настройки.

Наиболее близким по технической сущности и достигаемым результатам является способ управления многоячейковым преобразователем, выполненным в виде N преобразовательных ячеек, выходы которых соединены последовательно, заключающийся в том, что сравнивают заданное и фактическое значения выходного параметра преобразователя, формируют сигнал текущей ошибки, формируют управляющий сигнал, преобразуют его в N-разрядный двоичный цифровой код путем квантования по N уровням и включают в работу ячейки преобразователя, соответствующие разрядам этого кода, в соответствии с их текущими значениями, в котором в качестве управляющего сигнала используют сигнал ошибки, а преобразовательные ячейки включают или отключают с некоторой временной дискретностью, "отслеживая" сигнал задания с определенной точностью [2].

Указанный известный способ более прост в реализации, однако имеет низкие регулировочные свойства, обусловленные нечувствительностью к малым отклонениям выходного параметра от заданного значения.

Техническим результатом изобретения является улучшение регулировочных свойств преобразователя.

Этот результат достигается тем, что в известном способе управления многоячейковым преобразователем, выполненным в виде N преобразовательных ячеек, выходы которых соединены последовательно, заключающемся в том, что сравнивают заданное и фактическое значения выходного параметра преобразователя, формируют сигнал текущей ошибки, формируют управляющий сигнал, преобразуют его в N-разрядный двоичный цифровой код путем квантования по N уровням и включают в работу ячейки преобразователя, соответствующие разрядам этого кода, в соответствии с их текущими значениями, управляющий сигнал формируют путем суммирования сигналов, полученных при одновременном интегрировании по времени сигнала текущей ошибки с различными первой и второй постоянными времени с последующим их ограничением по модулю, соответственно, различными первым и вторым уровнями. При этом первую постоянную времени интегрирования выбирают меньше второй, первый уровень ограничения выбирают равным величине минимального уровня квантования, а второй уровень ограничения выбирают равным (N-1) величины первого уровня ограничения.

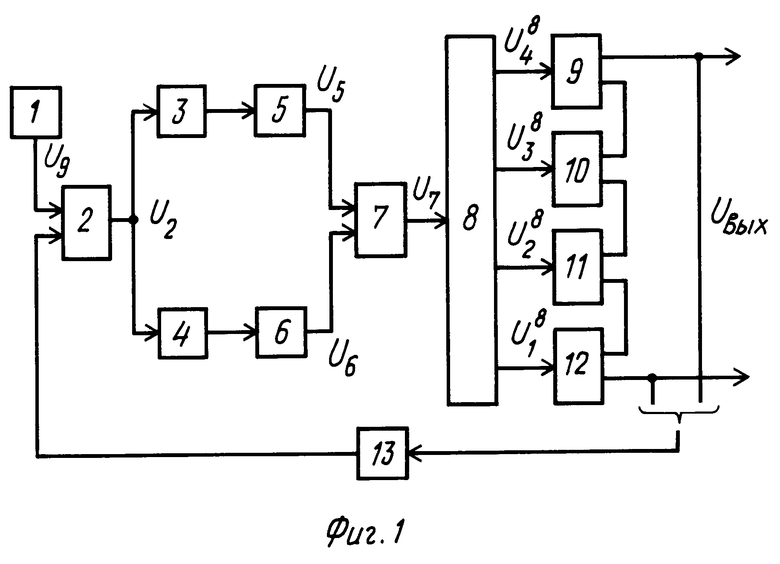

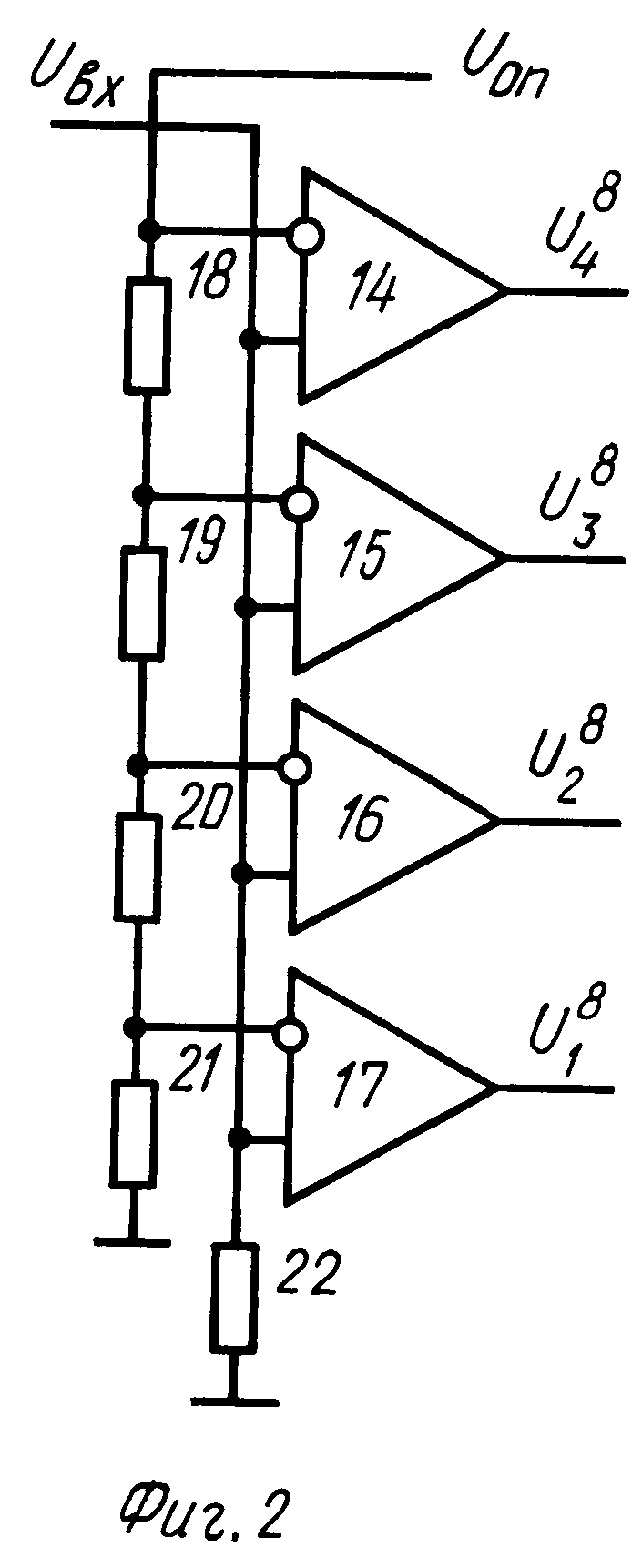

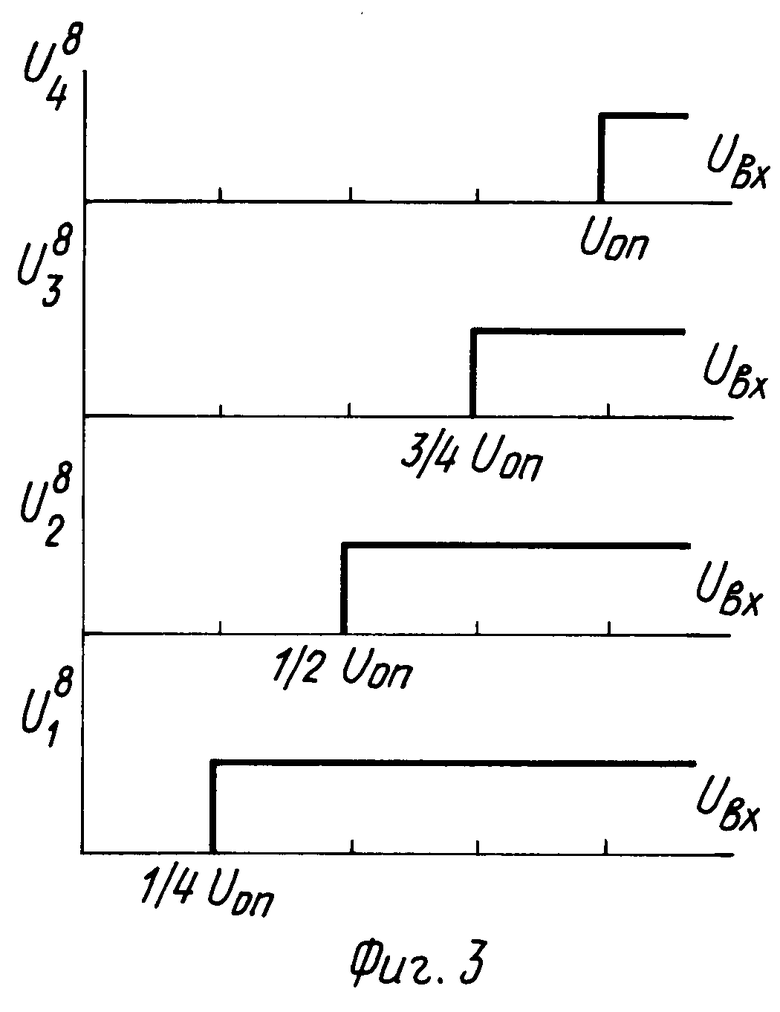

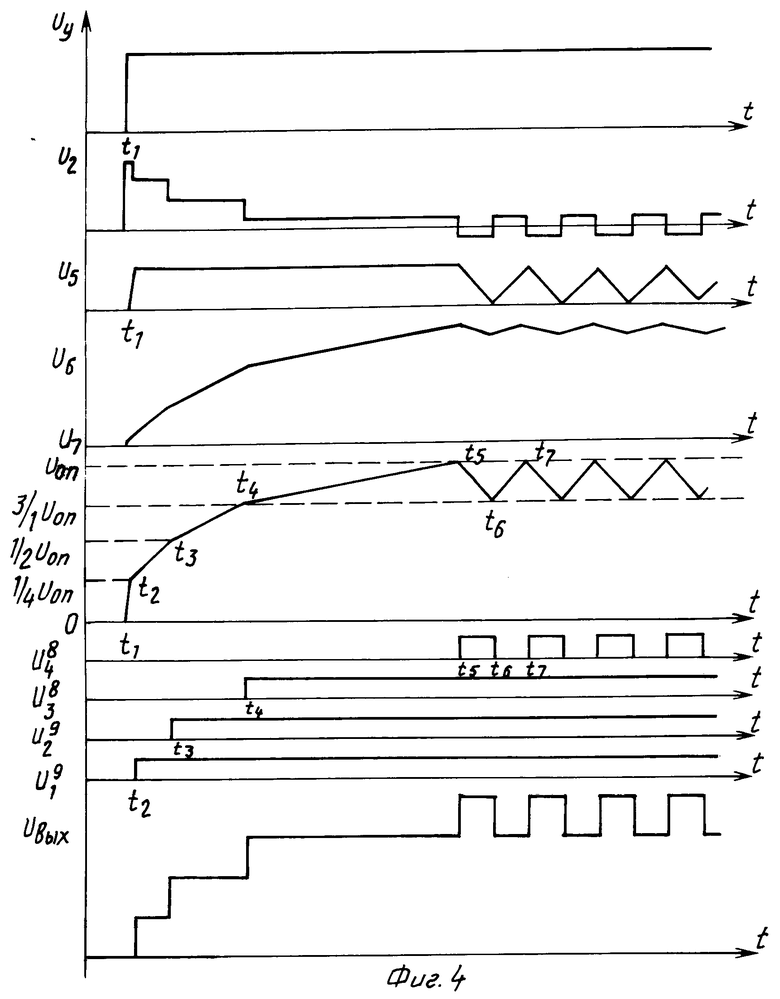

На фиг.1 представлена функциональная схема четырехячейкового преобразователя, реализующего предлагаемый способ; на фиг.2 - один из вариантов реализации аналого-цифрового преобразователя, реализующего квантование управляющего сигнала по N уровням; на фиг.3 - диаграммы, иллюстрирующие работу аналого-цифрового преобразователя; на фиг.4 - временные диаграммы, поясняющие сущность предложенного способа.

Преобразователь (фиг. 1), реализующий предложенный способ, состоит из узла задания 1, устройства выделения ошибки 2, интеграторов 3,4, ограничителей 5,6, сумматора 7, аналого-цифрового преобразователя 8, преобразовательных ячеек 9-12 и датчика выходного параметра 13. Выполнен преобразователь следующим образом. Выходы преобразовательных ячеек 9-12 соединены последовательно и являются выходом преобразователя. Управление преобразовательными ячейками производится сигналами с выхода аналого-цифрового преобразователя 8, осуществляющего постоянное преобразование входного сигнала U7, поступающего с выхода сумматора 7, который суммирует сигналы, поступающие с выходов интеграторов 3 и 4 через ограничители 5 и 6 соответственно. Входы интеграторов 3 и 4 соединены и подключены к выходу устройства 2 выделения ошибки выходного параметра, которое сравнивает сигнал управления Uy с сигналом обратной связи, пропорциональным выходному параметру, в данном случае напряжению, поступающим с выхода датчика 13 выходного параметра.

Один из вариантов выполнения аналого-цифрового преобразователя приведен на фиг. 2. Аналого-цифровой преобразователь состоит из компараторов 14-17, осуществляющих сравнение входного сигнала Uвх с напряжениями равными уровню опорного напряжения Uоп и его равноотстоящих частей. Формирование сетки напряжений сравнения осуществляется делителем напряжения на резисторах 18-21 равного значения. Входное напряжение Uвх подается на нагрузочный резистор 22. На фиг.3 приведена диаграмма работы аналого-цифрового преобразователя, откуда видно, что при превышении входным напряжением Uвх опорных уровней на выходе аналого-цифрового преобразователя формируется заполняющий код U18 - U48, то есть осуществляется квантование по N уровням. В данном случае N равно четырем. Число возможных кодовых комбинаций на выходе аналого-цифрового преобразователя равно пяти: от состояния 0000, соответствующего выключенному состоянию всех преобразовательных ячеек, далее следуют комбинации 0001, 0011, 0111, 1111, соответствующих включенному состоянию одной, двух, трех и четырех ячеек соответственно.

Рассмотрим реализацию способа на примере описанного выше четырехячейкового преобразователя, работающего в режиме регулятора напряжения. Способ осуществляется следующим образом.

При подаче с выхода узла задания 1 сигнала управления Uy, производится его сравнение с сигналом, пропорциональным выходному напряжению преобразователя. В результате сравнения формируется сигнал ошибки U2, величина которого пропорциональна мгновенному текущему значению ошибки. Полученный сигнал ошибки непрерывно интегрируется с двумя различными постоянными времени соответственно интеграторами 3 и 4 и при превышении определенного уровня ограничивается по величине ограничителями 5 и 6. Суммируя с помощью сумматора 7 выработанные сигналы, соответствующие интегралам сигналов ошибки, получают управляющий сигнал U7, который непрерывно подвергают аналого-цифровому преобразованию с помощью аналого-цифрового преобразователя 8, имеющего пять возможных состояний, а получаемый на выходе аналого-цифрового преобразователя цифровой код используют для управления включением и отключением преобразовательных ячеек 9-12, входящих в состав преобразователя. При этом одну из постоянных времени интегрирования выбирают относительно меньшей, исходя из допустимой частоты включения и отключения преобразовательных ячеек, а другую постоянную времени интегрирования - относительно большей, исходя из желаемого времени пуска преобразователя. Уровни же ограничения при этом устанавливают следующие: для интегратора с меньшей постоянной времени интегрирования - уровень равный минимальному уровню квантования аналого-цифрового преобразователя, а для интегратора с большей постоянной времени интегрирования - уровень, соответствующий N-1 первым уровням, в данном случае трем.

На фиг. 4 приведена диаграмма работы преобразователя в режиме пуска с нулевого выходного напряжения на уровень выходного напряжения, равный примерно 85-90% максимально возможного выходного напряжения преобразователя. В первоначальный момент времени сигнал управления Uy равен нулю, напряжение на выходах интеграторов 3 и 4 равно нулю, преобразовательные ячейки 9-12 выключены, выходное напряжение преобразователя равно нулю. В момент времени t1 вырабатывается ступенчатый сигнал управления Uy. При этом ступенчато увеличивается сигнал ошибки U2. Этот сигнал начинает интегрироваться интеграторами 3 и 4. Так как интегратор 3 имеет существенно меньшую постоянную времени интегрирования, его выходное напряжение быстро возрастает до уровня ограничения. Напряжение же на выходе интегратора 4 возрастает медленнее, чем на выходе интегратора 3. Когда сумма напряжений обоих интеграторов достигнет первого уровня квантования аналого-цифрового преобразователя 8 (момент t2) вырабатывается сигнал U18 и включается преобразовательная ячейка 12. Выходное напряжение преобразователя ступенчато увеличивается. При этом ступенчато уменьшается сигнал ошибки U2. Это приводит к уменьшению скорости нарастания напряжения на выходе интегратора 4, однако характер процесса остается монотонным. В момент времени t3 сумма напряжений интеграторов достигает второго уровня квантования аналого-цифрового преобразователя, появляется сигнал U28 и включается преобразовательная ячейка 11. Выходное напряжение преобразователя опять ступенчато увеличивается, а сигнал ошибки уменьшается. Последующие процессы происходят аналогично до момента времени t5, когда вследствие очередного увеличения выходного напряжения преобразователя величина ошибки меняет знак. При этом интегратор 3 выходит из режима ограничения и выходное напряжение интеграторов 3, 4 начинает уменьшаться, причем скорость уменьшения напряжения на выходе интегратора 3 выше, чем на выходе интегратора 4 вследствие меньшей постоянной времени интегрирования. Суммарное напряжение интеграторов также уменьшается, достигает уровня квантования аналого-цифрового преобразователя, выходное напряжение преобразователя уменьшается, величина ошибки снова меняет знак, напряжение интеграторов снова начинает увеличиваться и преобразователь входит в квазиустановившийся режим интегрального слежения за выходным напряжением с достаточно большой частотой переключения одной из ячеек, обусловленной в основном постоянной времени интегратора 3.

Таким образом при реализации описанного способа обеспечивается заданное быстродействие в пусковых режимах преобразователя и высокое быстродействие при стабилизации выходного напряжения преобразователя в "малом", что улучшает регулировочные свойства преобразователя в целом.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ СЛЕДЯЩЕГО ДИСКРЕТНОГО РЕГУЛИРОВАНИЯ НАПРЯЖЕНИЯ | 1991 |

|

RU2025763C1 |

| Способ регулирования выходного напряжения преобразователя постоянного напряжения | 1989 |

|

SU1737666A1 |

| СПОСОБ УПРАВЛЕНИЯ СЛЕДЯЩИМ АВТОНОМНЫМ ИНВЕРТОРОМ | 1991 |

|

RU2024175C1 |

| СПОСОБ УПРАВЛЕНИЯ СЛЕДЯЩИМ ИМПУЛЬСНЫМ ПРЕОБРАЗОВАТЕЛЕМ | 1991 |

|

RU2046528C1 |

| Способ управления преобразователем постоянного напряжения в переменное многоступенчатое | 1989 |

|

SU1688362A1 |

| СПОСОБ УПРАВЛЕНИЯ АВТОНОМНЫМ ИНВЕРТОРОМ С ШИРОТНО-ИМПУЛЬСНОЙ МОДУЛЯЦИЕЙ | 1991 |

|

RU2025879C1 |

| Аналого-цифровой интегратор | 1982 |

|

SU1037280A1 |

| СПОСОБ УПРАВЛЕНИЯ ИМПУЛЬСНЫМ СТАБИЛИЗАТОРОМ НАПРЯЖЕНИЯ | 2012 |

|

RU2509337C1 |

| МОДУЛИРОВАННЫЙ ПОДМЕШИВАЕМЫЙ ПСЕВДОСЛУЧАЙНЫЙ СИГНАЛ | 1994 |

|

RU2107389C1 |

| ЦИФРОВОЙ ИНТЕГРАТОР | 2018 |

|

RU2670389C1 |

Изобретение позволяет повысить регулировочные свойства многоячейковых преобразователей путем непрерывного интегрирования текущего сигнала ошибки выходного параметра преобразователя от заданного значения с двумя постоянными времени интегрирования, ограничения полученных сигналов, их суммирования и преобразования полученного таким образом сигнала регулирования в N-разрядный двоичный цифровой код путем квантования по N уровням, и управления с помощью сформированного кода работой преобразовательных ячеек, причем одна из постоянных времен интегрирования выбирается меньше второй. Первый уровень ограничения сигналов интегрирования устанавливается равным величине минимального уровня квантования, а второй - (N-1) величины первого уровня ограничения. 1 з.п. ф-лы, 4 ил.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Стабилизированный инвертор со ступенчатым выходным напряжением | 1978 |

|

SU790083A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1995-01-09—Публикация

1991-08-13—Подача