Изобретение относится к цифровой электроизмерительной технике и может быть использовано в информационно-измерительных системах.

Целью изобретения является повышение точности.

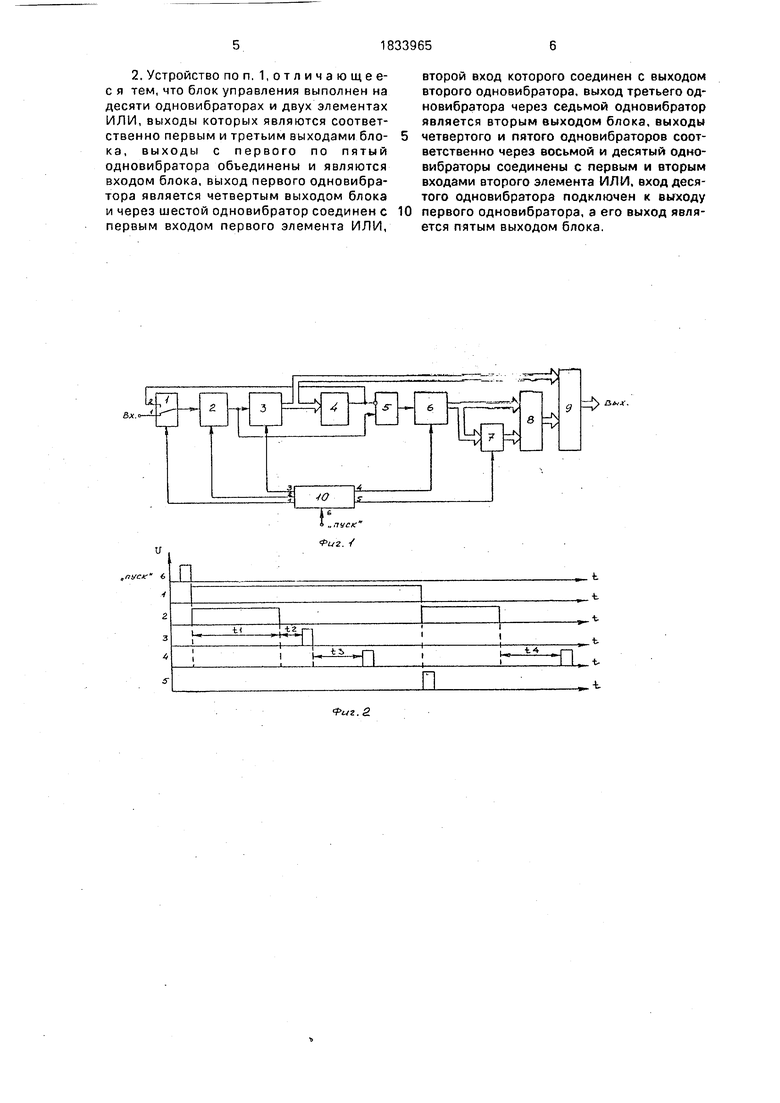

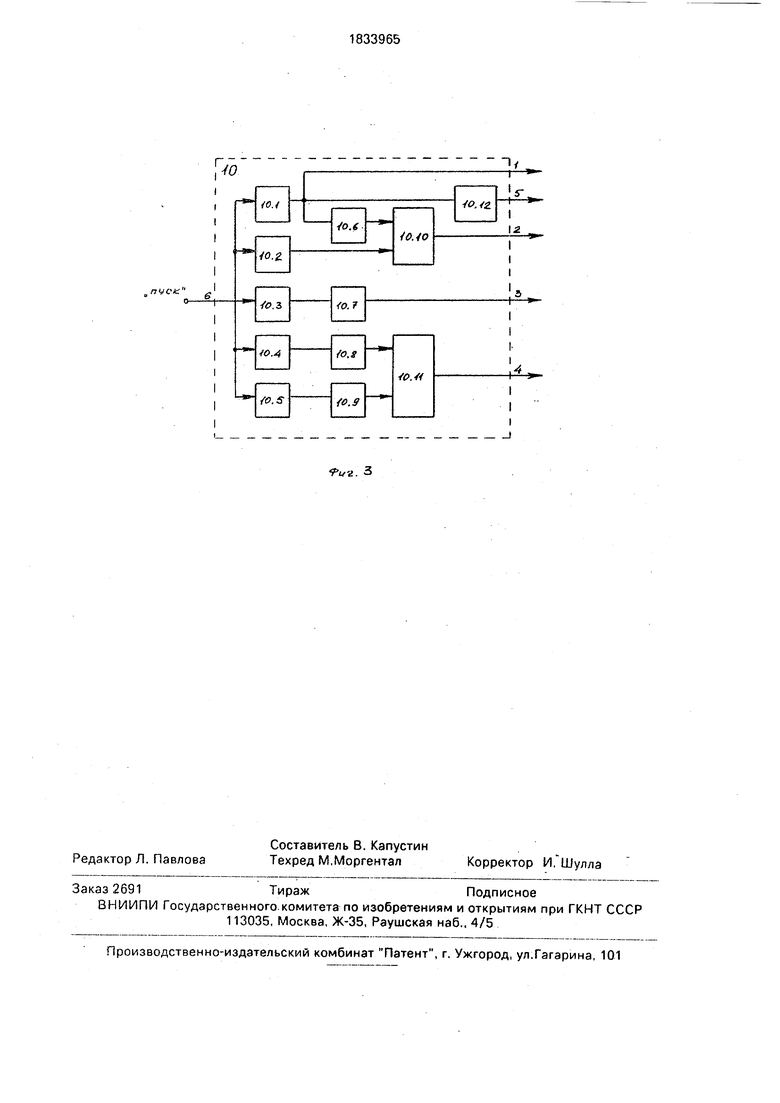

На фиг. 1 представлена схема устройства аналого-цифрового преобразования; на фиг. 2 - временная диаграмма его работы; на фиг. 3 - вариант схемы блока управления.

Схема устройства аналого-цифрового преобразования содержит: 1 - переключатель (П); 2 - блок выборки-хранения (БВХ); 3 - первый аналого-цифровой преобразователь (АЦП1); 4 - цифроаналоговый преобразователь (ЦАП); 5 - блок вычитания (БВ); 6 - второй аналого-цифровой преобразователь (АЦП2); 7 - запоминающий регистр

(ЗР); 8 - вычитатель кодов (В К); 9 -сумматор кодов (СК); 10 - блок управления (БУ).

Элементы схемы соединены следующим образом: первый вход П является входом всего устройства, второй вход П соединен с выходом ЦАП и инверсным входом БВ, выход П соединен со входом БВХ, выход БВХ соединен со входом АЦП1 и прямым входом БВ, выход АЦП1 соединен со входом управления ЦАП и первым входом СК, выход БВ соединен со входом АЦП2, выход АЦП2 соединен со входом ЗР и прямым входом ВК, выход ЗР соединен с инверсным входом ВК, выход ВК соединен со вторым входом СК, выход СК является выходом всего устройства, второй, третий и четвертый выходы БУ соединены со входами управления БВХ, АЦП1 и АЦП2 соответственно, дополнительные выходы БУ 1 и 5

ы

W

ю

о ел

соединены со входами управления П и ЗР, шестой вход БУ является шиной пуск всего устройства.

Нумерация диаграмм на фиг. 2 соответствует нумерации выходов БУ, Схема БУ, показанная на фиг, 3, выполнена на 10 од- новибраторах (блоки 10.1 - 10.9 и 10.12) и двух схемах ИЛИ (блоки 10.10 и 10.11).

Схема устройства аналого-цифрового преобразования работает следующим образом: после подачи на вход БУ команды пуск П подает на вход БВХ входной сигнал (U1). Через промежуток времени t1 (здесь и далее смотри фиг. 2) входной сигнал им запоминается (БВХ переходит из режима слежения в режим хранения). Далее, через промежуток времени t2, определяемый окончанием переходных процессов в БВХ АЦП1 преобразует его выходное напряжение (U2) в код (N1), который поступает на вход управления ЦАП и преобразуется им в напряжение U3. Затем, через промежуток времени t3, определяемый быстродействием ЦАП и БВ, выходное напряжение БВ, равное U2-U3, АЦП2 преобразует в код (N2), который запоминается в ЗР. После этого по команде БУ П подает на вход БВХ напряжение U2, которое им запоминается (при этом на выходе БВХ образуется напряжение U4). БВ вычитает из U4 напряжение U3, полученное при этом напряжение U5 после окончания переходного процесса на выходе БВ (t4) преобразуется в код N3. Далее В К вычитает из кода N2 код N3, результат СК суммирует с кодом N1. В результате на выходе СК образуется код N4, который является выходным кодом устройства.

Рассмотрим получение положительного эффекта более подробно. Обозначим погрешность БВХ - А 1, а погрешность АЦП1 - А2. При этом:

U2 U1.+ A1, U3 U2 + A2,

(1)

(2)

погрешностью ЦАП пренебрегаем. Как видно из выражений 1 и 2 код N2 пропорционален А2. Так как

U4 U2 + А 1,

то U5 А 1. В результате выходной код N4 N1 -(- N2 - N3 свободен от погрешностей АЦП1 и БВХ. В прототипе же выходной код свободен только от погрешности АЦП1 (3). За счет этого существенно повышается точность, так как погрешности БВХ обычно составляют 0,1 % - 0.03%. что препятствует

их применению на входе многоразрядных АЦП (порядка 15-16 двоичных разрядов). Преобразователи без БВХ имеют большую динамическую погрешность.

Устройство аналого-цифрового преобразования может быть выполнено на следующих элементах: АЦП1 и АЦП2 - К1108ПВ1А, ЦАП - М2ПАЦ4171, БВХ - К110.0СК2, П - К590КНЗ, БВ - на операционном усилителе типа К140УД17 с резисторами (по стандартной схеме), БУ - на микросхемах типа К155АГЗ и К561ЛЛ1, СК и ВК - на микросхемах типа К561 ИМ1.

Формула изобретения

1. Устройство аналого-цифрового преобразования, содержащее первый и второй аналого-цифровые преобразователи, циф- роаналоговый преобразователь, блок вычитания, сумматор кодов, блок управления и блок выборки-хранения, выход которого соединен с входом первого аналого-цифрового преобразователя, выходы первого аналого-цифрового преоб разоаателя со единены с соответствующими входами цифроа- налогового преобразователя и первыми входами сумматора кодов, выход цифроана- логового преобразователя соединен с инверсным входом блока вычитания, прямой

вход которого соединен с выходом блока выборки-хранения, а выход соединен с входом второго аналого-цифрового преобразователя, выход сумматора кодов является выходной шиной, первый, второй и третий

выходы блока управления соединены с входами управления блока выборки-хранения, первого аналого-цифрового преобразователя и второго аналого-цифрового преобразователя соответственно, а его вход является

шиной Пуск, о т.л и ч а ю щ е е с я тем, что, с целью повышения точности, в него введены переключатель, запоминающий регистр и вычитатель кодов, причем первый вход переключателя является входной шиной,

второй вход соединен с выходом цифроана- логового преобразователя, а выход соединен с входом блока выборки-хранения, прямые входы вычитателя кодов объединенного входами запоминающего регистра соединены с соответствующими выходами второго аналого-цифрового преобразователя, выходы вычитателя кодов соединены с соответствующими вторыми входами сумматора кодов, а его инверсные входы соедийены с выходом запоминающего регистра, соответственно четвертый и пятый выходы блока управления соединены с входами управления переключателя и запоминающего регистра соответственно.

2. Устройство по п. 1,отличающее- с я тем, что блок управления выполнен на десяти одновибраторах и двух элементах ИЛИ, выходы которых являются соответственно первым и третьим выходами блока, выходы с первого по пятый одновибратора объединены и являются входом блока, выход первого одновибратора является четвертым выходом блока и через шестой одновибратор соединен с первым входом первого элемента ИЛИ,

0

второй вход которого соединен с выходом второго одновибратора, выход третьего одновибратора через седьмой одновибратор является вторым выходом блока, выходы четвертого и пятого одновибраторов соответственно через восьмой и десятый одно- вибраторы соединены с первым и вторым входами второго элемента ИЛИ, вход десятого одновибратора подключен к выходу первого одновибратора, а его выход является пятым выходом блока.

ПЧСХ

| название | год | авторы | номер документа |

|---|---|---|---|

| БЫСТРОДЕЙСТВУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ И СПОСОБ ЕГО КАЛИБРОВКИ | 2006 |

|

RU2341017C2 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ И СПОСОБ ЕГО КАЛИБРОВКИ | 2006 |

|

RU2335844C2 |

| КОДЕР, ПЕРЕДАЮЩЕЕ УСТРОЙСТВО, СИСТЕМА ПЕРЕДАЧИ И СПОСОБ КОДИРОВАНИЯ ИНФОРМАЦИОННЫХ ОБЪЕКТОВ | 2009 |

|

RU2409897C1 |

| Электронный измеритель мощности и энергии | 1988 |

|

SU1638653A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ И СПОСОБ КАЛИБРОВКИ СМЕЩЕНИЯ НУЛЯ | 2013 |

|

RU2520427C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ И СПОСОБ ЕГО КАЛИБРОВКИ | 2010 |

|

RU2442279C1 |

| УСТРОЙСТВО ТЕЛЕМЕТРИЧЕСКОГО ПРИЕМА ЭЛЕКТРОКАРДИОСИГНАЛА | 1995 |

|

RU2106798C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2004 |

|

RU2276833C1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

| Функциональный аналого-цифровой преобразователь | 1989 |

|

SU1688411A1 |

Изобретение относится к цифровой электроизмерительной технике и может быть использовано в информационно- измерительных системах, в частности в аналого-цифровых преобразователях (АЦП). Целью изобретения является повышение точности. Устройство содержит два АЦП, цифроаналого- вый преобразователь, блок управления, сумматор кодов, блок выборки-хранения и блок вычитания. Положительный эффект достигается за счет того, что благодаря введению переключателя, запоминающего регистра и вычитателя кодов удается устранить погрешность, вносимую блоком выборки-хранения путем подачи на его вход тестового сигнала близкого ко входному. 1 з.п. ф-лы, 3 ил.

fu-i. 3

| Бахтиаров Т.Д., Малинин В.В., Школин В.П | |||

| Аналого-цифровые преобразователи/под ред | |||

| Г.Д | |||

| Бахтиарова | |||

| М,, Советское радио, 1980, 280с | |||

| Comparing ADC-Architecture is a designer s best bet | |||

| Koen M., ED, 1987, 35 | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1993-08-15—Публикация

1991-06-03—Подача