Изобретение относится к автоматике, вычислительной и преобразовательной технике, к функциональным, в частности логарифмическим,преобразователям аналоговой формы информации в цифровую.

Изобретение может применяться в контрольно-измерительных приборах, логарифмическихмикровольтметрах, анализаторах спектра, измерителях уровней, затуханий, измерителях амплитудно- частотных характеристик и т.д

Цель изобретения - расширение динамического диапазона путем одновременного кодоуправляемого преобразования как

первого, так и второго преобразуемых напряжений, улучшение точности преобразования путем взаимной коррекции погрешностей блоков, преобразующих уровни первого и второго входных напряжений, улучшение быстродействия преобразованияпутемпараллельного(одновременного) кодоуправляемого преобразования как первого, так и второго входных напряжений.

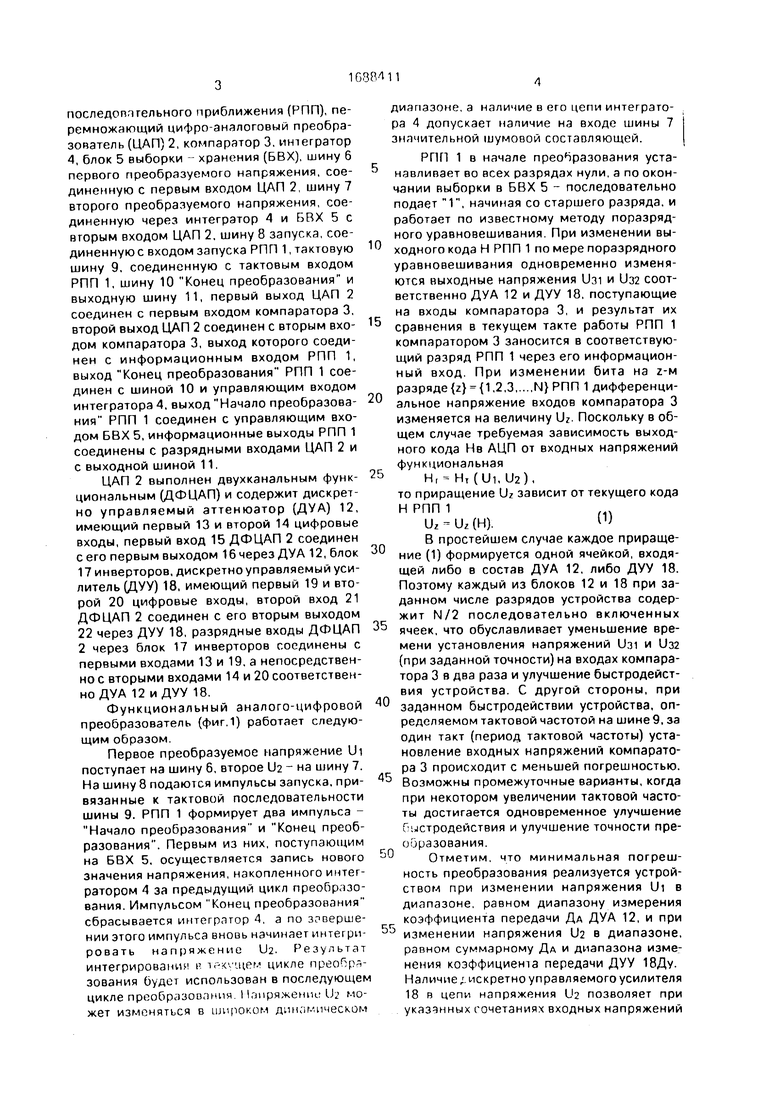

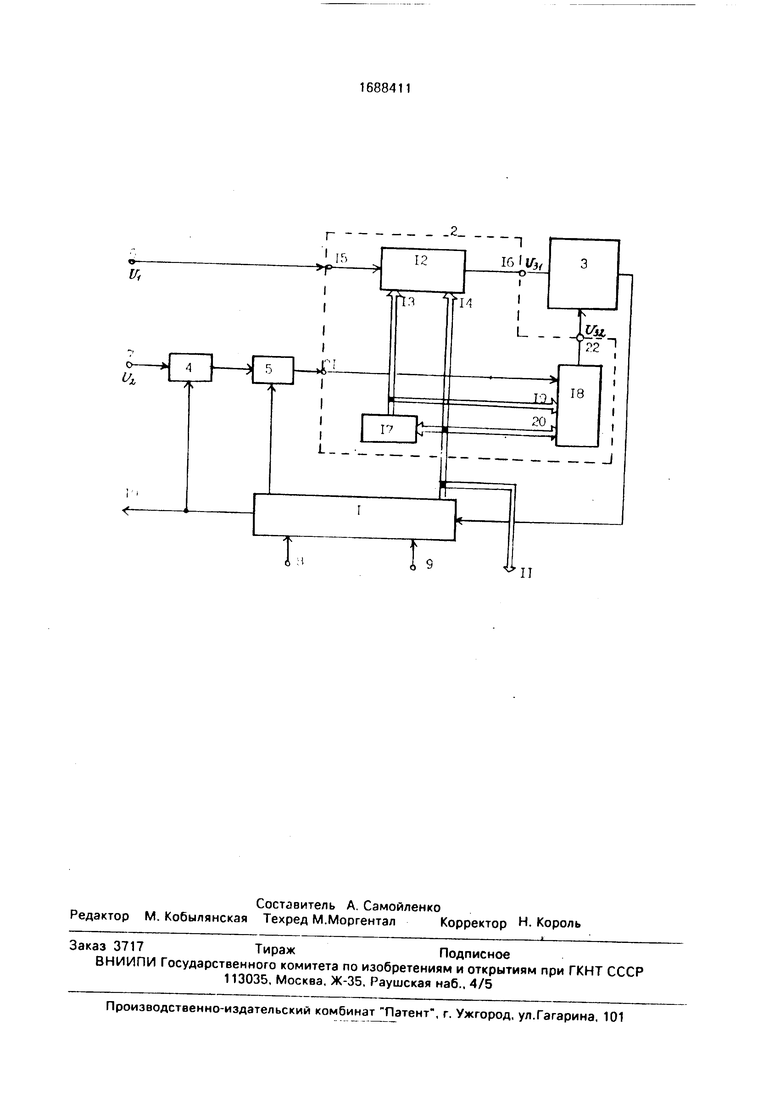

На чертеже изображена структурная схема функционального аналого-цифрового преобразователя.

Функциональный аналого-цифровой преобразователь (фиг. 1) содержит регистр 1

С 00 00

4

последоппгельного приближения (РПП), перемножающий цифро-аналоговый преобразователь (ЦАП) 2, компаратор 3. интегратор 4, блок 5 выборки - хранения (БВХ), шину 6 первого преобразуемого напряжения, сое- диненную с первым входом ЦАП 2, шину 7 второго преобразуемого напряжения, соединенную через интегратор 4 и БВХ 5 с вторым входом ЦАП 2, шину 8 запуска, соединенную с входом запуска РПП 1, тактовую шину 9, соединенную с тактовым входом РПП 1, шину 10 Конец преобразования и выходную шину 11, первый выход ЦАП 2 соединен с первым входом компаратора 3, второй выход ЦАП 2 соединен с вторым вхо- дом компаратора 3, выход которого соединен с информационным входом РПП 1, выход Конец преобразования РПП 1 соединен с шиной 10 и управляющим входом интегратора 4, выход Начало преобразова- ния РПП 1 соединен с управляющим входом БВХ 5, информационные выходы РПП 1 соединены с разрядными входами ЦАП 2 и с выходной шиной 11,

ЦАП 2 выполнен двухканальным функ- циональным (ДФЦАП) и содержит дискретно управляемый аттенюатор (ДУА) 12, имеющий первый 13 и второй 14 цифровые входы, первый вход 15 ДФЦАП 2 соединен сего первым выходом 16 через ДУА 12, блок 17 инверторов, дискретноуправляемый усилитель (ДУУ) 18, имеющий первый 19 и второй 20 цифровые входы, второй вход 21 ДФЦАП 2 соединен с его вторым выходом 22 через ДУУ 18, разрядные входы ДФЦАП 2 через блок 17 инверторов соединены с первыми входами 13 и 19, а непосредственно с вторыми входами 14 и 20 соответственно ДУА 12 и ДУУ 18.

Функциональный аналого-цифровой преобразователь (фиг.1) работает следующим образом.

Первое преобразуемое напряжение Ui поступает на шину 6, второе U2 - на шину 7. На шину 8 подаются импульсы запуска, при- вязанные к тактовой последовательности шины 9. РПП 1 формирует два импульса - Начало преобразования и Конец преобразования. Первым из них, поступающим на БВХ 5, осуществляется запись нового значения напряжения, накопленного интегратором 4 за предыдущий цикл преобразования. Импульсом Конец преобразования сбрасывается интегратор 4, а по завершении этого импульса вновь начинает интегри- ровать напряжение U2. Результат интегрирования р чг-кгщем цикле преобразования будет использован в последующем цикле преобразования I Спряжение LJj может изменяться в широком динамическом

диапазоне, а наличие в его цепи интегратора 4 допускает наличие на входе шины 7 значительной шумовой составляющей.

РПП 1 в начале преобразования устанавливает во всех разрядах нули, а по окончании выборки в БВХ 5 - последовательно подает 1, начиная со старшего разряда, и работает по известному методу поразрядного уравновешивания. При изменении выходного кода Н РПП 1 по мере поразрядного уравновешивания одновременно изменяются выходные напряжения 1)з1 и 1)з2 соответственно ДУА 12 и ДУУ 18, поступающие на входы компаратора 3, и результат их сравнения в текущем такте работы РПП 1 компаратором 3 заносится в соответствующий разряд РПП 1 через его информационный вход. При изменении бита на Z-M разряде {г} {1,2,3N} РПП 1 дифференциальное напряжение входов компаратора 3 изменяется на величину Uz. Поскольку в общем случае требуемая зависимость выходного кода Нв АЦП от входных напряжений функциональная

H, HT(U1,U2),

то приращение Uz зависит от текущего кода Н РПП 1

UZ UZ(H).I1)

В простейшем случае каждое приращение (1) формируется одной ячейкой, входящей либо в состав ДУА 12, либо ДУУ 18. Поэтому каждый из блоков 12 и 18 при заданном числе разрядов устройства содержит N/2 последовательно включенных ячеек, что обуславливает уменьшение времени установления напряжений 1)з1 и U32 (при заданной точности) на входах компаратора 3 в два раза и улучшение быстродействия устройства. С другой стороны, при заданном быстродействии устройства, определяемом тактовой частотой на шине 9, за один такт (период тактовой частоты) установление входных напряжений компаратора 3 происходит с меньшей погрешностью. Возможны промежуточные варианты, когда при некотором увеличении тактовой частоты достигается одновременное улучшение Гистродействия и улучшение точности преобразования.

Отметим, что минимальная погрешность преобразования реализуется устройством при изменении напряжения Ui в диапазоне, равном диапазону измерения коэффициента передачи ДА ДУА 12, и при изменении напряжения LJ2 в диапазоне, равном суммарному ДА и диапазона изменения коэффициента передачи ДУУ 18Ду. Наличие дискретно управляемого усилителя 18 в цепи напряжения U2 позволяет при указанных сочетаниях входных напряжений

увеличить синфазное напряжение входов компаратора 3 и тем самым уменьшить влияние его напряжения смещения на точность преобразования.

Формирование величин (1) младших разрядов с номерами i осуществляется дискретно управляемым аттенюатором (12) в соответствии с выражением

Ui ufc-llfc.(2)

Первое слагаемое обеспечивается одним разрядом первого входа 13 ДУА 12, соединенным с выходом 1-го инвертора, а второе слагаемое - одним корректирующим разрядом второго входа 14 ДУА 12, соединенного с входом 1-го инвертора. Выражение (2) описывает самокоррекцию в ДУА 12

величины U(о с помощью величиныи& для уменьшения погрешности формирова- ния Ui.

Формирование величины (1) старших разрядов с номерами j осуществляется дискретно управляемым усилителем 18 и дискретно управляемым аттенюатором 12 в соответствии с выражением

Uj Uf0 - Ufc ± Ufc .(3)

Первое слагаемое обеспечивается одним разрядом первого входа 19 ДУУ 18, соединенным с выходом J-ro инвертора, вто- рое слагаемое - корректирующим разрядом второго входа 20 ДУУ 18, соединенного с входом J-ro инвертора. Третье слагаемое обеспечивается корректирующим разрядом либо первого входа 13 ДУА 12, соединен- ным с выходом j-ro инвертора (знак плюс в (3)), либо корректирующим разрядом второго входа 14 ДУА 12, соединенным с входом j-ro инвертора (знак минус в (3)). Выражение (3) описывает самокоррекцию

погрешностей в ДУУ 18 (слагаемое U$) и взаимную коррекцию ДУУ 18 с помощью ДУА 12 (слагаемое Lift).

П р и м е р 1. Логарифмическая характе- ристика устройства аналог - код. В этом случае величины (1) и корректирующие величины в (2) и (3) удобнее выражать в единицах затухания.

Затухание ДУА 12 (фиг.1)

A(H)alog,(4)

где а - коэффициент;

а - основание логарифма.

При а 20 и а 10 величина (4) выраже- на в децибелах.

Затухание напряжения U2 относительно напряжения 11з2 (без потери общности коэффициенты блоков 4 и 5 (фиг.1) приняты равными единице), численно равное выраженному в логарифмических единицах усилению ДУУ 18,равно

B(H).(5)

В конце преобразования текущего цикыходной код РПП 1 Н Нт. напряжение входах компаратора 3

U31«U32.(6)

Из (4) и (5) следует

7аС7)

.aB(HTX«

С учетом (7) из (6) вытекает

Ml JA(HT) + b(Hr)J/a

U2

после логарифмирования а1ода А(НТ) + В(Нт).

(8)

(9)

(10)

где величина

С(НТ) - А(НТ) + В(НТ)(11)

показывает затухание напряжения IJ2 по отношению к напряжению Ui.

При линейной связи

СОН) ч.Н,(12)

где ч - разрешающая способность логарифмического АЦП, выходной код из (9), (10) и (11)

HT laloga

(13)

пропорционален логарифму отношения преобразуемых напряжений и показывает затухание напряжения U2 по отношению к Ui.

ДУА 12 и ДУУ 18 могут быть реализованы аналогично авт.св. СССР Nb 1487189. В ДУА 12 цифроаналоговые преобразователи код - ток и операционные усилители соединены по схеме с ослаблением. В ДУУ 18 ЦАП и ОУ соединены по схеме с усилением,

В ДУА 12 предусматриваются разряды в весами А|0 первого входа 13, корректирующие разряды AJK первого входа 13 либо второго входа 14, корректирующие разряды с весами Аж второго входа 14.

В ДУУ 18 предусматриваются разряды с весами BJO первого входа 19 и корректирующие разряды BJK второго входа 20. Указанные величины рассчитывают аналогично авт.св. СССР Nf 1487189. Величины А|0 и AIK выбирают из дискретного множества {А} реализуемых ДУА 12 перепадов ослабления в соответствии с

А|-А|0-А|к«С|.(14)

где Ci - требуемый перепад затухания, управляемый битом 1-го разряда ДФЦАП 2.

Погрешность выражения (14) A-Ai-Ci(15)

удовлетворяет

,(16)

где Ra - дискретность множества {А}.

Величины BJO и BJK выбирают из дискретного множества {В} реализуемых ДУУ 18 значений, а величину AJK - из множества {А} так, что

Bj Bj0-BjK±A|K.Cj,(17)

где С) - требуемый перепад усиления, управляемый битом j-ro разряда ДФЦАП 2.

Погрешность выражения (17) Aj-Bj-Cj(18)

также удовлетворяет (16), поскольку слагаемое AJK в (17) выбирают из множества {А} с дискретностью

,(19)

где Rb-дискретность множества {В}.

Этим достигается улучшение точности ДФЦАП и всего устройства в целом.

П р и м е р 2. Степенная характеристика аналог - код. Пусть связи входов 14 и 20 отсутствуют. Пусть ДУА 12 реализован аналогично формированию соединенных рядов и содержит М1 последовательно соединенных ЦАП и ОУ по схеме с ослаблением, а ДУУ 18 содержит М2 последовательно соединенных ЦАП и ОУ по схеме с усилением. Входы 13 и 19 соединены поразрядно параллельно. Тогда

-)м1,(20)

U31 Ui(HO Нч

НГ

U32 U2()Mi.

(21)

Из (6) вытекает, что в конце преобразования

Ui -HO )/99ч

Ш Но ;1

откуда, возведя обе части в степень

1

М 1 +М2 получаем

йт Ноф-1/М1 + М2

(23)

где Нт Но-Нт - инверсия кода Нт;

Но - емкость ЦАП.

В частном случае, кода М1 М2 1, т.е. в ДУА и ДУУ по одному ЦАП, устройство реализует функцию извлечения квадратного корня

Нт Но VW(24)

lh

Формула изобретения

1. Функциональный аналого-цифровой преобразователь, содержащий регистр последовательного приближения, вход запуска

которого является шиной запуска, тактовый вход является тактовой шиной, выход конца преобразования - шиной Конец преобразования, а информационные выходы соединены соответственно с разрядными входами перемножающего цифроаналого- вого преобразователя, первый вход которого является шиной первого преобразуемого

Q напряжения, первый выход соединен с первым входом компаратора, выход которого соединен с информационным входом регистра последовательного приближения, о т- личающийся тем, что, с целью расшиg рения динамического диапазона преобразуемых напряжений, повышения точности и быстродействия преобразователя, в него введены интегратор и блок выборки и хранения, управляющий вход которого соеди0 нен с выходом Начало преобразования регистра последовательно приближения, выход подключен к второму входу перемножающего цифроаналогового преобразователя, а информационный вход - к выходу

с интегратора, управляющий вход которого подключен к выходу конца преобразования регистра последовательного приближения, а информационный вход является шиной второго преобразуемого напряжения, при

Q этом второй выход перемножающего цифроаналогового преобразователя соединен с вторым входом компаратора, а разрядные входы являются выходной шиной.

2. Преобразователь поп 1, отличаюс щ и и с я тем, что перемножающий цифроа- налоговый преобразователь выполнен на блоке инверторов, дискретно управляемом усилителе и дискретно управляемом аттенюаторе, выход которого является первым

Q выходом перемножающего цифроаналогового преобразователя, вторым выходом которого является выход дискретно управляемого усилителя, первые входы которого объединены с соответствующими первыми входами дискретно управляемого аттенюатора и соединены с соответствующими вы5 ходами блока инверторов, входы которого объединены с соответствующими вторыми входами дискретно управляемого усилителя и дискретно управляемого аттенюатора и являются соответствующими разрядными

0 входами перемножающего цифроаналогового преобразователя, первым и вторым входами которого являются третьи входы дискретно управляемого аттенюатора и дискретно управляемого усилителя соответ5 ственно.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство широкодиапазонного логарифмического аналого-цифрового преобразования | 1988 |

|

SU1571763A1 |

| Аналого-цифровой преобразователь интегральных характеристик напряжений | 1988 |

|

SU1615888A1 |

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

| Модулярный измерительный преобразователь | 2016 |

|

RU2619831C1 |

| Аналого-цифровой преобразователь последовательного приближения | 1985 |

|

SU1248067A1 |

| Преобразователь угла поворота вала в код | 1987 |

|

SU1478331A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1410271A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2007 |

|

RU2359403C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО ДЕЙСТВИЯ | 2003 |

|

RU2245000C2 |

| Дельта-кодер | 1988 |

|

SU1646056A1 |

Изобретение относится в автоматике, вычислительной технике, к функциональным преобразователям аналоговой, формы информации в цифровую и может быть использовано в контрольно-измерительных приборах, измерителях амплитудно-частотных характеристик, анализаторах спектра, селективных вольтметрах, в составе широкодиапазонных функциональных аналого- цифровых преобразователей, в качестве и в составе устройств допускового контроля уровней, затуханий, АЧХ и т.д. Цель изобретения - расширение динамического диапазона преобразуемых напряжений, повышение точности и быстродействия преобразователя. Преобразователь содержит регистр последовательного приближения, перемножающий ЦАП, шину первого и второго преобразуемых напряжений, компаратор, тактовую шину и шину запуска, выходную шину, шину Начало преобразования, шину Конец преобразования, интегратор, блок выборки - хранения. Даны примеры реализации логарифмической и степенной функциональной зависимости аналог-код, пример реализации извлечения квадратного корня из отношения двух напряжений. 1 з.п. ф-лы, 1 ил. Ё

| Ямный В.Б | |||

| Аналого-цифровые преобразователи напряжений в широком динамическом диапазоне | |||

| - Минск, БГУ им | |||

| Ленина, 1980, с | |||

| Способ получения борнеола из пихтового или т.п. масел | 1921 |

|

SU114A1 |

| Способ получения бензидиновых оснований | 1921 |

|

SU116A1 |

| Аналого-цифровой преобразователь последовательного приближения | 1985 |

|

SU1248067A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-10-30—Публикация

1989-10-23—Подача