Пзвестны шифраторы десятичного кода, задаваемого потенциалами на девяти входны.к шинах и преобразуемого в двоично-десятичный код на четырех выходных шинах, содержашие собирательные диодные схемы, транзисторные схемы запрета и выходные инверторы.

Предложенный шифратор отличается от известиых тем, что в нем коллектор транзистора первой схемы запрета подсоединен к первой входной шине, а база - ко второй входной шине; коллектор транзистора второй схемы запрета подсоединен ко второй и через диод к третьей входным шинам, а база -к четвертой входной шине; коллектор транзистора третьей схемы запрета подсоединен к пятой, база - к шестой входным шннам; коллектор транзистора четвертой схемы запрета подсоедииен к четвертой и через диоды к шестой и седьмой входным шинам, база - к восьмой входной шине. Кроме того, нечетные входные шины через нятивходовую собирательную схему подключены к первому выходному инвертору, вторая и шестая входные шины через собирательную схему - ко второму выходному инвертору, K0v1лeктop транзистора четвертой схемы запрета и восьмая входная шина соответственно - к третьему и четвертому выходным инверторам. Выходы инверторов связаны с соответствующими выходными шинами.

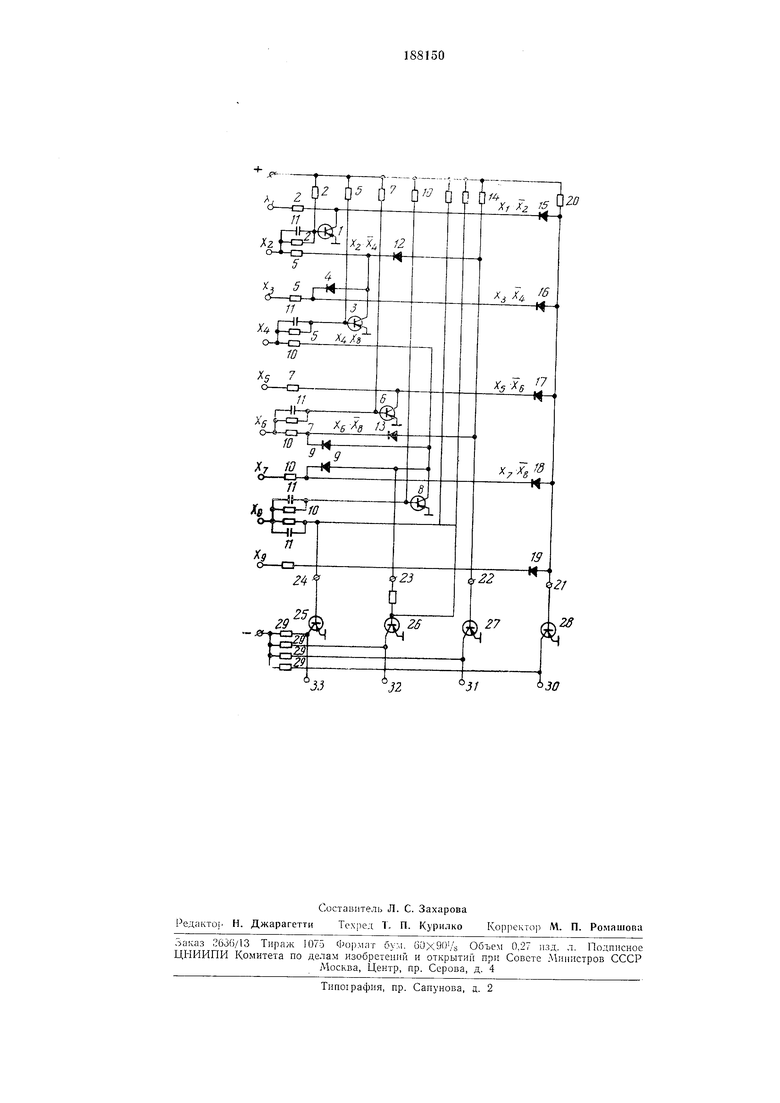

Это обеспечнвает возможность преобразования десятичного кода, заданного низкими управляюш,имн потенциалами на / последовательных входных шинах и высокими потенциалами на остальных (9 - г) шинах, где / - десятичная цифра, в потенциальный двоично-десятичный код. Па чертеже приведена принципиальная схема предлол енного устройства.

Шифратор состоит из четырех схем запрета, двух собирательных схем и четырех выходных инверторов.

Первая схема запрета реализует логическую операцию Aj-Ao и собрана на транзисторе У и сопротивлениях 2.

Вторая схема запрета реализует одновременно две логические операции н Аз-А4 и собрана на транзисторе 3, разделительном диоде 4 и сопротивлениях 5.

Схема запрета, собранная на транзисторе 6 и сопротивлениях 7, ничем не отличается от

первой схемы и реализует операцию .

Для выполнения одновременно трех операций A., XQ-XS, XT Xs схема запрета, собранная на транзисторе 8, разделительных диодах 9 и сопротивле иях W. Емкости

Для получения логической суммы двух величин Х.-Х и используется двухвходовая собирательная схема на диодах 12, 13 и сонротиилепин 14.

Схема на диодах 15-19 и сопротивлении 20 производит логическое суммирование пере.менных 1а . Х, X, , X, Те, А -As и А ,,.

Для уменьшения выходного сопротивления схемы и разброса амплитуды спгпа.юв на выходах 21-24 служат выходные ннверторы на транзнсторах 25-28 с нагрузочными сонротивленнями 29.

Единичному значению входной переменной соответствует низкий уровень напряжения, а нулевому - высокий уровеиь.

Рассмотрим работу схемы.

Цифре «О десятичной системы счисления соответствуют Xi X2 . . .Х9 0, т. е. на исех входных шииах будет высокий потенниа;. При этом транзисторы /, 3, 6, 8 закрыты ноложительным нанряжением питания, и иа выходных шннах 30-33 будет иизкнй нотенниа; (инверсный двоичный код 1111).

Цифре «1 десятичной системы счисления соответствуют , Х2 Хз . . . Х9 0.

Таким образом, на шиие Al низкий нотенциал, а на всех остальных входных шинах - высокий. Диод 15 и транзистор 28 открыты иизким уровием напряжения на шине А, состояние остальных транзисторов остается нрежним. На шииах 30-33 образуется инверсный двоичиый код 1110.

Десятичной цифре «2 соответствует Ац Хз Х4 . . . Х9 0. Следовательно, на шины Al и Х-2 иодаи низкий иотенниал, а на все остальные - высокий. Низкий нотенцнал на входе Ао открывает транзистор /, благодаря чему нотеиииал его коллектора иовышается, и транзистор 28 закрывается. Цизки11 потенниал с шнны Х через диод 12 открывает транзистор 27. На выходных шинах 30-33 образуется ниверсиый двоичный код 1101.

Цифра «3 десятичной системы счнелегнг/ соответствует Ai АО АЗ 1, А4 Х-, -- ... :Х.):0. Нри этом транзисторы / и 27 остаются открытыми, но через уа,иод 16 открывается также транзнстор 28, и на выходных шииах фиксируется инверсный код 1100.

Цри десятичном коде «4 открывается транзистор 3, благодаря чему закрываются транзисторы 27 и 28 и открывается траизистор 26. На выходе образуется код 1011.

Нри десятичном коде «5 донолнительно открывается транзнстор 28. На шинах 30-33 фиксируется код 1010.

Цифре «6 десятичио} системы счисления соответствует открытое состояние транзистора 6. Цри этом нотенинал его коллектора повышается, и закрьи ается траизистор 28, а через диод 13 откр1Л1,ается транзистор 27. На выходе образуется код 1001.

При десятичном коде «7 донолнительно открывается транзистор 28, и иа вьгкодных HJHнах образуется код 1000.

Низкий уровень 1шнряже11ня иа шине As ири десятичном коде «8 открывает транзнсторы 25 и 8, что вызывает иовьннение иотенинала на коллекторе и одновре,1енно на катодах днодо1; 13 н 18, транз11стор1 1 26-28 закрываются, н на выходах ноявляется код 0111.

Нри десятичном коде «9 через диод 19 доиолшггельно открываете;: транзистор .26, и на 11ыходных 1иинах образуется код 0110.

Нр

н 3 о о р е т е н и я

Шифратор дееятичиого кода, задаваемого потенниалами на девяти входных шииах и

преобразуемого в двоично-десятичиый код на четырех выходных шннах, содержагций собирательные диодиые схемы, транзисторные схемы занрета и выходные ннверторы, отличающийся тем, что, с целью преобразования десятичпого кода, задаииого ннзкими унравляюни-iми иотенииалами на / носледовате.льных входных шннах и высокими потенциалами на остальных (9 - /) HJHiiax, где i - десятичная цифра, в нотенциальиый двоично-десятичный

код, коллектор траизистора иервой схемы заирета иодсоедииен к нервой входной шине, а база - ко второй входной шине; коллектор транзистора второй схемы заирета нодсоедннен ко второй н через диод к третьей входные

1нннам, а база-к четвертой входной гниис; коллектор транзистора третьей схемы занрета иодсоединен к нятой, база - к шестой входным ншнам; коллектор транзистора четвертой с.хе.мы занрета нодсоедннсн к четвертой и через диоды к И1естой и седьмой 1 ходным HJHпам, а база - к жзсьмой входной IHIJHC; крол1е юго, нечстн1)1е 1 ходн1ле шины через пятпвходовую собнрател1)Пу10 подк,тючепы к 1и 1ходпому инвертору, вторая и шестая входные пп-пи через собирательиую схе.iy -- ко второ.му выходному инвертору, KO;Iлектор транзистора четвертой ехемы заирета и восьмая входная шииа соответственно - к третьему н четвертому выходным инверторам,

причем выходы инверторов связан с соответствуюшпмн выходными 1нннами.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПЬЕЗОТРАНСФОРМАТОРНОЕ ЗАПОЛИШАЮЩЕЕ УСТРОЙМТ?|11е0-1ЕЛКГ1:: | 1972 |

|

SU331421A1 |

| ОДНОТАКТИЫЙ РЕГИСТР СДВИГА | 1971 |

|

SU291246A1 |

| РАЗРЯД ДИНАМИЧЕСКОГО РЕГИСТРА СДВИГА | 1972 |

|

SU324711A1 |

| ПРЕОБРАЗОВАТЕЛЬ КОД-НАПРЯЖЕНИЕ | 1967 |

|

SU195204A1 |

| Преобразователь двоично-десятичного кода в десятичный | 1980 |

|

SU930665A1 |

| УСТРОЙСТВО для СРАВНЕНИЯ | 1970 |

|

SU269223A1 |

| Реле времени | 1991 |

|

SU1800609A1 |

| АВТОМАТИЧЕСКАЯ ТЕЛЕФОННАЯ СТАНЦ1*Я~- С ЭЛЕКТРОННЫМ УПРАВЛЕНИЕМ | 1972 |

|

SU350202A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1970 |

|

SU287422A1 |

| ОДНОФАЗНЫЙ ТРИГГЕР | 1973 |

|

SU399012A1 |

Даты

1966-01-01—Публикация