(5k ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНО-ДЕСЯТИЧНОГО КОДА В ДЕСЯТИЧНЫЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоично-десятичного кода в код семисегментного индикатора | 1976 |

|

SU712959A1 |

| Двоично-десятичный счетчик в коде 8-4-2-1 | 1985 |

|

SU1272504A1 |

| Двоично-десятичный счетчик вКОдЕ 8-4-2-1 | 1979 |

|

SU849498A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1987 |

|

SU1522411A1 |

| Двоично-десятичный счетчик в коде 8-4-2-1 | 1987 |

|

SU1462474A1 |

| ШИФРАТОР ДЕСЯТИЧНОГО КОДА | 1966 |

|

SU188150A1 |

| Преобразователь двоичных чисел в двоично-десятичные | 1987 |

|

SU1481897A1 |

| Преобразователь двоично-десятичных чисел в двоичные | 1981 |

|

SU1003068A1 |

| Преобразователь двоично-десятичного кода в код семисегментного индикатора | 1983 |

|

SU1200275A1 |

| Устройство для программного управления | 1984 |

|

SU1229730A1 |

1

Изобретение относится к области автоматики и вычислительной техники.

Известны преобразователи двоично-десятичного кода в десятичный, содержащие транзисторы, инверторы, элементы И, И-НЕ и ИЛИ Q.

Наиболее близким к изобретению является преобразователь двоично-десятичного кода в десятичный, содержащий четыре входные шины и десять выходных шин, каждая из которых соединена с коллектором одноименного транзистора, при этом первая входная шина подключена к входу первого инв ртора, выход которого непосредстг венно соединен с базами нечетных транзисторов, а через второй инвертор - с базами нулевого и четных транзисторов, а также элемент И-НЕ,. выход которого подключен к эмиттерам нулевого и первого транзисторов, первый вход - к второй входной шине, второй вход - к третьей входной шине

и прямому входу основного элемента ИЛИ,а третий вход соединен с четвертой входной шиной, инверсный вход основного элемента ИЛИ подключен к выходу элемента И, а его выход сое- дйнен с эмиттерами шестого и седьмого транзисторов 2.

Недостаток известных устройств большая потребляе7« я мощность.

Цель изобретения - уменьшение потребляемой мощности преобразователя двоично-десятичного кода в десятичный.

Указанная цель достигается тем, что в преобразователе двоично-десятичного кода в десятичный, 1содержащем четыре входные шины и десять выходных шин, каждая из которых соединена с коллектором одноименндго транзистора, при этом первая входная шина подключена к входу первого инвео-г тора, ВЫХОД-которого непосредственно соединен с базами нечетных транзисторов , а через второй инверУор - с базами нулевого и четных транзисторов.

а также элемент И-НЕ, выход которого подключен к эмиттерам нулевого и первого транзисторов, первый выход - к второй входной шине, второй вход к третьей входной шине и прямому входу основного элемента ИЛИ,а третий вход соединен с четвертой входной шиной, инверсный вход основного элемента ИЛИ подключен к выходу элемента И, а его выход соединен с эмиттерами шестого и седьмого транзисторов, введены два элемента импликации прямой вход первого из которых соединен с инверсным входом второго элемента импликации и второй входной шиной, инверсный вход подключен к прямому входу второго элемента импликации и третьей входной шине, а выход соединен с эмиттерами второго и третьего транзисторов и первым входом элемента И, второй вход которого подключен к выходу второго элемента импликации и к эмиттерам четвертого и пятого транзисторов, при этом четвертая входная шина соединена с эмиттерами восьмого и девятого транзисторов.

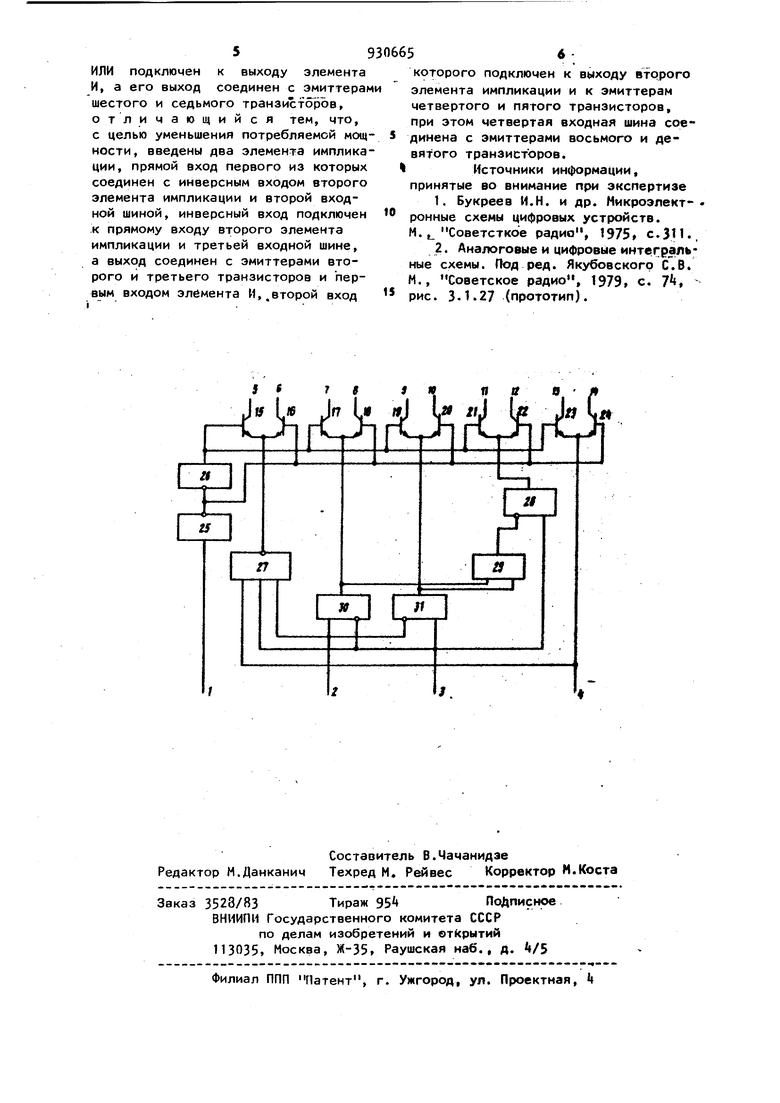

На чертеже представлена функциональная схема преобразователя двоично-десятичного кода в десятичный.

Устройство содержит входные шины , выходные шины 5-1, каждая из которых соединена с коллектором одноименного тгранзистора 15-2, входная шина 1 подключена к входу инвертора 25, выход которого непосредственно соединен с базами нечетных транзисторов 1б, 18, 20, 22, 2k и Через инвертор 26 - с базами нулевого 15 и четных 17, 19, 21, 23 транзисторов, элемент И-НЕ 27, выход которого подключен к эмиттерам транзисторов 15 и 16, первый вход - к входной шине 2, второй вход - к входной шине 3 и прямому входу элемента ИЛИ 25, а третий вход соединен с входной шиной t, инверсный вход элемента ИЛИ 28 подключен к выходу элемента И 29, а его выход соединен с эмиттерами транзисторов 21 и 22, элементы импликации 30 и 31, прямой вход первого из которых соединен с инверсным входом элемента 31 и входной шиной 2, инверсный вход подключен к прямому входу элемента 3V и входной шине 3, а выход соединен с эмиттерами транзисторов 17 и 18 и первым входом элемента И 29,

торой вход которого подключен к выходу элемента 31 и эмиттерам ранзисторов 19 и 20, входная шина соединена с эмиттерами транз стоов 23 и 2.

Устройствоработает следующим обазом.При подаче, например, единичного логического уровня на входные шины l-tj на выходах инвертора 25 и элемента И-НЕ 27 формируется нулевой логический уровень, вследствие чего открыт будет только транзистор 15. П0й подаче, например, единичного логическог о уровня на входные шины 1 и /4 и нулевого логического уровня на входные шины 2 и 3, на выходах элементов 30 и 31 и элемента И 29 формируется единичный логический уровень. И результате этого нулевой логический уровень имеем на выходе элемента ИЛИ 28 и открывается только транзистор 21. Преобразователь двоично-десятичного кода в десятичный функционирует аналогично и при подаче на выходные шины 1- других входных наборов.

Таким образом, введение дополнительных элементов ИЛИ и новых конструктивных связей позволяет уменьшить потребляемую мощность предлагаемого преобразователя двоично-десятичного кода в десятичный по сравнению с известным.

формула изобретения

Преобразователь двоично-десятичного кода в десятичный, содержащий четыре входные шины и десять выходных шин, каждая из которых соединена с коллектором одноименного транзистора , при этом первая входная шина подключена к входу первого инвертора выход которого непосредственно соединен с базами нечетных транзисторов, а через второй инвертор - с базами нулевого и четных транзисторов, а также элемент И-НЕ, выход которого подключен к эмиттерам нулевого и первого транзисторов, первый вход к второй входной шине, второй вход - к третьей входной шине и прямому входу основного элемента ИЛИ, а третий вход соединен с четвертой входной шиной, инверсный вход основного элемента 59 ИЛИ подключен к выходу элемента И, а его выход соединен с эмиттерам шестого и седьмого транзисторов, отличающийся тем, что, с целью уменьшения потребляемой мощнести, введены два элемента импликации, прямой вход первого из которых соединен с инверсным входом второго элемента импликации и второй входной шиной, инверсный вход подключен к прямому входу второго элемента импликации и третьей входной шине, а выход соединен с эмиттерами второго и третьего транзисторов и первым входом элемента И,.второй вход

t Л и а а It Л1 Г Vl V J« U

ГЦ У

и

,

j L

г

tt II о

tzd 5 которого подключен к выходу второго элемента импликации и к эмиттерам четвертого и пятого транзисторов, при этом четвертая входная шина соединена с эмиттерами восьмого и девятого транзисторов. Источники информации, принятые во внимание при экспертизе 1.Букреев И.Н. и др. Никроэлектронные схемы цифровых устройств. М. Советсткое радио, 1975, с.311., 2.Аналоговые и цифровые интеграль ные схемы. Под ред. Якубовского С.В. Н., Советское радио, 1979, с, 7, рис. 3.1.27 (прототип).

Авторы

Даты

1982-05-23—Публикация

1980-06-11—Подача