Изобретение относится к запоминающим устройствам и может быть применено при разработке вычислительных цифровы.х машин, там, где требуется скоростное неразрушаюш,ее воспроизведение «нформащш нрл ее сравнительно медленной смене.

Известны пьезотрансформаторные запоминающие устройства с параллельным неразрушающим воспроизведением информации, содержащие числовые и разрядные шины, в нересечениях которых установлены широкополосные сегнетоэлектрические пьезотрансформаторы, входные электроды которых подключены гк числовЫМ шйиам, выходные электроды объединены и подключены к разрядным шииам, а также ко входу разрядных усилителей считывания, а экранируюп ие электроды объединены и ио-дключены к обЩИ.А шинам, которые соединены с общей точкой устройства через ключи и с выходом формирователя записи, л, кроме того, входы адресных ключей объединены и подключены к выходам формирователя стирания и формирователя записи.

В известных устройствах из-за объединения экранирующих электродов в общие шины по адресам между разрядными шинами существуют большие емкостные паразитные связи, которые снижают надежность, помехозащищенность и объем памяти заиоминаюи1его устройства.

В предлагаемом устройстве для ПОВЫЕИСИИЯ иомехозашишенности устройства без его усложнения, одновременного повышения надежности, экоио.мпчиости, уменьшения аипаратурных затрат, упрощения схе;мы л увеличения объема иа.мяти запоминающего устройства экраиирующие электроды объединены но разрядам в общие шины, и В1слючены па. соответствующие входы разрядных усилителей считывания, причем выходы адресных ключей соединены с числовылш шлнами, а к их объединенным входам через разделительные диоды подключены источиики постояииого иапряження, величина которого выбрана меньше нанряжеиия записи.

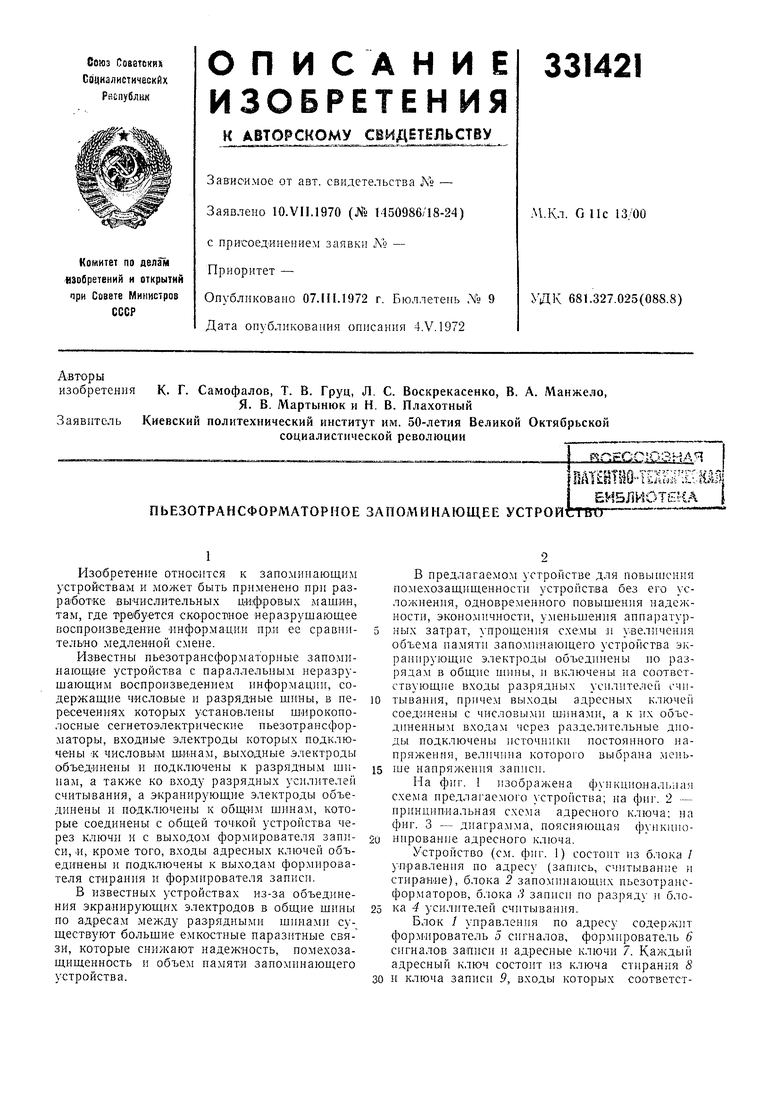

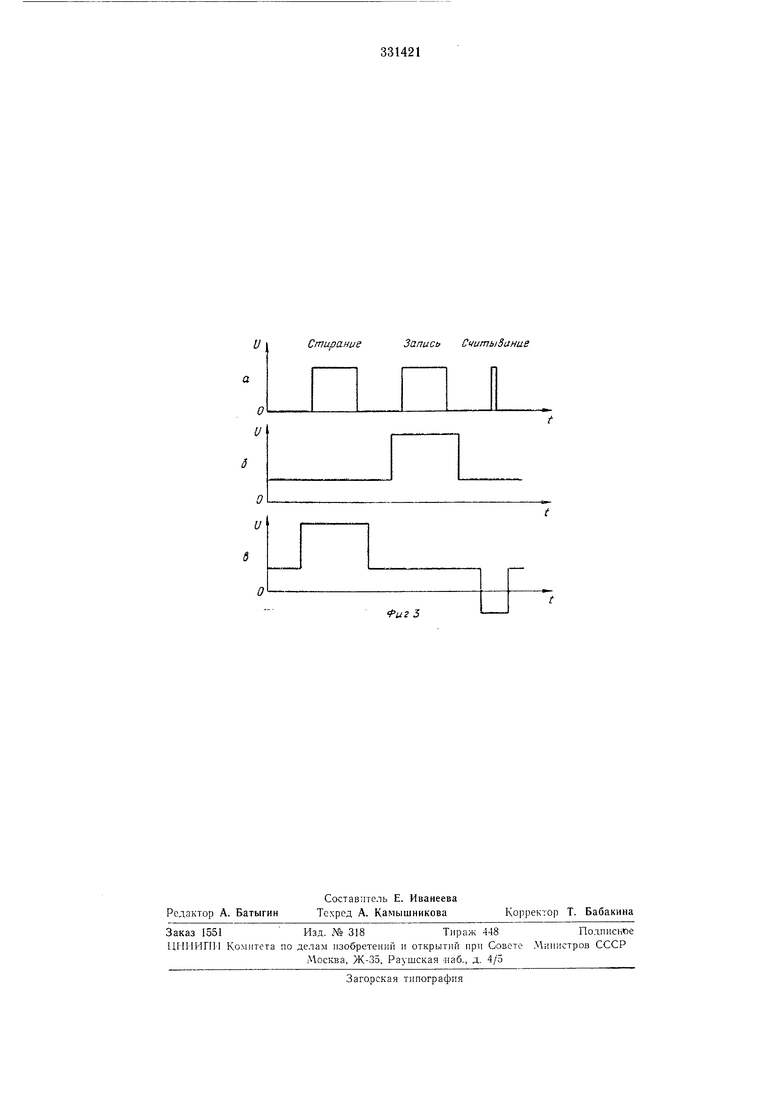

На фиг. 1 изображена фуикииональпая

нредлагаемого стройства; на фиг. 2 -

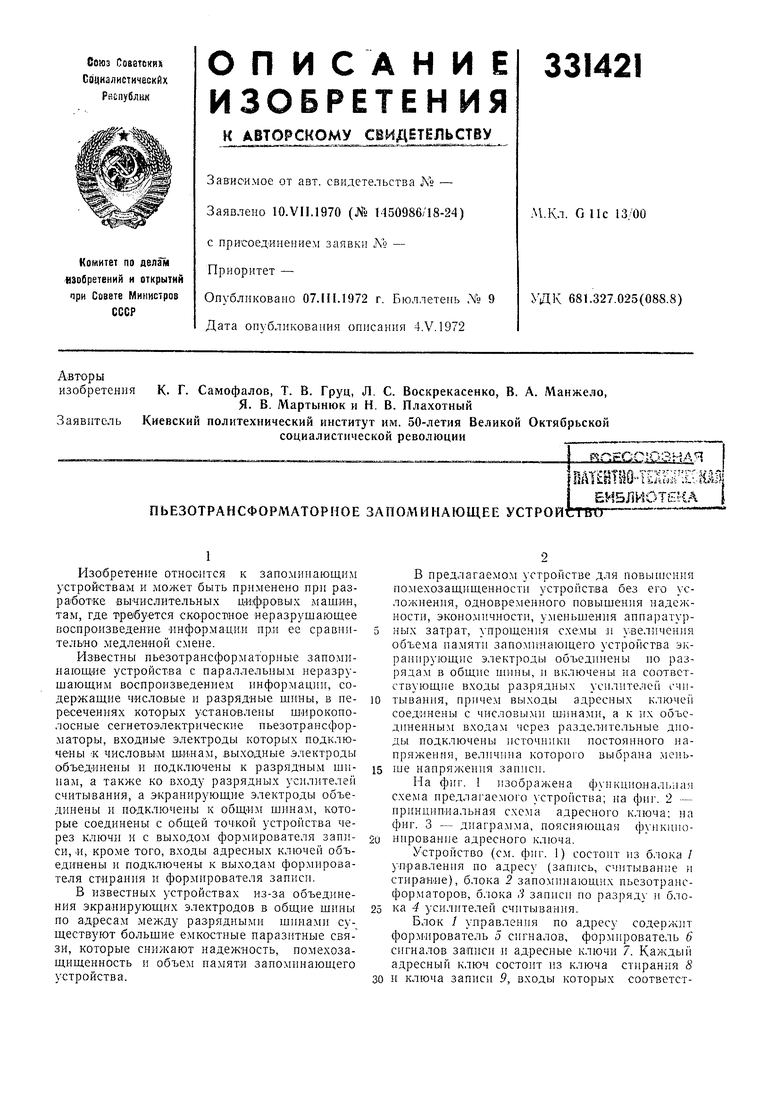

иринциннальная схема адресного ключа: на

фнг. 3 - диаграмма, поясняющая функционироваиие адресного ключа.

Устройство (см. фиг. 1) состоит из блока /

управления по адресу (запись, считывание и

стираш1е), блока 2 запоминающих иьезотрансфор.маторов, блока 3 записи по разряду л блока 4 усилителей считывания.

Блок 1 управления по адресу содержит

формирователь 5 сигналов, формирователь 6

венно объединены шиналш 10 i 11 и подключены на выходы формиравателя стирания и формирователя записи. Кроме того, шина 10 через диод 12 подключена к выходу источника напряжеии5г - bl (клемма /3), а шина // через диод 14 - к выходу источника напряжения + bz (клемма 15). Формирователи сигналов 5 6 выполнены в виде ключей, на их входы (клеммы 16 и 17) подаются напряжения f/3 и (/4 соответственно, вы бираемые из

условия , , а Uj , где Ц, -

напряжение, при котором происходит переноляризаЦИЯ за-поминающей пластины пьезотрансформатора; клеммы 18 и 19 являются управляющими входами формирователей 5 и 6.

Управляющие логические входы ключей 8 и 9 соединены с щинами 20 дешифратора адреса (на фиг. 1 не показан) и соответственно с щннамн 2} рода работы «Стирание и гнинами 22 «Запись, а выходы ключей объединены через резисторы 23 н соединены с чнсловыми щинами 24 блока 2.

В нересечениях чнсловых 24 и разрядиых 25 шин установлены широкополосные сегиетоэлектрические пьезотрансформаторы 26. Они состоят из покрытых металлически ми электродами пьезокерамических пластин, соединенных Л1ежду собой по общему электроду 27. Пластина 28 является генераторной секцией, а пластина 29 - секцией возбуждения. Входные электроды 30 иьезотрансформаторов подключены к числовым шинам, а выходные 31- к разрядным шинам. Экраннрующие электроды объединены но разрядам в общие шииы ,32, которые с одной стороиы соединены через ключи 33 с общей точкой и через резисторы 34 - с выходом формирователя сигналов записи 35, а с другой стороны - через конденсаторы 56 -с входами одного илеча дифференциальных усилителей считывания 37, входы другого плеча которых соединены через конденсаторы 38 с разрядными нл1нами.

Формирователь сигналов 35, как и формир01ватели 5 и 6, выполнен в виде ключа, к входу которого (клемма 39) подключен нсточиик напряжения - Us, выбираемый из условия;

(/-- П

(Клемма 40 является управляющим входом формирователя).

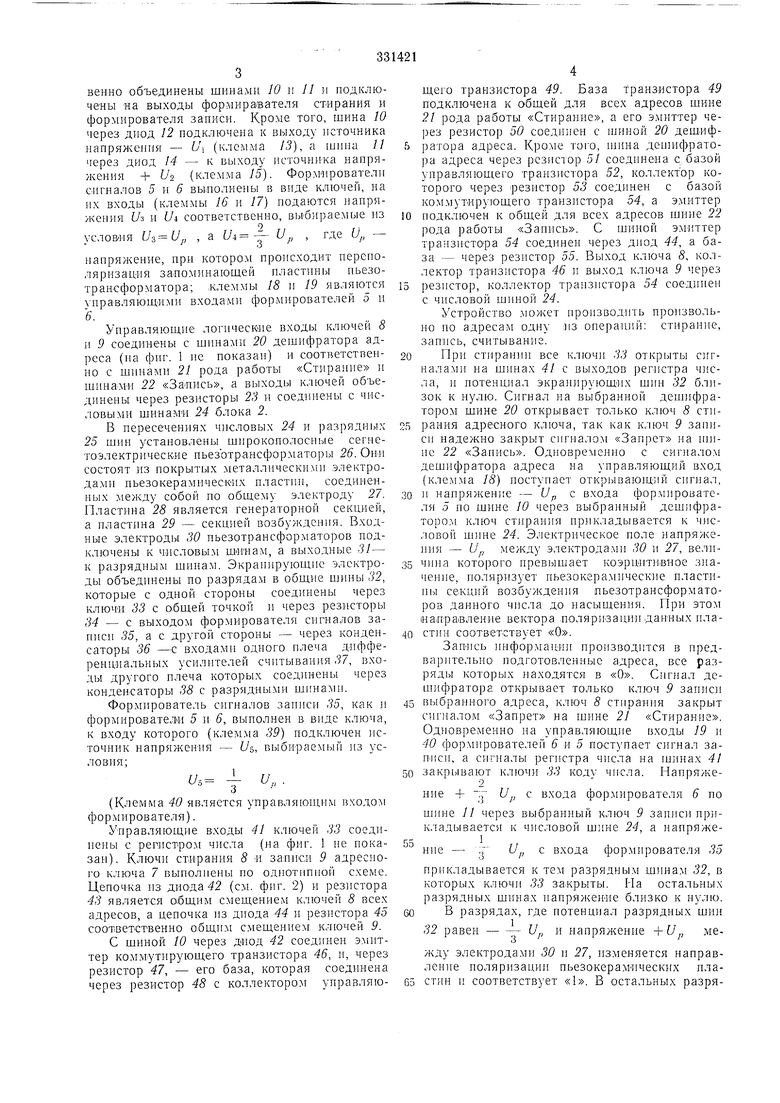

Управляющие входы 41 ключей 33 соедииены с регнстром чнсла (на фиг. 1 не показан). Ключи стирания 8 и заииси 9 адресного ключа 7 выполнены по однотгшиой схеме. Цепочка из диода 42 (см. фиг. 2) и резистора 43 является 0|бщим смещеннем ключей 8 всех адресов, а цепочка из диода 44 и резистора 45 соответственно общим смещением ключей 9.

С шиной 10 через диод 42 соединен эмнттер коммутнрующего транзистора 46, и, через резистор 47, - его база, которая соединена через резистор 48 с коллектором управляющего транзистора 49. База Транзистора 49 подключена к общей для всех адресов шине 21 рода работы «Стираиие, а его эмиттер через резистор 50 соединен с И1иной 20 дещифратора адреса. Кроме того, 1нина деп ифратора адреса через резистор 51 соедннена с базой унравляющего транзистора 52, коллектор которого через резнстор 53 соединеи с базой коммутирующего транзистора 54, а эмиттер подключен к общей для всех адресов шине 22 рода работы «Занись. С шиной эмиттер транзистора 54 соединеи через днод 44, а база - через резнстор 55. Выход ключа 8, коллектор траизистора 46 и выход ключа 9 через резистор, коллектор траизистора 54 соедииен с числовой шиной 24.

Устройство может производить про)1звольио ио адресам одиу из оиераний: стираиие, запись, считывание.

При стираиии все ключи 33 открыты oirналами иа шинах 41 с выходов регистра числа, и иотенциал экраиирующ-их шш-i 32 близок к нулю. Сигнал на выбранной дешифратором шине 20 открывает только ключ 8 стиран ия адресного ключа, так как ключ 9 заииси надежно закрыт снгналом «Запрет на HIHие 22 «Занись. Одиовремеиио с сигналом дешифратора адреса на управляющий вход (клемма 18} поступает открывающий сигиал, и напряжение - U с входа формирователя 5 по щине 10 через выбранный дешифраторо.м ключ стирания ирикладывается к числовой шине 24. Электрнческое иоле иаиряжеиия - Uf, между электродами 30 и 27, величии а которого превышает коэрцитивное значеиие, иоляризует иьезокерамические пластины секций возбуждения пьезотрансформаторов данного числа до насыидения. При этом наиравление ве.ктора иоляризации даниых пластин соответствует «О.

Запись информации ироизводится в предварительно подготовленные адреса, все разряды которых находятся в «О. Сиг)1ал дешифратора открывает только ключ 9 занисн выбранного адреса, ключ 8 стирання закрыт сигналом «Запрет на шине 21 «Стираиие. Одновременно на уиравляюшие в.ходы 19 и 40 формирователей 6 и 5 поступает сигнал записи, а сигиалы регистра числа на 1нинах 4

закрывают ключи 33 коду чнсла. Папряже2

ние + . и,, с входа формирователя 6 по

шиле // через выбраииый ключ 9 записи прикладывается к числовой шине 24, а напряжение - :г b,, с входа формирователя 35

прикладывается к тем разрядным шинам 32, в

которых ключи 33 за крыты. Па остальных

разрядиых шинах иапряжение близко к нулю.

В разрядах, где потенциал разрядных шнн

32 равен /7, и напряжение +U, между электродами 30 и 27, изменяется направление иоляризации пьезокерамических пластин и соответствует «1. В остальных разрядах данного числа напряжение между электродами 30 27 составляет -у Up , что недостаточно для изменения направления поляризацнн соответствующнх пьезокерамнческнх пластин 29; прн этом нанравлен1 е полярнзаннп соответствует «О. Такнм образом, нанравление поляризации пластин 29 пьезотрансформаторов, выбранных дешифратором, соответствует коду записанного числа. Длительность управляющих сигналов записи и стирания определяется временем нереключеиня пьезокерамических пластин.

При счнтываннн информац-ии все адресные ключи 9 записи открыты сигиалом «РазрепАеиие иа шние 22, иа пряжение +U2 приложено к числовы. шииам 24, а все ключи 33 открыты сигналамн на ппшах 41 и потенциал разрядных шин близок к нулю. Импулье иапряжения снгиала чтення на шине 20 открывает выбранный дешифратором адреса ключ 20-; во время его действия к шипе 24 прикладывается напряжение - Ll. Импульсное воздействпе напряжения вызывает импульсную деформацию пьезокерамических секций возбуждения одиовремеино генераторных секций.

На основе явления пьезоэффекта на выходных электродах появляются сигналы, полярность которых определяется нанравлеиием деформа.цш, которая, в свою очередь, оиределяется направлением поляризации секций возбуждения, т. е. заиисанной информацией. Снгналы с выходных электродов суммируются с сигналами на общих шинах, возиикающих из-за изменения тока в ключах 33 ирн считыва«ш1 цнфор:маци.и, .и но разрядным щинам через конденсаторы 38 ноступают на входы одного плеча дифференциальных усилнтелен 37. На входы второго плеча через конденеаторы 36 поступают сигналы с общих шин 32.

В уснЛИтелях цз сигнала разрядной шины вычитается сигнал общей шины, и на ix ВЕЯходах появляются импульспые сигналы, полярность которых оиределяется только наиравленнем иоляризации секций возбуждения, т. е. записанной информаццей. Велцчины амплитуд напряжений - Ui и -ft/2 выбираются зиачительио меньше величины амплитуды наиряжения переполяризацИИ Uj, . Вследствие этого действие напряжений - U м + Us не изменяет значения поляризации секций возбуждения, т. е. не разрушает информацию при воспроизведении.

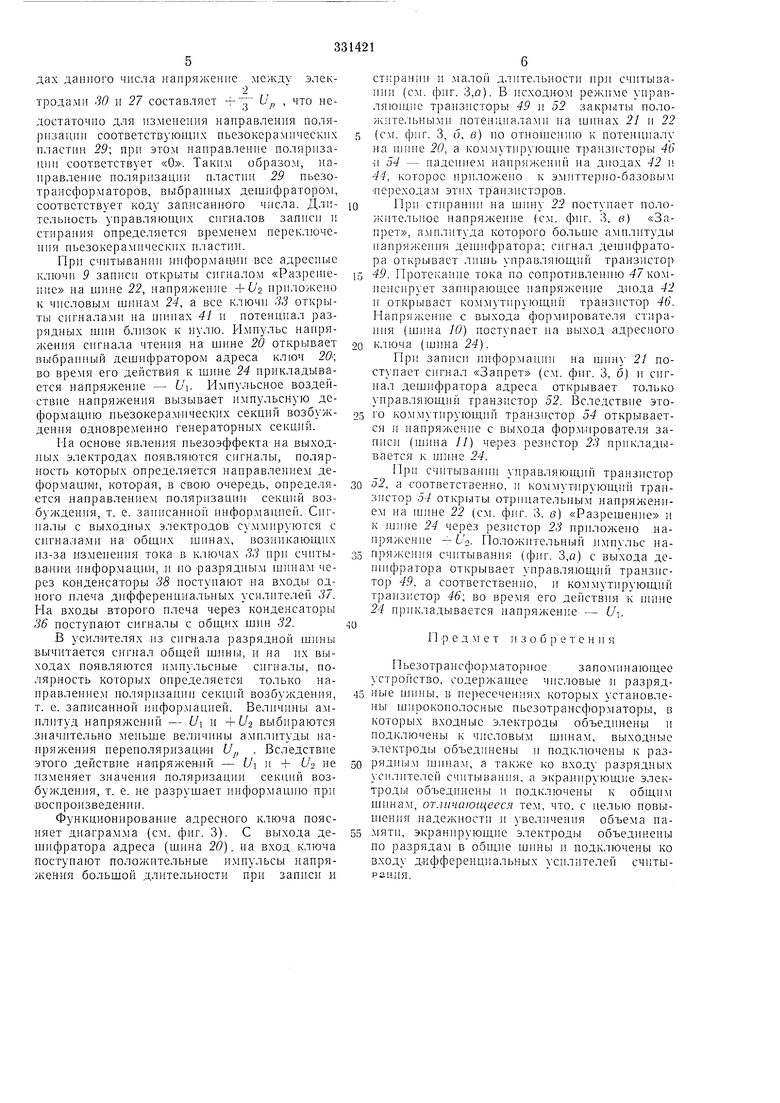

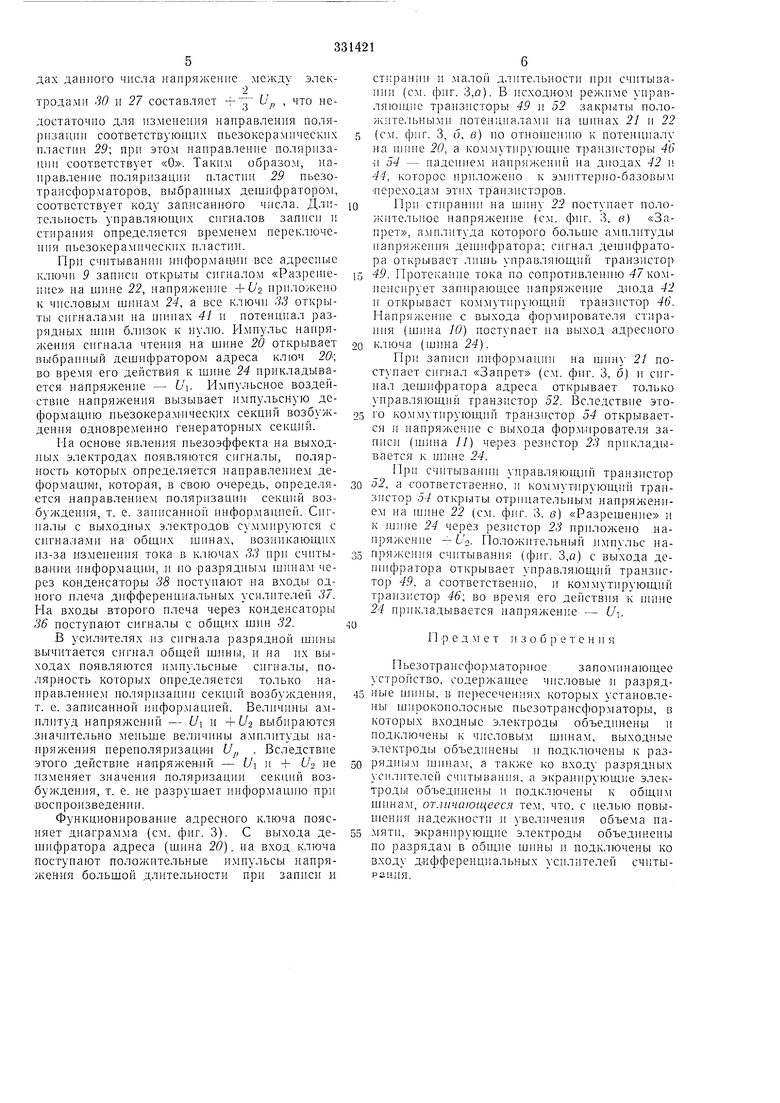

Функционирование адресного ключа поясняет диаграм.ма (см. . 3). С выхода дешифратора адреса (шина 20). на вход ключа поступают положительные и.мпульсы напря/кения большой длительности при записи и

стирании и малоГ длительиости при считывании (см. фиг. 3,о). В исходном режнме унранляюшие транзнсторы 49 и 52 закрыты лоложительиыми потенциалами на 1нниах 21 н 22

5 (см. фиг. 3, о, в) но OTHOHJCHino к потенциалу иа шиие 20, а колимутирующие тра}1зисторы 46 и 54 - иадеиием напряжений иа диодах 42 и 44, которое ириложеио к эмиттерио-базовым иерехода.м этих транзисторов. 0При стираиии на шину 22 постунает положительное напряжение (см. фнг. 3, в) «Запрет, амплитуда которого больше амплитуды напряжения дешифратора; сигнал деи ифратора открывает лишь управляющий транзистор

15 49. Протекаиие тока по сопротивлеиию 47комцеисирует запирающее иапряженпе диода 42 и открывает коммутирующий транзистор 46. Напряженне с выхода формировател.я стирання (шина 10) поступает иа выход адресного

0 ключа (шина 24).

При записи нформации на шину 21 постунает сигнал «Заирет (см. фиг. 3, б) и сигнал дешифратора адреса открывает только управляющий транзистор 52. Вследствие этого ко.м.мутирующий транзистор 54 открывается и ианряжеиие с выхода форм ирователя записи (шица //) через резистор 23 прикладывается к шине 24.

При считывании уиравляющий транзистор

0 о2, а соответственно, и коммутирующий траизистор 54 открыты отрицательным напряжением на шине 22 (см. фиг. 3. в) «Разрешение и к шине 24 через резистор 23 п|рнложено наиряженне --LV Положнтельный нмпульс напряжения считывания (фиг. 3,о) с выхода деншфратора открывает уиравляющий транзистор 49. а соответственно, i коммутирующий траизистор 46; во время его действия к шиие 24 прикладывается иапряжеи е - Ll.

Предмет и з о б р е тени я

Пьезотрансформаторное запоминающее устройство, содержащее числовые и разрядные шины, в пересечениях которых установлены широкополосные иьезотраисформаторы, в которых входные электроды объедипеиы и нодключеиы к числовым шинам, выходные электроды объедииены и подключены к разрядны.м шинам, а также ко входу разрядных силителей считывания, а экранирующие электроды обт едииены и иодключеиы к общим тинам, отличающееся тем, что, с целью повышения надежности i увеличения объема памяти, экранирующие электроды объед1 неиы но разрядам в о. шины и подключены ко входу дифференциальных усилителей считыPiiHИЯ.

/5 о

8v- W

J2

/27/5

/J

0 -P

L -F

I±

p/

W)39

та

/7 JJ

3 4/1 J-

1

33

/4

I

31

26A

-28

UU-L

27

Еаша-)

-29

30

J.J

2425 Ji

P5- 22

iii

и

hf

2

i: ЬЗ Jg

. /

| название | год | авторы | номер документа |

|---|---|---|---|

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU385314A1 |

| Запоминающее устройство | 1973 |

|

SU481067A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВОЦП•'t-li | 1971 |

|

SU419982A1 |

| Запоминающее устройство | 1968 |

|

SU842961A1 |

| Запоминающее устройство | 1976 |

|

SU690564A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU364962A1 |

| Запоминающее устройство | 1973 |

|

SU447757A1 |

| Полупостоянное запоминающее устройство с электрической перезаписью информации | 1983 |

|

SU1088068A1 |

| ВСЕСОЮЗНАЯ ' | 1973 |

|

SU368645A1 |

| Полупостоянное запоминающее устройство с электрической перезаписью информации | 1976 |

|

SU634373A1 |

/Л

Даты

1972-01-01—Публикация