Известны логические элементы, содержащие диодно-резистивный дешифратор, инвертор и дополнительный диодный переключатель тока, один диод которого подключен к выходу инвертора, а другой - к его входу. Возможно подключение эмиттерного повторителя на вход инвертора.

Предложенное устройство отличается тем, что в нем выход инвертора через диод соединен с коллектором эмиттерного новторителя, а эмиттер носледнего через диод - с базой инвертора.

Это повышает быстродействие устройства и снижает рассеиваемую моигность.

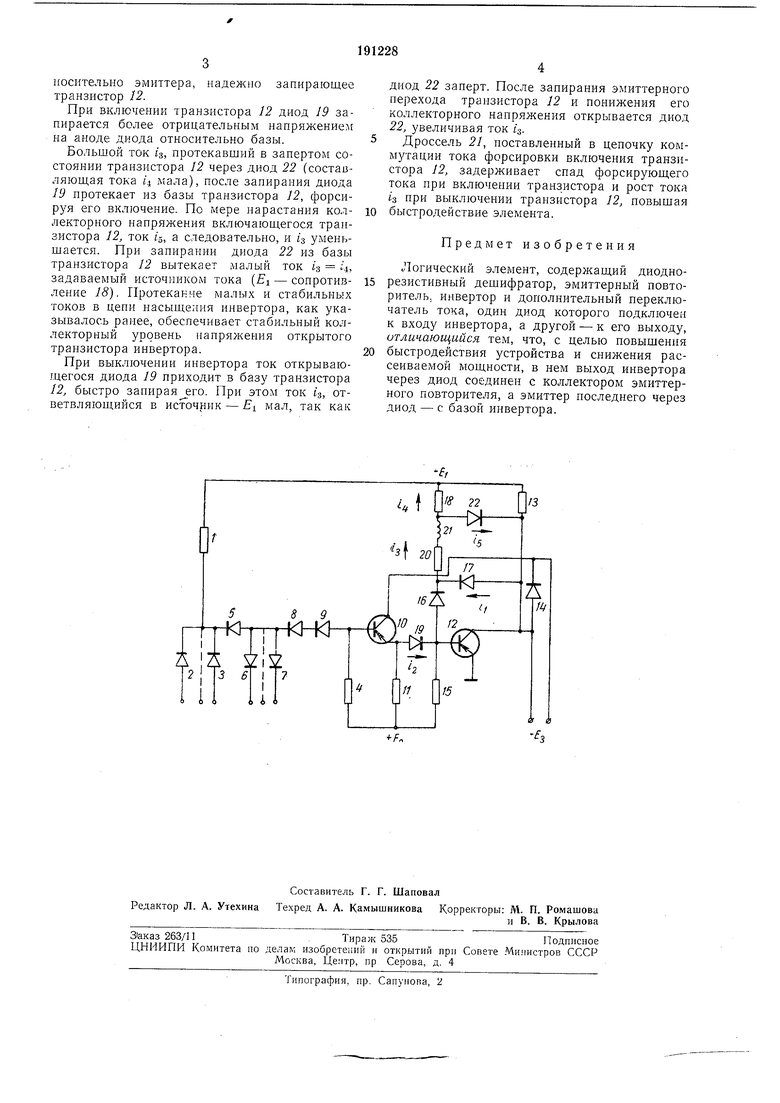

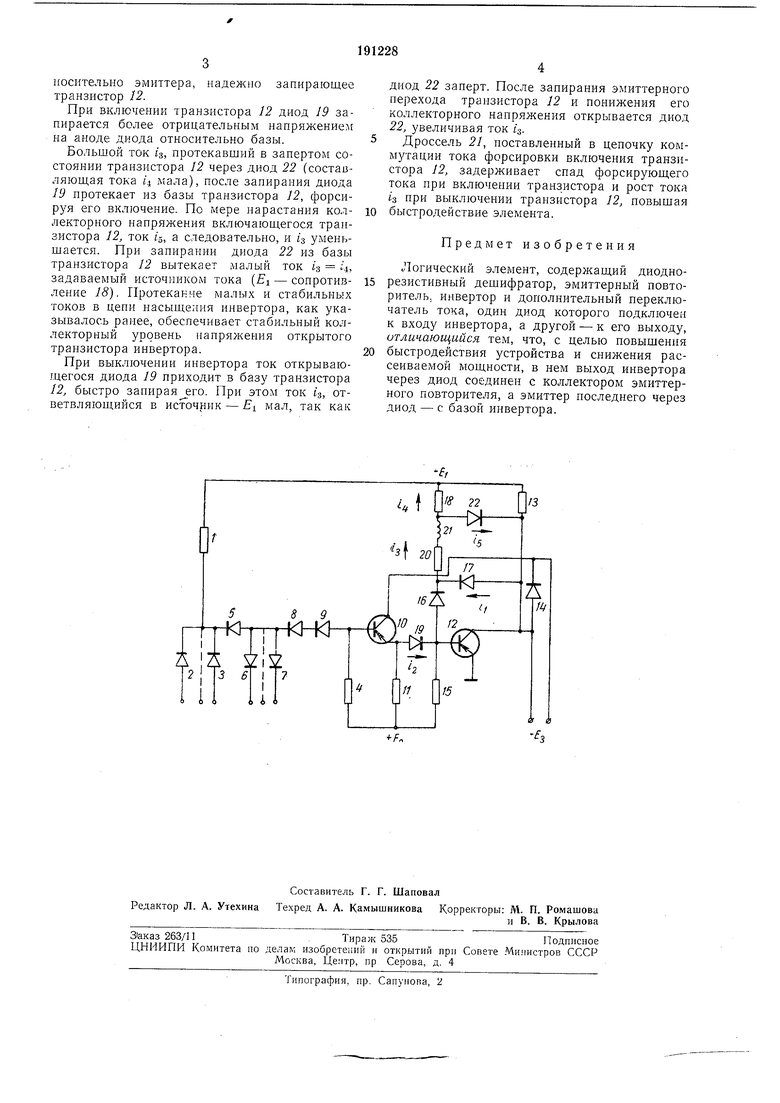

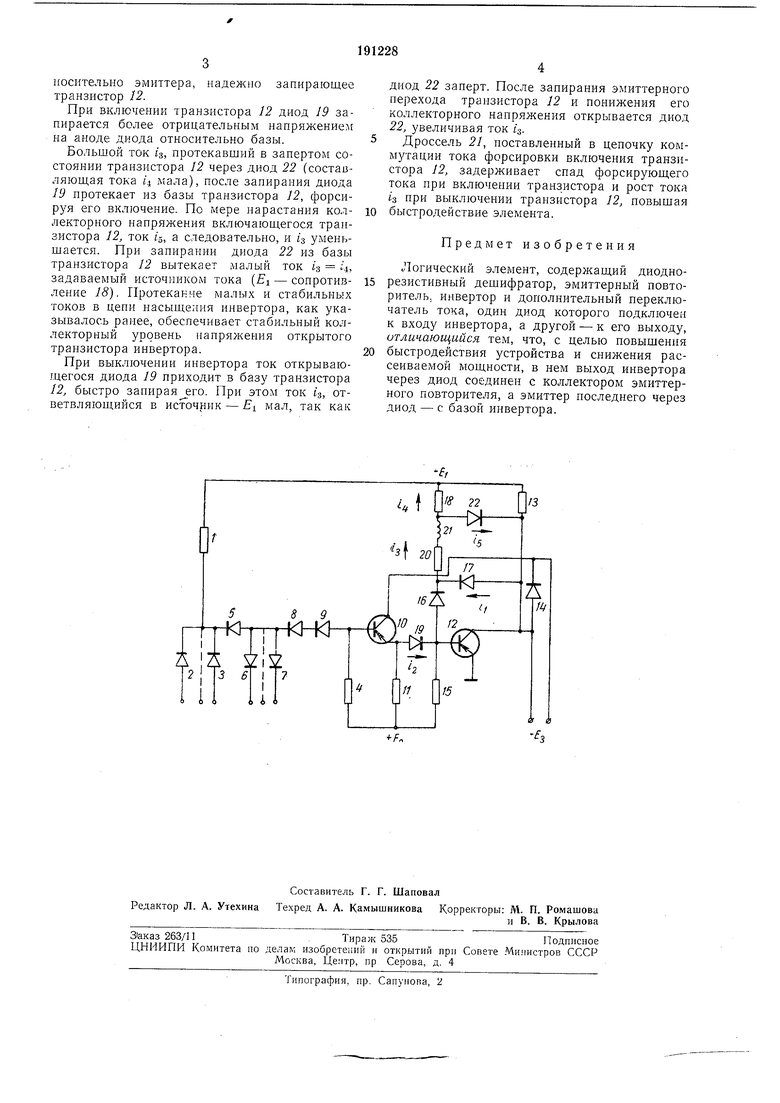

На чертеже дана схема элемента.

Она содержнт схемы И и ИЛИ (сонротивленне /, диоды 2, 3; сопротивление 4, диоды 5, 6, 7, S, 9}, эмиттерный повторитель (транзистор 10, сопротивление нагрузки 11); схему инвертора (транзнстор 12, коллекторная пагрузка 13, диод фиксации нижнего уровня 14) с цепочкой нелинейной обратной связи (сопротивления 15, дноды 16 и 17), с сопротивлением 18, задаюи,им ток в базовой цепи к открытом инверторе, и ключевым диодом 19.

Связь базы транзистора 12 с коллектором с помош,ью сопротивлення 20, дросселя 21 и диода 2 обеспечивает отключение токов фо;)сировки включения транзнстора 12 от базы.

В реальных устройствах логические элемеиты срабатывают от сигналов, формируемых аналогичным элементом.

Подача нижнего уровня сигнала элемента (прпблизительно равного - 3) обеспечивает на аноде диода 19 более отрицательный потенциал, чем на катоде (потенцнал катода диода 19 равен Ябэ открытого транзистора /2).

Диод 19 отключает эмиттерный повторитель от базовых цепей транзистора 12.

Верхний уровень выходного сигнала инвертора формируется с помощью цепочки нелинейной обратной связн, причем, ио диодам цепочки протекают пебольшие токи, задаваемые источииком тока. Это обеспечивает более стабильный верхний уровень выходного сигпала по сравнению с ypoБпя rи известных схем н хорошие нагрузочные свойства, так как ток /1 мал. Прн этом диод 22 закрыт более отрнцательным иаиряжеиие.м иа аноде, образованном делителем еонротивлений 20 и 18. Дроссель 21 не влияет на статический режн пивертора. Ток гь протекающий через диод 17 обратной сзязи, мал, что гарантирует хорошие нагрузочиые качества элемента.

Ток /J диода 19 протекает через цепочку 16,

иосительно эмиттера, надежно запирающее транзистор 12.

При включении транзистора 12 диод 19 запирается более отрицательным напряжением на аноде диода относительно базы.

Большой ток гз, протекавший в запертом состоянии транзистора 12 через диод 22 (составляющая тока ц мала), после запирания диода 19 протекает из базы транзистора 12, форсируя его включение. По мере нарастания коллекторного напряжения включающегося транзистора 12, ток /5, а следовательно, и гз уменьшается. При запирании диода 22 из базы транзистора 12 вытекает малый ток /з i, задаваемый источником тока (fi - сопротивление 18. Протекание малых и стабильных токов в цепи насыщения инвертора, как указывалось ранее, обеспечивает стабильный коллекторный уровень напряжения открытого транзистора инвертора.

При выключении инвертора ток открывающегося диода 19 приходит в базу транзистора 12, быстро запирая его. При этом ток гз, ответвляющийся в источник - EI мал, так как

диод 22 заперт. После запирания эмиттерного перехода транзистора 12 и понижения его коллекторного напряжения открывается диод 22, увеличивая ток rg.

Дроссель 21, поставленный в цепочку коммутации тока форсировки включения транзистора 12, задерживает спад форсирующего тока при включении транзистора и рост тока гз при выключении транзистора 12, повышая

быстродействие элемента.

Предмет изобретения

Логический элемент, содержащий диоднорезистивный дешифратор, эмиттерный повторитель, инвертор и дополнительный переключатель тока, один диод которого подключен к входу инвертора, а другой - к его выходу, итличающийся тем, что, с целью повышения быстродействия устройства и снижения рассеиваемой мощности, в нем выход инвертора через диод соединен с коллектором эмиттерного повторителя, а эмиттер последнего через диод - с базой инвертора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Транзисторный инвертор | 1990 |

|

SU1739463A1 |

| Однотактный преобразователь постоянного напряжения | 1990 |

|

SU1767649A1 |

| Формирователь импульсов управления | 1985 |

|

SU1290501A1 |

| Двухтактный инвертор | 1978 |

|

SU748747A1 |

| Импульсный стабилизатор постоянного напряжения последовательного типа | 1990 |

|

SU1725204A2 |

| ДВУХТАКТНЫЙ ИНВЕРТОР | 1992 |

|

RU2009609C1 |

| ТТЛ-вентиль | 1985 |

|

SU1324105A1 |

| Коммутатор аналоговых сигналов | 1981 |

|

SU978345A1 |

| МАГНИТНО-ТРАНЗИСТОРНЫЙ КЛЮЧ | 1991 |

|

RU2013860C1 |

| СРАВНИВАЮЩЕЕ УСТРОЙСТВО | 1971 |

|

SU291184A1 |

. t U L, D

589

-КЬ-гт-КЬ-К}

2 3 6

Даты

1967-01-01—Публикация