Известны делители частоты с любым це.лочисленным коэффициентом деления на двоичных ячейках.

Предложенный делитель частоты отличается от известных тем, что содерл ит два поочередно работающих счетчика, входы которых подключены к выходам схем совпадения; на импульсные входы схем совпадения поступают входные импульсы, а на управляющие входы - напряжения с разных плеч триггера, входы которого соединены соответственно с выходами счетчиков.

Это позволяет повысить максимальную рабочую частоту и получить любой сдвиг импульсов по фазе относительно друг друга.

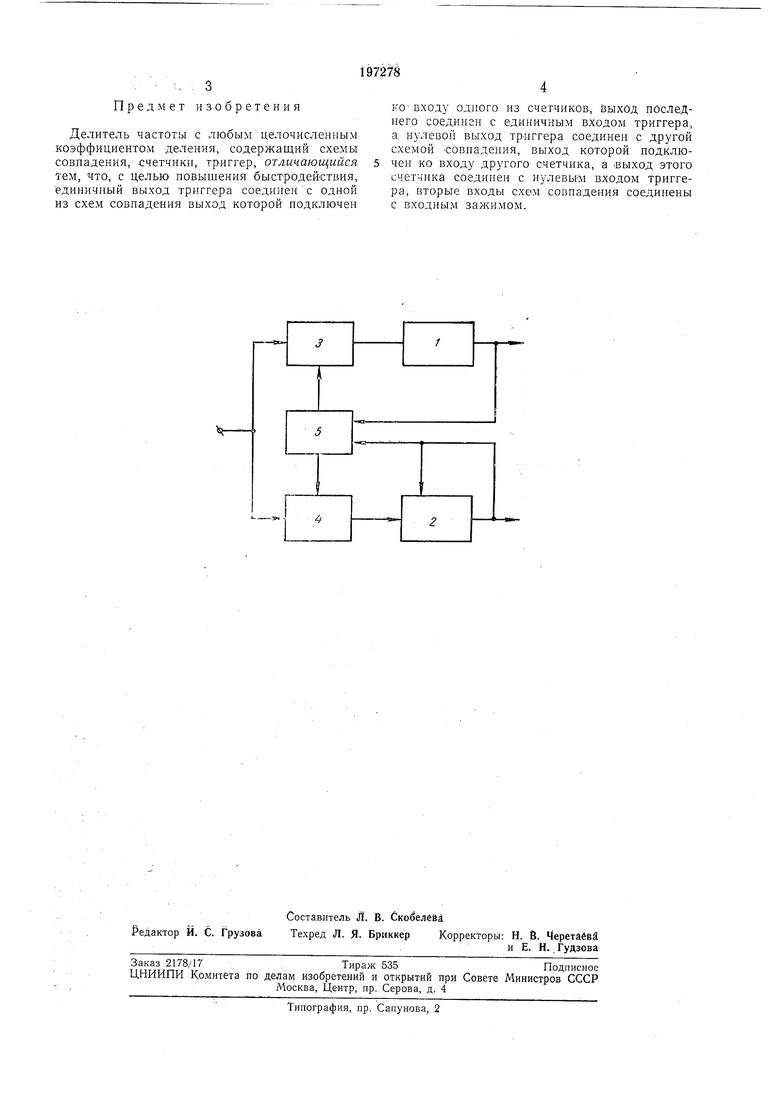

На чертеже представлена функциональная схема делителя.

Делитель состоит из двух счетчиков 1 п 2, двух схем совпадения 5 и 4 и триггера 5.

На схемы совпадения 3 и 4 подаются импульсы, подлежащие делению, и управляющие напряжения с разных плеч триггера 5. Одна из схем совпадения всегда открыта, другая закрыта и счетчики вследствие этого работают поочередно. Коэффициенты деления обо их счетчиков подобраны так, чтобы их сумма была равна требуемому коэффициенту. Один из счетчиков целесообразно использовать без обратных связей с максимально возможным двоичным коэффициентом деления.

Например. Требуемый коэффициент деления 173. Коэффициент деления одного счетчика выбираем равным 128. Тогда коэффициент другого будет равен 173-128 45.

Делитель частоты работает следующим образом.

Когда открыта схема совпадения 3, работает счетчик /. После того, как через схему совпадения пройдут 128 (для рассматриваемого случая) импульсов, на выходе счетчика вырабатывается импульс. Этот импульс установит триггер 5 в другое состояние. В результате схема совпадения 3 закроется, схема совпадения 4 откроется и начнет работать счетчик 2.

Если через схему совпадения 4 пройдет 64 импульса, на выходе, счетчика 2 вырабатывается импульс. Триггер 5 установится в исходное состояние и njpouecc повторится. Импульс на выходе счетчика 2 используют также для обратной связи в счетчике 2 с целью обеспечения его коэффициента деления, равного 45. После выработки этого импульса счетчик 2 находится в режиме ожидания, поэтому Bed переходные процессы в цепи обратной связи не ;ЕЛИЯЮТ на быстродействие всего делителя, Фазовый сдвиг между импульсаМИ определяется только соотношением коэффициентов деления счетчиков 1 и 2,

Предмет изобретения

Делитель частоты с любым целочисленным коэффициентом деления, содержащий схемы совпадения, .счетчикн, триггер, отличающийся тем, что, с целью повышения быстродействия, единичный выход триггера соединен с одной из схем совнадения выход которой нодключен

ко-входу одного из счетчиков, выход последнего соединен с единичным входом триггера, а нулевой ВЕЛХОД тр 1ггера соединен с другой схемой совнадения, выход которой подключен ко входу другого счетчика, а выход этого счетчика соединен с нулевьгм входом триггера, вторые входы схем совпадения соединены с входным зажимом.

| название | год | авторы | номер документа |

|---|---|---|---|

| УПРАВЛЯЕМЫЙ ДЕКАДНЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ С ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ | 1970 |

|

SU270354A1 |

| ГЕНЕРАТОР СЛУЧАЙНЫХ ПРОЦЕССОВВПТБ4чп2л^ iiiJijiiEaf | 1972 |

|

SU439064A1 |

| Управляемый делитель частоты | 1976 |

|

SU594585A1 |

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ ЧАСТОТЫ С ДРОБНЫМ КОЭФФИЦИЕНТОМ | 1971 |

|

SU436446A1 |

| Устройство управления многофазным инвертором | 1974 |

|

SU600672A1 |

| ЦИФРОВОЕ УСТРОЙСТВО для ИЗЛ\ЕРЕНИЯ ФАЗОВЫХСДВИГОВ | 1972 |

|

SU353207A1 |

| Синтезатор интервалов времени | 1986 |

|

SU1406558A1 |

| Система регулирования частоты вращения судовой турбины | 1981 |

|

SU964198A1 |

| Делитель частоты | 1982 |

|

SU1019644A1 |

| Селектор импульсов | 1973 |

|

SU471663A1 |

Даты

1967-01-01—Публикация