1

Изобретение относится к области преобразовательной техники и может быть использовано в системах электропривода, автоматики, вычислительной техники для управления многофазным инвертором.

Известное устройство управления с делением частоты на три 1 содержит задающий генератор и формируюпдее устройство из трех потенциальных триггеров с раздельной установкой и шести трехвходовых схем совпадений, соединенных между собой так, чтобы можно было дешифрировать каждое разрешенное состояние ригистра.

При подаче на входы устройства двух сдвинутых друг относительно друга на полпериода последовательностей импульсов на одноименных выходах триггеров регистра благодаря логической схеме образуется трехфазное напряжение. Основными недостатками такого устройства являются возможность сбоя в ложный режим работы на тройной частоте и большая длительность переходного процесса при пуске.

Известное устройство управления с трехфазным выходом 2 содержит задаюш,ий генератор и формирующее устройство, выполненное на девяти элементах И-НЕ, соединенных между собой так, чтобы на трех выходах получать три последовательности, длительность импульсов в каждой из которых равна

длительности входных импульсов, а частота в три раза меньше при сдвиге импульсов каждого выхода относительно соседних на период входных импульсов. В том случае, если входная последовательность представляет собой прямоугольные, импульсы, с выходов схем И-НЕ может быть снято трехфазное напряжение, скважность каждой из фаз которого равна двум.

В устройстве практически отсутствует переходный процесс, так как оно не может устойчиво находиться в одном из запрещенных состояний.

К недостаткам этого устройства следует

отнести ограничения в выборе также величины фазового сдвига и числа фаз, отсутствие парафазных выходов.

Известное устройство для получения трех сдвинутых на 120° напряжений из однофазного напряжения той же частоты 3 содержит задающий генератор и формирзющее устройство, в которое входят статический регистр на трех триггерах и шесть схем совпадений на два входа, и позволяет с помощью

наращивания регистра и схем совпадений получить многофазный преобразователь (один триггер и две схемы совпадения на каждую дополнительную фазу) с жестким фазовым сдвигом.

Такой инвертор наиболее близок по технической сущности к предлагаемому, но его недостатками являются невозможность получения нроизвольного фазового сдвига между соседними на временной диаграмме напряжениями и длительный нереходной нроцесс при пуске, достигающий величину, равную периоду выходной частоты.

Цель предлагаемого изобретения - сокращение времени переходного процесса и расщирение функциональных возможностей устройства.

Поставленная цель достигается тем, что в формирующее устройство введены дополнительно дещифратор 2т состояний, перестранваемый делитель частоты с 2т входами перестройки коэффициента деления, причем вход делителя частоты соединен с выходом задающего генератора, выходы дешифратора соединены с соответствующими входами для перестройки деления частоты и с первым входом соответствующих схем совпадения, выход делителя частоты соединен со вторыми входами всех схем совнаденнй, выходы которых соединены соответствующими входами статического /п-разрядного выходного регпстра, выходами соединенного со входами дешифратора.

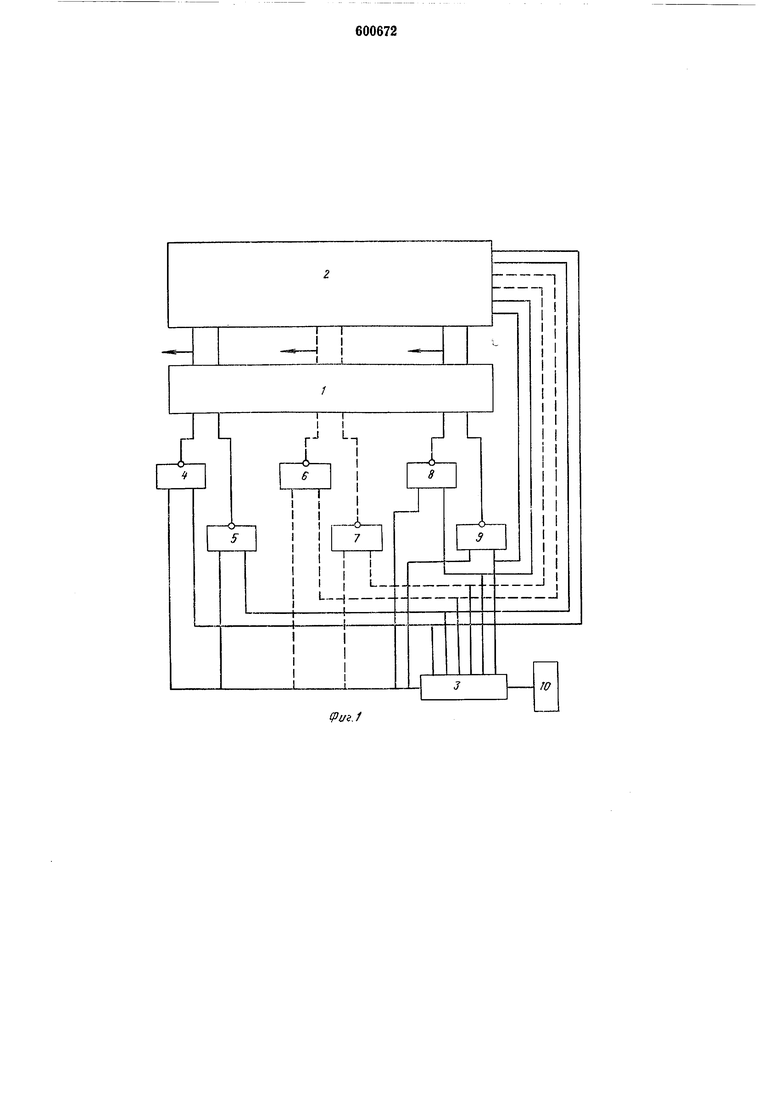

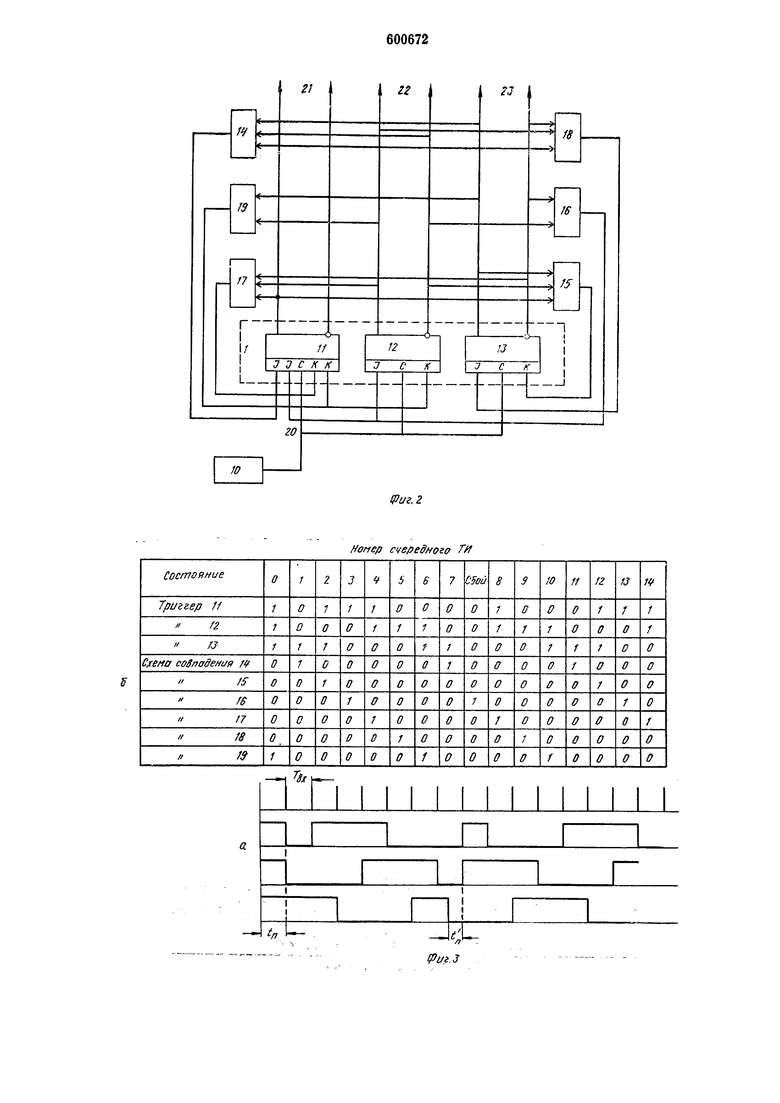

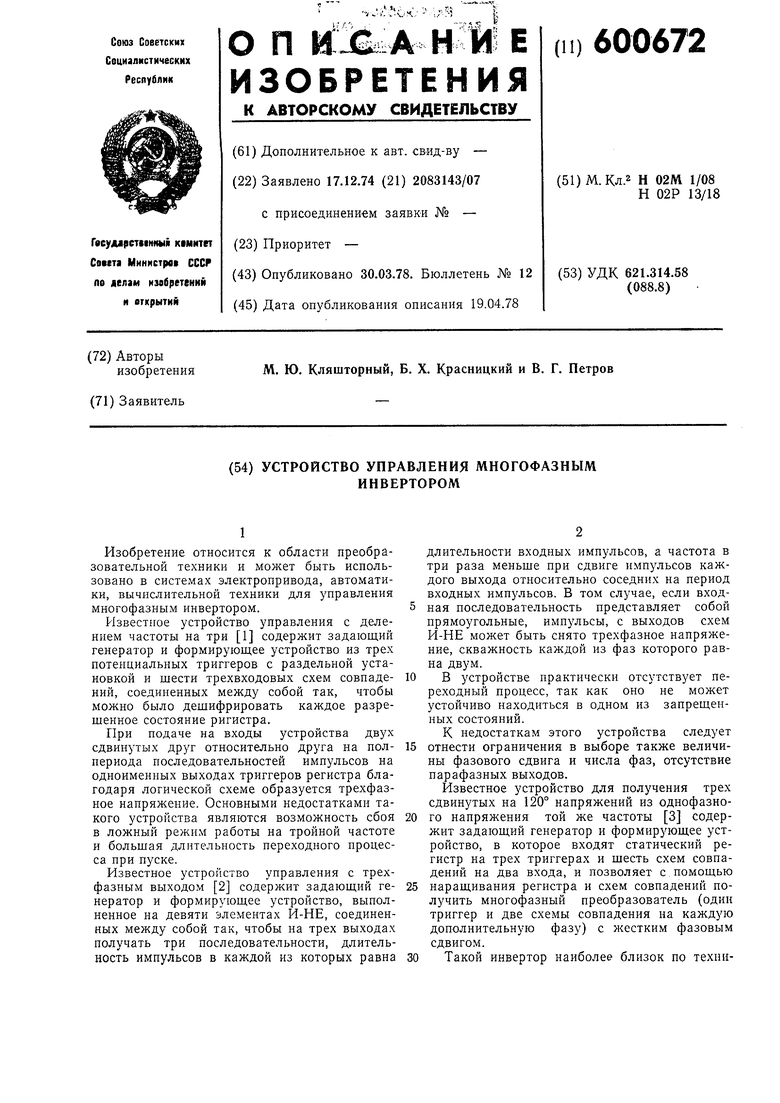

На фиг. 1 дана структурная схема предлагаемого от-фазного устройства; на фиг. 2 - логическая схема предлагаемого устройства для и фазовых сдвигах ai a2 120°; на фнг. 3 - временные диаграммы и таблица истинности устройства, изображенного на фиг. 2.

Предлагаемое устройство содержит статический т-разрядный регистр 1, с выходов которого снимается т-фазное выходное переменное нанряжение, соединенный через эти выходы со сходами дещифратора 2. Выходы дешифратора 2 управляют соответствующими входами перестройки коэффициента деления делителя частоты 3 и первыми входами схем совпадений 4, 5, 6, 7, 8 и 9. Вход делителя частоты 3 соединен с выходом задающего генератора 10, а выход - со вторыми входами всех схем совпадений 4, 6, 5, 7, 8 и 9, выходы которых связаны с соответствующими входами выходного регистра 1.

Статический регистр 1 предназначен для преобразования двоичного кода из импульсной формы представления в потенциальную, выдачи т-фазного переменного напряжения на выход устройства и хранения текущей комбинации выходов до прихода очередного управляющего сигнала с выхода делителя частоты 3.

Дещифратор 2 представляет собой дешифратор 2т разрешенных состояний регистра 1 из возможных 2™, минимизированный с учетом 2™-2т запрещенных состояний так, чтобы каждое из разбитых на группы запрещенных состояний склеивалось только с одним разрешенным, носледнее же может нокрывать группу запрещенных. Подобная минимизация нриводит к тому, что при любой запрещенной комбинацин на выходном регистре 1 полезный

сигнал появится всегда, и только на одном из выходов дешифратора 2.

Делитель частоты 3 используется для деления тактовой частоты, получаемой с задающего генератора 10 на переменный коэффициент деления, нерестройка которого осуществляется с помощью 2т выходов дешифратора 2. При этом достаточно иметь m коэффициентов деления, так как скважность выходного т-фазного нанряжения равна двум.

Схемы совнадения 4, 5, 6, 7, 8, 9 служат для формирования сигнала установки регистра 1 в разрешенные состояния.

Устройство работает следующим образом.

Исходное состояние регистра 1 дешифрируется так, чтобы при любой начальной комбинации (в том числе и запрещенной) управляющий сигнал появился только на одном из выходов дешифратора 2 (назовем его выходом /). Этот сигнал устанавливает в делителе частоты 3 соответствующей коэффициент нересчета К,, первый же импульс, появившийся на выходе делителя 3 после прихода с задающего генератора 10 серии из /Cj импульсов, пройдет через ту схему совнадения, которая подготовлена управляющим сигналом дешифратора 2, установнвшим коэффициент пересчета /Cj, и с ее выхода попадает на вход регистра 1. В регистре 1 в соответствии с заданным сдвигом фаз между выходными нанрял ениями будет установлена следующая но порядку разрешенная комбинация. После этого исчезнет сигнал на /-м выходе дешифратора 2 и появится сигнал на (/+1)-м. Делитель частоты 3 будет этим сигналом перестроен на новый коэффициент пересчета /Cj+l- Очередной имнульс на выходе делителя 3 появится после серии из Kj+l импульсов и т. д.

В качестве примера ниже приводится описание устройства управления трехфазным инвертором с постоянным фазовым сдвигом между соседними выходными напряжениями . Выбор примера продиктован наглядностью сравнения с нрототипом, поскольку его описание составлено для тех же условий. В этом случае коэффициенты деления Ki K.Kz и поэтому в схеме отсутствует делитель частоты 3.

Па фиг. 2 изображена принципиальная схема трехфазного преобразователя, которая включает в себя регистр 1, состоящий из трех /-/(-триггеров 11, 12, 13, дешифратор 2 шести разрещенных состояний регистра 1 на шести схемах совнадения 14, 15, 16, 17, 18, 19, соединенных своими выходами с соответствующими / или К. входами триггеров 11, 12, 13, и генератор 10.

Работа схемы поясняется с помощью временных диаграмм на фиг. За, приведенных к следующим точкам: выход генератора 10- точка 20; единичные выходы 21, 22 и 23 триггеров 11, 12 и 13 регистра 1 соответственно.

Для наглядности на временных диаграммах в точках 21, 22 и 23 высокие уровни напряжения, обозначенные через состояние логической единицы («1), а низкие - логического нуля («О). Условно принято, что триггеры регистра 1 устанавливаются при 0 в одно из запрещенных состояний, а именно - на выходах 21, 22 и 23 присутствуют уровни логической единицы. В этом состоянии может находиться регистр 1 как при включении питания, так и при любол виде сбоя. Причем в схеме отсутствуют какая-либо цепь, запрещающая ложные срабатывания, поскольку интервал времени, в течение которого регистр

Iнаходится в запрещенном состоянии, не превышает периода частоты, получаемой с выхода генератора 10, и отсчитывается от момента сбоя до появления импульса в точке 20.

Устройство, приведенное на фиг. 2, функционирует следующим образом.

ПОСКОЛЬКУ в момент 0 триггеры II, 12 и 13 находятся в единичном состоянии, сигнал логической единицы появится только на выходе схемы совпадения 19, что обусловлено склеиванием запрещенного состояния регистра 1 («111) с разрещенным («011), а достигается наличием связей схемы совпадения 19 только с выходами триггеров 12 и 13. Указанный сигнал поступит на К входы триггеров

IIи 12. Первый импульс, появившийся на синхровходах всех триггеров с выхода 20 генератора 10, установит своим задним фронтом триггеры И и 12 в состояние логического нуля. Таким образом, на выходах преобразователя появится разрешенная комбинация («001), что приведет к запиранию схемы совпадения 19, отпиранию схемы совпадения 14 и появлению на ее выходе единичного сигнала, который поступит на 7 вход триггера И. Очередной тактовый сигнал с генератора 10 установит триггер 11 в единичное состояние, что приведет к появлению на выходах 21, 22 и 23 комбинапии («101) и т. д.

Полный рабочий цикл преобразователя сведен в таблицу, представленную на фиг. 3, б, причем разобраны случаи установки в запрещенные состояния регистра I как при включении питания (to), так и при случайном сбое в момент tc5- В первом случае триггеры И, 12 и 13 устанавливаются в единичные состояния («111), во втором - в нулевые («000). Максимальное время переходного процесса не превосходит периода частоты синхросигналов, снимаемых с выхода генератора 10. Следовательно, по сравнению с прототипом, время переходного процесса сокращается в щесть раз.

Формула н 3 о б р е т е н и я

Устройство управления многофазным инвертором, содержащее задающий генератор, статический т-разрядный регистр (где т-число фаз), 2т двухвходовых схем совпадения, отл и ч а ю щ и и с я тем, что, с целью повышения

быстродействия и расширения функциональных возможностей, оно снабжено дешифратором на 2т состояний и перестраиваемым делителем частоты с 2га входами для перестройки коэффицтента деления, причем вход делителя частоты соедипен с выходом задающего генератора, выходы дещифратора соединены с соответствующими входами для перестройки делителя частоты и с первым входом соответствующих схем совпадения, выход делителя частоты соединен со вторыми входами всех схем совпадений, выходы которых соединены с соответствующими входами регистра, выходы которого являются выходом устройства управления и дополнптельно соединены со входами дешифратора.

Источники информации, принятые во вннмание при экспертизе 1. Авторское свидетельство СССР №356797, кл. Н ОЗК 23/24, 1970.

2. Авторское свидетельство СССР №449450, кл. Н ОЗК 23/02, 1972.

3. Патент ФРГ № 1247465, кл. 21d2 13, 1967.

Viis.f

Z1

/

п

IZ

fS

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор случайных процессов | 1979 |

|

SU849464A2 |

| Делитель частоты следования импульсов с переменным коэффициентом деления | 1978 |

|

SU786010A1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ ВРЕМЕННЫХ ИМПУЛЬСНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 1970 |

|

SU280535A1 |

| Устройство умножения частоты следования импульсов | 1975 |

|

SU525235A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ИМПУЛЬСНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 1991 |

|

RU2030831C1 |

| Устройство для преобразования частоты следования импульсов | 1978 |

|

SU764114A1 |

| ЦИФРОВОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО ГАММА-ПРОФИЛО ГРАФА | 1970 |

|

SU270858A1 |

| Устройство контроля частоты вращения | 1985 |

|

SU1303941A1 |

| Устройство для измерения угла сдвига фаз | 1990 |

|

SU1789939A1 |

| Устройство для коррекции шкалы времени | 1987 |

|

SU1432451A2 |

9

/7

Г

I I/

//

у у с к /f

IB

/У

п

/J

Авторы

Даты

1978-03-30—Публикация

1974-12-17—Подача